石经院基于FPGA等精度测频原理的频率计

石家庄经济学院

通信实习报告

院系:信息工程学院

学号:

姓名:

日期:2013.1.15

一、实习目的

1、通过本次专业课程设计巩固并扩展通信课程的基本概念、基本理论、分析方

法和仿真实现方法。

2、结合所学的EDA应用和仿真技术,完成通信专业相关课程内容的建模和设计

仿真。到达通信专业相关理论课程有效的巩固和整合,实现将理论知识和软件设计紧密结合。

3、通过本次专业课程设计达到培养学生的创新能力、通信系统建模和仿真设计

能力以及软件调试和分析能力的目的。

二、实习要求

1、应用通信类软件完成通信系统相关内容的设计和建模,并仿真出正确结果,

对仿真波形加以重点分析和说明。

2、按要求格式书写报告,原理充分、设计方法及仿真结果分析正确、条理清晰、

重点突出。

三、实习内容

1、实习题目

基于FPGA等精度测频原理的频率计

2、设计原理

(1)直接测频方法

常用的直接测频方法主要有测频法和测周期法两种:

测频法就是在确定的闸门时间Tw内。记录被测信号的变化周期数(或脉冲个数)Nx,则被测信号的频率为:Fx=Nx/Tw。

测周期法需要有标准信号的频率fs,在待测信号的一个周期Tx内,记录标准频率的周期数Ns,则被测信号的频率为:fx=fs/Ns。

这两种方法的计数值会产生±1个字误差,并且测试精度与计数器中记录的数值Nx或Ns有关。为了保证测试精度,一般对于低频信号采用测周期法;对于高频信号采用测频法,因此测试时很不方便。

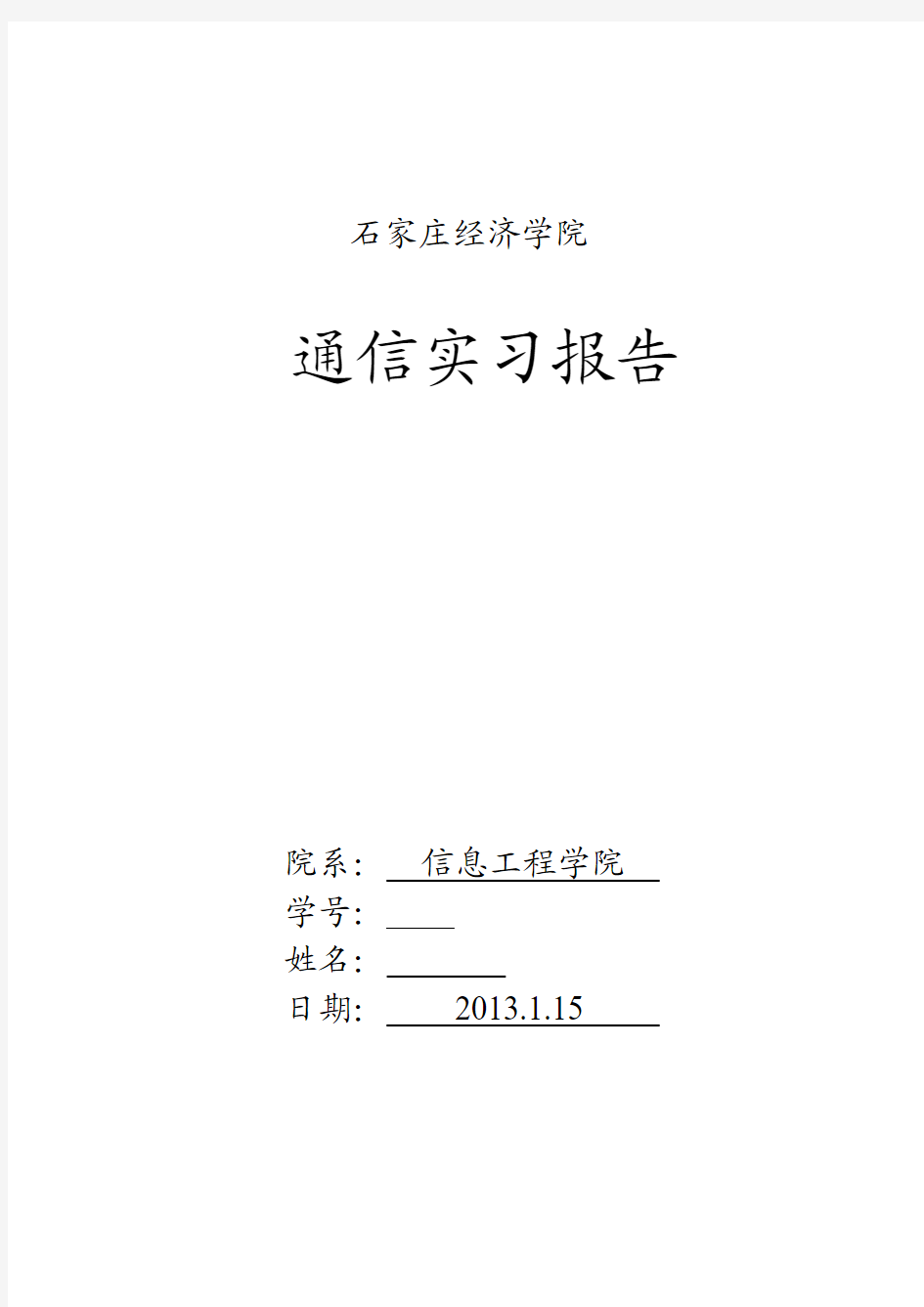

(2)等精度测频方法

图1 等精度测频原理波形图

等精度测频方法是在直接测频方法的基础上发展起来的。它的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,因此,消除了对被测信号计数所产生±1Hz误差,并且达到了在整个测试频段的等精度测量。测频原理如图1所示。

在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。首先给出闸门开启信号(预置闸门上升沿)。此时计数器并不开始计数,而是等到被测信号的上升沿到来时,计数器才真正开始计数。然后预置闸门关闭信号(下降沿)到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成一次测量过程。可以看出,实际闸门时间T与预置闸门时间下,并不严格相等,但差值不超过被测信号的一个周期。

设在一次实际闸门时间下中计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns。标准信号的频率为fs,则被测信号的频率为:

Fx=(Nx/Ns)fs。 (1)

若忽略标频fs的误差,则等精度测频可能产生的相对误差为:

δ=(|fxc-fx|/fxe)×100%。 (2)

其中&e为被测信号频率的准确值。

在测量中,由于fx计数的起停时间都是由该信号的上升沿触发的,在闸门时间T 内对fx的计数Nx无误差(T=NxTx);对fs的计数Ns最多相差一个数的误差,即

|△Ns|≤l,其测量频率为:fxe=[Nx/(Ns+△Ns)]/fs (3)

将式(1)和(3)代入式(2),并整理得:δ=|△Ns|/Ns≤l/Ns=1/(T·fs) 由上式可以看出。测量频率的相对误差与被测信号频率的大小无关,仅与闸门时间和标准信号频率有关。即实现了整个测试频段的等精度测量。闸门时间越长,标准频率越高,测频的相对误差就越小。标准频率可由稳定度好、精度高的高频率晶体振荡器产生,在保证测量精度不变的前提下,提高标准信号频率,可使闸门时间缩短,即提高测试速度。表1所列为:标频在10KHz和100MHz时闸门时间与最大允许误差的对应关系。

表1 闸门时间与精度的关系

等精度测频的实现方法可简化为图2所示的框图。CNT1和CNT2是两个可控计数器。标准频率(fs)信号从CNTl的时钟输入端CLK输入;经整形后的被测信号(&)从CN他的时钟输入端CLK输入。每个计数器中的CEN输入端为时钟使能端控制时钟输入。当预置门信号为高电平(预置时间开始)时.被测信号的上升沿通过D触发器的输出端,同时启动两个计数器计数;同样,当预置门信号为低电平(预置时间结束)时,被测信号的上升沿通过D触发器的输出端。同时关闭计数器的计数。

图2 等精度测频实现方法原理

(3)系统组成

系统由分频器、计数器l、计数器2、D触发器等组成。分频器出来的信号作为等精度测频原理的预置闸门信号。其中D触发器,计数器2和计数器1的作用与图2中所示相同。运算模块就是完成公式(1)的运算。复位主要对分频、计数器1和计数器2进行清零操作。系统组成方框图如图3所示。

图3 采用等精度测频原理的频率计系统组成方框图

3、程序与仿真

以下所列为一种4位显示等精度频率计的程序,其中系统的FPGA电路符号如图4所示。

图4 系统FPGA电路符号图

VHDL程序如下:

library ieee;

use ieee.std_logic_1164.all;

use ieee.std_logic_unsigned.all;

use ieee.std_logic_arith.all;

entity PLJ is

port(clk:in std_logic;--基准时钟(10KHz)

tclk:in std_logic; --被测信号

start:in std_logic; --复位信号

alarm0,alarm1:out std_logic; --超量程,欠量程显示

dian:out std_logic_vector(3 downto 0); --小数点

data1:out integer range 0 to 9999 ); --频率数据

end PLJ;

architecture behav of PLJ is

signal q:integer range 0 to 9999; --预置闸门分频系数

signal q1:integer range 0 to 10000; --被测信号计数器

signal q2:integer range 0 to 20000; --基准信号计数器

signal en,en1:std_logic; --预置闸门,实际闸门

signal qq,qqq:integer range 0 to 200000000; --运算器

signal data0:integer range 0 to 9999; --频率数据中间信号

begin

process(clk) --此进程得到一个预置闸门信号begin

if clk'event and clk='1' then

if start='1' then q<=0;en<='0';

else q<=q+1;en<='1';

end if;

end if;

end process;

process(tclk) --此进程计被测信号脉冲数,和得到一个实际闸门信号begin

if tclk'event and tclk='1' then

if start='1' then q1<=0;en1<='0';

elsif en='1' then q1<=q1+1;en1<='1';

else en1<='0';

end if;

end if;

end process;

process(clk) --此进程完成在实际闸门时间内,计基准脉冲数begin

if clk'event and clk='1' then

if start='1' then q2<=0;

elsif en1='1' then

if q2=20000 then q2<=20000;

else q2<=q2+1;

end if;

end if;

end if;

end process;

process(clk) --此进程完成等精度频率计的运算

begin

if clk'event and clk='1'then

if start='1' then data0<=0;dian<="0000";alarm0<='0';alarm1<='0';qqq<=0;qq<=00;

elsif en1='0' then

if q1>=1000 then qq<=q1*10000; --根据q1的大小来判断小数点的位置if qqq

end if;

elsif q1>=100 then qq<=q1*100000;

if qqq elsif data0>=10000 then data1<=1000;dian<="0000"; else data1<=data0;dian<="0010"; end if; elsif q1>=10 then qq<=q1*1000000; if qqq elsif data0>=10000 then data1<=1000;dian<="0010"; else data1<=data0;dian<="0100"; end if; elsif q1>=1 then qq<=q1*10000000; if qqq elsif data0>=10000 then data1<=1000;dian<="0100"; else data1<=data0;dian<="1000"; end if; end if; elsif q2>19999 then alarm1<='1'; --欠量程显示 else alarm1<='0'; end if; end if; end process; end behav; 仿真结果如下: 标准时钟为10khz,即周期为100us。 小数点dian在en1的下降沿就输出,只有当数据转换完成时,小数点dian的信号才能保证正确。用数据作为闸门来控制小数点dian信号输出,这部分可以在译码部分完成。 ①tclk=5clk时,即输入信号的频率为2000hz。 data1显示为2000hz。 ②tclk=10clk时,即输入信号的频率为1000hz。 data1显示为1000hz。 tclk=100clk时,即输入信号频率为100hz。 小数点dian的‘1’表示的是小数点的位置,即100.0hz。○4tclk=300clk时,即输入信号的频率为33.3hz。 ○5tclk=1000clk时,即输入信号的频率为10hz。 小数点dian的‘1’表示的是小数点的位置,即10.00hz。 ○6clk为100us,tclk为95us时,明显超过了最大量程9999khz。 可以看到alarm0由'0'变为'1',提示超量程。 ○7欠量程显示 可以看到alarm1变为'1'. 4、结论 本程序设计了一个基于等精度测频原理的频率计,并给出了系统的FPGA程序设计与仿真结果。该频率计的测量范围为1~9999kHz,其精度为lO^(-4)。用4位带小数点数码管来显示其频率,并且具有超量程、欠量程提示功能。数字频率计的设计原理实际上是测量单位时间内的周期数。这种方法免去了实测以前的预测,同时节省了划分频段的时间,克服了原来高频段采用测频模式而低频段采用测周期模式的测量方法存在换挡速度慢的缺点。和传统的频率计相比,利用FPGA 设计的频率计简化了电路板设计,提高了系统设计的实用性和可靠性,实现数字系统的软件化,这也是数字逻辑设计的趋势。 四、参考文献 [1] 梁勇,王留奎. EDA技术教程. 人民邮电出版社,2010年5月 [2] 陈琼,潘礼,黄松. FPGA系统设计与实践. 电子工业出版社,2005年1月 [3] 王紫婷,吴蓉,张彩珍,吴晓春. EDA技术与应用. 兰州大学出版社,2003 年4月 五、实习体会 通过此次课程设计,我更加扎实熟练地掌握了QuartusⅡ软件以及VHDL编程方面的知识。在设计过程中虽然遇到了一些问题,但经过一次又一次的思考,一遍又一遍的检查终于找出了原因所在,也暴露出了前期我在这方面的知识欠缺和经验不足。实践出真知,通过亲自动手制作,使我们掌握的知识不再是纸上谈兵。在终于仿真成功的那一刻,我特别开心,终于尝到了小小成功的滋味。在课程设计过程中,我们不断发现错误,不断改正,不断领悟,不断获取。 这次课程设计终于顺利完成了,在设计中遇到了很多问题,百思不得其解,最终在老师的指导下,才一一解决。在今后社会的发展和学习实践过程中,一定要不懈努力,不能遇到问题就想到要退缩,一定要不厌其烦的发现问题所在,然 后细心将其解决,只有这样,才能成功的做成想做的事,才能在今后的道路上劈荆斩棘。 我认为,这学期的课设,不仅培养了我们独立思考、动手操作的能力,其它能力上也都有了提高,也让我们小小体验了一下毕业设计的感觉。更重要的是,在课程设计中,我们学会了很多学习方法,由于每个人的题目是不一样的,每每遇到问题就得自己动手查资料,分析,修改,而这是日后最实用的,真的是受益匪浅。要面对社会的挑战,只有不断的学习、实践,再学习、再实践。这对于我们的将来也有很大的帮助。以后,不管有多苦,我想我们都能变苦为乐,找寻有趣的事情,发现其中珍贵的事情。我们都可以在课设结束之后变的更加专业、成熟,更从容地迎接大学最后的毕业设计。 课程设计使我们专业课程知识综合应用的实践训练,是我们迈向社会从事工作前的一个必不可少的过程。千里之行始于足下,通过这次课程设计,我懂得了脚踏实地的走好每一步,就是为明天能够稳健的在工作压力中奔跑,打下坚实的基础。 1 #include 目录 1. 引言 (1) 2.设计任务书 (1) 3. 数字频率计基本原理 (1) 3.1 设计思路 (1) 3.2 原理框图 (2) 4. 设计步骤及实现方法 (2) 4.1 信号拾取与整形 (2) 4.2 计数电路 (3) 4.3 锁存电路 (5) 4.4 译码显示电路 (6) 4.5 时钟电路及波形设计 (7) 5 总体电路图及工作原理 (10) 6 元器件的检测与电路调试缺点分析 (12) 7 心得体会 (12) 参考文献 (13) 1. 引言 数字频率计是一种基础测量仪器,在许多情况下,要对信号的频率进行测量,利用示波器可以粗略测量被测信号的频率,精确测量则要用到数字频率计。本设计项目可以进一步加深我们对数字电路应用技术方面的了解与认识,进一步熟悉数字电路系统设计与调试的方法和步骤。 2.设计任务书 1、设计题目:数字频率计 2、设计出一个数字频率计,其技术指标如下: ( 1 )频率测量范围: 10 ~ 9999Hz 。 ( 2 )输入电压幅度 >300mV 。 ( 3 )输入信号波形:任意周期信号。 ( 4 )显示方式:4位十进制数显示。 ( 5 )电源: 220V 、 50Hz 。 3、给定仪器设备及元器件 示波器、音频信号发生器、逻辑笔、万用表、数字集成电路测试仪、直流稳压电源。 4.电路原理要求简单,便于制作调试,元件成本低廉易购。 3. 数字频率计基本原理 3.1 设计思路 (1)利用光电开关管做电机转速的信号拾取元件,在电机的转轴上安装一圆盘,在圆盘上挖一小洞,小洞上下分别对应着光发射和光接受开关,圆盘转动一圈既光电管导通一次,利用此信号做为脉冲计数所需。 (2)计数脉冲通过计数电路进行有效的计数,按照设计要求每一秒种都必须对计数器清零一次,因为电路实行秒更新,所以计数器到译码电路之间有锁存电路,在计数器进行计数的过程中对上一次的数据进行锁存显示,这样做不仅解决了数码显示的逻辑混乱,而且避免了数码显示的闪烁问题。 (3)对于脉冲记数,有测周和测频的方式。测周电路的测量精度主要受电路系统的脉冲产生电路的影响,对于低频率信号,其精度较高。测频电路其对于正负一的信号差比较敏感,对于低频率信号的测量误差较大,但是本电路仍然采用测频方式,原因是本电路对于马达电机转速精度要求较低,本电路还有升级为频率计使用,而测频方式对高频的精度还是很高的。 时钟实现方法很多,本电路采用晶振电路,已求得高精度的时钟需求。3.2 原理框图 图3-1 系统框图 PIC单片机等精度测量频率法 单片机测量频率,是一个比较常见但又不好解决的问题。主要是测量频率是高端和低端不能兼顾的问题。测量频率无非两种方法: 1.在一段固定的时间及脉冲的个数,然后除时间得到频率。 2.测量脉宽计算频率。 第一种方法,适合测频率在1KHz以上的脉冲信号。因为要保证测量精度在0.1%,至少要保证脉冲个数在1000个,假设测10HZ左右的信号,则一个测试周期需要100秒,这显然不是我们所能接受的。 第二种方法,适合测频率小于1KHz的信号。因为要保证测量精度在0.1%,在一个脉冲宽度(1ms)内,作为时标的定时器至少要走1000个数(此时PIC 的晶振理论上至少也要4MHz)。事实上,想利用上述两种方法精确测量宽范围的频率,几乎是不可能的。PIC系列特有的平级中断,也使其测量频率比51系列测量困难。 等精度数字测频基本框图 等精度数字测频基本框图如下 fx 图中的闸门G1、G2分别用来控制输入信号周期计数和闸门时间宽度计时。其中,G1与输入信号同步,这样可使计数器N1的量化误差dN1=0。计数器N2对标准时标信号Tc进行计数,并以此来测量实际的闸门宽度Tg,则输入信号的频率可表示为: fx=N1/Tg=N1/(Tc*N2) 标准时标信号采用单片机自身的工作时钟,可看作常数。因此fx的相对误差为: dfx/fx=dN1/N1-dN2/N2=-dN2/N2 式中,dN2为计数器N2产生的量化误差,最大为±1个Tc,在实际设计中,选择适当的时标Tc和闸门宽度Tg可是N2始终足够大,以次在fx的全频段范围内得到足够高的精度。 等精度测量法的实质就是一种变相的测脉宽法。 在实际使用时(PIC为例),可将Timer0作计数器N1,Timer1作计数器N2, 2015 年全国大学生电子设计竞赛 全国一等奖作品 设计报告部分错误未修正,软 件部分未添加 竞赛选题:数字频率计(F 题) 摘要 本设计选用FPGA 作为数据处理与系统控制的核心,制作了一款超高精度的数字频率计,其优点在于采用了自动增益控制电路(AGC)和等精度测量法,全部电路使用PCB 制版,进一步减小误差。 AGC 电路可将不同频率、不同幅度的待测信号,放大至基本相同的幅度,且高于后级滞回比较器的窗口电压,有效解决了待测信号输入电压变化大、频率范围广的问题。频率等参数的测量采用闸门时间为1s 的等精度测量法。闸门时间与待测信号同步,避免了对被测信号计数所产生±1 个字的误差,有效提高了系统精度。 经过实测,本设计达到了赛题基本部分和发挥部分的全部指标,并在部分指标上远超赛题发挥部分要求。 关键词:FPGA 自动增益控制等精度测量法 目录 1. 系统方案 1.1. 方案比较与选择 宽带通道放大器 方案一:OPA690 固定增益直接放大。由于待测信号频率范围广,电压范围大,所以选用宽带运算放大器OPA690,5V 双电源供电,对所有待测信号进行较大倍数的固定增益。对于输入的正弦波信号,经过OPA690 的固定增益,小信号得到放大,大信号削顶失真,所以均可达到后级滞回比较器电路的窗口电压。 方案二:基于VCA810 的自动增益控制(AGC)。AGC 电路实时调整高带宽压控运算放大器VCA810 的增益控制电压,通过负反馈使得放大后的信号幅度基本保持恒定。 尽管方案一中的OPA690 是高速放大器,但是单级增益仅能满足本题基本部分的要求,而在放大高频段的小信号时,增益带宽积的限制使得该方案无法达到发挥部分在频率和幅度上的要求。 方案二中采用VCA810 与OPA690 级联放大,并通过外围负反馈电路实现自动增益控制。该方案不仅能够实现稳定可调的输出电压,而且可以解决高频小信号单级放大时的带宽问题。因此,采用基于VCA810 的自动增益控制方案。 正弦波整形电路 方案一:采用分立器件搭建整形电路。由于分立器件电路存在着结构复杂、设计难度大等诸多缺点,因此不采用该方案。 方案二:采用集成比较器运放。常用的电压比较器运放LM339 的响应时间为1300ns,远远无法达到发挥部分100MHz 的频率要求。因此,采用响应时间为4.5ns 的高速比较器运放TLV3501。 主控电路 方案一:采用诸如MSP430、STM32 等传统单片机作为主控芯片。单片机在现实中与FPGA 连接,建立并口通信,完成命令与数据的传输。 方案二:在FPGA 内部利用逻辑单元搭建片内单片机Avalon,在片内将单片机和测量参数的数字电路系统连接,不连接外部接线。 在硬件电路上,用FPGA 片内单片机,除了输入和输出显示等少数电路外,其它大部分电路都可以集成在一片FPGA 芯片中,大大降低了电路的复杂程度、减小了体积、电路工作也更加可靠和稳定,速度也大为提高。且在数据传输上方便、简单,因此主控电路的选择采用方案二。 文献综述 一.课题来源及研究的目的和意义 数字频率计已经广泛应用于高科技等产品上面,可以不无夸张的说没有不包含有频率计的电子产品。我国的CD、VCD、DVD和数字音响广播等新技术已开始大量进入市场;而在今天这些行业中都必须用到频率计。到今天频率计已开始并正在向智能、精细方向的发展,因此系统对电路的要求越来越高,传统的集成电路设计技术已经无法满足性能日益提高的系统要求。在信息技术高度发展的今天,电子系统数字化已成为有目共睹的趋势。从传统的应用中小规模芯片构成系统到广泛地应用单片机,直至今天FPGA/CPLD在系统设计中的应用,电子技术已迈入一个全新的阶段。而在电子技术中,频率是最基本的参数之一,而信号的频率往往与测量方案的制定、测量结果都有十分密切的关系,所以测频率方法的研究越来越受到重视。 数字频率计属于时序电路,它主要由具有记忆功能的触发器构成。在计算机及各种数字仪表中,都得到了广泛的应用。在CMOS电路系列产品中,数字频率计是用量最大、品种很多的产品,是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此,频率的测量就显得更为重要。EDA技术是面向解决电子系统最基本最底层硬件实现问题的技术,通过设计输入编辑、仿真、适配、下载实现整个系统硬件软件的设计过程。通过EDA技术设计者不但可以不必了解硬件结构设计, 而且将使系统大大简化, 提高整体的可靠性,再加上其设计的灵活性使得EDA技术得以快速发展和广泛应用。 二、主要研究内容 1、研究内容 数字频率计用于对方波、正弦波、三角波的测量,并将结果用十进制数字显示,本设计的应达到的技术指标有: 1)频率测量范围:10HZ~100MHZ; 2)测量分辨率:1HZ; 3)测量通道灵敏度:50mVpp; 4)通道输入阻抗:不小于100KΩ; 5)测量误差:±1; 2、测量方案 (1)测频原理选择 目前常用测量频率原理有三种:直接测量频率方法、直接与间接测量相结合 数字频率计 摘要 以FPGA(EP2C8Q208C8N)为控制核心设计数字频率计,设计采用硬件描述语言Verilog 该作品主要包括FPGA控制、数码管模块、信号发生器、直流电源模块、独立按键、指示灯模块。主要由直流电源供电、数字信号发生器输出信号,FPGA 控制信号的采集、处理、输出,数码管显示数据,按键切换档位,指示灯显示档位。作品实现了测频、测周、测占空比,能准确的测量频率在10Hz 到100kHz之间的信号。 关键字: 频率计等精度 FPGA (EP2C8Q208C8N)信号发生器Verilog语言 一、系统方案论证与比较 根据题目要求,系统分为以下几个模块,各模块的实现方案比较选择与确定如下: 1.主控器件比较与选择 方案一:采用FPGA(EP2C8Q208C8N)作为核心控制,FPGA具有丰富的I/O 口、内部逻辑和连线资源,采集信号速度快,运行速度快,能够显示大量的信息,分频方便。 方案二:采用SST89C51作为主控器件,虽然该款单片机较便宜,但运行速度较慢,不适合对速度有太大要求的场合,并且不带AD,增加了外围电路。 综上所述,主控器件我选择方案一。 2.测量方法的比较与选择 方案一:采用测频法测量。在闸门时间内对时钟信号和被测信号同时计数,由于在闸门闭合的时候闸门时间不能是被测信号的整数倍,导致计数相差为一个被测信号时间,所以测频法只适合频率较高的测量。 方案二:采用测周法测量。用被测信号做闸门,在闸门信号内对时钟信号计数,由于在闸门闭合的时候闸门时间不能是时钟信号的整数倍,导致计数相差为一个时钟信号时间,所以测周法只适合较低频率的测量。 方案三:采用等精度法和测周法结合的方法。用等精度发测量1KHZ以上的频率,测周法测量1KHZ一下的频率。这种方法取长补短,既能准确的测高频又能测低频。 综上所述,测量方法我选用方案三。 3. 界面显示方案的选择 方案一:采用数码管显示,控制程序简单,价格便宜,显示直观。 方案二:液晶5110,虽然体积小,可以显示各种文字,字符和图案。 考虑到数码管完全可以满足数据显示要求,所以显示部分我选用方案一。 二、理论分析与计算 1、键盘设计 系统中我们采用独立键盘,用2个I/O控制2个键。原理是将2个I/O口直接接键盘的2个引脚,低电平有效,这种键盘的优点反应的速率快。 2、计算公式 (1)测频: 1khz以上:被测频率=时钟频率*(被测频率计数/时钟频率计数) 1khz以下:被测频率=时钟频率/(时钟频率在被测信号高电平计数+时钟频率在被测信号低电平计数) VHDL 课程设计报告——基于FPGA的数字频率计 姓名: 学号: 班级: 目录 1 设计原理 (1) 2功能设计 (1) 3系统总体框图 (1) 4各功能块设计说明 (2) 5实验结果 (14) 6结论分析 (15) 一、设计原理 频计的基本原理是用一个频率稳定度高的频率源作为基准时钟,对比测量其他信号的频率。通常情况下计算每秒内待测信号的脉冲个数,即闸门时间为1 s。闸门时间可以根据需要取值,大于或小于1 s都可以。闸门时间越长,得到的频率值就越准确,但闸门时间越长,则每测一次频率的间隔就越长。闸门时间越短,测得的频率值刷新就越快,但测得的频率精度就受影响。一般取1 s作为闸门时间,此测量方法称为直接测频法。由于闸门时间通常不是待测信号的整数倍,这种方法的计数值也会产生最大为±1个脉冲误差。进一步分析测量准确度:设待测信号脉冲周期为Tx,频率为Fx,当测量时间为T=1s时,测量相对误差为Tx/T=Tx=1/Fx。由此可知直接测频法的测量准确度与信号的频率有关:当待测信号频率较高时,测量准确度也较高,反之测量准确度也较低。 二、功能设计 1、测量范围:1HZ--------99MHZ,测量精度±1HZ。 2、测量结果高4位与低4位进行分页显示。 当超过9999HZ时,系统亮灯提示超出低4位显示范围,可通过按键进行高低4位结果的显示切换。高4位显示时,伴有小数点位的点亮,提示已成功切换到高4位。 3、测量所测信号的占空比。 能够快速测出输入待测信号的占空比,并且通过按键,切换到占空比显示状态。 4、内置自测信号 由内部时钟产生三个特定时钟,以供自身测试功能是否正常。 三、系统总体框图 了解数字频率计测频率与测周期的基本原理;熟练掌握数字频率计的设计与调试方法及减小测量误差的方法。 [重点与难点] 重点:数字频率计的组成框图和波形图。 难点:时基电路和逻辑控制电路。 [理论内容] 一、数字频率计测频率的基本原理 所谓频率,就是周期性信号在单位时间(1s)内变化的次数。若在一定时间间隔T内测得这个周期性信号的重复变化次数为N,则其频率可表示为 f=N/T (1) 二、数字频率计的主要技术指标 1、频率准确度 2、频率测量范围 在输入电压符合规定要求值时,能够正常进行测量的频率区间称为频率测量范围。频率测量范围主要由放大整形电路的频率响应决定。 3、数字显示位数 频率计的数字显示位数决定了频率计的分辨率。位数越多,分辨率越高。 4、测量时间 频率计完成一次测量所需要的时间,包括准备、计数、锁存和复位时间。 三、数字频率计的电路设计与调试 1.基本电路设计 数字频率计的基本框图如图2所示,各部分作用如下。 ①放大整形电路 放大整形电路由晶体管3DG100与74LS00等组成。其中3DGl00组成放大器将输入频率为的周期信号如正弦波、三角波等进行放大。与非门74LS00构成施密特触发器,它对放大器的输出信号进行整形,使之成为矩形脉冲。 实验五数字频率计 实验目的 1. 了解数字频率计测量频率与测量周期的基本原理; 2. 熟练掌握数字频率计的设计与调试方法及减小测量误差的方法。实验任务 用中小规模集成电路设计一台简易的数字频率计,频率显示为四位,显示量程为四挡, 用数码管显示。1HZ—9.999KHZ ,闸门时间为1S ; 10HZ—99.99KHZ, 闸门时间为0.1S ; 100HZ—999.9KHZ, 闸门时间为10MS ; 1KHZ—9999KHZ, 闸门时间为1MS ; 实验五数字频率计 实验原理 1. 方案设计 原理框图见图1: 原理简述 所谓频率,就是周期性信号在单位时间(1s) 内变化的次数.若 采用等精度测频原理的频率计的设计 一.设计要求 1.设计一个用等精度测频原理的频率计。 2.频率测量测量范围1~9999; 3.用4位带小数点数码管显示其频率; 二.测频原理及误差分析 1.常用的直接测频方法主要有测频法和测周期法两种。 2.测频法就是在确定的闸门时间Tw内,记录被测信号的变化周期数(或脉冲个数)Nx,则被测信号的频率为:fx=Nx/Tw。 3.测周期法需要有标准信号的频率fs,在待测信号的一个周期Tx内,记录标准频率的周期数Ns,则被测信号的频率为:fx=fs/Ns。 4.这两种方法的计数值会产生±1个字误差,并且测试精度与计数器中记录的数值Nx或Ns有关。为了保证测试精度,一般对于低频信号采用测周期法;对于高频信号采用测频法,因此测试时很不方便,所以人门提出等精度测频方法。 5.等精度测频方法是在直接测频方法的基础上发展起来的。 6.它的闸门时间不是固定的值,而是被测信号周期的整数倍,即与被测信号同步,因此,测除了对被测信号计数所产生±1个字误差,并且达到了在整个测试频段的等精度测量。 等精度测频原理波形图 7.在测量过程中,有两个计数器分别对标准信号和被测信号同时计数。 8.首先给出闸门开启信号(预置闸门上升沿),此时计数器并不开始计数,而是等到被测信 号的上升沿到来时,计数器才真正开始计数。 然后预置闸门关闭信号(下降沿)到时,计数器并不立即停止计数,而是等到被测信号的上升沿到来时才结束计数,完成一次测量过程。可以看出,实际闸门时间τ与预置闸门时间τ1并不严格相等,但差值不超过被测信号的一个周期 9.设在一次实际闸门时间τ中计数器对被测信号的计数值为Nx,对标准信号的计数值为Ns。 10.标准信号的频率为fs,则被测信号的频率为 11.由式(1)可知,若忽略标频fs的误差,则等精度测频可能产生的相对误差为 12.δ=(|fxc-fx|/fxe)×100% (2) 13.其中fxe为被测信号频率的准确值。 14.δ=|ΔNs|/Ns≤1/Ns=1/(τ·fs) ?由上式可以看出,测量频率的相对误差与被测信号频率的大小无关,仅与闸门时间和标 准信号频率有关,即实现了整个测试频段的等精度测量。 ?闸门时间越长,标准频率越高,测频的相对误差就越小。 ?标准频率可由稳定度好、精度高的高频率晶体振荡器产生,在保证测量精度不变的前提 下,提高标准信号频率,可使闸门时间缩短,即提高测试速度。 等精度测频的实现方法可简化为下图所示的框图 三.设计步骤 ?CNT1和CNT2是两个可控计数器,标准频率(fs)信号从CNT1的时钟输入端CLK 输入;经整形后的被测信号(fx)从CNT2的时钟输入端CLK输入。 ?每个计数器中的CEN输入端为时钟使能端控制时钟输入。 ?当预置门信号为高电平(预置时间开始)时,被测信号的上升沿通过D触发器的输出端, 2015 年全国大学生电子设计竞赛 全国一等奖作品 摘要 目录 目录 前言...............................................................1 第一章 FPGA及Verilog HDL..........................................2 1.1 FPGA简介.....................................................2 1.2 Verilog HDL 概述.............................................2 第二章数字频率计的设计原理........................................3 2.1 设计要求.....................................................3 2.2 频率测量.....................................................3 2.3.系统的硬件框架设计..............................................4 2.4系统设计与方案论证............................................5 第三章数字频率计的设计............................................8 3.1系统设计顶层电路原理图........................................8 3.2频率计的VHDL设计.............................................9 第四章软件的测试...............................................15 4.1测试的环境——MAX+plusII.....................................15 4.2调试和器件编程...............................................15 4.3频率测试.....................................................16 等精度数字频率计的设计 李艳秋 摘要 基于传统测频原理的频率计的测量精度将随着被测信号频率的下降而降低,在实用中有很大的局限性,而等精度频率计不但有较高的测量精度,而且在整个测频区域内保持恒定的测试精度。运用等精度测量原理,结合单片机技术设计了一种数字频率计,由于采用了屏蔽驱动电路及数字均值滤波等技术措施,因而能在较宽定的频率范围和幅度范围内对频率,周期,脉宽,占空比等参数进行测量,并可通过调整闸门时间预置测量精度。选取的这种综合测量法作为数字频率计的测量算法,提出了基于FPGA 的数字频率计的设计方案。给出了该设计方案的实际测量效果,证明该设计方案切实可行,能达到较高的频率测量精度。 关键词等精度测量,单片机,频率计,闸门时间,FPGA Ⅱ ABSTRACT Along with is measured based on the traditional frequency measurement principle frequency meter measuring accuracy the signalling frequency the drop but to reduce, in is practical has the very big limitation, but and so on the precision frequency meter not only has teaches the high measuring accuracy, moreover maintains the constant test precision in the entire frequency measurement region. Using and so on the precision survey principle, unified the monolithic integrated circuit technical design one kind of numeral frequency meter, because has used the shield actuation electric circuit and technical measure and so on digital average value filter, thus could in compared in the frequency range and the scope scope which the width decided to the frequency, the cycle, the pulse width, occupied parameter and so on spatial ratio carries on the survey, and might through the adjustment strobe time initialization measuring accuracy. Selection this kind of synthesis measured the mensuration took the digital frequency meter the survey algorithm, proposed based on the FPGA digital frequency meter design proposal. Has produced this design proposal actual survey effect, proved this design proposal is practical and feasible, can achieve the high frequency measurement precision Keywords Precision survey, microcontroller, frequency meter, strobe time,field programmable gate array Ⅱ 基于FPGA 的数字频率计的设计和实现 杨守良 (渝西学院物理学与电子信息工程系 重庆 402168) 摘 要:现场可编程门阵列的出现给现代电子设计带来了极大的方便和灵活性,使复杂的数字电子系统设计变为芯片级设计,同时还可以很方便地对设计进行在线修改。本文以设计一个四位显示的十进制数字频率计为例,介绍了在一片F PG A 芯片上实现多位数字频率计的设计方法和实现步骤,并且给出了仿真结果。在设计中,所有频段均采用直接测频法对信号频率进行测量,克服了逼近式换挡速度慢的缺点。所设计的电路通过硬件仿真,下载到目标器件上运行,能够满足实际测量频率的要求。 关键词:数字频率计设计;V HDL ;现场可编程门阵列(FP GA );直接测频法 中图分类号:T P 271+.82 文献标识码:B 文章编号:1004373X (2005)1111803 Construction and Realization of the Digital C ymometer Based on FPGA Y A NG Shouliang (Department of Physics &Elec t roni c Informa tion Eng i neeri ng ,West ern Chongqing Uni v ersit y ,Chongqi ng ,402168,China ) Abstract :T he appear ance of F PG A (Field P ro gr ammable G ate A r ray )leads to t he co nvenience and flex ibility of the mo der n electr o nic construction ,w hich cha ng es the complicated dig ital electr onic sy stem co nstr uctio n into the on chip co nst ructio n .On the o ther hand ,it can a lso make so me o nline modificat ion expediently.W ith a case which describes an quadbit sho wn on t he decimal digital fr equency ,t he author intro duces the co nstr uct ion metho d and the r ealiza tio n steps o n a sing le F PG A chip.T he aut ho r show s an em ulational result.D ur ing the constr uction pro cess,the sig nal f requency of all the F requency Channel is measur ed by the way o f direct measurement ,which o ver comes the shor tcoming of lo w appr ox imate shift speed .W ith the cer tificatio n of t he har dwar e emulatio n system,t he cir cuit constructed can meet the demand of measur ing fr equency in the r eality,which has so me theor etic and pr act ical sig nificatio n. Keywords :desig n of the dig ital cymo meter ;V HDL ;F PGA (Field Pr og ram mable G ate A rr ay );dir ect frequency measur ement 收稿日期:200501 22 可编程逻辑器件和EDA 技术给今天的硬件系统设计者提供了强有力的工具,使得电子系统的设计方法发生了质的变化。传统的“固定功能集成块+连线”的设计方法正逐步地退出历史舞台,而基于芯片的设计方法正在成为现代电子系统设计的主流。在设计方法上,已经从“电路设计—硬件搭试—焊接”的传统方式转到“功能设计—软件模拟—下载”的电子设计自动化模式,从而大大提高了系统设计的灵活性。本文以一个四位的十六进制频率计为例,介绍其设计和实现方法。 1 数字频率计设计实例 数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器。采用V DHL 编程设计实现的数字频率计,除被测信号的整形部分、键输入部分和数码显示部分以外,其余全部在一片FPGA 芯片上实现,整个设计过程变得十分透明、快捷和方便,特别是对于各层次电路系统的工作时序的了解和把握显得尤为准确,而且具有灵活的现场可更改性。在不更改硬件电路的基础上, 对系统进行各种改进还可以进一步提高系统的性能和测量频率的范围。该数字频率计具有高速、精确、可靠、抗干扰性强、而且可根据需要进一步提高其测量频率的范围而不需要更改硬件连接图,具有现场可编程等优点。 1.1 数字频率计设计的基本原理 本文以一个四位十进制、测量范围为1Hz ~16kHz 的数字频率计为例,采用SOPC /SOC 实验开发系统,以1 Hz 测频控制信号,说明设计的基本原理及实现方法。设计的数字频率计由测频控制信号发生器模块、锁存器和译码显示模块组成。根据频率的定义和频率测量的基本原理,测定信号的频率必须有一个脉宽为1s 的对输入信号脉冲计数允许的信号;1s 计数结束后,计数值锁入锁存器的锁存信号和为下一测频计数周期做准备的计数器清0信号。这3个信号可以由一个测频控制信号发生器产生,即图1中的T EST CT L ,他的设计要求是,T EST CT L 的计数使能信号CN T _EN 能产生一个1s 脉宽的周期信号,并对频率计的每一计数器CNT 10的EN A 使能端进行同步控制。当CN T _EN 高电平时,允许计数;低电平时停止计数,并保持其所计的脉冲数。在停止计数期间,首先需要一个锁存信号LO AD 的上跳沿将计数器在前1秒钟的计数值锁 118 电子技术杨守良:基于FPGA 的数字频率计的设计和实现 基于Ver ilog语言的等精度频率计设计 赵 亮,吴振宇 (大连理工大学创新院 ,辽宁省大连市116023) 摘 要:介绍了等精度测量频率的原理,利用Veril og硬件描述语言设计实现了频率计内部功能模块,对传统的等精度测量方法进行了改进,增加了测量脉冲宽度的功能;采用AT89S51单片机进行数 据运算处理,利用液晶显示器对测量的频率、周期、占空比进行实时显示,可读性好。充分发挥FPG A (现场可编程门阵列)的高速数据采集能力和单片机的高效计算与控制能力,使两者有机地结合起来。 在QuartusⅡ6.0EDA(电子设计自动化)开发平台上进行仿真、测试,并最终下载到FPG A芯片内部。 系统测量精度高,实时性好,具有很好的应用前景。 关键词:等精度;频率计;Veril og硬件描述语言;单片机 中图分类号:T M935.1 收稿日期:2007201222;修回日期:2007203221。 0 引 言 传统测量频率的方法主要有直接测量法、分频测 量法、测周法等,这些方法往往只适用于测量一段频 率,当被测信号的频率发生变化时,测量的精度就会下 降。本文提出一种基于等精度原理的测量频率的方 法,在整个频率测量过程中都能达到相同的测量精度, 而与被测信号的频率变化无关。本文利用FPG A(现 场可编程门阵列)的高速数据处理能力,实现对被测 信号的测量计数;利用单片机的运算和控制能力,实现 对频率、周期、脉冲宽度的计算及显示。 1 等精度测量原理 等精度测量的一个最大特点是测量的实际门控时 间不是一个固定值,而是一个与被测信号有关的值,刚 好是被测信号的整数倍。在计数允许时间内,同时对 标准信号和被测信号进行计数,再通过数学公式推导 得到被测信号的频率。由于门控信号是被测信号的整 数倍,就消除了对被测信号产生的±1误差,但是会产 生对标准信号±1的误差。如图1所示。 图1 等精度测量原理 系统中,如果采用的标准信号源的精度很高,就可 以达到一个很高的测量精度,一般情况下都是采用晶 体作为标准信号源,因此可以达到很高的精度,满足一 般系统的要求。 2 FPGA模块设计 本系统在传统的等精度测量原理基础上进行了改 进和优化。增加了测量占空比的功能,同时由FPG A 内部产生清零信号,节省了资源。改进后的FPG A核 心模块如图2所示。FPG A部分主要由门控信号产生 模块、计数器控制模块、计数器模块、锁存器、中断输 出、数据选择输出、顶层模块组成。 图2 等精度测量核心结构 1)门控信号 为了测量频率为1Hz的信号,要求系统的开门时 间不小于1s;同理,为了测量0.1Hz频率的信号,要 求开门时间最短为10s。但是如果系统一直采用10s 的门控信号,测量高频信号的等待时间太长,显然不合 理,因为测量结果的显示必须要等到一个测量周期结 束之后才能更新。本系统采用的方法是,由单片机给 FPG A提供一个门控的选择信号,如果FPG A测得的频 率小于1Hz,那么单片机自动给出一个启动10s门控? 4 1 ? 第33卷第9期 2007年9月 电子工程师 E LECTRON I C E NGI N EER Vol.33No.9 Sep.2007等精度频率计设计C程序

数字频率计的设计与实现

PIC单片机等精度测量频率法

全国大学生电子设计大赛题一等奖数字频率计

基于FPGA的频率计的文献综述

等精度频率计的实验报告

基于FPGA数字频率计 (可测占空比)

数字频率计测频率与测周期的基本原理

采用等精度测频原理的频率计的设计

全国大学生电子设计大赛F题一等奖数字频率计

设计报告 部分错误未修正,软 件部分未添加

竞赛选题:数字频率计(F 题)

1 / 10

本设计选用 FPGA 作为数据处理与系统控制的核心,制作了一款超高精度 的数字频率计,其优点在于采用了自动增益控制电路(AGC)和等精度测量法, 全部电路使用 PCB 制版,进一步减小误差。

AGC 电路可将不同频率、不同幅度的待测信号,放大至基本相同的幅度, 且高于后级滞回比较器的窗口电压,有效解决了待测信号输入电压变化大、频率 范围广的问题。频率等参数的测量采用闸门时间为 1s 的等精度测量法。闸门时 间与待测信号同步,避免了对被测信号计数所产生±1 个字的误差,有效提高了 系统精度。

经过实测,本设计达到了赛题基本部分和发挥部分的全部指标,并在部分指 标上远超赛题发挥部分要求。

关键词:FPGA 自动增益控制 等精度测量法

1 / 10

摘 要....................................................................................................................1 目录........................................................................................................................ 2 1. 系统方案...................................................................................................3

1.1. 方案比较与选择................................................................................3 1.1.1. 宽带通道放大器.........................................................................3 1.1.2. 正弦波整形电路.........................................................................3 1.1.3. 主控电路.....................................................................................3 1.1.4. 参数测量方案.............................................................................4

1.2. 方案描述............................................................................................4 2. 电路设计...................................................................................................4

2.1. 宽带通道放大器分析........................................................................4 2.2. 正弦波整形电路................................................................................5 3. 软件设计...................................................................................................6 4. 测试方案与测试结果...............................................................................6 4.1. 测试仪器............................................................................................6 4.2. 测试方案及数据................................................................................7

4.2.1. 频率测试.....................................................................................7 4.2.2. 时间间隔测量.............................................................................7 4.2.3. 占空比测量.................................................................................8 4.3. 测试结论............................................................................................9 参考文献................................................................................................................ 9

2 / 10计算机毕业论文_基于FPGA的等精度频率计的设计与实现

等精度数字频率计的设计

基于FPGA的数字频率计的设计和实现

基于Verilog语言的等精度测频计设计