数字逻辑习题参考解答

第6章习题参考解答

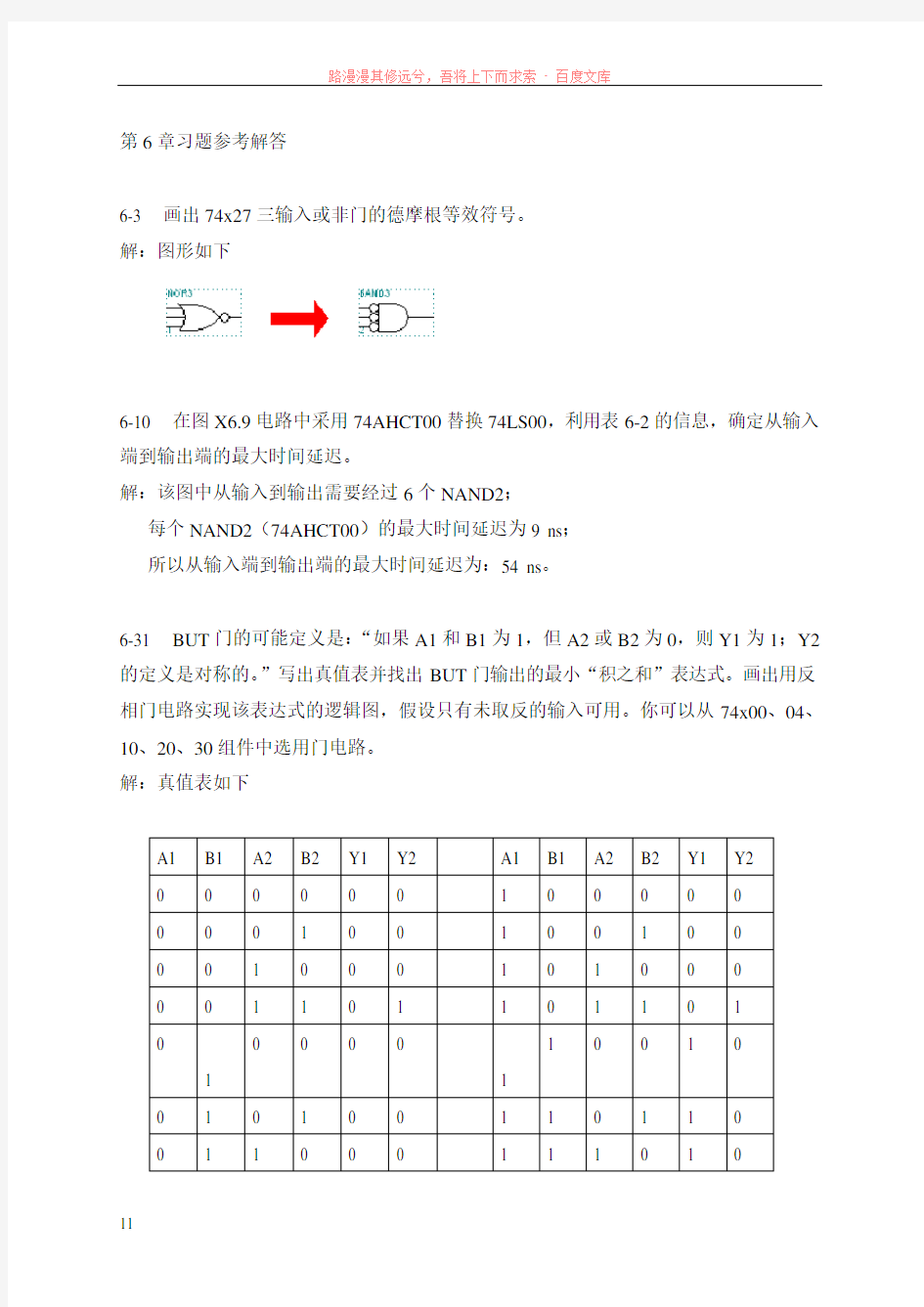

6-3 画出74x27三输入或非门的德摩根等效符号。

解:图形如下

6-10 在图X6.9电路中采用74AHCT00替换74LS00,利用表6-2的信息,确定从输入端到输出端的最大时间延迟。

解:该图中从输入到输出需要经过6个NAND2;

每个NAND2(74AHCT00)的最大时间延迟为9 ns;

所以从输入端到输出端的最大时间延迟为:54 ns。

6-31 BUT门的可能定义是:“如果A1和B1为1,但A2或B2为0,则Y1为1;Y2的定义是对称的。”写出真值表并找出BUT门输出的最小“积之和”表达式。画出用反相门电路实现该表达式的逻辑图,假设只有未取反的输入可用。你可以从74x00、04、10、20、30组件中选用门电路。

解:真值表如下

A1 B1 A2 B2 Y1 Y2 A1 B1 A2 B2 Y1 Y2

0 0 0 0 0 0 1 0 0 0 0 0

0 0 0 1 0 0 1 0 0 1 0 0

0 0 1 0 0 0 1 0 1 0 0 0

0 0 1 1 0 1 1 0 1 1 0 1

1

0 0 0 0

1

1 0 0 1 0

0 1 0 1 0 0 1 1 0 1 1 0

0 1 1 0 0 0 1 1 1 0 1 0

0 1 1 1 0 1 1 1 1 1 0 0

利用卡诺图进行化简,可以得到最小积之和表达式为

Y1=A1·B1·A2’+A1·B1·B2’ Y2=A1’·A2·B2+B1’·A2·B2Y 2

采用74x04得到各反相器 采用74x10得到3输入与非 采用74x00得到2输入与非 实现的逻辑图如下:

6-32 做出练习题6-31定义的BUT 门的CMOS 门级设计,可以采用各种反相门逻辑的组合(不一定是二级“积之和”),要求使用的晶体管数目最少,写出输出表达式并画出逻辑图。

解:CMOS 反相门的晶体管用量为基本单元输入端数量的2倍;

对6-31的函数式进行变换:

()()()()'2211'2'211'211'2111B A B A B A B A B B A A B A Y ???=+??=??+??= ()()()()'1122'1'122'122'1222B A B A B A B A B B A A B A Y ???=+??=??+??=

利用圈-圈逻辑设计,可以得到下列结构:

()()()'''22'111B A B A Y ?+?= ()()()'''11'222B A B A Y ?+?=

此结构晶体管用量为20只 (原设计中晶体管用量为40只)

6-20 采用一片74x138或74x139二进制译码器和NAND 门,实现下列单输出或多数出逻辑函数。

解:a) ()∑=Z Y X F ,,7,4,2

b) ()()∑∏==C B A C B A F ,,,,2,1,07,6,5,4,3

c) ()()∑∑?==d C B A C B A D F ,,,,,6,5,1,0'12,10,2,0

d) ()()()∑∑∑?+==Z Y X W Y X Z W W F ,,,,,2,1'214,12,10,8,5,4,3,2

e) ()∑=Y X W F ,,5,4,2,0 ()∑=Y X W G ,,6,3,2,1

f) ()()∑∑?==B A C B A C F ,,,3,1'6,2 ()()∑∑=?==E D C E D C G ,,,3,2,0'3,2,0

6-38 假设要求设计一种新的组件:优化的十进制译码器,它只有十进制输入组合。与取消6个输出的4-16译码器相比,怎样使这样的译码器价格降至最低?写出价格最低译码器的全部10个输出的逻辑等式。假设输入和输出高电平有效且没有使能输入。 解:

设输入为:A ,B ,C ,D ,将6个输入组合作为无关项以化简其余输出的乘积项,输出函数卡诺图如下:

利用无关项进行最小成本设计,可以得到下列输出函数:

''''0D C B A Y ???= D C B A Y ???='''1 ''2D C B Y ??= D C B Y ??='3 ''4D C B Y ??= D C B Y ??='5 '6D C B Y ??= D C B Y ??=7 '8D A Y ?= D A Y ?=9

与4-16译码器的前10个输出的实现相比,减少了10个与门输入端,减少了20只晶体管的用量。

6-43 采用一片SSI 器件(4 x Nand2)和一片74x138,实现下列4个逻辑函数。 解:()∑=??+??=Z Y X Z Y X Z Y X F ,,7,0'''1 ()∑=??+??=Z Y X Z Y X Z Y X F ,,6,1'''2 ()∑=??+??=Z Y X Z Y X Z Y X F ,,5,2'''3 ()∑=??+??=Z Y X Z Y X Z Y X F ,,4,3'''4

6-21 图X6.21电路有什么可怕的错误?提出消除这个错误的方法。

解:该电路中74x139两个2-4译码器同时使能,会导致2个3态门同时导通,导致输出逻辑电平冲突。为解决这一问题,可将使能端分开,进行反相连接,各自使能,即可消除该错误。

6-63设计适合于24引脚IC 封装的3输入,5位多路复用器,写出真值表并画出逻辑图和逻辑符号。

解:设数据输入A(4..0),B(4..0),C(4..0),数据输出Y (4..0) 选择端S1,S0 则 Y=S1·S0·A+S1·S0’·B+S1’·S0·C 真值表:

S1 S0 Y 0 0 d 0 1 C 1 0 B 1

1

A

其中Y ,A,B,C 均为5位总线,S1,S2为单线,加上电源和接地,可以采用24引脚IC 封装。

逻辑图和逻辑符号如下:

6-68 对于图X6.68所示CMOS电路实现的逻辑功能,写出真值表并画出逻辑图(电路包含3.7.1节介绍的传输门)。

解:

S A B Z S A B Z

0 0 0 0 1 0 0 0

0 0 1 0 1 0 1 1

0 1 0 1 1 1 0 0

0 1 1 1 1 1 1 1

Z=AS’ Z=SB

Z=AS’+BS为2选1多路器

逻辑图为:

6-24 采用奇数块XNOR门,用图6-70(a)的形式构成某种校验电路,该电路实现什么功能?

解:XNOR为XOR增加一个反相圈构成;对于偶数块的连接,利用圈到圈设计可以看到,功能与XOR的连接相同(如下图所示);

所以,对于奇数块连接时,输出与对应XOR 连接电路正好相反,即得到偶校验电路。

6-96 采用3块74x682和必要的门电路设计一个24位比较器,将2个24位的无符号数P 和Q 进行比较,产生2位输出表达P=Q 和P>Q 。

解:利用3块74x682(8位数值比较器)分别进行高中低3个8位段的比较; 将各段的PEQQ_L 进行NAND 运算,可以得到PEQQ (P=Q );

()''3'2'1321PEQQ PEQQ PEQQ PEQQ PEQQ PEQQ PEQQ ++=++=

利用下式可以得到PGTQ (P>Q ):

()()()'

'3'2'1'2'1'13

21211PGTQ PEQQ PEQQ PGTQ PEQQ PGTQ PGTQ PEQQ PEQQ PGTQ PEQQ PGTQ PGTQ ++?+?=??+?+=

电路连接图如下所示:

6-97 设计一个3位相等检测器,该器件具有6个输入端:SLOT[2..0]和GRANT[2..0],一个低电平有效的输出端MATCH_L 。利用表6-2,6-3提供的SSI 和MSI 器件,设计

出最短时间延迟的器件。

解:采用表6-3的74FCT682,延迟时间为11 ns。器件连接图如下:

数字逻辑电路期末考试试卷及答案

期末考试试题(答案) 考试科目:数字逻辑电路 试卷类别:3卷 考试时间:110 分钟 XXXX 学院 ______________系 级 班 姓名 学号 题号 一 二 三 四 总分 得分 一、选择题(每小题2分,共20分) 1. 八进制(273)8中,它的第三位数2 的位权为___B___。 A .(128)10 B .(64)10 C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。 A .A B F = B . C AB F += C .C A AB F += D . C B AB F += 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A . 原码 B .ASCII 码 C . 补码 D . BCD 码 4.对于如图所示波形,其反映的逻辑关系是___B_____。 A .与关系 B . 异或关系 C .同或关系 D .无法判断 5. 连续异或1985个1的结果是____B_____。 A .0 B .1 C .不确定 D .逻辑概念错误 得分 评卷人 装 订 线 内 请 勿 答 题

6. 与逻辑函数D C B A F+ + + =功能相等的表达式为___C_____。 D C B A F+ + + =B.D C B A F+ + + = D.D C B A F+ + = 7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。 8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为 _____D_____。 A.500KHz B.200KHz C.100KHz D.50KHz 9.下列器件中,属于时序部件的是_____A_____。 A.计数器B.译码器C.加法器D.多路选择器 装

万能课程设计心得体会2个

1 两周的课程设计结束了,在这次的课程设计中不仅检验了我所学习的知识,也培养了我如何去把握一件事情,如何去做一件事情,又如何完成一件事情。在设计过程中,与同学分工设计,和同学们相互探讨,相互学习,相互监督。学会了合作,学会了运筹帷幄,学会了宽容,学会了理解,也学会了做人与处世。 课程设计是我们专业课程知识综合应用的实践训练,着是我们迈向社会,从事职业工作前一个必不少的过程.”千里之行始于足下”,通过这次课程设计,我深深体会到这句千古名言的真正含义.我今天认真的进行课程设计,学会脚踏实地迈开这一步,就是为明天能稳健地在社会大潮中奔跑打下坚实的基础. 通过这次模具设计,本人在多方面都有所提高。通过这次模具设计,综合运用本专业所学课程的理论和生产实际知识进行一次冷冲压模具设计工作的实际训练从而培养和提高学生独立工作能力,巩固与扩充了冷冲压模具设计等课程所学的内容,掌握冷冲压模具设计的方法和步骤,掌握冷冲压模具设计的基本的模具技能懂得了怎样分析零件的工艺性,怎样确定工艺方案,了解了模具的基本结构,提高了计算能力,绘图能力,熟悉了规范和标准,同时各科相关的课程都有了全面的复习,独立思考的能力也有了提高。 在这次设计过程中,体现出自己单独设计模具的能力以及综合运用知识的能力,体会了学以致用、突出自己劳动成果的喜悦心情,从中发现自己平时学习的不足和薄弱环节,从而加以弥补。 在此感谢我们的xxx老师.,老师严谨细致、一丝不苟的作风一直是我工作、学习中的榜样;老师循循善诱的教导和不拘一格的思路给予我无尽的启迪;这次模具设计的每个实验细节和每个数据,都离不开老师您的细心指导。而您开朗的个性和宽容的态度,帮助我能够很顺利的完成了这次课程设计。 同时感谢对我帮助过的同学们,谢谢你们对我的帮助和支持,让我感受到同学的友谊。 由于本人的设计能力有限,在设计过程中难免出现错误,恳请老师们多多指教,我十分乐意接受你们的批评与指正,本人将万分感谢。 2 通过此次课程设计,使我更加扎实的掌握了有关xxx方面的知识,在设计过程中虽然遇到了一些问题,但经过一次又一次的思考,一遍又一遍的检查终于找出了原因所在,也暴露出了前期我在这方面的知识欠缺和经验不足。实践出真知,通过亲自动手制作,使我们掌握的知识不再是纸上谈兵。 过而能改,善莫大焉。在课程设计过程中,我们不断发现错误,不断改正,不断领悟,不断获取。最终的检测调试环节,本身就是在践行“过而能改,善莫大焉”的知行观。这次课程设计终于顺利完成了,在设计中遇到了很多问题,最后在老师的指导下,终于游逆而解。在今后社会的发展和学习实践过程中,一定要不懈努力,不能遇到问题就想到要退缩,一定要不厌其烦的发现问题所在,然后一一进行解决,

数字逻辑电路试题

院系: 专业班级: 学号: 姓名: 座位号: A. 4 B. 3 C. 6 D. 5 7. 下列电路中属于时序逻辑电路的是 【 】 A. 加法器 B. 数据分配器 C. 计数器 D. 译码器 8. 下列关于门电路的使用,描述不正确的是 【 】 A. TTL 与非门闲置输入端可以直接接电源 B. 具有推拉输出结构的TTL 门电路的输出端可以直接并联使用 C. CMOS 或门闲置输入端应接地 D. CMOS 门电路的闲置输入端不允许悬空 9. 为了降低555定时器组成多谐振荡器的振荡频率,外接R 、C 值应为 【 】 A. 同时增大R 、C 值 B. 同时减小R 、C 值 C. 同比增大R 值减小C 值 D. 同比增大C 值减小R 值 10. 若停电数分钟后恢复供电,下列选项中信息能够保持不变的是 【 】 A. ROM B. 动态RAM C. MUX D. 静态RAM 1. 8位D/A 转换器的理论分辨率是_____________________。 2. 64个输入端的编码器按二进制数编码时,输出端的个数是__________________。 3. 变量数相同时,下标编号相同的最大项i M 和最小项i m 的关系是_____________。 4. 图2.1所示集成计数器的模M=_____________________。 图2.1 (题2.4图) 5. 共阳极接法数码显示器需要配用输出 电平有效的译码器。 二、填空题 (每小题2分,共20分)

6. 对于T 触发器,当T=______时,触发器处于保持状态。 7. 逻辑函数C B AB F +=的反函数F 为_____________________。 8. 5个变量的逻辑函数全部最大项有_____________________个。 9. 二进制数()20110.101110转换成十进制数是___________________。 10. 同步RS 触发器的特性方程中,约束条件为RS=0,说明这两个输入信号不能同时为_____________________。 1. 时序逻辑电路中可以没有门电路,但是必须要有触发器。 ( ) 2. 对于二进制正数,反码和补码相同。 ( ) 3. 半加器只能用于对两个1位二进制数相加。 ( ) 4. 多谐振荡器需要输入触发信号才可以输出矩形脉冲。 ( ) 5. 逻辑函数的取值与逻辑变量的取值不同,可以有0、1、2等多种可能。 ( ) 6. 分析组合逻辑电路的目的是要得到逻辑电路的真值表。 ( ) 7. 数字逻辑电路的晶体管和模拟电路的晶体管工作状态相同。 ( ) 8. 同步时序逻辑电路有稳定状态,异步时序逻辑电路没有稳定状态。 ( ) 9. 两个或多个OC 门的输出端可以直接相连,实现线与。 ( ) 10. 可编程阵列逻辑PAL 的与阵列可编程,或阵列不可编程。 ( ) 1. 写出图4.1所示电路表示的逻辑函数关系式; F A C B 图4.1(题4.1) F= _____________________ 2. 画出实现逻辑函数C B A ABC Y +=的门电路图; 3. 由D 触发器和与非门组成的电路如图 4.2所示,试画出Q 端的波形,设电路 初态为 0; A Q 12345CP A Q 图4.2(题4.2) 4. 用卡诺图法将逻辑函数()∑=)15,14,12,10,8,7,5,2,0(m D ,C ,B ,A Y 化成最简 “与或”表达式。 四、综合题 (每小题5分,共20分) 三、判断题(正确的在题号后括号内填写“T ”,错误的填写“F ”) (每小题1分,共10分)

《数字逻辑》考试答案

中国石油大学(北京)远程教育学院 《数字逻辑》期末复习题 一、单项选择题 1. TTL 门电路输入端悬空时,应视为( A ) A. 高电平 B. 低电平 C. 不定 D. 高阻 2. 最小项D C B A 的逻辑相邻项是( D ) A .ABCD B .D B C A C .C D AB D .BCD A 3. 全加器中向高位的进位1+i C 为( D ) A. i i i C B A ⊕⊕ B.i i i i i C B A B A )(⊕+ C.i i i C B A ++ D.i i i B C A )(⊕ 4. 一片十六选一数据选择器,它应有( A )位地址输入变量 A. 4 B. 5 C. 10 D. 16 5. 欲对78个信息以二进制代码表示,则最少需要( B )位二进制码 A. 4 B. 7 C. 78 D. 10 6. 十进制数25用8421BCD 码表示为(B ) A.10 101 B.0010 0101 C.100101 D.10101 7. 常用的BCD 码有(C ) A:奇偶校验码 B:格雷码 C:8421码 D:ASCII 码 8. 已知Y A AB AB =++,下列结果中正确的是(C ) A:Y=A B:Y=B C:Y=A+B D: Y A B =+ 9. 下列说法不正确的是( D ) A:同一个逻辑函数的不同描述方法之间可相互转换 B:任何一个逻辑函数都可以化成最小项之和的标准形式 C:具有逻辑相邻性的两个最小项都可以合并为一项 D:任一逻辑函数的最简与或式形式是唯一的 10. 逻辑函数的真值表如下表所示,其最简与或式是(C )

A: ABC ABC ABC ++ B: ABC ABC ABC ++ C: BC AB + D: BC AC + 11.以下不是逻辑代数重要规则的是( D ) 。 A. 代入规则 B. 反演规则 C. 对偶规则 D. 加法规则 12.已知函数E)D (C B A F +?+=的反函数应该是( A ) 。 A. [])E (D C B A F +?+?= B. [])E D (C B A F +?+?= C. [])E (D C B A F +?+?= D. [] )E D (C B A F +?+?= 13.组合逻辑电路一般由( A )组合而成。 A 、门电路 B 、触发器 C 、计数器 D 、寄存器 14.求一个逻辑函数F 的对偶式,可将F 中的( A )。 A 、“·”换成“+”,“+”换成“·”,常数中的“0”“1”互换 B 、原变量换成反变量,反变量换成原变量 C 、变量不变 D 、常数中的“0”换成“1”,“1”换成“0” 15.逻辑函数()()()()=++++=E A D A C A B A F ( A ) 。 A. AB+AC+AD+AE B. A+BCED C. (A+BC)(A+DE) D. A+B+C+D+E 16.下列逻辑电路中,不是组合逻辑电路的有( D ) A 、译码器 B 、编码器 C 、全加器 D 、寄存器 17.逻辑表达式A+BC=( C )

《数字逻辑与数字系统》期末考试试题(A)

北京邮电大学2008——2009学年第一学期 《数字逻辑与数字系统》期末考试试题(A ) 考试注意事项 一、学生参加考试须带学生证或学院证明,未带者不准进入考场。学生必须按照监考教师指定座位就坐。 二、书本、参考资料、书包等物品一律放到考场指定位置。 三、学生不得另行携带、使用稿纸,要遵守《北京邮电大学考场规则》,有考场违纪或作弊行为者,按相应规定严肃处理。 四、学生必须将答题内容做在试题答卷上,做在草稿纸上一律无效。 五、学生的姓名、班级、学号、班内序号等信息由教材中心统一印制。 考试 课程 数字逻辑与数字系统 考试时间 2009年1月13日 题号 一 二 三 四 五 六 七 八 总分 满分 10 20 10 10 10 12 14 14 得分 阅卷 教师 一、选择题(每小题1分,共10分。) 1. )D C B (B )B A (A F ++++==( ) A . B B . A+B C . 1 D .AB 2.同步时序电路和异步时序电路比较,其差异在于后者( ) A . 没有稳定状态 B . 没有统一的时钟脉冲控制 C . 输入数据是异步的 D . 输出数据是异步的 3.(10000011)8421BCD 的二进制码为( )。 A .( 10000011)2 B .(10100100)2 C . (1010011)2 D . (11001011)2 4. 74LS85为四位二进制数据比较器。如果只进行4位数据比较,那么三个级联输入端ab 、a=b 应为( )。 A . ab 接地,a=b 接地 B . ab 接高电平,a=b 接高电平 C . ab 接高电平,a=b 接地

课程设计心得体会范文

课程设计心得体会范文 范文一 整个设计通过了软件和硬件上的调试。我想这对于自己以后的学习和工作都会有很大的帮助。在这次设计中遇到了很多实际性的问题,在实际设计中才发现,书本上理论性的东西与在实际运用中的还是有一定的出入的,所以有些问题不但要深入地理解,而且要不断地更正以前的错误思维。一切问题必须要靠自己一点一滴的解决,而在解决的过程当中你会发现自己在飞速的提升。对于教材管理系统,其程序是比较简单的,主要是解决程序设计中的问题,而程序设计是一个很灵活的东西,它反映了你解决问题的逻辑思维和创新能力,它才是一个设计的灵魂所在。因此在整个设计过程中大部分时间是用在程序上面的。很多子程序是可以借鉴书本上的,但怎样衔接各个子程序才是关键的问题所在,这需要对系统的结构很熟悉。因此可以说系统的设计是软件和硬件的结合,二者是密不可分的。通过这次课程设计我也发现了自身存在的不足之处,虽然感觉理论上已经掌握,但在运用到实践的过程中仍有意想不到的困惑,经过一番努力才得以解决。 这也激发了我今后努力学习的兴趣,我想这将对我以后的学习产生积极的影响。其次,这次课程设计让我充分认识到团队合作的重要性,只有分工协作才能保证整个项目的有条不絮。另外在课程设计的过程中,当我们碰到不明白的问题时,指导老师总是耐心的讲解,给我们的设计以极大的帮助,使我们获益匪浅。因此非常感谢老师的教导。通过这次设计,我懂得了学习的重要性,了解到理论知识与实践相结合的重要意义,学会了坚持、耐心和努力,这将为自己今后的学习和工作做出了最好的榜样。我觉得作为一名软件工程专业的学生,这次课程设计是很有意义的。更重要的是如何把自己平时所学的东西应用到实际中。虽然自己对于这门课懂的并不多,很多基础的东西都还没有很好的掌握,觉得很难,也没有很有效的办法通过自身去理解,但是靠着这一个多礼拜的“学习”,在小组同学的帮助和讲解下,渐渐对这门课逐渐产生了些许的兴趣,自己开始主动学习并逐步从基础慢慢开始弄懂它。 我认为这个收获应该说是相当大的。一开始我们从参考书上找来了课题,但是毕竟是参考书,做到后来发现很多程序都是不完整的,这让我们伤透了脑筋。看着别的小组都弄得有模有样了,可是我们连一个课题都还没有定好。好不容易又找到了课题,可是结果还是很不尽人意。程序接线什么的都弄好了,调试也没有问题,可是就是无法达到预期想要的结果。参考书毕竟只是一个参考,设计这种东西最后还是要靠自己动脑筋。然后我们大家一起齐心协力,从平时做的实验﹑老师上课的举例﹑书本上的知识以及老师的辅导和其他同学的帮助下终于完成了。应该说这是通过我们小组成员的共同努力和动脑完成的,虽然内容并不是很复杂,但是我们觉得设计的过程相当重要,学到了很多,收获了很多。我觉得课程设计反映的是一个从理论到实际应用的过程,但是更远一点可以联系到以后毕业之后从学校转到踏上社会的一个过程。小组人员的配合﹑相处,以及自身的动脑和努力,都是以后工作中需要的。 所以我认为这次的课程设计意义很深,和其他4位同学的共同学习﹑配合﹑努力的 过程也很愉快,另外还要感谢老师的耐心辅导。 范文二 对于此次课程设计,我早在寒假就借了linux相关书籍参看,但上面讲的主要是有关linux操作方面的内容,编程方面讲得很少,而且在假期中也并不知道课设的题目是什么,因此此次课设基本上都是在开学后的这两周内完成的。 以前做过的软件方面的课设如c语言课设、数据结构课设都是在假期完成的,由于自己是一个十分追求完美的人,因此几乎每次都花了将近大半个假期的时间来做,如c语言就花了一个多月的时间来做,分数当然也较高,有90来分。对于课程设计,我历来都是相当认真的,此次操作系统的课程设计当然也不例外。可是linux以前没怎么接触过,学校也没怎么系统地讲过,在刚接到题目时除了知道如何用gcc编译等等,几乎可以算作处于一无所知的

数字逻辑复习题

数字逻辑复习题

————————————————————————————————作者:————————————————————————————————日期: 1

1 数字逻辑复习提要 一、选择题 1.若ABCDEFGH 为最小项,则它有逻辑相邻项个数为( A ) A. 8 B. 82 C. 28 D. 16 2.如果编码0100表示十进制数4,则此码不可能是(B ) A. 8421BCD 码 B. 5211BCD 码 C. 2421BCD 码 D. 余3循环码 3.构成移位寄存器不能采用的触发器为( D ) A. R-S 型 B. J-K 型 C. 主从型 D. 同步型 5.以下PLD 中,与、或阵列均可编程的是(C )器件。 A. PROM B. PAL C. PLA D. GAL 6.函数F(A,B,C,D)=∑m(1,3,4,6,8,10),它的卡诺图如右图所示。函数的最简与或表达式F= A 。 A . B . C . D . 7.组合电路是指 B 组合而成的电路。 A .触发器 B .门电路 C .计数器 D .寄存器 8.电路如右图所示,经CP 脉冲作用后,欲使Q n+1 =Q ,则A ,B 输入应为 A 。 A .A=0,B=0 B .A=1,B=1 C .A=0,B=1 D .A=1,B=0 9.一位十进制计数器至少需要 4个触发器。 A .3 B .4 C .5 D .10 D B A D B A D B A ++D B A D C A C B A ++D C A D B A C B A ++D B A D B A D B A ++

数字逻辑电路期末考试卷及答案

- - 优质资料 期末考试试题(答案) 考试科目:数字逻辑电路 试卷类别:3卷考试时间:110 分钟 XXXX 学院 ______________系级班 学号 题号 一 二 三 四 总分 得分 一、选择题(每小题2分,共20分) 1. 八进制(273)8中,它的第三位数2 的位权为___B___。 A .(128)10 B .(64)10 C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。 A .A B F =B . C AB F += C .C A AB F += D .C B AB F += 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A . 原码 B .ASCII 码 C . 补码 D .BCD 码 4.对于如图所示波形,其反映的逻辑关系是___B_____。 得分 评卷人 装 订 线 内 请 勿 答 题

- 优 A .与关系 B . 异或关系 C .同或关系 D .无法判断 5. 连续异或1985个1的结果是____B_____。 A .0 B .1 C .不确定 D .逻辑概念错误 6. 与逻辑函数D C B A F +++=功能相等的表达式为___C_____。 A .D C B A F +++=D C B A F +++= .D C B A F ++= 7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。 8. 如图所示电路,若输入CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。 A . 500KHz B .200KHz

数字逻辑期末考试题

数字逻辑考试题 数字逻辑考试题(一) 一、填空(共17分,每空1分) 1. (1011.11)B =( ) D =( )H 2. (16)D =( )8421BCD 码。 3. 三态门的输出有 、 、 三种状态。 6. ABC C B A Y =),,( 的最简式为Y= 。 7. 由n 位寄存器组成的扭环型移位寄存器可以构成 进制计数器。 10. 四位环型计数器初始状态是1000,经过5个时钟后状态为 。 11. 在RS 、JK 、T 和D 触发器中, 触发器的逻辑功能最多。 12. 设一个包围圈所包围的方格数目为S ,消去的变量数目为N ,那么S 与N 的关系式应是 。 13. 在卡诺图化简逻辑函数时,圈1求得 的最简与或式,圈0求得 的最简与或式。 二、选择(共10分,每题1分) 1. DE BC A Y +=的反函数为Y =( )。 A. E D C B A Y +++?= B. E D C B A Y +++?= C. )(E D C B A Y +++?= D. )(E D C B A Y +++?= 3. 十进制数25用8421BCD 码表示为( )。 A. 10101 B. 0010 0101 C. 100101 D. 10101 4. 若用1表示高电平,0表示低电平,则是( )。 A. 正逻辑 B. 负逻辑 C. 正、负逻辑 D. 任意逻辑 5. 下逻辑图的逻辑表达式为( )。 A. AC BC AB Y = B. BC AC AB Y ++= C. BC AC AB Y ++= D. BC AC AB Y = 6. 三态门的逻辑值正确是指它有( )。 A. 1个 B. 2个 C. 3个 D. 4个 9. 组合逻辑电路在电路结构上的特点下列不正确的是( )。 A. 在结构上只能由各种门电路组成 B. 电路中不包含记忆(存储)元件 C. 有输入到输出的通路 D. 有输出到输入的反馈回路 10. 已知74LS138译码器的输入三个使能端(E 1=1,022==B A E E )时,地址码A 2A 1A 0=011,则输 出07~Y Y 为( )。 A. 11111101 B. 10111111 C. 11110111 D. 11111111 三 、简答题(共15分,每题5分)

关于课程设计心得体会范文三篇

---------------------------------------------------------------范文最新推荐------------------------------------------------------ 关于课程设计心得体会范文三篇 篇一:课程设计心得体会600字 (一)通过此次课程设计,使我更加扎实的掌握了有关高频电子线路方面的知识,在设计过程中虽然遇到了一些问题,但经过一次又一次的思考,一遍又一遍的检查终于找出了原因所在,也暴露出了前期我在这方面的知识欠缺和经验不足。实践出真知,通过亲自动手制作,使我们掌握的知识不再是纸上谈兵。过而能改,善莫大焉。在课程设计过程中,我们不断发现错误,不断改正,不断领悟,不断获龋最终的检测调试环节,本身就是在践行”过而能改,善莫大焉”的知行观。这次课程设计终于顺利完成了,在设计中遇到了很多问题,最后在老师的指导下,终于游逆而解。在今后社会的发展和学习实践过程中,一定要不懈努力,不能遇到问题就想到要退缩,一定要不厌其烦的发现问题所在,然后一一进行解决,只有这样,才能成功的做成想做的事,才能在今后的道路上劈荆斩棘,而不是知难而退,那样永远不可能收获成功,收获喜悦,也永远不可能得到社会及他人对你的认可!课程设计诚然是一门专业课,给我很多专业知识以及专业技能上的提升,同时又是一门讲道课,一门辩思课,给了我许多道,给了我很多思,给了我莫大的空间。同时,设计让我感触很深。使我对抽象的理论有了具体的认识。通过这次课程设计,我掌握了常用元件的识别和测试;熟悉了常用仪器、仪表;了解了电路的连线方法;以及 1 / 11

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试 A 卷参考答案 、判断题:下面描述正确的打’/,错误的打‘X’(每小题1分,共10 分) 1、为了表示104个信息,需7位二进制编码[V ] 2、BCD码能表示0至15之间的任意整数[X ] 3、余3码是有权码[X ] 4、2421码是无权码[X ] 5、二值数字逻辑中变量只能取值 6、计算机主机与鼠标是并行通信 7、计算机主机与键盘是串行通信8、占空比等于脉冲宽度除于周期0和1,且表示数的大小[X ] [X ] [V ] [V ] 9、上升时间和下降时间越长,器件速度越慢[V ] 10、卡诺图可用来化简任意个变量的逻辑表达式[X ] 、写出图中电路的逻辑函数表达式。(每小题5分,共10分) 1、F=A B 2、F= AB CD 2分,共20分)

1、在图示电路中.能实现逻辑功能F = ATH 的电路是 A ° TTL 电路 (A) F = ABCD (B) F = AH ? CD - (C) F= A + B + C + D (D) F = A + B ? C + D (E) F= A BCD 4 . 己知F 二ABC + CD ■可以肯定使F = 0的情况是 _° (A) A=0, BC= 1; (B) B= 1 , C= 1 } (C) AB= 1, CD=Q. (D) BC= 1 , D= 1 5、逻辑函数A B+BCD+A C+ B C 可化简为A,B,C,D 。 (A) AB + AC + BC (B) AB + C (A4-B) (C) AB + CAB A — O ? =1 1 Q A |— I 1 F ?- & 1 Q A B L I l — (B) 悬0 ---- 空 。— A — & Bo — Co- & B A 3 ?满足如图所示电路的输岀函数F 的表达式为丄3 B 1 o — V OF

2018~2019数字逻辑设计期末考题

2018~2019 数字逻辑设计期末考题 回忆 by liuxilai && 18~19年选课同学 一、简答题(6×5=30分) 1、非确定组合逻辑优化中的蕴含项、质蕴含项和实质蕴含项 2、简述SR、D、JK、D触发器的功能 3、建立时间(setup time)和保持时间的概念,并说明如何确保同步时序逻辑电路正常的工作 4、请简述摩尔机、米利机和同步米利机的概念,并说明如何将前两者转换为后者 5、状态等价的两个含义 6、状态分配的五个原则 二、组合逻辑(2×10=20分) 1、用卡诺图化简以下函数,画卡诺图,并写出蕴含项与实质蕴含项(SOP) F(A,B,C,D)=m(0,2,8,9,10,14)+d(3,4,5) 2、用QM算法化简以下函数 F(A,B,C,D)=m(0,1,2,5,6,7,8,9,10,14)+d(12) 三、时序逻辑(15×2=20) 1、用163计数器设计从1~24计数的计数器,输入为时钟信号CLK,,使能信号En,输出为进位ECO与h[4:0]。 2、使用蕴含表法化简以下状态表 四、状态机设计(30分) 1(10分)、用verilog语言,设计识别串行同步输入序列为1的同步米利机,初始状态复位时输出为0,当1的个数被3整除时输出为1. 2、(20分)米利机,当输入序列中出现011或101时,输出z0有效,序列可重叠。

1(10分)、给出以下状态图,补充完整(图中状态内的编码与输入序列无关)。 2)使用D触发器与最少的NAND与非门,根据上面的状态分配设计电路 (2分)画出二进制状态表 (8分)触发器激励输入与电路输出的卡诺图化简,并写出化简后的函数。

心得体会 关于安卓课程设计心得体会

关于安卓课程设计心得体会 关于安卓课程设计心得体会如何写?下面是xxx整理的关于安卓课程设计心得体会范文,欢迎借鉴! 关于安卓课程设计心得体会范文一 刚开始接触Android感觉到它很有意思,在界面开发上和web也可以形成了相通的架构,更加方便,视觉上也是非常的酷,在前期我通过的大量的Android SDK开发范例大全中的例子以及Android提供的APIDEMOS进行学习,尽管例子之间的连接比较零散,不过通过这些例子的学习我可以学习到了很多和以前java上相通的思想,因为Android在现在也是全新的技术和框架,在其中我也学到了如何用单例模式、工厂模式等常用的设计模式进行学习,通过API进行开发客户端,对Request发送,Response处理中通过比较方便的JSON对象传输,以及对XML、JSON、图片、业务等下载处理,对API接口调用等问题处理,学习Android心得体会。首先在界面上,我们同样可以通过不同布局进行设计非常酷的界面,这些界面可以通过include进行引入,和jsp、html也有相通的地方,同样在android上可以用到自定义的样式这和css也有比较相通的地方,我们可以通过一些公用的方法写个BaseActivity这个基类,通过继承方式比较不错的实现了Activity的界面,因为这样你可以Header(头部)和Footer(尾部)进行处

理一些触发事件或者特效等,心得体会《学习Android心得体会》。布局模式以相对模式为主,线线布局模式可以在比较简单的include 进行完成,最重要的一点就是:我们可以自己通过重写方法或者通过实现View或者Layout等类进行扩充项目需要的布局(或者控件),在学习界面中,我发现Android为我们提供了很好的类似反射机制,通过Layout文件夹下的配置文件,可以快速的形成界面,在配置文件可以设置属性或者样式都是很快捷方便。对比较特殊的界面也可以通过处理嵌入到指定的界面,同样你可以通过java代码直接创建View进行添加,不过这种方式比较复杂。对一些点击、选中、按键等处理的事件,界面之间的跳转Intent管理,通过Bundle对数据在界面之间进行传输。其次在手机交互式通信服务中,学习了Android手机之间进行短信发送、广播、对广播的监听、服务等,在Service类中没有context,可以通过Handler来每秒反复运行,自动送出系统广播信息,同时在这里我们也知道可以设计一个常用的变量类,设计一个当前的CurrentActivity这个变量进行控制,进行处理。 关于安卓课程设计心得体会范文二 两个星期的时间非常快就过去了,这两个星期不敢说自己有多大的进步,获得了多少知识,但起码是了解了项目开发的部分过程。虽说上过数据库上过管理信息系统等相关的课程,但是没有亲身经历过相关的设计工作细节。这次实习证实提供了一个很好的机会。

数字逻辑精选题

逻辑代数基础 一、选择题 1. 以下表达式中符合逻辑运算法则的是 D 。 A.C ·C =C 2 B.1+1=10 C.0<1 D.A +1=1 2. 逻辑变量的取值1和0可以表示: ABCD 。 A.开关的闭合、断开 B.电位的高、低 C.真与假 D.电流的有、无 3. 当逻辑函数有n 个变量时,共有 D 个变量取值组合? A. n B. 2n C. n 2 D. 2n 4. 逻辑函数的表示方法中具有唯一性的是AD 。 A .真值表 B.表达式 C.逻辑图 D.卡诺图 5.F=A B +BD+CDE+A D= AC 。 A.D B A + B.D B A )(+ C.))((D B D A ++ D.))((D B D A ++ 6.逻辑函数F=)(B A A ⊕⊕ = A 。 A.B B.A C.B A ⊕ D. B A ⊕ 7.求一个逻辑函数F 的对偶式,可将F 中的 ACD 。 A .“·”换成“+”,“+”换成“·” B.原变量换成反变量,反变量换成原变量 C.变量不变 D.常数中“0”换成“1”,“1”换成“0” E.常数不变 8.A+BC= C 。 A .A + B B.A + C C.(A +B )(A +C ) D.B +C 9.在何种输入情况下,“与非”运算的结果是逻辑0。 D A .全部输入是0 B.任一输入是0 C.仅一输入是0 D.全部输入是1 10.在何种输入情况下,“或非”运算的结果是逻辑0。 B C D A .全部输入是0 B.全部输入是1 C.任一输入为0,其他输入为1 D.任一输入为1 二、判断题(正确打√,错误的打×) 1. 逻辑变量的取值,1比0大。( × )。 2. 异或函数与同或函数在逻辑上互为反函数。( √ )。 3.若两个函数具有相同的真值表,则两个逻辑函数必然相等。( × )。

(完整版)数字逻辑期末试卷(B卷)试题及答案

华东师范大学期末试卷(B) 2009 — 2010 学年第 一 学期 课程名称:___数字逻辑________ 学生姓名:___秦宽________________ 学 号:_2013041046__________________ 专 业:____软件工程_______ 年级/班级:13级软件工程 课程性质:公共必修、公共选修、专业必修、专业选修 一、填空题 (20分,每空2分) 1. (2010)D =( )B = ( )H = ( )8421BCD 答案:(111 1101 1010)B = (7DA )H = (0010 0000 0001 0000)8421BCD 2. 仓库门上装了两把暗锁,A 、B 两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。这种逻辑关系为 。 答案:与逻辑 3. 逻辑函数式F=AB+AC 的对偶式为 ,最小项表达式为∑=m F ( )。 答案:))((C A B A F D ++= ∑=m F (5,6,7) 2.逻辑函数D AC CD A C AB D C ABD ABC F ''''''+++++=的最简与或式是 。 答案:'D A + 4. 从结构上看,时序逻辑电路的基本单元是 。 答案:触发器 5. JK 触发器特征方程为 。 答案:Q K JQ ''+ 6.A/D 转换的一般步骤为:取样,保持, ,编码。 答案:量化

二、选择题 (20分,每题2分) 1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。 A) 6 B) 7 C) 8 D) 51 答案:B 2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。 A) 2 B) 4 C) 6 D) 7 答案:D 3. 为实现“线与”逻辑功能,应选用( )。 A) 与非门 B) 与门 C) 集电极开路(OC )门 D) 三态门 答案:C 4. 图1所示逻辑电路为( )。 A) “与非”门 B) “与”门 C)“或”门 D) “或非”门 图1 答案:A 5. 在下列逻辑部件中,属于组合逻辑电路的是( )。 A) 计数器 B) 数据选择器 C) 寄存器 D) 触发器 答案:B 6. 已知某触发器的时钟CP ,异步置0端为R D ,异步置1端为S D ,控制输入端V i 和输出Q 的波形如图2所示,根据波形可判断这个触发器是( )。 B C

课程设计心得体会万能版

最新课程设计心得体会万能版 【最新课程设计心得体会一】 本学期为期一周的嵌入式课程设计在不知不觉中结束了,虽说这次课程设计时光不是很长,但是感觉自我收获颇丰,不仅仅学习到了一些新知识,回顾了以前的一些快要遗忘的知识点,而且使自我的学习目标更加明确,学习方法更加完善,也体会到软件开发的趣味,更加清楚地认识到了自我在软件开发及学习上的一些不足之处。下方就来详细写一下我关于此次课程设计的心得体会: 此次课程设计的实训的是由上海杰普公司的楚老师带我们完成的。楚老师看上去比较年轻,给我们很有亲和力,技术上也很强,而且讲解的比较详细,操作上相当娴熟。让我们感觉到了计算机科学技术学习的趣味性,计算机技术的实用性。此次课程设计给老师选取项目是在Linux下用C语言开发一个摄像头驱动程序。项目的实施方式是团队分组合作,共同完成,让我们体验了一下公司开发项目的氛围。我们一人一机,老师边讲边练,还有企业项目经理的全程指导。虽说一些些技术我们在课堂上也曾学习过,但是大多停留在理论学习上,实际开发很少,而这次课程设计给了我们一个很好的边学习边实践的机会,对我们深入学习这些技术有很大帮忙,深刻体会到了这些技术的实用性。每当自我成功调试一段代码或者透过自我的努力克服一个技术困难,都颇有收获感。这次实训让我们体验了软件开发的全过程,发现自我的不足,了解了当前流行技术的软件开发,增加了必须的项目开发经验,增强了必须的就业竞争力。简短的回顾一下这几天我们所学习的:

实训的前一天下午,我们先明确了一下下周课程设计的要求和目的,跟上海杰普公司的楚老师相互认识了一下。然后楚老师给我们详细的讲解了这一周我们要做什么,并演示了一个他自我开发的摄像头驱动程序。同学们看了,都很感兴趣,如果自我能开发出这样的一个小程序,着实让人高兴。接下来的这几天我们就跟着范老师一齐学习摄像头驱动的开发,同时我们也分了小组,模拟体验一下公司的团队开发,同学们都用心策划自我团队的名字、团队的口号、队歌我们首先从基本的Linux命令学起,以及linux底下的C语言的一些基本知识。虽说这学期我们也学过Linux开发技术,有必须的基础,但这几天的学习,还是感觉到我们学的太浅,很多的东西需要去深入的学习才能有所收获。而且深刻的体会到熟能生巧这句良训,光学不练还是白搭。后两天我们学习了Linux底下一些开发工具的使用,如Qt,感觉这些工具功能确实够强大。当透过自我写的代码能够控制摄像头拍照时,别提有多高兴了。当然在调试的过程中也遇到不少错误,每当透过自我的努力把问题解决(一般自我思考一下,查查资料都没问题),也是一种很好的收获。还有一个比较深刻的体会就是API及一些文档的查阅,这对开发人员来说是一个务必具备的潜力。 此次实训最大的收获不是我学习到了多少知识而是这几天实训给我的感悟:首先是心态。必须要有一个用心的心态,独立解决问题的意识,培养扎实基础的认识。不要什么东西都感觉跟简单(很多东西可能是看似简单)就不去做了或者不屑一做,以至于性网上搜搜就能够了,这样很不好。有自我的东西有自我的付出才会有程序运行成功时的喜悦和小自豪,这样也有助于培养自我的兴趣。要时刻牢记态度决定一切。其次是兴趣,感觉学习工作中兴趣很关键,只是一个引发人用心性的问题,有了兴趣就自觉了,效率自然就高了。再次要敢于尝试和挑战。不

数字逻辑与数字集成电路习题

《数字逻辑》习题案例(计算机科学与技术专业、信息安全专业) 2004年7月 计算机与信息学院、计算机系统结构教研室

一、选择题 1.十进制数33的余3码为 。 A. 00110110 B. 110110 C. 01100110 D. 100100 2.二进制小数-0.0110的补码表示为 。 A .0.1010 B .1.1001 C .1.0110 D .1.1010 3.两输入与非门输出为0时,输入应满足 。 A .两个同时为1 B .两个同时为0 C .两个互为相反 D .两个中至少有一个为0 4.某4变量卡诺图中有9个“0”方格7个“1”方格,则相应的标准与或表达式中共有多少个与项 ? A . 9 B .7 C .16 D .不能确定 5. 下列逻辑函数中,与A F =相等的是 。 )(A 11⊕=A F )(B A F =2⊙1 )(C 13?=A F )(D 04+=A F 6. 设计一个6进制的同步计数器,需要 个触发器。 )(A 3 )(B 4 )(C 5 )(D 6 7. 下列电路中,属于时序逻辑电路的是 。 )(A 编码器 )(B 半加器 )(C 寄存器 )(D 译码器 8. 列电路中,实现逻辑功能n n Q Q =+1的是 。 )(A )(B 9. 的输出端可直接相连,实现线与逻辑功能。 )(A 与非门 )(B 一般TTL 门 )(C 集电极开路OC 门 )(D 一般CMOS 门 10.以下代码中为无权码的为 。 A . 8421BCD 码 B . 5421BCD 码 C . 余三码 D . 格雷码 11.以下代码中为恒权码的为 。 A .8421BCD 码 B . 5421BCD 码 C . 余三码 D . 格雷码 12.一位十六进制数可以用 位二进制数来表示。 A . 1 B . 2 C . 4 D . 16 13.十进制数25用8421BCD 码表示为 。 A .10 101 B .0010 0101 C .100101 D .10101 14.在一个8位的存储单元中,能够存储的最大无符号整数是 。 CP Q CP Q CP Q CP

数字逻辑电路期末考试试卷及答案

期末考试试题(答案) 一、选择题(每小题2分,共20分) 1.八进制(273)8中,它的第三位数2 的位权为___B___。 A.(128)10B.(64)10C.(256)10 D.(8)10 2. 已知逻辑表达式C B C A AB F+ + =,与它功能相等的函数表达式 _____B____。 A.AB F=B.C AB F+ = C.C A AB F+ =D.C B AB F+ = 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A.原码B.ASCII码C.补码D.BCD码4.对于如图所示波形,其反映的逻辑关系是___B_____。 A.与关系B.异或关系C.同或关系D.无法判断 5.连续异或1985个1的结果是____B_____。 A.0B.1 C.不确定D.逻辑概念错误 6. 与逻辑函数D C B A F+ + + =功能相等的表达式为___C_____。 A.D C B A F+ + + =B.D C B A F+ + + = C.D C B A F=D.D C B A F+ + = 7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。 B A F & ? F B A &

8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。 A. 500KHz B.200KHz C. 100KHz D.50KHz 9.下列器件中,属于时序部件的是_____A_____。 A.计数器B.译码器C.加法器D.多路选择器 10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。 A. 0100100 B.1100011 C. 1011011 D.0011011 二、填空题(每小题2分,共20分) 11.TTL电路的电源是__5__V,高电平1对应的电压范围是__2.4-5____V。 12.N 个输入端的二进制译码器,共有___N2____个输出端。对于每一组输入代码,有____1____个输出端是有效电平。 13.给36个字符编码,至少需要____6______位二进制数。 14.存储12位二进制信息需要___12____个触发器。