数据选择器

深圳大学实验报告课程名称:数字电路与逻辑设计实验项目名称:数据选择器

学院:计算机与软件学院专业:软件工程计算机科学与技术指导教师:余航

报告人:杜龙艺余卓燃

学号:2009150093 2009150330 班级:三实验时间:2010-11-18

实验报告提交时间:2010-12-02

教务处制

注:1、报告内的项目或内容设置,可根据实际情况加以调整和补充。

2、教师批改学生实验报告时间应在学生提交实验报告时间后10日内。

2输入数据选择器(mux2)集成电路课设报告

课程设计任务书 学生姓名:助人为乐专业班级:不计得失 指导教师:一定过工作单位:信息工程学院 题目: 二输入数据选择器版图设计 初始条件: 计算机、ORCAD软件、L-EDIT软件 要求完成的主要任务: 1、课程设计工作量:2周 2、技术要求: (1)学习ORCAD软件、L-EDIT软件软件。 (2)设计一个二输入数据选择器电路。 (3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。 3、查阅至少5篇参考文献。按《武汉理工大学课程设计工作规范》要求撰写设计报告书。全文用A4纸打印,图纸应符合绘图规范。 时间安排: 2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。 2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。 2013.11.28-12.5对二输入数据选择器电路进行设计仿真工作,完成课设报告的撰写。 2013.12.6提交课程设计报告,进行答辩。 指导教师签名:年月日 系主任(或责任教师)签名:年月日

目录 1.绪论 (2) 2.软件简介 (3) 2.1Cadence简介 (3) 2.2L-edit简介 (3) 3.二输入多路选择器电路设计及仿真 (4) 3.1数据选择器原理 (4) 3.2电路原理图的绘制 (5) 3.3电路图仿真 (6) 4.集成电路版图设计 (7) 4.1CMOS数字电路基本单元版图设计 (7) 4.1.1反相器版图设计 (7) 4.1.2与非门版图设计 (8) 4.2整体版图设计 (9) 4.3设计规则的验证及结果 (9) 5.总结 (10) 参考文献 (11)

实验3-组合逻辑电路数据选择器实验

南通大学计算机科学与技术学院计算机数字逻辑设计 实验报告书 实验名组合逻辑电路数据选择器实验 班级_____计嵌151_______________ 姓名_____张耀_____________________ 指导教师顾晖 日期 2016-11-03

目录 实验一组合逻辑电路数据选择器实验 (1) 1.实验目的 (1) 2.实验用器件和仪表 (1) 3.实验内容 (1) 4.电路原理图 (1) 5.实验过程及数据记录 (2) 6.实验数据分析与小结 (9) 7.实验心得体会 (9)

实验三组合逻辑电路数据选择器实验 1 实验目的 1. 熟悉集成数据选择器的逻辑功能及测试方法。 2. 学会用集成数据选择器进行逻辑设计。 2 实验用器件和仪表 1、8 选 1 数据选择器 74HC251 1 片 3 实验内容 1、基本组合逻辑电路的搭建与测量 2、数据选择器的使用 3、利用两个 74HC251 芯片(或 74HC151 芯片)和其他辅助元件,设计搭建 16 路选 1 的电路。 4 电路原理图 1、基本组合逻辑电路的搭建与测量 2、数据选择器的使用

3、利用两个 74HC251 芯片(或 74HC151 芯片)和其他辅助元件,设计搭建 16 路选 1 的 电路。 5 实验过程及数据记录 1、基本组合逻辑电路的搭建与测量 用 2 片 74LS00 组成图 3.1 所示逻辑电路。为便于接线和检查,在图中要注明芯片编号及各引脚对应的编号。

图 3.1 组合逻辑电路 (2)先按图 3.1 写出 Y1、Y2 的逻辑表达式并化简。 Y1==A·B ·A =A + A·B=A + B Y2=B·C ·B·A = A · B+ B ·C (3)图中 A、B、C 接逻辑开关,Y1,Y2 接发光管或逻辑终端电平显示。(4)改变 A、B、C 输入的状态,观测并填表写出 Y1,Y2 的输出状态。 表 3.1 组合电路记录

八选一数据选择器

1.4’b1001<<2=(6‘b100100),4’b1001>>2=(4’b0010 )。 2、完整的条件语句将产生(组合逻辑电路)电路,不完整的条件语句将产生(时序逻辑电路)电路。 3、用EDA技术进行电子系统设计的目标是最终完成(专用集成电路ASIC)的设计。 4、可编程器件分为(现场可编程列阵FPGA)和(复杂可编程逻辑器件 PLD) 5、系统函数和任务函数的首字符标志为($),预编译指令首字符标志为(#)。 6、一个基本的Verilog-HDL程序由(Verilog-HDL )模块构成。 7、EDA技术在应用设计领域主要包含哪四个方面的内容(HDL)、(PLD )、( EDA工具软件)、(EDA开发系统) 8、EDA技术的基本特征主要有哪5个方面:(自顶向下的设计方法)、(采用硬件描述语言)、(高层综合和优化).(并行工程)、(开放性和标准化) 9、当前最流行的并成为IEEE标准的硬件描语言是( VHDI )和( Verilog-HDL) 10、一个完整的Verilog-HDL设计模块包括:(模块关键字和模块名)、(端口列表)、(端口定义)、(功能描述)这4部分。 11Verilog-HDL模块的I/O端口声明用来声明模块端口定义中各端口数据流动方向,包括(输入端口)、(输出端口)、和(双向端口) 12、Verilog-HDL语言的三种常用的模型描述方法为(行为描述)、(数据描述)和(结构描述) 13、Verilog-HDL的数值集合由哪四种基本的值组成( 0)、(1 )、 x)、( z ) 14、10’hxf=( 10’xxxxxx1111 ) 10’hzf=( 10’zzzzzz1111 ) 15、若a=5’b10x01,b=5’b10x01,则a= =b的结果为( X )、a= = =b的结果为( 1 ) 16、Wire[15:0] wire-b表示连线宽度为(16 )位,其最高位为(15),最低位为(0)。 17、若A=5’b11011,B=5’b10101,则有&A=(0)|B=(1) ~A=(5’b00100)A&B(5’b10001) 18、若A=8’b1000_0100则A<<3的结果为(11’b10000100000)A>>3的结果为(8’b00010000) 19、对于Verilog-HDL语言中的关键字,在建模时都必须(小)写。 20、if(a) out1<=int1; else out1<=int2;当a= (1)执行out1<=int1 ;当a=(0)执行out1<=int2 二、选择题: 21、在verilog语言中整型数据与( C )位寄存器数据在实际意义上是相同的。 A、8 B、16 C、32 D、64 22、大规模可编程器件主要有FPGA、CPLD两类,下列对FPGA结构与工作原理的描述中,正确的是( C )。 A.FPGA全称为复杂可编程逻辑器件; B.FPGA是基于乘积项结构的可编程逻辑器件; C.基于SRAM的FPGA器件,在每次上电后必须进行一次配置; D.在Altera公司生产的器件中,MAX7000系列属FPGA结构。 23. 子系统设计优化,主要考虑提高资源利用率减少功耗(即面积优化),以及提高运行速度(即速度优化);指出下列哪些方法是面积优化( B )。 ①流水线设计②资源共享③逻辑优化④串行化 ⑤寄存器配平⑥关键路径法 A.①③⑤B.②③④C.②⑤⑥D.①④⑥ 24、下列标识符中,(A)是不合法的标识符。 A、9moon B、State0 C、Not_Ack_0 D、signall 25、下列语句中,不属于并行语句的是:(D ) A、过程语句 B、assign语句 C、元件例化语句 D、case语句 26、在verilog中,下列语句哪个不是分支语句?( D ) A.if-else B、case C、casez D、repeat 27、下列标示符哪些是合法的( B ) A、$time B、_date C、8sum D、mux# 28、如果线网类型变量说明后未赋值,起缺省值是( D ) A、x B、1 C、0 D、z 29、现网中的值被解释为无符号数。在连续赋值语句中,assign addr[3:0]=-3;addr被赋予的值是(A )

数字电路实验报告——数据选择器

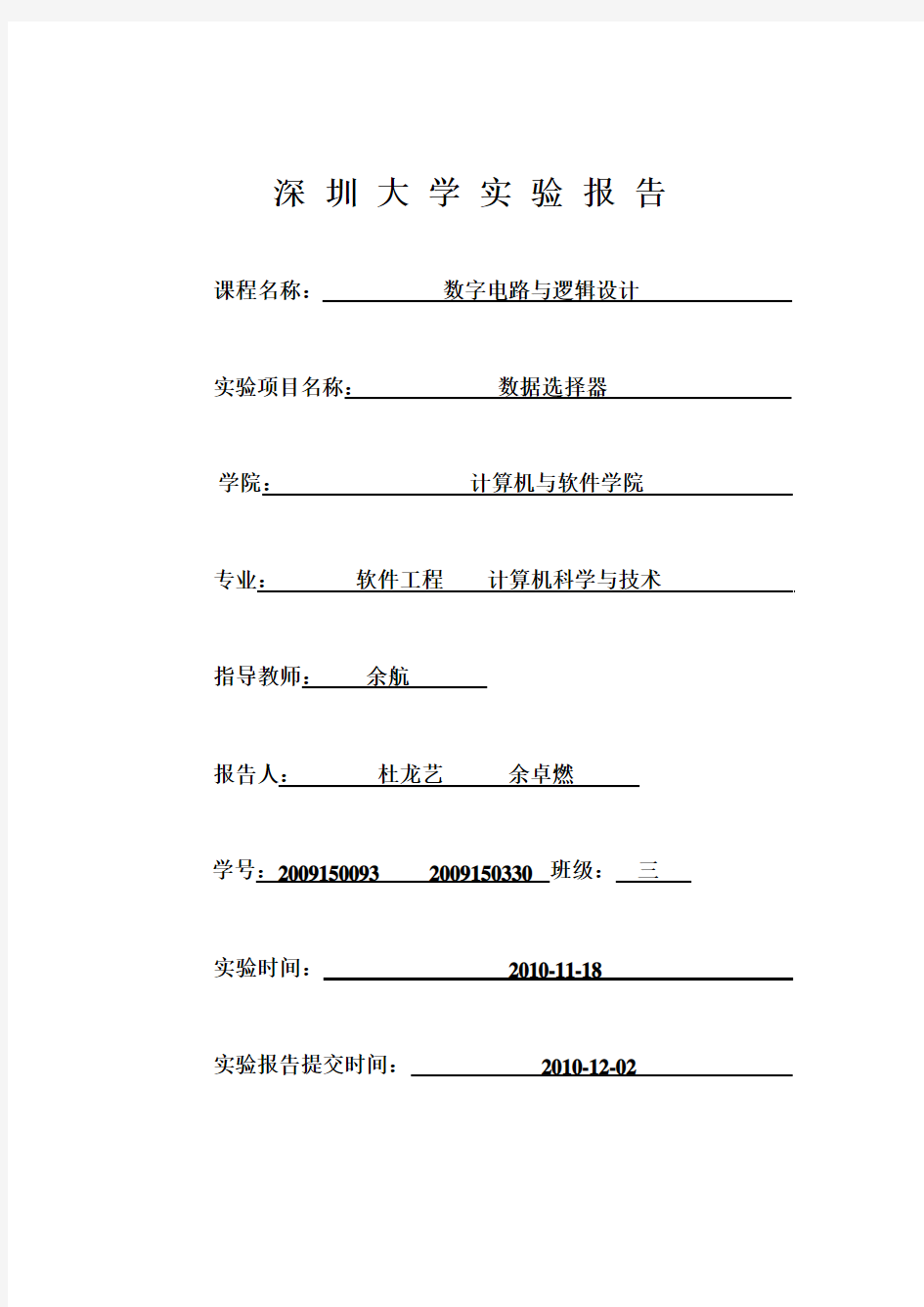

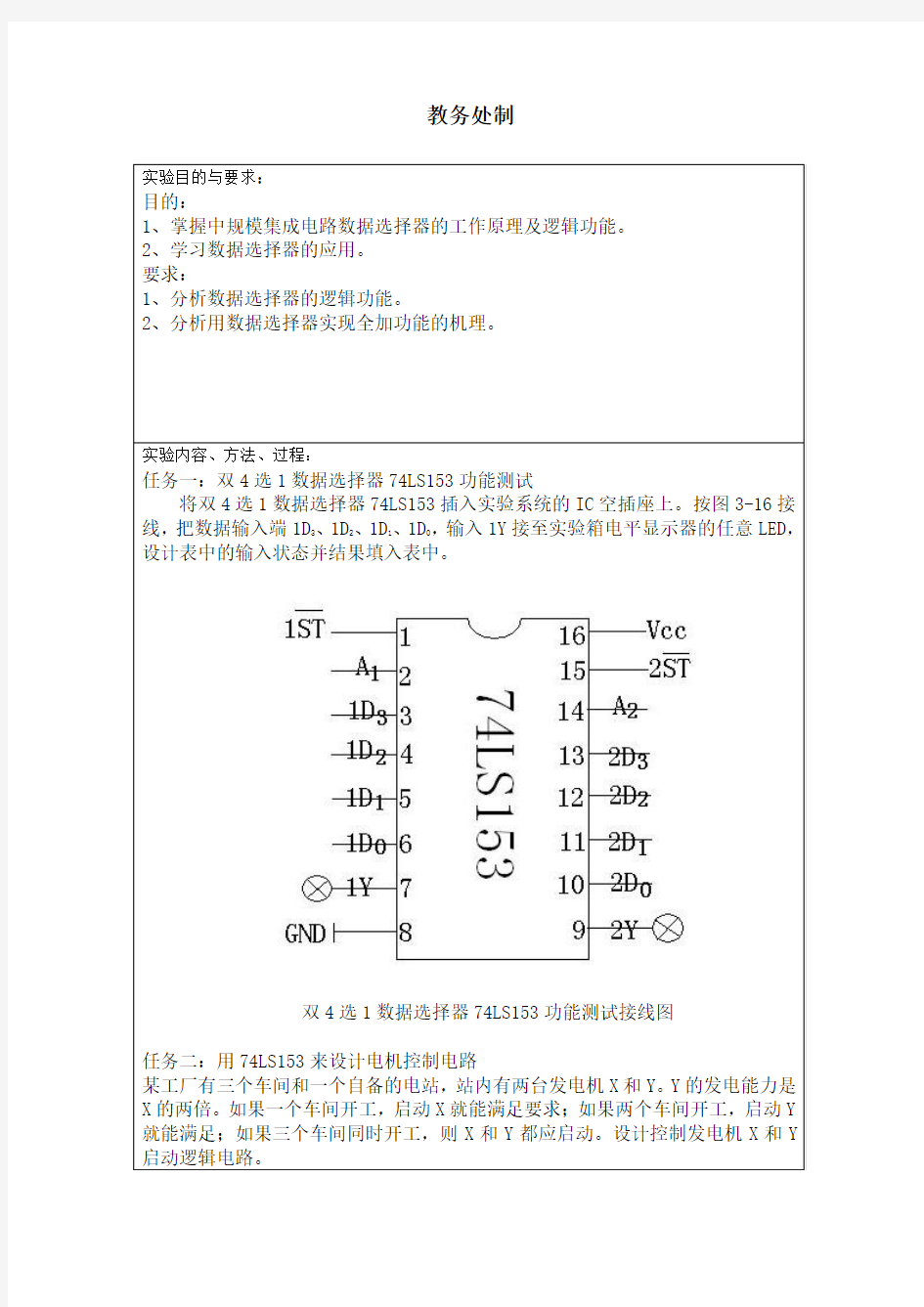

第八次实验报告 实验六 数据选择器 一、实验目的要求 1、 熟悉中规模集成电路数据选择器的工作原理与逻辑功能 2、 掌握数据选择器的应用 二、实验仪器、设备 直流稳压电源、电子电路调试器、T4153、CC4011 三、实验线路、原理框图 (一)数据选择器的基本原理 数据选择器是常用的组合逻辑部件之一,它有若干个输入端,若干个控制输入端及一个输出端。 数据选择器的地址变量一般的选择方式是: (1) 选用逻辑表达式各乘积项中出现次数最多的变量(包括原变量与反变量),以简 化数据输入端的附加电路。 (2) 选择一组具有一定物理意义的量。 (二)T4153的逻辑符号、逻辑功能及管脚排列图 (1)T4153是一个双4选1数据选择器,其逻辑符号如图1: 图1 (2) T4153的功能表如下表 其中D0、D1、D2、D3为4个数据输入端;Y 为输出端;S 是使能端,在S 是使能端,在 原SJ 符号

S =0时使能,在S =1时Y=0;A1、A0是器件中两个选择器公用的地址输入端。该器件的 逻辑表达式为: Y=S (1A 0A 0D +101D A A +201D A A +301A A A ) (3) T4153的管脚排列图如图2 图2 (三)利用T4153四选一数据选择器设计一个一位二进制全减器的实验原理和实验线路 (1)一位二进制全减器的逻辑功能表见下表: n D =n A n B 1-n C +n A n B 1-n C +n A n B 1-n C +n A n B 1-n C n C =n A n B 1-n C +n A n B 1-n C +n A n B 1-n C +n A n B 1-n C =n A n B 1-n C +n A n B +n A n B 1-n C (3)根据全减器的逻辑功能表设计出的实验线路图为图3: S 11D 3 1D 2 1D 1 1D 0 1Y

实验三 数据选择器及其应用

实验三数据选择器及其应用 一、实验目的 1.掌握数据选择器的逻辑功能和使用方法。 2.学习用数据选择器构成组合逻辑电路的方法。 二、实验原理 数据选择是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去。实现数据选择功能的逻辑电路称为数据选择器。它的功能相当于一个多个输入的单刀多掷开关,其示意图如下: 图9-1 4选1数据选择器示意图 图中有四路数据D0~D3,通过选择控制信号A1、A0(地址码)从四路数据中选中一路数据送至输出端Q。 1.八选一数据选择器74LS151 74LS151是一种典型的集成电路数据选择器,它有3个地址输入端CBA,可选择I0~I78个数据源,具有两个互补输入端,同相输出端Z和反相输出端Z。其引脚图和功能表分别如下: 2.双四选一数据选择器74LS153

所谓双四选一数据选择器就是在一块集成芯片上有两个完全独立的4选1数据选择器,每个数据选择器有4个数据输入端I0~I3,2个地址输入端S0、S1,1个使能控制端E和一 个输出端Z,它们的功能表如表9-2,引脚逻辑图如图9-3所示。 图9-3 74LS153引脚逻辑图表9-2 74LS153的真值表 其中,EA、EB(1、15脚)分别为A路和B路的选通信号,I0、I1、I2、I3为四个 数据输入端,ZA(7脚)、ZB(9脚)分别为两路的输出端。S0(14脚)、S1(2脚)为地址信号,8脚为GND,16脚为VCC。 3.用74LS151组成16选1数据选择器 用低三位A2A1A0作每片74LS151的片内地址码, 用高位A3作两片74LS151的片选信号。当A3=0时,选中74LS151(1)工作, 74LS151(2)禁止;当A3=1时,选中74LS151(2)工作, 74LS151(1)禁止,如下图所示。 图9-4用74LS151组成16选1数据选择器

译码器和数据选择器

实验四译码器及其应用 一、实验目的 1.掌握中规模集成译码器的逻辑功能和使用方法 2.熟悉数码管的使用 二、实验原理 译码器是一个多输入、多输出的组合逻辑电路。它的作用是把给定的代码进行“翻译”,变成相应的状态,使输出通道中相应的一路有信号输出。译码器可分为通用译码器和显示译码器两类。前者又分为变量译码器和代码变换译码器。 1.变量译码器(又称二进制译码器),用以表示输入变量的状态,如2线-4线、3线-8线和4线-16线译码器。若有n个输入变量,则有2n个不同的组合状态,就有2n个输出端供其使用。而每一个输出所代表的函数对应于n个输入变量的最小项。 以3线-8线译码器74LS138为例进行分析,图4-1(a)、(b)分别为其 逻辑图及引脚排列。其中A2、A1、A0为地址输入端,0Y~7Y为译码输出端,S1、2S、3S 为使能端。 (a) (b) 图4-1 3-8线译码器74LS138逻辑图及引脚排列 表4-1为74LS138功能表 当S1=1,2S+3S=0时,器件使能,地址码所指定的输出端有信号(为0)输出,其 它所有输出端均无信号(全为1)输出。当S1=0,2S+3S=X时,或S1=X,2S+3S=1时,译码器被禁止,所有输出同时为1。 表4-1

二进制译码器实际上也是负脉冲输出的脉冲分配器。若利用使能端中的一个输入端输入数据信息,器件就成为一个数据分配器(又称多路分配器),如图4-2所示。若在S 1输入端输入数据信息,2S =3S =0,地址码所对应的输出是S 1数据信息的反码;若从2S 端输入数据信息,令S1=1、3S =0,地址码所对应的输出就是2S 端数据信息的原码。若数据信息是时钟脉冲,则数据分配器便成为时钟脉冲分配器。 根据输入地址的不同组合译出唯一地址,故可用作地址译码器。接成多路分配器,可将一个信号源的数据信息传输到不同的地点。 二进制译码器还能方便地实现逻辑函数,如图4-3所示,实现的逻辑函数是 Z =C B A C B A C B A +++ABC 图4-2 作数据分配器 图4-3 实现逻辑函数

数字电路实验二

实验2 数据选择器功能测试及设计应用 王玉通信工程 2012117266 一、实验目的 1.掌握中规模集成数据选择器的逻辑功能及测试方法。 2.掌握数据选择器的工作原理及使用方法。 二、实验仪器设备与主要器件 试验箱一个;双踪示波器一台;稳压电源一台。 双4选1数据选择器74LS153;8选1数据选择器74LS151和75LS251. 三、实验原理 能够实现从多路数据中选择一路进行传输的电路叫做数据选择器。数据选择器又称多路选择器,是中规模集成电路中应用非常广泛的组合逻辑部件之一。它是一种与分配器过程相反的器件。它有若干个数据输入端,D0,D1,D2,……,若干个控制输入端A0,A1……和一个或两个输出端Q(或Q非)。当控制输入码A0,A1……具有不同数据组合时,将选择组合码所对应的二进制数Dx输出。由于控制输入端的作用是选择数据输入端的地址,故又称为地址码输入端。 目前常用的数据选择器有2选1、4选1、8选1等多种类型。本实验主要熟悉4选1和8选1数据选择器。 四、实验内容与结果 1.测试74LS153的逻辑功能。 电路如下图: 测试结果为: A0 A1 s1s2Q1 Q2 * * 1 1 0 0 0 0 0 0 1D0 2D0 0 1 0 0 1D1 2D1 1 0 0 0 1D 2 2D2 1 1 0 0 1D3 2D3 2.用多路选择器设计实现一个8421-CD非法码检测电路。使得当输入端为非法码组合时输出1,否则为0.二进制数与BCD码的对应关系如下。写出函数Y的表达式,并进行化简,然后画出电路图,接线调试电路,用发光二极管显示输出结果,观察是否与表2-2-5相符。设

数据选择器及其应用

数据选择器及其应用

物联网工程 郭港国 26 一、实验目的 1、掌握中规模集成数据选择器的逻辑功能及使用方法 2、学习用数据选择器构成组合逻辑电路的方法 二、实验原理 数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择 器的功能类似一个多掷开关,有四路数据D 0~D 3 ,通过选择控制信号 A 1 、A (地 址码)从四路数据中选中某一路数据送至输出端Q。 1、双四选一数据选择器 74LS153 所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。引脚排列如图4-1,功能如表4-1。 表4-1

图4-1 74LS153引脚功能 S1、S2为两个独立的使能端;A1、A0为公用的地址输入端;1D0~1D3和2D0~ 2D 3分别为两个4选1数据选择器的数据输入端;Q 1 、Q 2 为两个输出端。 1)当使能端S1(S2)=1时,多路开关被禁止,无输出,Q=0。 2)当使能端S1(S2)=0时,多路开关正常工作,根据地址码A 1、A 的状态, 将相应的数据D 0~D 3 送到输出端Q。 如:A 1A =00 则选择D O 数据到输出端,即Q=D 。 A 1A =01 则选择D 1 数据到输出端,即Q=D 1 ,其余类推。 数据选择器的用途很多,例如多通道传输,数码比较,并行码变串行码,以及实现逻辑函数等。 2、数据选择器的应用—实现逻辑函数 例:用4选1数据选择器74LS153实现函数:ABC C AB C B A BC A F+ + + = 函数F的功能如表(4-2)所示 表4-2 表4-3

实验二 数据选择器及其应用

实验二数据选择器及其应用 一、实验原理 数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择器的功能类似一个多掷开关,如图4-1所示,图中有四路数据D0~D3,通过选择控制信号A1、A0(地址码)从四路数据中选中某一路数据送至输出端Q。 图4-1 4选1数据选择器示意图图4-2 74LS151引脚排列 数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别。 数据选择器的电路结构一般由与或门阵列组成,也有用传输门开关和门电路混合而成的。

二、实验目的 1、掌握中规模集成数据选择器的逻辑功能及使用方法; 2、学习用数据选择器构成组合逻辑电路的方法。 三、实验设备与器件 1、+5V直流电源 2、逻辑电平开关 3、逻辑电平显示器 4、74LS151(或CC4512) 74LS153(或CC4539) 四、实验内容 1、测试数据选择器74LS151的逻辑功能。 接图4-7接线,地址端A2、A1、A0、数据端D0~D7、使能端S接逻辑开关,输出端Q接逻辑电平显示器,按74LS151功能表逐项进行测试,记录测试结果。 图4-7 74LS151逻辑功能测试

2、测试74LS153的逻辑功能。 测试方法及步骤同上,记录之。 逻辑功能见下表: 3、用8选1数据选择器74LS151设计三输入多数表决电路。 1)写出设计过程 有三个人进行表决,当其中任意两个人赞同时,输出为真,否则输出为假。真值表如下:

八选一数据选择器实验报告——孙小喃

学生实验报告 实验课名称:VHDL硬件描述语言 实验项目名称:八选一数据选择器 专业名称:电子科学与技术 班级:32050801 学号:05 学生姓名:孙小喃 教师姓名:程鸿亮 2010年11月06日

组别第三组同组同学钞田田 实验日期2010年11月06日实验室名称______________成绩_____ 一.实验名称 八选一数据选择器 二.实验目的与要求 目的: 设计一个8选1的数据选择器,初步掌握QuartusII软件的使用方法以及硬件编程下载的基本技能。 要求: 通过VHDL编程,实现一个数据选择器,要求有8位数据输入端,1位数据输出端,通过3位地址输入信号寻址,并具有输出使能功能。首先在QuartusII上进行功能和时序仿真,之后通过器件及其端口配置下载程序到SOPC开发平台中。 三.实验内容 1、打开QuartusII软件,建立一个新的工程: 1)单击菜单File\New Project Wizard… 2)输入工程的路径、工程名以及顶层实体名。 3)单击Next>按钮,进入下一个界面。由于我们建立的是一个空的项目,所以没有包含已有文件,单击Next>继续。 4) 设置我们的器件信息:设置为cyclone∏,选择FBGA,484,8,在available devices中选择EP2C35F484C8 33216 483840 70 4, 然后单击Next>,指定第三方工具。这里我们不指定第三方EDA工具,单击Next>后结束工程建立。 2、建立VHDL文件: 1) 单击File\New菜单项,选择弹出窗口中的VHDL File项,单击OK按钮以建立打开空的VHDL文件,注意此文件并没有在硬盘中保存。 2) 在编辑窗口中输入VHDL源文件并保存,注意实体名、文件名必须和建立工程时所设定的顶层实体名相同。 3) 编译工程 单击Processing\Start Compilation开始编译,编译过程中可能会显示若干出错消息,参考提示原因对程序进行修改直到编译完全成功为止。 3. 建立矢量波形文件 1) 单击File\New命令,在弹出的对话框中选择Other Files页面中的Vector Waveform File 项,打开矢量波形文件编辑窗口。 2) 双击窗口左边空白区域,打开Insert Node or Bus对话框。 3) 单击Node Finder…按钮,打开以下对话框,选择Filter下拉列表中的Pins:all,并点击List列出所有的端口,通过>>按钮把这些端口加入到右面的窗口中,单击OK完成端口的添加。 4) 回到波形编辑窗口,对所有输入端口设置输入波形,具体可以通 过左边的工具栏,或通过对信号单击鼠标右键的弹出式菜单中完成操 作,最后保存次波形文件。

实验三译码器及其应用、数据选择器及其应用

实验三译码器及其应用、数据选择器及其应用 一、实验目的 1 ?掌握采用中规模集成器件进行组合逻辑电路设计、电路连接及测试的方法. 2 ?用实验验证所设计电路的逻辑功能. 二、实验设备与器件 1.电子学实验装置 2.集成块74LS20、74LS00、74LS138、74LS151、74LS153。 三、实验原理 中规模集成器件多数是专用的功能器件,具有某种特定的逻辑功能,采用这些功能器件实现组合逻辑函数,基本 方法是采用逻辑函数对比法. 中规模集成器件多数都带有控制端(片选端),例如译码器74LS138有三个附加控制端S B、S C和S A,当S A=1、 S B= S C =0时,译码器才被选通工作,否则,译码器被禁止,所有的输出端被封锁在高电平?利用片选可将多片连接 起来以扩展译码器的功能. 在一般情况下,使用译码器和附加的门电路实现多输出逻辑函数较方便,使用数据选择器实现单输出逻辑函数较方便,当逻辑函数输出为输入变量相加时,则采用全加器实现较为方便. 1 ?译码器 一个n变量的译码器的输出包含了n变量的所有最小项.例如3线/8线译码器(74LS138)的8个输出包含了3个变 量的全部最小项的译码?参见模拟电子技术基础教材中3线/8线译码器功能表. 用n变量译码器加上输出与非门电路,就能获得任何形式的输入变量不大于n的组合逻辑电路. 2 ?数据选择器 一个n个地址端的数据选择器, 具有2n个数据选择的功能.例如,数据选择器74LS151, n=3,可完成八选一的功能?参见附录中八选一数据选择器(74LS151)的真值表.由真值表可写出: 丫A2AA0D0 A2AA0D1A 2 Al A o D 2 A? A1A0D 3 A2A A0D 4 A2A A0D 5 A2 A A) A2AA0D7 数据选择器又称多路开关,其功能是把多路并行传输数据选通一路送到输出线上. 四、实验内容 1 ?三输入变量译码器功能测试 地址输入端AA1A0是一组三位二进制代码,其中A权最高,A o权最低,按实验电路图3-1接线,将实验结果填入

实验二 数据选择器

实验二数据选择器 院系:信息科学与技术学院 专业:电子信息工程 姓名:刘晓旭 学号:2011117147

一.实验目的 1.掌握中规模集成数据选择器的逻辑功能及测试方法。 2.学习数据选择器的使用方法。 二.实验仪器及器材 稳压电源,数字多用表,四选一数据选择器74LS153,八选一数据选择器74LS151。 三 .实验原理 数据选择器又称多路选择器,是中规模集成电路中应用非常广泛的组合逻辑部件之一。它有若干个数据输入端D0 ,D1......,若干个控制输入端A0 ,A1 ......和一个两个输出Q,Q’。当A0,A1......数据不同时,将选择与其相应的输入控制端D X输出,由于控制输入端的作用是选择数据输入端的地址,故又称为地址输入端。 四.实验内容 1.利用逻辑电平产生电路和逻辑电平指示电路测试74LS153的逻辑功能,验证是否和功能表一致。 实验目的:利用逻辑电平产生电路和逻辑电平指示电路测试74LS153的逻辑功能,验证是否和功能表一致。 实验器材:直流电压源,开关,74LS153,电灯,逻辑控制开关 实验内容:测试74LS153的逻辑功能 74LS153为两个四选一数据选择器,S1’,S2’是每一个选择器的选通输入端,低电平有效。 A0,A1为公共的控制输入信号。1D0,1D1....1D3,2D0,2D1...2D3分别是每一选择器的数据输入端。 电路如图1 图1

74LS153的逻辑功能表2.1 注:测试过程中1G,2G 始终接地。当A,B 为00.01,10,11不同情况时,分别对应于1C 0, 2C 0; 1C 1,, 2C 1; 1C 2, 2C 2; 1C 3, 2C 3;的开关接上高电平,灯泡会发光,从真值表所列的功能来看,74LS153符合其逻辑功能。 2.设计一位二进制数A 和B 的比较器。 实验目的:用74LS153设计出一位二进制数A 和B 的比较器。 实验器材:74LS153,单刀双掷开关,直流电源,灯泡。 实验内容:当接至高电平时代表1,接至低电平时代表0; A>B 时,x1亮;AB I ,则地址码为 01,根据电路图看出Y 1Y 2=10;若A I 多路数据选择器

基于FPGA的多路数据采集器的设计 李庭武李本印 (陇东学院电气工程学院,甘肃庆阳745000) 摘要:数据采集是从一个或多个信号获取对象的过程,它是计算机与外部物理世界连接的桥梁,尤其在恶劣的数据采集环境中得到广泛应用。本课题主要研究利用FPGA把采集到的八路模拟信号电压分别转换成数字信号,在数码管上实时显示电压值,并且与计算机运行的软件示波器连接,实现电压数据的发送和接收功能。 关键词:FPGA;模数转换;数码显示管;键盘;设计 Design of multi-channel data terminal Based on FPGA Li Tingwu Li Benyin (Electrical Engineering College, Longdong University, Qingyang 745000, Gansu, China) Abstract: Data acquisition is a process that access to the object from the one or more signal, it is the bridge between the computer and the external physical world, and especially widely applied in data acquisition in harsh environment . This essay mainly studies on the usage of FPGA to collect the eight analog signals that are converted to digital voltage signal, digital tube display real-time voltage value. Connecting with the computer running software oscilloscope so that to realize the voltage data sending and receiving function. Keywords: FPGA; analog-to-digital converting chip; digital display tube; keyboard; design

实验三译码器及其应用、数据选择器及其应用

实验三 译码器及其应用、数据选择器及其应用 一、实验目的 1.掌握采用中规模集成器件进行组合逻辑电路设计、电路连接及测试的方法. 2.用实验验证所设计电路的逻辑功能. 二、实验设备与器件 1.电子学实验装置 2.集成块74LS20、74LS00、74LS138、74LS151、74LS153。 三、实验原理 中规模集成器件多数是专用的功能器件,具有某种特定的逻辑功能,采用这些功能器件实现组合逻辑函数,基本方法是采用逻辑函数对比法. 中规模集成器件多数都带有控制端(片选端),例如译码器74LS138有三个附加控制端B S 、C S 和A S ,当A S =1、 B S = C S =0时,译码器才被选通工作,否则,译码器被禁止,所有的输出端被封锁在高电平.利用片选可将多片连接 起来以扩展译码器的功能. 在一般情况下,使用译码器和附加的门电路实现多输出逻辑函数较方便,使用数据选择器实现单输出逻辑函数较方便,当逻辑函数输出为输入变量相加时,则采用全加器实现较为方便. 1.译码器 一个n 变量的译码器的输出包含了n 变量的所有最小项.例如3线/8线译码器(74LS138)的8个输出包含了3个变量的全部最小项的译码.参见模拟电子技术基础教材中3线/8线译码器功能表. 用n 变量译码器加上输出与非门电路,就能获得任何形式的输入变量不大于n 的组合逻辑电路. 2.数据选择器 一个n 个地址端的数据选择器,具有2n 个数据选择的功能.例如,数据选择器74LS151,n=3,可完成八选一的功能.参见附录中八选一数据选择器(74LS151)的真值表.由真值表可写出: 21002101210221032104210521062107Y A A A D A A A D A A A D A A A D A A A D A A A D A A A D A A A D =+++++++ 数据选择器又称多路开关,其功能是把多路并行传输数据选通一路送到输出线上. 四、实验内容 1.三输入变量译码器功能测试 地址输入端A 2A 1A 0是一组三位二进制代码,其中A 2权最高,A 0权最低,按实验电路图3-1接线,将实验结果填入功能表3-1中.

实验二数据选择器

实验二数据选择器功能测试及设计应用 实验目的 1、掌握中规模集成数据选择器的逻辑功能及测试方法。 2、掌握数据选择器的使用方法。 一、实验仪器及器材 稳压电源、实验箱一个、双四选数据选择器74LS153、八选一数据选择器74LS151。 二、实验原理 1、4选1数据选择器 中规模集成电路74LS153为双四选数据选择器,其逻辑符号如图2-2-1所示,其中,1S、S分别为两个数据选择器的选通输入端,低电平有效。A0,、A1为公告控制输入端地址端,2 1D0、1D1、1D2、1D3与2D0、2D1、2D2、2D3分别为两个数据选择器的数据输入端,其功能表如表2-2-1所示。 有功能表得逻辑表达式: () =+++ Q A A D A A D A A D A A D S 110101011101210131 () =+++ 210201021102210232 Q A A D A A D A A D A A D S 2、8选1数据选择器74LS151 74LS151是常用的8选1数据选择器,用于各种数字电路和单片机系统的显示电路中。其功能如表2-2-2所示。 表2-2-2 74LS151的功能表

其中,S 为数据选择器的选通端,低电平有效。A0、A1、A2为地址码,D0~D7为数据输入端。 3、数据选择器的应用 (1)多路信号共用一个通道(总线)传输。 (2)变并行码为串行码。 (3)转换4位二进制码为补码。 (4)组成数码比较电路。 (5)实现逻辑函数。 三、实验内容 1,利用逻辑电平产生电路和逻辑电平指示电路测试74LS153的逻辑功能,验证是否和逻辑功能表一致。 1、根据题目可画出电路图为:

实验2 数据选择器功能测试及设计应用

实验2 数据选择器功能测试及设计应用专业:通信工程学号:2012119032 姓名:余海东 2.21 实验目的 1.掌握中规模集成数据选择器的逻辑功能及测试方法。 2.掌握数据选择器的工作原理及使用方法。 2.2.2 实验仪器设备与主要器件 试验箱一个;双踪示波器一台;稳压电源一台。 双4选1数据选择器74LS153;8选1数据选择器74LS151和75LS251. 2.2.3 实验原理 能够实现从多路数据中选择一路进行传输的电路叫做数据选择器。数据选择器又称多路选择器,是中规模集成电路中应用非常广泛的组合逻辑部件之一。它是一种与分配器过程相反的器件。它有若干个数据输入端,D0,D1,D2,……,若干个控制输入端A0,A1……和一个或两个输出端Q(或Q非)。当控制输入码A0,A1……具有不同数据组合时,将选择组合码所对应的二进制数Dx输出。由于控制输入端的作用是选择数据输入端的地址,故又称为地址码输入端。 目前常用的数据选择器有2选1、4选1、8选1等多种类型。本实验主要熟悉4选1和8选1数据选择器。下面分别介绍它们的逻辑功能。 2.24 实验内容 1.测试74LS153的逻辑功能,验证是否和表2-2-1的功能一致。 仿真图:

2.用多路选择器设计实现一个8421-CD非法码检测电路。使得当输入端为非法码组合时输出1,否则为0.二进制数与BCD码的对应关系如下。写出函数Y的表达式,并进行化简,然后画出电路图,接线调试电路,用发光二极管显示输出结果,观察是否与表2-2-5相符。设Y=0表示发光二极管熄灭,Y=1表示发光二极管点亮。 二进制数与BCD码的对应关系 二进制B BCD码 B3 B2 B1 B0 Q3 Q2 Q1 Q0 Y 0 0 0 0 0 0 0 0 0 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 1 0 0 0 0 1 1 0 0 1 1 0 0 1 0 0 0 1 0 0 0 0 1 0 1 0 1 0 1 0 0 1 1 0 0 1 1 0 0 0 1 1 1 0 1 1 1 0 1 0 0 0 1 0 0 0 0 1 0 0 1 1 0 0 1 0 1 0 1 0 0 0 0 0 1 1 0 1 1 0 0 0 1 1 1 1 0 0 0 0 1 0 1 1 1 0 1 0 0 1 1 1 1 1 1 0 0 1 0 0 1 1 1 1 1 0 1 0 1 1 表达式: Y=B3(B2B1B0+B2B1B0ˊ+ B2B1ˊB0+ B2B1ˊB0ˊ+ B2ˊB1ˊB0ˊ+ B2ˊB1B0ˊ)由题示真值表化简得Y=B3B2+B3B1 将74LS151的三个地址输入端A、B、C接B1、B2 、B3,将输入D5、D6、D7接1,其他都接0. 仿真图:

八选一数据选择器

《集成电路设计实践》报告 题目:8选1数据选择器 院系:自动化学院电子工程系 专业班级:微电 学生学号: 学生姓名: 指导教师姓名:职称:讲师 起止时间:2015-12-21——2016-1-9 成绩: 设计任务 1) 依据8选1数据选择器的真值表,给出八选一MUX电路图,完成由电路图到晶体管级的转化(需提出至少2种方案); 2) 绘制原理图(Sedit),完成电路特性模拟(Tspice,瞬态特性),给出电路最大延时时间; 3) 遵循设计规则完成晶体管级电路图的版图,流程如下:版图布局规划-基本单元绘制-功能块的绘制-布线规划-总体版图); 4) 版图检查与验证(DRC检查);

5) 针对自己画的版图,给出实现该电路的工艺流程图。 电路设计方案的确定 数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。它的作用相当于多个输入的单刀多掷开关,其示意图如下所示 数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路,函数发生器及数码比较器等,常见的数据比较器有2选1,4选1,8选1,16选1电路。

示意图 在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器。 数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号。 本次设计的是8选1数据选择器。选择控制端(地址端)为K2,K1,K0,按二进制译码,从8个输入数据D0-D7中,选择一个需要的数据送到输出端Y。 根据多路开关的开关状态(地址码)K2,K1,K0的状态选择D0-D7中某一个通道的数据输送到输出端Y。 如:K2K1K0=000,则选择D0数据到输出端,即Y=D0。 如:K2K1K0=001,则选择D1数据到输出端,即Y=D1,其余类推。 8选1 MUX功能表如下: 电路图设计如下: 1:

数据选择器及其应用解读

实验五数据选择器及其应用 [实验目的] 1、掌握中规模集成数据选择器的逻辑功能及使用方法。 2、学习用数据选择器构成组合逻辑电路的方法。 [实验原理] 数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择器的功能类似一个多掷开关,如图4-5-1所示,图中有四路数据D0~D3,通过选择控制信号A1、A0(地址码)从四路数据中选中某一路数据送至输出端Q。 数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、16选1等类别。 数据选择器的电路结构一般由与或门阵列组成,也有用传输门开关和门电路混合而成的。 图4-5-1 4选1数据选择器示意图图4-5-2 74LS151引脚排列 表4-5-1 1、8选1数据选择器74LS151 74LS151为互补输出的8选1数据选择器,引脚排列如图4-5-2,功能如表4-5-1。 选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,选择1个需要的数据送到输出端Q,S为使能端,低电平有效。 (1)使能端S——=1时,不论A2~A0状态如何,均无输出(Q=0,Q——=1),多路开关被禁止。 (2)使能端S——=0时,多路开关正常工作,根据地址码A2、A1、A0的状态选择D0~D7中

某一个通道的数据输送到输出端Q 。 如:A 2A 1A 0=000,则选择D 0数据到输出端,即Q=0。 如:A 2A 1A 0=001,则选择D 1数据到输出端,即Q=D 1,其余类推。 2、双四选一数据选择器74LS153 所谓双4选1数据选择器就是在一块集成芯片上有两个4选1数据选择器。74LS153的引脚排列如图4-5-3,功能如表4-5-2。 表4-5-2 图4-5-3 74LS153引脚功能 1S —— 、2S —— 为两个独立的使能端,A 1、A 0为公用的地址输入端;1D 0~1D 3和2D 0~2D 3 分别为两个4选1数据选择器的数据输入端;Q 1、Q 2为两个输出端。 (1)当使能端1S —— (2S —— )=1时,多路开关被禁止,无输出,Q=0. (2)当使能端1S —— (2S —— )=0时,多路开关正常工作,根据地址码A 1、A 0的状态,将相应的数据D 0~D 3送到输出端Q 。 如:A 1A 0=00,则选择D 0数据到输出端,即Q=D 0。 A 1A 0=01,则选择D 1数据到输出端,即Q=D 1,其余类推。 数据选择器的用途很多,例如多通道传输、数码比较、并行码变串行码以及实现逻辑函数等。 3、数据选择器的应用-实现逻辑函数 例1:用8选1数据选择器74LS151实现函数F=AB — +A — B (1)列出函数F 的功能表如表4-5-4所示。 (2)将A 、B 加到地址端A 1、A 0,而A 2接地,由表4-5-3可见,将D 1、D 2接“1”及D 0、D 3接地,其余数据输入端D 4~D 7都接地,则8选1数据选择器的输出Q ,便实现了函数 F=AB — +A — B 接线图如图4-5-4所示。 表4-5-3 图4-5-4 8选1数据选择器实现F=AB — +A — B 的接线图 显然,当函数输入变量数小于数据选择器的地址端(A)时,应将不用的地址端及不用的数据输入端(D)都接地。 例2:用双4选1数据选择器74LS153实现函数F= A — BC + AB — C +ABC — +ABC 函数F 的功能如表4-5-4所示。

实验四数据选择器及其应用

实验四数据选择器及其应用 以下是为大家整理的实验四数据选择器及其应用的相关范文,本文关键词为实验,数据,选择器,及其,应用,实验,数据,选择器,及其,应,您可以从右上方搜索框检索更多相关文章,如果您觉得有用,请继续关注我们并推荐给您的好友,您可以在教育文库中查看更多范文。 实验四数据选择器及其应用 一、实验目的 1、掌握中规模集成数据选择器的逻辑功能及使用方法 2、学习用数据选择器构成组合逻辑电路的方法

二、实验原理 数据选择器又叫“多路开关”。数据选择器在地址码(或叫选择控制)电位的控制下,从几个数据输入中选择一个并将其送到一个公共的输出端。数据选择器的功能类似一个多掷开关,如图4-1所示,图中有四路数据D0~D3,通过选择控制信号A1、A0(地址码)从四路数据中选中某一路数据送至输出端Q。 图4-14选1数据选择器示意图图4-274Ls151引脚排列 表4-1输入s输出A0×01010101Q0D0D1D2D3D4D5D6D7QA2×00001111A1×00110011100 0000001D0D1D2D3D4D5D6D7数据选择器为目前逻辑设计中应用十分广泛的逻辑部件,它有2选1、4选1、8选1、 16选1等类别。 数据选择器的电路结构一般由与或门阵列组成,也有用传输门开关和门电路混合而成的。 1、八选一数据选择器74Ls151 74Ls151为互补输出的8选1数据选择器,引脚排列如图4-2,功能如表4-1。 选择控制端(地址端)为A2~A0,按二进制译码,从8个输入数据D0~D7中,选择一个需要的数据送到输出端Q,s为使能端,低电平有效。 1)使能端s=1时,不论A2~A0状态如何,均无输出(Q=0,Q=1),多路开关被禁止。