74LS283加法器

实验二组合逻辑电路实验—加法器

一、实验目的:

1.掌握加法器相关电路的设计和测试方法。

2.掌握常见加法器集成芯片使用方法。

二、实验原理:

在组合逻辑电路中任意时刻的输出只取决于该时刻的输入,与电路原来的状态无关。

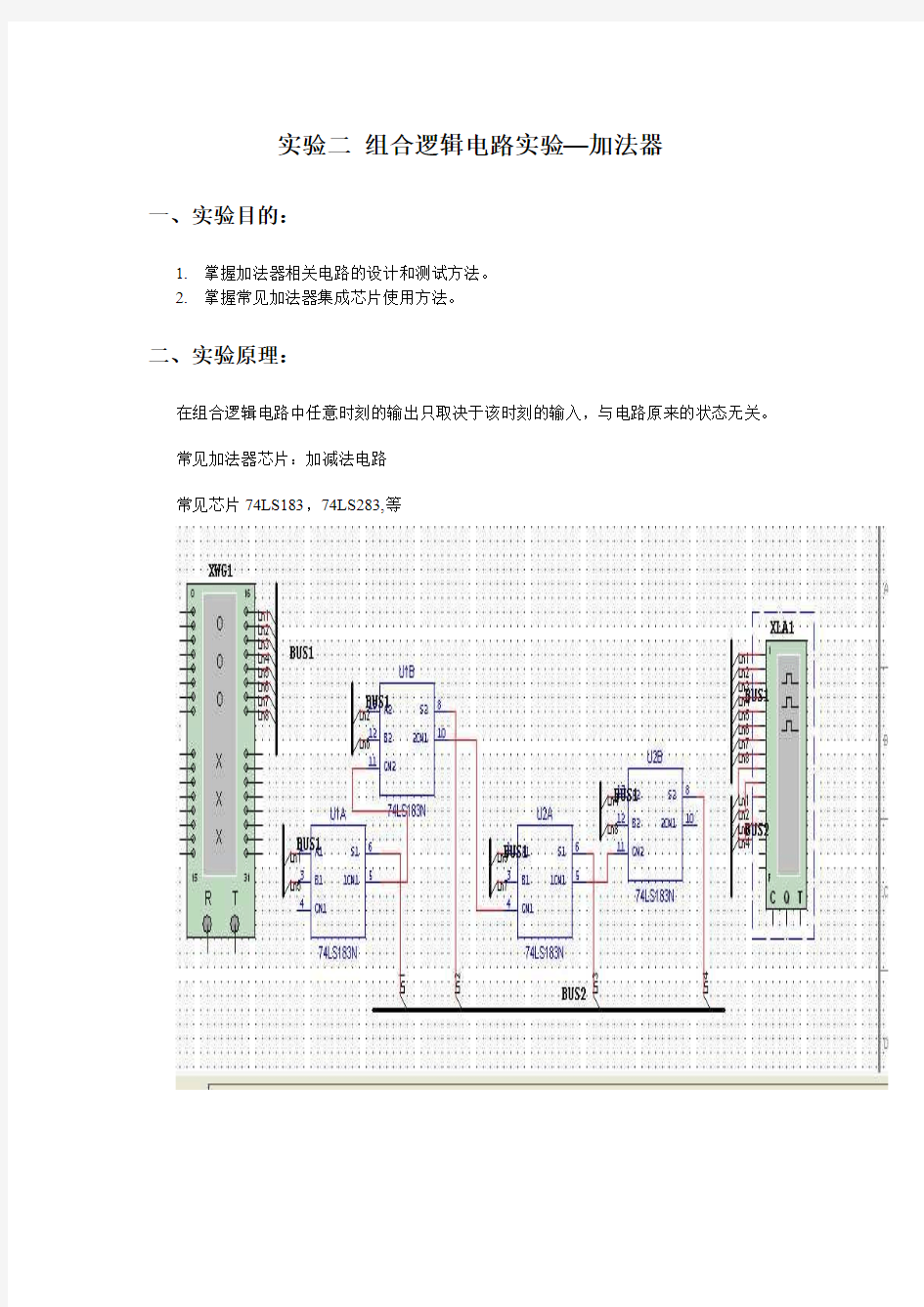

常见加法器芯片:加减法电路

常见芯片74LS183,74LS283,等

三、实验内容

一、实现两个BCD码的加法运算。

要求:利用74LS283加法器来完成。

根据实验要求列出真值表:

根据真值表得出逻辑表达式:

Y=S4*S3+S4*S2

设计电路如下:

字发生器内部参数:

逻辑分析仪结论:

二、实现两个四位二进制的减法

要求:利用74LS283加法器来完成。

要实现两个四位二进制的减法,只需把二进制码转化为对应的补码相加。

源码与补码:

设计电路图:

↑

符号位字发生器内部参数:

逻辑分析仪结论:

四、实验分析:

1、通过该实验,意识到自己对74LS283加法器的掌握还不过全面,实验设计过程中遇到很多困难。经过自己的努力,对74LS283加法器有了进一步的了解。

2、实验对于组合逻辑电路的设计能力的考验很重视,通过实验可以加强这方面的能力。

3、在做加法时,易忽略进位端对实验结果的影响,需注意。

4、在做减法时,对于二进制码转化为对应的补码的组合逻辑电路的设计尤为重要。另外,如果可以考虑到符号位就更好了!

阵列除法器设计与实现

课程设计报告 课程设计名称:计算机组成原理课程设计课程设计题目:阵列除法器设计及实现 院(系):计算机学院 专业: 班级: 学号: 姓名: 指导教师: 完成日期:2016年1月12日

目录 第1章总体设计方案0 1.1设计原理0 1.2设计思路2 1.3设计环境3 第2章详细设计方案4 2.1功能模块的设计及实现4 2.1.1细胞模块的设计及实现5 2.1.2除法器模块的设计及实现7 2.2仿真调试9 参考文献11 附录(电路原理图)

1 2

第1章总体设计方案 1.1 设计原理 在原码除法中,原码除法符号位是单独处理的,商符由两数符号位进行异或运算求得,商值由两数绝对值相除求得。原码除法中由于对余数的处理不同,又可分为恢复余数法和不恢复余数法(加减交替法)。在机器操作中通常采用加减交替法,因为加减交替法机器除法时间短,操作规则。 加减交替法的运算规则如下: (1)当余数为正时,上商1,余数左移一位后减去除数得下一 位余数。 (2)当余数为负时,上商0,余数左移一位后加上除数得下一位 余数。 阵列除法器是一种并行运算部件,采用大规模集成电路制造,及早期的串行除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速度。阵列除法器有多种形式,如不恢复余数阵列除法器、补码阵列除法器等等。本实验设计的是加减交替阵列除法器。 本实验利用的细胞单元是一个可控加法/减法CAS单元,利用它组成的流水阵列来实现四位小数的除法。CAS单元有四个输入端、四个输出端。其中有一个控制输入端P,当P=0时,CAS作加法运算;

当P=1时,CAS作减法运算。逻辑结构图如图1.1所示。 图1.1 可控加法/减法(CAS)单元逻辑结构图CAS单元的输入及输出的关系可用如下逻辑方程来表示:Si=Ai⊕(Bi⊕P)⊕Ci Ci+1=(Ai+Ci)(Bi⊕P)+AiCi 当P=0时,CAS单元就是一个全加器,如下: Si=Ai⊕B⊕iCi Ci+1=AiBi+BiCi+AiCi 当P=1时,则得求差公式: Si=Ai⊕B⊕iCi Ci+1=AiBi+BiCi+AiCi

实验二加减法器

计算机组成原理实验报告 一、实验目的及要求 本次实验要求掌握加法器、减法器的设计与实现。 可以利用原理图设计并实现 1 位、8 位和32 位加法器,以及32 位加减器。设计1 位加法器,将加法器中加入减法功能,可以利用SUB(减)的控制信号; 二、实验设备(环境)及要求 1. Windows 2000 或Windows XP 2. QuartusII9.1 sp2、DE2-115 计算机组成原理教学实验系统一台。 三、实验内容与步骤 (1)两个二进制数字A,B 和一个进位输入C0相加,产生一个和输出S,以及一个进位输出C1,这种运算电路成为全加器(1 位加法器)。1 位全加器有两个输出S 和C1,其中S 为加法器的和,C1 为进位位输出。下表中列出一位全加器进行加法运算的输入输出真值表: 表2-1 加法器的真值表 根据以上真值表,可以得到 1 位加法器的输入与输出逻辑关系。 根据上面的逻辑关系式可以建立如下图的 1 位加法器的原理图

接着进行功能仿真: 开始功能仿真,在【Processing】菜单下,选择【Start Simulation】启动仿真工具。实验结果: 在5-10ns 时,A=1,B=0,C0=0,则C1=0,S=1; 在15-20ns 时,A=1,B=1,C0=0,则C1=1,S=0; 在30-35ns 时,A=0,B=1,C0=1,则C1=1,S=0; 在35-40ns 时,A=1,B=1,C0=1,则C1=1,S=1; (2)8 位加法器的原理图设计 实验原理8 位加法器用于对两个8 位二进制数进行加法运算,并产生进位。8 位加法器真值表如下所示:

计算机组成原理_原码阵列除法器

计算机组成原理专周报告 成都电子机械高等专科学校计算机工程系

` 目录 一、项目名称 (1) 二、实验目的 (1) 三、不恢复余数的阵列除法器介绍 (1) 四、逻辑流程图及原理 (3) 算法流程 (3) 粗框图 (4) CSA逻辑结构图 (4) 原理分析 (5) 五、实例结果及求解过程 (8) 实例结果图 (8) 实例求解过程 (9) 六、心得体会: (10)

计算机组成原理专周报告 一、项目名称 原码阵列除法器 二、实验目的 1)理解原码阵列除法运算的规则。 2)掌握原码阵列除法器设计思想,设计一个原码阵列除法器。 3)熟悉proteus 7 professional软件的使用。 4)复习巩固课堂知识,将所学知识运用于实际,做到学以致用。三、不恢复余数的阵列除法器介绍 阵列式除法器是一种并行运算部件,采用大规模集成电路制造,与早期的串行除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速度。阵列除法器有多种多样形式,如不恢复余数阵列除法器,补码阵列除法器等等。我们所用到的就是不恢复余数的阵列除法器。 设:所有被处理的数都是正的小数(仍以定点小数为例)。不恢复余数的除法也就是加减交替法。在不恢复余数的除法阵列中,每一行所执行的操作究竟是加法还是减法, 取决于前一行输出的符号与

被除数的符号是否一致。当出现不够减时,部分余数相对于被除数来说要改变符号。这时应该产生一个商位“0”,除数首先沿对角线右移,然后加到下一行的部分余数上。当部分余数不改变它的符号时, 即产生商位“1”,下一行的操作应该是减法。图(四)示出了 (4位÷4位)的不恢复余数阵列除法器的逻辑原理图。由图看出,该阵列除法器是用一个可控加法/减法(CAS)单元所组成的流水阵列来实现的。推广到一般情况,一个(n+1)位除(n+1)位的加减交替除法阵列由(n+1)2个CAS单元组成,其中两个操作数(被除数与除数)都是正的。单元之间的互连是用n=3的阵列来表示的。 这里被除数X是一个6位的小数(双倍长度值):X=0.A1A2A3A4A5A6它是由顶部一行和最右边的对角线上的垂直输入线来提供的。 除数Y是一个3位的小数:Y=0.B1B2B3 它沿对角线方向进入这个阵列。这是因为,在除法中所需要的部分余数的左移,可以用下列等效的操作来代替:即让余数保持固定,而将除数沿对角线右移。 商Q是一个3位的小数:Q=0.Q1Q2Q3 它在阵列的左边产生。 余数r是一个6位的小数:r=0.00r0r1r2r3 它在阵列的最下一行产生。

加法器与减法器

电子设计自动化 大作业 题目加法器与减法器 学院泉城学院 班级电气09Q2班 姓名李文建 学号 20093005034 二O一一年十一月六日

加法器和减法器 一、设计要求: (1)构造一个四位二进制加法器和一个四位二进制减法器,完成各自的功能仿真。(2)利用四个按键输入四位加数(或减数)和被加数(或被减数)。 (3)用七段数码管显示四位和(或差),用一只发光二极管指示进位(或借位)信号。(4)利用个开关控制,确定是四位二进制加法器还是一个四位二进制减法器。 二、总体设计: 1、总体结构图

2、各模块功能 (1)第一个4-16译码器实现输入四位加数(或减数)和被加数(或被减数)。 (2)开关模块:控制B0、B1、B2、B3,当M=0时,执行A+B,当M=1时,执行A-B。 (3)加法(减法)器模块: 加法器:采用全加器的串行进位,本四位二进制加法器由四个一位二进制加法器组成,输入A i、B i、C i,输出S i、C i+1。 减法器:与加法器的区别仅仅在于最后的和数为两数相减。 (4)LED灯: 加法器:灯亮表示有进位,灯灭表示无进位。 减法器:灯亮表示有借位,灯灭表示无进位。 (5)第二个4-16译码器:输入为四为加法器的和S0、S1、S2、S3,输出为Y0—Y6分别控制七段数码管的a1、b1、c1、d1、e1、f1、g1,输出Y9—Y15分别控制第二个七段数码管的a2、b2、c2、d2、e2、f2、g2。 (6)数码管:显示输出结果。 三、单元模块设计 1、第一个4—16译码器 (1)模块功能 通过四个按键输入四位二进制数,由译码器得到四位加数(或减数)和被加数(或被减数)的所有组合,从而实现加法器(或减法器)的输入。 (2)端口定义

组成原理,除法器

二.不恢复余数法(加减交替法)除法器 1.1 设计 1.1.1 设计原理 对两个正数采用不恢复余数的算法的一般步骤如下。 1)r 1=x-y ,若r 1<0,同时恢复余数:r 1=r 1+y 。否则,商q 0=1。说明商大于0。根据计算机中的定点小数表示规定,超过了数的表示范围,作溢出处理。 2)如果已经求得第i 次的部分余数r ,若r i <0,则上商为q i -1=0,r i +1=2r i +y 。上次多减的y 在这次运算中补回来了,否则,商q i =1,ri+1=2r i -y 。 3)不断循环2),直到求得所需要的商的位数(n+1)。 例: x=0.1001, y=-0.1011, 用不恢复余数法求 x/y=? 解: 求解过程如下: 所以 x ÷ y 的商 [q ]原 = 0.1101,余数[ r ]原 = 0.00000001 1.1.2 设计环境 MASM 1.1.3. 程序运行界面 被除数x /余数r 商数q 说明 0 0.1 0 0 1 +[-y ]补 1 1.0 1 0 1 x 减y 1 1.1 1 1 0 余数r 0<0,商0 ← 1 1.1 1 0 0 0 商0,r 和q 左移一位 +[y ]补 0 0.1 0 1 1 加y 0 0.0 1 1 1 余数r 1>0,商1 ← 0 0.1 1 1 0 0.1 商1,r 和q 左移一位 +[-y ]补 1 1.0 1 0 1 减y 0 0.0 0 1 1 余数r 2>0,商1 ← 0 0.0 1 1 0 0.1 1 商1,r 和q 左移一位 +[-y ]补 1 1.0 1 0 1 减y 1 1.1 0 1 1 余数r 3<0,商0 ← 1 1.0 1 1 0 0.1 1 0 商0,r 和q 左移一位 +[y ]补 0 0.1 0 1 1 加y 0 0.0 0 0 1 余数r 4>0,商1 1 1 0 1 商1,仅q 左移一位

VHDL加法器和减法器的原理

加法器 3.2.1 加法器的原理 在将两个多位二进制数相加时,除了最低位以外,每一位都应该考虑来自低位的进位,即将两个对应位的加数和来自低位的进位3个数相加。这种运算称为全加,所用的电路称为全加器。 多位加法器的构成有两种方式:并行进位和串行进位。并行进位加法器设有进位产生逻辑,预算速度较快;串行进位方式是将全加器级联构成多位加法器。并行进位加法器通常比串行级联加法器占用更多的资源。随着为数的增加,相同位数的并行加法器与串行加法器的资源占用差距也越来越大,因此,在工程中使用加法器时,要在速度和容量之间寻找平衡点。 本次设计采用的是并行加法器方式。 3.2.2 加法器要求实现的功能 实现两个二进制数字的相加运算。当到达时钟上升沿时,将两数输入,运算,输出结果。 3.2.3 加法器的VHDL语言实现 (以下以12位数加16位数生成16位数的加法器为例) LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_arith.ALL; ENTITY add121616 is PORT(clk : in STD_LOGIC; Din1 :in signed (11 downto 0); Din2 :in signed (15 downto 0); Dout:out signed (15 downto 0)); END add121616; ARCHITECTURE a of add121616 is SIGNAL s1: signed(15 downto 0); BEGIN s1<=(Din1(11)&Din1(11)&Din1(11)&Din1(11)&Din1); PROCESS(Din1,Din2,clk) BEGIN if clk'event and clk='1' then Dout<=s1+Din2; end if; end process; end a; 3.2.4 加法器的模块图

高效除法器verilog实现

v1.0可编辑可修改 西北工业大学 《FPGA技术实验》 实验报告二 (高效除法 器)

可编辑可修改 学院: 学号: 姓名: 专业: 实验时间: 实验地点: 软件与微电子学院微电子学 毅字楼335

指导教师:王少熙 西北工业大学 2010年10月

为了能清楚的展示以上算法我们看下面例子:为了简单期间我们假设被除数 (did)是4位,除数(dis)是2位,商(quo)是4位,余数(rem)是4位,设did=0110,dis=10,我们来看看是怎么执行的?首先余数和商都清零,即rem=0,quo=0;把被除数的最高位0拼接到rem的最低位,此时rem=0000B,由于rem小于除数dis=10,则商quo[3]=0;下面进行第二次计算,把did[2]拼接到rem 最低位,此时rem=0001,dis=10>rem,故quo[2]=0;继续计算,把 did[1]拼接到rem 最低位,此时rem=0011,dis=10 进行最后一轮运算,把did[O]拼接到rem最低位,此时rem=0010,dis=10=rem, 因此 quo[0]=1,rem=rem-dis=0010-10=0000,至此我们已计算完毕商quo=0011, 余数rem=0000;计算简单快速. 2.测试平台设计 模块设计 'timescale 1ns/1ns module divider_8_4(did, error 置 1 ); parameter M=7; 数分别是9,10,11,12,13,14,15 时商为0,余数分别9,10,11,12,13,14,15. 当被除数为147,除数分别为1,2,3,4,5,6,7 时,商分别为 147,73,49,36,29,24,21, 余数分别为0,1,0,3,2,3,0. 结果正确. 并行除法器,并行除法器结构原理是什么? 1.可控加法/减法(CAS)单元 和阵列乘法器非常相似,阵列式除法器也是一种并行运算部件,采用大规模集成电路制造。与早期的串行除法器相比,阵列除法器不仅所需的控制线路少,而且能提供令人满意的高速运算速度。 阵列除法器有多种多样形式,如不恢复余数阵列除法器,补码阵列除法器等等。 首先介绍可控加法/减法(CAS)单元,它将用于并行除法流水逻辑阵列中,它有四个输出端和四个输入端。当输入线P=0时,CAS作加法运算;当P=1时,CAS作减法运算。逻辑结构图: CAS单元的输入与输出的关系可用如下一组逻辑方程来表示: S i=A i⊕(B i⊕P)⊕C i C i+1=(A i+C i)·(B i⊕P)+A i C i(2.32) 当P=0时,方程式(2.32)就等于式(2.23),即得我们熟悉的一位全加器(FA)的公式: Si=Ai⊕Bi⊕Ci Ci+1=AiBi+BiCi+AiCi 当P=1时,则得求差公式: S i=A i⊕B i⊕C i C i+1=A i B i+B i C i+A i C i (2.33) 其中B i=B i⊕1。 在减法情况下,输入C i称为借位输入,而C i+1称为借位输出。 为说明CAS单元的实际内部电路实现,将方程式(2.32)加以变换,可得如下形式: S i=A i⊕(B i⊕P)⊕C i =A i B i C i P+A i B i C i P+A i B i C i P+A i B i C i P+A i B i C i P+A i B i C i P+A i B i C i P+A i B i C i P C i+1=(A i+C i)(B i⊕P)+A i C i =A i B i P+A i B i P+B i C i P+B i C i P+A i C i 在这两个表达式中,每一个都能用一个三级组合逻辑电路(包括反向器)来实现。因此每一个基本的CA S单元的延迟时间为3T单元。 2.不恢复余数的阵列除法器 假定所有被处理的数都是正的小数。 不恢复余数的除法也就是加减交替法。在不恢复余数的除法阵列中,每一行所执行的操作究竟是加法还是减法,取决于前一行输出的符号与被除数的符号是否一致。当出现不够减时,部分余数相对于被除数来说要改变符号。这时应该产生一个商位“0”,除数首先沿对角线右移,然后加到下一行的部分余数上。当部分余数不改变它的符号时,即产生商位“1”,下一行的操作应该是减法。下图示出了4位除4位的不恢复 余数阵列除法器的逻辑原理图。其中 被除数x=0.x1x2x3x4x5x6(双倍长) 除数y=0.y1y2y3 商数q=0.q1q2q3 余数r=0.00r3r4r5r6 字长n+1=4 沈阳航空工业学院 课程设计报告 课程设计名称:计算机组成原理课程设计课程设计题目:阵列除法器的设计 院(系):计算机学院 专业:计算机科学与技术 班级:7401101 学号:200704011004 姓名:刘慧 指导教师:施国君 完成日期:2010年1月15日 沈阳航空工业学院课程设计报告 目录 第1章总体设计方案 (1) 1.1设计原理 (1) 1.2设计思路 (2) 1.3设计环境 (3) 第2章详细设计方案 (6) 2.1顶层方案图的设计与实现 (6) 2.1.1创建顶层图形设计文件 (6) 2.1.2器件的选择与引脚锁定 (7) 2.1.3编译、综合、适配 (8) 2.2功能模块的设计与实现 (8) 2.3仿真调试 (10) 第3章编程下载与硬件测试 (12) 3.1编程下载 (12) 3.2硬件测试及结果分析 (12) 参考文献 (14) 附录(电路原理图) (15) 第1章总体设计方案 1.1 设计原理 阵列除法器的功能是利用一个可控加法/减法(CAS)单元所组成的流水阵列来实现的。它有四个输出端和四个输入端。当输入线P=0时,CAS作加法运算;当P=1时,CAS作减法运算。可控加法/减法(CAS)单元的逻辑电路图如图1.1所示。 图1.1可控加法/减法(CAS)单元的逻辑图 CAS单元的输入与输出关系可用如下一组逻辑方程来表示: S i=A i ⊕(B i ⊕P) ?C C i+1=(A i+C i) ?(B i ⊕P)+A i C i 当P=0时,就得到我们熟悉的一位全加器(FA)的公式: S i=A i ⊕B i ⊕C i C i+1=A i B i+B i C i+A i C i 当P=1时,则得求差公式: S i=A i ?B i '?C i C i+1=A i B i '+B i 'C i+A i C i 其中B i '=B i?1。 称为借位输出。 在减法情况下,输入C i称为借位输入,而C i +1 除法器设计 摘要: 本设计要求设计一个简单的除法器,根据要求采用乘法器BG314与运算放大器3554AM以及外部电源共同实现除法器功能.乘法器用以实现乘法运算,然后通过运算放大器工作于负反馈状态实现信号的放大,并由自制电源电路供电.通过对系统各模块进行仔细的分析,了解了各器件的性能与用途后,便可将其运用到自己的设计当中去.电路设计完成后,开始对系统进行测试,方法有两种,可以通过对系统电路在Multisim软件下仿真测试,也可以做出相应的印制电路板来进行测试.在本设计中,通过仿真测试与实物测试相结合的综合测试后,发现系统基本能达到设计要求. 关键字: 乘法器运算放大器电源Multisim 印制电路板Summary: This design requests to design a simple division machine, adopting the multiplication machine BG314 and the operation enlarger 3554 AMses and the exterior power supplies according to the request to carry out the division machine function together.The multiplication machine carries out the multiplication operation in order to, then pass to operate the enlarger work to carry out the signal to enlarge in the negative feedback appearance, and from the self-control power supply electric circuit power supply.Pass to carry on the careful analysis to each mold of system piece, after understanding the function and uses of each machine piece, can make use of it to own design then in the middle.The electric circuit is after design complete, starting carrying on the test to the system, the method have two kinds of, can pass to imitate the true test to the system electric circuit under the software of Multisim, can also do a homologous of print and make circuit board to carry on the test.In this design, after passing to imitate the comprehensive test that the true test and real objects test combine together, discover that the system is basic and can attain design to request. Key word: The multiplication machine operation enlarger power supply Multisim prints to make the circuit board 目录 综合电子系统实习报告 设计题目:8位加法器和减法器的设计 一、实习目的:综合电子系统实习是电子信息类专业学生了解电子系统设计实现过程,培养实践动手能力的实践性教学环节,是电子信息工程等理工科专业学生一门必修的实践性课程。通过学习和实践,可以让学生进一步接触电子元器件,电子材料及电子产品的生产实际,了解电子工艺的一般知识和掌握基本电路板的制作,元件的焊接,产品的组装等技能,了解电子工艺生产线的流程和基本管理知识,使学生通过设计一个课题,巩固和加深在“模拟电子技术基础”和“数字电子技术基础”等课程中所学到的理论知识和实验技能,掌握常用电子电路中的一般分析和设计方法,熟悉protel和其他开发软件的使用方法,提高电子电路的分析、设计和实验能力,为以后从事生产和科研工作打下一定的基础,为今后专业实验,毕业设计准备必要的工艺知识和操作技能。同时培养学生严谨的工作作风,养成良好的工作习惯,它是基本技能和工艺知识的入门向导,又是创新实践和创新精神的启蒙。综合电子系统实习对训练我们基本操作技能,提高我们实际动手能力是难得的一次好机会。 二、实习基本内容和要求: (1)掌握常用电子元器件的种类,性能,选用原则及质量辨别; (2)掌握电子产品装配及材料; (3)学会印制电路板的制作,掌握锡焊原理及手工焊接工艺技术; (4)学会器件的装配,焊接,调试; (5)学会使用常用电子测试仪器设备,初步具有借助说明书或资料掌握常用工具,仪器的使用能力; (6)掌握常用电子电路的设计方法,学会系统实物制作和调试。 三、实习工具: (1)电烙铁:由于焊接的元件多,所以使用的是外热式电烙铁,功率为30w,烙铁头是铜制。 (2)螺丝刀、钻孔机、斜口钳、尖嘴钳等必备工具。 (3)焊锡,由于锡它的熔点低,焊接时,焊锡能迅速散步在金属表面焊接牢固,焊点光亮美观。 (4)数字万用表,5V直流稳压电源。 要求:1、利用逻辑门电路设计8位加法器和减法器,实现两个8位二进制数的加法运算和减法运算; 2、具有进位信号输入和输出能力; 3、通过功能选择控制信号F选择运算功能,F=0,加法运算,F=1, 进行减法运算; 4、用发光二极管显示两个输入数据和运算结构。 1、设计原理: 哈尔滨理工大学 课程设计 (计算机组成原理) 题目:简单模型机指令系统的设计 班级: 姓名: 指导教师: 系主任: 2017年03月10日 计算机组成原理(课程设计)设计过程情况表 目录 1.课程设计的目的 (1) 2.课程设计的任务 (1) 3.课程设计所用设备及所需资料 (1) 4.设计内容 (1) 4.1设计原理 (1) 4.1.1总体概述 (1) 4.1.2模型机的寻址方式 (2) 4.1.3模型机微指令系统的特点 (2) 4.2设计过程与步骤................................................................. 错误!未定义书签。 4.2.1. 模拟乘法除法的原理 (4) 4.2.2.对应算法分配硬件 (8) 4.2.3设计全新的指/微指令系统 (10) 4.3设计结果及分析 (12) 4.3.1汇编语言程序 (12) 4.3.2程序执行跟踪 (13) 5心得体会 (16) 1.课程设计的目的 1.在实验机上设计机器指令及对应的微指令(微程序),从而进一步掌握微程序设 计控制器的基本方法并了解指令系统与硬件结构的对应关系; 2. 通过控制器的微程序设计,综合理解计算机组成原理课程的核心知识并进一 步建立整机系统的概念; 3. 培养综合实践及独立分析、解决问题的能力。 2.课程设计的任务 针对COP2000实验仪,首先通过综合实验了解该模型机微程序控制器原理(主要指熟悉该模型机指令/微指令系统的详细情况),然后以实现二进制乘法和除法运算功能为应用目标,在COP2000的集成开发环境下,设计全新的指令系统并编写对应的微程序;并编写并运行实现乘法和除法的程序进行设计的验证。 3.课程设计所用设备及所需资料 1. COP2000实验系统 2. PC机( COP2000仿真软件) 3. COP2000计算机组成原理实验仪说明书 4.设计内容 4.1设计原理 4.1.1总体概述 COP2000模型机包括了一个标准CPU所具备所有部件,这些部件包括:运算器ALU、累加器A、工作寄存器W、左移门L、直通门D、右移门R、寄存器组R0-R3、程序计数器PC、地址寄存器MAR、堆栈寄存器ST、中断向量寄存器IA、输入端口IN、输出端口寄存器OUT、程序存储器EM、指令寄存器IR、微程序计数器uPC、微程序存储器uM,以及中断控制电路、跳转控制电路。其中运算器和中断控制电路以及跳转控制电路用CPLD来实现,其它电路都是用离散的数字电路组成。 微程序控制部分也可以用组合逻辑控制来代替。结构图如图1所示 模型机为8位机,数据总线、地址总线都为8位,但其工作原理与16位机相同。 实验报告 课程名称电子设计自动化实验(基于FPGA)实验项目加法器、减法器的设计 实验仪器计算机+ Quartus Ⅱ9.1 系别信息与通信工程学院 专业通信工程 班级/学号 学生姓名 实验日期2012、5 成绩_______________________ 指导教师_______________________ 加法器、减法器的设计 完成一个8位二进制带符号数的加减电路设计。设计要求如下:通过拨码开关输入两组8位二进制数,最高位为符号位,0表示正数,1表示负数,其余位表示二进制数值。用一按键对加、减方式进行控制,0表示加,1表示减。输出用四位LED数码管显示BCD码。其中LED显示器最高位为符号位。 VHDL代码 LIBRARY IEEE; USE IEEE.std_logic_1164.all; USE IEEE.std_logic_arith.all; USE IEEE.std_logic_unsigned.all; ENTITY add IS PORT(a:in std_logic_vector(7 downto 0); b:in std_logic_vector(7 downto 0); ctrl:in std_logic; bcd:out std_logic_vector(15 downto 0)); END ENTITY; ARCHITECTURE func OF add IS SIGNAL x:std_logic_vector(9 downto 0); SIGNAL y:std_logic_vector(9 downto 0); SIGNAL z:std_logic_vector(9 downto 0); SIGNAL c:std_logic_vector(8 downto 0); SIGNAL dec:integer; BEGIN yunsuan:BLOCK --运算模块 BEGIN PROCESS(a) BEGIN 2.5 定点除法运算 2.5.1 原码一位除法 设被除数[x]原=xf.x1x2…xn,除数[y]原=yf.y1y2…yn 则有[x÷y]原=(xf⊕yf)+(0.x1x2…xn/0.y1y2…yn) 对于定点小数,为使商不发生溢出,必须保证|x|<|y|;对于定点整数,为使商不发生溢出,必须保证双字|x|的高位字部分<|y|。 计算机实现原码除法,有恢复余数法和不恢复余数法两种方法。 1. 恢复余数法 由于每次商0之前都要先恢复余数,因此这种方法称之为恢复余数法。 [例2.40] x=0.1001,y=-0.1011,用原码恢复余数法计算x÷y。 2. 不恢复余数法 不恢复余数法又称加减交替法,它是恢复余数法的一种变形。设ri表示第i次运算后所得的余数,按照恢复余数法,有: 若ri>0,则商1,余数和商左移1位,再减去除数,即 ri+1=2ri-y 若ri<0,则先恢复余数,再商0,余数和商左移1位,再减去除数,即 ri+1=2(ri+y)-y=2ri+y 由以上两点可以得出原码加减交替法的运算规则: 若ri>0,则商1,余数和商左移1位,再减去除数,即ri+1=2ri-y; 若ri<0,则商0,余数和商左移1位,再加上除数,即ri+1=2ri+y。 由于此种方法在运算时不需要恢复余数,因此称之为不恢复余数法。原码加减交替法是在恢复余数的基础上推导而来的,当末位商1时,所得到的余数与恢复余数法相同,是正确的余数。但当末位商0时,为得到正确的余数,需增加一步恢复余数,在恢复余数后,商左移一位,最后一步余数不左移。 [例2.41] x=0.1001,y=-0.1011,用原码加减交替法计算x÷y。 由例2.41可以看出,运算过程中每一步所上的商正好与当前运算结果的符号位相反,在原码加减交替除法硬件设计时每一步所上的商便是由运算结果的符号位取反得到的。由例2.41还可以看出,当被除数(余数)和除数为单符号时,运算过程中每一步所上的商正好与符号位运算向前产生的进位相同,在原码阵列除法器硬件设计时每一步所上的商便是由单符号位运算向前产生的进位得到的。 [例2.42] x=-10110000,y=1101,用原码加减交替法计算x÷y。 南京铁道职业技术学院 创新电子培训 项目:加法器 老师:袁秀红 姓名:高书杰 二〇一三年三月二十五日 目录 一、实验目的 (3) 二、实验设备 (3) 三、实验原理 (3) 1.加法电路 (3) (1) 反相加法电路 (3) (2) 同相加法电路 (5) 2.差分放大电路 (6) 四、实验过程 (7) 1.双电源反相加法器电路 (7) (1) 双电源反相加法器直流测试电路 (7) (2) 双电源反相加法器交流测试电路 (16) (3) 双电源反相加法器动态范围测试 (22) 2.单电源反相加法器电路 (29) 3.双电源同相加法器电路 (29) (1) 双电源同相加法器直流测试电路 (29) (2) 双电源同相加法器交流测试电路 (37) 4.单电源同相加法器电路 (42) 5.双电源差分放大器电路 (43) (1)双电源差分放大器直流测试电路 (43) (2)双电源差分放大器交流测试电路 (50) 6.单电源差分放大器电路 (56) 五、实验结果 (57) 六、实验心得 (57) 加 法 器 一、实验目的 1.掌握运算放大器线性电路的设计方法。 2.熟悉掌握Multisim 软件对运算放大器进行仿真的用法及仿真分析的方法。 3.能正确判断和分析电路在仿真中的故障并正确解决。 4.理解运算放大器的工作原理。 二、实验设备 表1 序号 设备、材料 数量 备注 1 计算机 1台 2 Multisim 软件 1套 三、实验原理 1.加法电路 (1)反相加法电路 反相加法器电路是根据“虚断”和“虚短”的概念,运用节点电流法推导而出。 由“虚断”可得 n i f i i i i i +++== 21; 再根据“虚短”可得 1 11R u i i = ,222R u i i = ,…,n in n R u i =; )( 2211n in i i f f f o R u R u R u R i R u +++-=-= 。 加法器实验报告 篇一:加法器实验报告 实验 __一__ 【实验名称】 1位加法器 【目的与要求】 1. 掌握1位全加器的设计 2. 学会1位加法器的扩展 【实验内容】 1. 设计1位全加器 2. 将1位全加器扩展为4位全加器 3. 使4位的全加器能做加减法运算 【操作步骤】 1. 1位全加器的设计 (1)写出1位全加器的真值表 (2)根据真值表写出表达式并化简 (3)画出逻辑电路 (4)用quartusII进行功能仿真,检验逻辑电路是否正确,将仿真波形截图并粘贴于此 (5)如果电路设计正确,将该电路进行封装以用于下一个环节 2. 将1位全加器扩展为4位全加器 (1)用1位全加器扩展为4位的全加器,画出电路图 (2)分别用两个4位补码的正数和负数验证加法器的正确性(注意这两 个数之和必须在4位补码的数的范围内,这两个数包括符号在内共4位),用quartusII进行功能仿真并对仿真结果进行截图。 3. 将4位的全加器改进为可进行4位加法和减法的运算器 (1)在4位加法器的基础上,对电路进行修改,使该电路不仅能进行加 法运算而且还能进行减法运算。画出该电路 (2)分别用两个4位补码的正数和负数验证该电路的正确性(注意两个 数之和必须在4位补码的数的范围内),用quartusII进行功能仿真并对仿真结果进行截图。 【附录】 篇二:加法器的基本原理实验报告 一、实验目的 1、了解加法器的基本原理。掌握组合逻辑电路在Quartus Ⅱ中的图形输入方法及文本输入方法。 2、学习和掌握半加器、全加器的工作和设计原理 3、熟悉EDA工具Quartus II和Modelsim的使用,能够熟练运用Vrilog HDL 语言在Quartus II下进行工程开发、调试和仿真。 4、掌握半加器设计方法 5、掌握全加器的工作原理和使用方法 二、实验内容 1、建立一个Project。 2、图形输入设计:要求用VHDL结构描述的方法设计一个半加器 3、进行编译,修改错误。 4、建立一个波形文件。(根据真值表) 5、对该VHDL程序进行功能仿真和时序仿真Simulation 三、实验步骤 1、启动QuartusⅡ 2、建立新工程 NEW PROJECT 3、设定项目保存路径\项目名称\顶层实体名称 4、建立新文件 Blok Diagram/Schematic File 5、保存文件FILE /SAVE 6、原理图设计输入 元件符号放置通过EDIT_>SYMBOL 插入元件或点击图标 本文运用数字电路知识来设计加减法器,在PROTEUS中仿真出电路原理图,通过控制开关的闭合来模拟数据的输入以及控制控制开关来选择加法器或者减法器。通过数码管的显示可以看到所输入的数据以及输入数据的运算结果。通过加减法器的课程设计,可以从中学习和巩固数字电路的相关知识。比如,减法器电路的设计,全加器芯片以及各种逻辑门器件的使用等等。 关键字:加减法器;数码管;逻辑门;全加器;PROTEUS。 1概述 (1) 2方案设计 (2) 2.1设计要求 (2) 2.2方案设计 (2) 2.3设计原理 (3) 3电路设计 (4) 3.1置数电路的设计 (4) 3.2加减法器电路的设计 (5) 3.3数码管显示电路的设计 (5) 3.4完整电路图的设计 (6) 4仿真与调试 (7) 4.1系统仿真步骤 (7) 4.2系统仿真结果分析 (7) 5总结 (10) 参考文献 (11) 致谢 (12) 第1章概述 目前,随着社会经济的发展,运算是人们生活中必不可少的,因此设计性能可靠的计算器是很有必要的。信息技术代表着当今先进生产力的发展方向,信息技术的广泛应用使信息的重要生产要素战略资源的作用得以发挥,使人们能更高效地进行资源优化配置,从而推动传统产业不断升级,提高社会劳动生产率和社会运行效率。 21世纪初,人类将全面迈向一个信息时代,信息技术革命是经济全球化的重要推动力量和桥梁,是促进全球经济和社会发展的主导力最,以信息技术为中心的新技术革命将成为世界经济发展史上的新亮点。信息技术将使人类能够进一步把潜藏在物质运动中的巨大信息资源挖掘出来,把世界变成一个没有边界的信息空间,以微处理机进入亿万办公室和家庭、超级计算机问世、卫星通信与光导通信的发展,特别是网络化的迅速发展为标志的,信息技术革命不仅以最为便捷的方式沟通了各国、各地区、各企业、各团体以及个人之间的联系,而且在一定程度上打破了种种地域乃至国家的限制,把核个世界空前地联系在一起,推动了全球化的迅速发展。 当今的世界是信息时代,而运算能力的强弱关系到自身获取信息的速度。这点对于人们很重要,它不仅对于个人,对于国家的安全和发展和国家的安全也是极其重要的。一个国家的综合实力的强弱可以从多个方面看出来,其中就包括对信息处理的能力,所以,研究高性能的计算机是每个国家都十分重视的一件事情。 我国以建设创新型国家为目标,把掌握装备制造业和信息产业核心技术的自主知识产权作为提高国家竞争力的突破口。虽然我国信息技术的总体水平与国际先进水平仍有不少差距,但近年来我国在一些有较大影响的关键信息技术领域有了可喜的突破。因此,作为天之骄子的我们很有必要学好信息技术,努力成为国家所需要的人才,为国家的繁荣富强作出自己的贡献,为中华民族的伟大复兴尽一份自己的力量。 实验二组合逻辑电路实验—加法器 实验目的: 1. 掌握加法器相关电路的设计和测试方法 2. 掌握常见加法器集成芯片使用方法 实验原理: 在组合逻辑电路中任意时刻的输出只取决于该时刻的输入,与电路原来的状态无关。 常见加法器芯片:加减法电路 常见芯片74LS183,74LS283等 实验内容: 一、实现两个BCD码的加法运算 要求:利用74LS283加法器来完成。 思考:当两数之和小于或等于9时,相加结果和二进制数相加没有区别,如果大于9时,要如何处理进位。 下表为两个8421的二——十进制数相加应得到的二——十进制形式的结果: 由表可见,将两个二——十进制数用二进制加法器相加,则相加结果小于等于9 (1001)时,得到的和就是所求的二——十进制和。而当相加结果 大于等于10(1010)后,必须将这个结果在另一个二进制加法器加6(0110) 修正,才能得到二——十进制的和及相加的进位输出。所以,产生进位输出CO2 的条件为 产生CO2的同时,应该在上加上6(0110),得到的 和CO2就是修正后的结果,电路图如下: 在信号发生器中输入数据如下: 则结果为: 图中 由下往上读数,即为结果的二进制形式,26为进位端,即十位。 二、实现两个四位二进制的减法 要求:利用74LS283加法器来完成。 思考:如何将加法器转换为减法功能。二进制的减法如何实现。 在算术运算中,减法可以看做加上这个数的负数来表示,在数字电路中,可以将减去一个数表示成加上这个数的反码。故在设计电路时,可将减数取反,所以电路图为: 在信号发生器中输入数据如下: 则结果为: 实验八加、减法器 —数字逻辑电路加法器 一、实验目的 1.了解二进制加法,加法计数器的工作过程。 2.学会计数器的调整及测试。 二、实验仪器及器件 稳压电源一台 实验板一块 数字万用表一块 集成块74LS74 74LS112 74LS76 74LS93 三、实验内容及说明 该电路是二进制并行加法器,是一种能并行产生两个二进制数算术和的组合逻辑部件. 采用4位二进制并行加法器设计一个用余3码表示的1位十进制数加法器。 根据余3码的特点,两个余3码表示的十进制数相加时,需要对相加结果进行修正。修正法则是:若相加结果无进位产生,则"和"需要减3;若相加结果有进位产生,则"和"需要加3。据此,可用两片4位二进制并行加法器和一个反相器实现给定功能,逻辑电路图如图7.6所示。其中,片Ⅰ用来对两个1位十进制数的余3码进行相加,片Ⅱ用来对相加结果进行修正。修正控制函数为片Ⅰ的进位输出FC4,当FC4=0时,将片Ⅰ的"和"输出送至片Ⅱ,并将其加上二进制数1101(即采用补码实现运算结果减二进制数0011);当FC4=1时,将片Ⅰ的"和"输出送至片Ⅱ,并将其加上二进制数0011,片Ⅱ的"和"输出即为两余3码相加的"和"数。 图7.6 逻辑电路图 四位二进制并行加法器T693构成思想如下: 第i位全加器的进位输出函数表达式为 Ci = A i B i +(A i +B i )C i-1 令 A i +B i →P i (进位传递函数) A i B i →G i (进位产生函数) 则有 C i =P i C i-1 +G i 于是,当i=1、2、3、4时,可得到4位并行加法器各位的进位输出函数表达式为 C 1=P 1 C +G 1 C 2=P 2 C 1 +G 2 =P 2 P 1 C +P 2 G 1 +G 2 C 3=P 3 C 2 +G 3 =P 3 P 2 P 1 C +P 3 P 2 G 1 +P 3 G 2 +G 3 C 4=P 4 C 3 +G 4 =P 4 P 3 P 2 P 1 C +P 4 P 3 P 2 G 1 +P 4 P 3 G 2 +P 4 G 3 +G 4 由于C 1~C 4 是Pi、Gi和C 的函数,而Pi、Gi又是 Ai、Bi的函数,所以, 在输入Ai、Bi和C 0之后,可以同时产生C 1 ~C 4 。通常将根据Pi、Gi和C0形成并行除法器

阵列除法器

简单的除法器设计系统

8位加法器和减法器设计实习报告

计算机组成原理乘法器和除法器课程设计

加法器、减法器的设计 VHDL

原码加减交替除法

加法器、减法器

加法器实验报告

加减法器的设计

加法器 减法器

加、减法器