PCI-Express总线的接口电路设计

PCI-Express总线的接口电路设计

王福泽 (天津工业大学)

一、课题背景

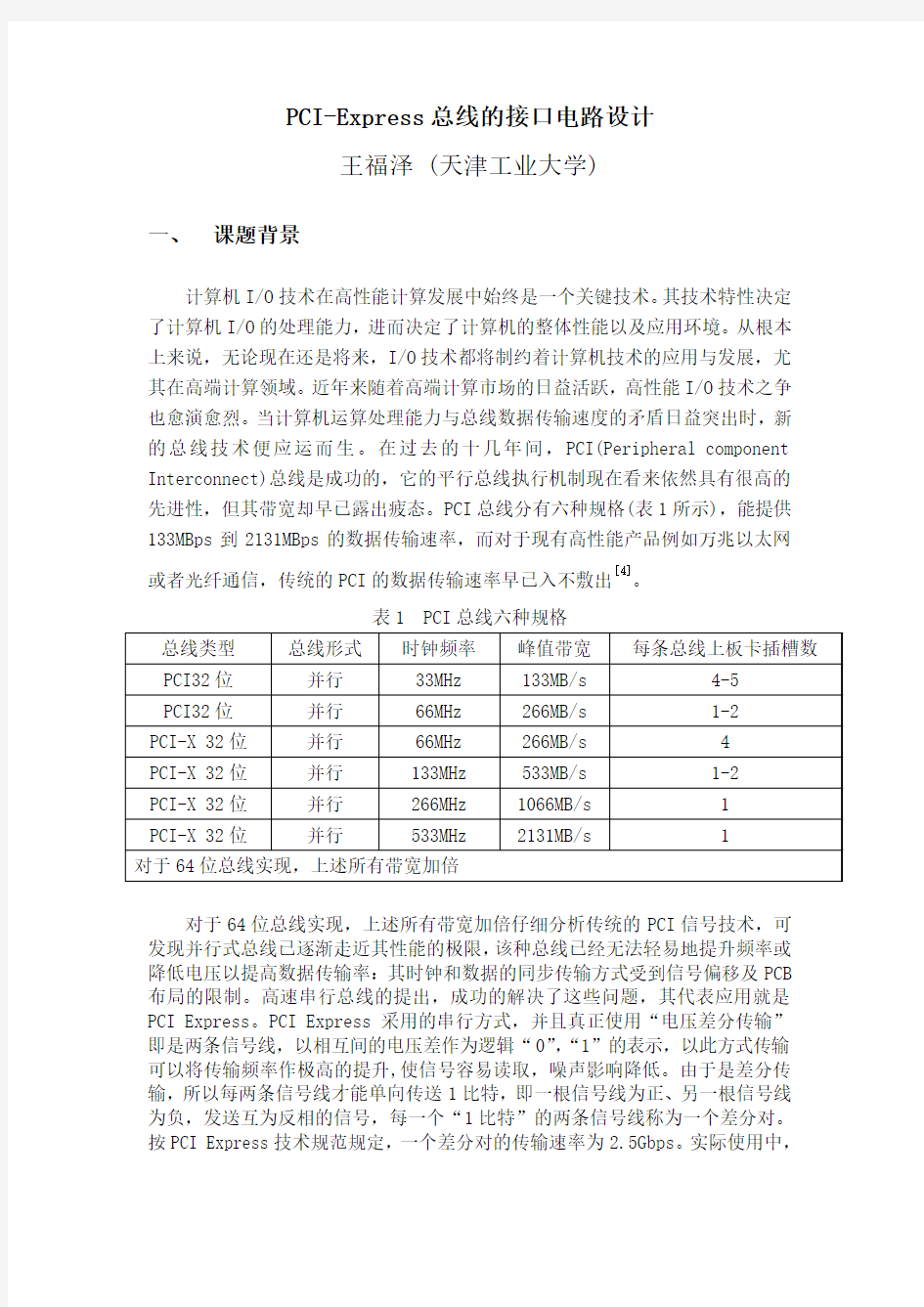

计算机I/O技术在高性能计算发展中始终是一个关键技术。其技术特性决定了计算机I/O的处理能力,进而决定了计算机的整体性能以及应用环境。从根本上来说,无论现在还是将来,I/O技术都将制约着计算机技术的应用与发展,尤其在高端计算领域。近年来随着高端计算市场的日益活跃,高性能I/O技术之争也愈演愈烈。当计算机运算处理能力与总线数据传输速度的矛盾日益突出时,新的总线技术便应运而生。在过去的十几年间,PCI(Peripheral component Interconnect)总线是成功的,它的平行总线执行机制现在看来依然具有很高的先进性,但其带宽却早已露出疲态。PCI总线分有六种规格(表1所示),能提供133MBps到2131MBps的数据传输速率,而对于现有高性能产品例如万兆以太网或者光纤通信,传统的PCI的数据传输速率早已入不敷出[4]。

表1 PCI总线六种规格

对于64位总线实现,上述所有带宽加倍仔细分析传统的PCI信号技术,可发现并行式总线已逐渐走近其性能的极限,该种总线已经无法轻易地提升频率或降低电压以提高数据传输率:其时钟和数据的同步传输方式受到信号偏移及PCB 布局的限制。高速串行总线的提出,成功的解决了这些问题,其代表应用就是PCI Express。PCI Express采用的串行方式,并且真正使用“电压差分传输”即是两条信号线,以相互间的电压差作为逻辑“0”,“1”的表示,以此方式传输可以将传输频率作极高的提升,使信号容易读取,噪声影响降低。由于是差分传输,所以每两条信号线才能单向传送1比特,即一根信号线为正、另一根信号线为负,发送互为反相的信号,每一个“1比特”的两条信号线称为一个差分对。按PCI Express技术规范规定,一个差分对的传输速率为2.5Gbps。实际使用中,

则要使用两个差分对作为一个条链路,分别用做发送和接收。因为有了这样的机制,使得数据带宽是可以弹性调配的。根据相关标准PCI-Express总线能够以xl/x2/x4/x8/x12/x16/x32进行传输(如表2所示),可提供5Gbps到160Gbps的传输带宽。当系统内某一通道需要更高频宽时,可以机动调度多个链路给该通道,

让其传输频宽提升,以适应一时激增的数据传输需求[1]。

表2 PCI-Express多链路传输速率表

除了传输方式的改变外,PCI Express还有一个更有意义的改变,即连接方式的改变。PCI Express采用点对点连接方式,较PCI的共享总线方式是一个重要的进步。对于PCI的共享总线方式,PCI总线上在某一时刻只能有一个设备进行通信,一旦PCI总线上挂接的设备增多,每个设备的实际传输速率就会下降,性能也得不到保证。而PCI Express则采用一种较为先进的连接方式,以点对点的方式处理通信,每个设备在要求传输数据时建立独立的传输通道,对于其它设备这个信道是封闭的,这种操作方式保证了通道的专有性,避免其它设备的干扰,使信号的质量和可靠性增加。由于是点对点的关系,也很好的保证了其扩展性。由于PCI-Express只是扩展总线,与操作系统无关,也可保证其与原有PCI的兼容性,给用户的升级带来了方便。下图为PCI-Express的拓扑结构。

图1 PCI-Express系统拓扑结构

PCI Express不但具有高性能的传输速率,而且其通用性也有重要的意义。由于其通用的模式,不仅可用于北南桥和其它设备的连接,也可以延伸到芯片组间的连接,甚至也可以用于连接图形芯片。这样整个计算机的I/O系统将重新统一起来,将更进一步的简化计算机系统,使其具有更强的通用性。从目前己经显现的特点看,PCI Express一改传统PCI的并行总线架构,因此比其它I/O技术有着更为领先的带宽优势,随着时间的推移有逐步取代PCI和PCI-X的趋势。PCI Express被广泛地认为是一项革命性的总线技术,其重要性可以满足不同使用者

的需求。随着未来持续增加的带宽需求,PCI Express具有广泛的应用前景[2]。

二、基于FPGA的PCI-Express接口具体设计方案

本设计将采用Xilinx公司最新的Virtex5LXT设计平台,使用了两个用于实现PCI Express 功能的集成端点模块,其中一个模块(主控模块)具有配置另一个模块(从属模块)的功能。数据可以在这两个集成端点模块之间双向(即在全双工模式下)流动。该设计的用户接口是通过本地链路 (LL) 接口提供的。该设计

能够在 x1、x2、x4 和 x8 通道配置下操作[3]。

设计功能如下:

?用户接口的本地链路成帧接口

? 64 位数据总线宽度与 3 位提醒总线

?包化接口,带用于标记包的帧起始 (SOF) 和帧结束 (EOF)

?传输和接收方向用户接口的包中断特性

?帧错误检测支持

?多通道配置支持:x1、x2、x4 和 x8

?每通道 1.62 Gb/s 或更高的吞吐量

?自动初始化、恢复与通道维护,对用户应用是透明的

? Virtex-5 LXT 器件中的集成端点模块

1.Xilinx IP核及其应用说明

该设计的完整框图如图3所示。两个端点可以直接通信,其中一个模块(主控模块)具有配置另一个模块(从属模块)的功能,数据可以在两个集成端点模块之间双向流动,用户接口由本地接口提供。

图3 基于PCI-Express的点到点连接结构框图

其中主控端可以在本地自行配置,另一端作为从属端,由主控端通过PCI-Express链路进行配置。进行配置后,该设计便已经准备好可以在全双工模式下进行数据传输操作了。设计的用户接口符合本地链路协议的要求。在传输期间,用户提供的本地链路帧在前往集成端点模块进行传输之前,会先被转换成传输层包(TLP)。在接收期间,来自集成端点模块的TLP会被转换正本地链路帧,而数据以及其他控制信号将通过本地链路接口传送给用户,因此,PCI-Express会分为三个架构模块:配置IP(config IP)、Context IP传输和Context IP接收。

配置IP模块

配置IP模块负责在本地配置主控端,并通过 PCI Express 协议链路配置从属端。配置完成后,会触发 LINK_READY,以表明链路已准备好可以进行数据传输了。配置期间,将在主控端和从属端设置最大有效载荷大小。配置 IP 会根据选择的用户设计选项设置集成端点模块的最大有效载荷大小 (MPS),如果是设计选项 1,则设置为 512 字节,如果是设计选项 2,则设置为 1024 字节。

Context IP传输模块

Context IP 传输模块采用存储转发技术原理,通过协议链路以存储器写TLP 的形式传输用户帧。存储器写 TLP 标头中的 TAG 区段未经过定义,可以包含任何值,因此可用于存储帧起始、帧结束、帧中断等标记,这些标记有助于在收到结束信号时重建本地链路帧。

传输器逻辑可将从用户处传来的数据存储在 FIFO 中。FIFO 的容量等于为选定设计选项设置的MPS。长度计数器会对有效载荷的长度进行计数,有效载荷的长度用于建立 TLP 标头中的长度区段。计数器在达到最高计数值(MPS = 512 时为 511, MPS = 1024 时为 1023)后会归零。帧的长度会存储在长度缓冲器内。Context传输框图如下图所示:

图4 Context传输框图

Virtex-5 器件中的内置 FIFO用于进行存储。如果数据传输之间的链路断开(LINK_UP 信号变为低),则当前存储在缓冲器内的所有数据都将丢失。由于

必须重新进行配置,因此可以将数据传输之间的链路断开视为复位。

如果用户帧大小小于在集成端点模块中设置的MPS,整个帧将作为单个TLP 进行传输,。

Context IP 接收

该模块(如图5)可接收来自传输层接收接口的 TLP,然后提取其中的有效载荷。从TLP的TAG区段提取的标记位将被写入到接收端 FIFO 的数据奇偶位输入

区段。提取的数据以及相应的本地链路成帧信号会被发送给接收端的用户[6]。

图5 Context IP 接收框图

2.PCI-Express端点IP核说明

Xilinx 提供的 Endpoint Block Plus for PCIe 解决方案适用于 Virtex?-5 LXT/SXT FPGA 架构,是一种可靠的高带宽可缩放串行互连构建模块。其顶层功能模块如图6所示,从中可以看出,核接口分为系统(SYS)接口、PCI-Express (PCI-EXP)接口、配置(CFG)接口以及事务(TRN)接口。

图6 顶层功能模块和接口

核使用数据包在各模块之间交换信息。数据包在事务层和数据链路层形成,用来承载从发送元件到接收元件的信息。传输的数据包中包括在各层处理数据包所需的必要信息。在接收端,各层接收元件处理输入的数据包,剥取相关信息,然后将数据包传送到下一层。于是,接收到的数据包从其物理层表现形式转换为数据链路层表现形式和事务层表现形式。

Endpoint Block Plus for PCIe核包括顶层信号接口,这些接口按接收方向、发送方向和双向共用信号分组。下面主要对各个接口进行分别介绍。

系统(SYS)接口

系统 (SYS) 接口信号由系统复位信号 sys_reset_n 和系统时钟信号sys_clk 组成,如下表所示:

系统复位信号是异步低有效输入信号。sys_reset_n 的有效置位致使整个核(包括Rocket I/O GTP和Rocket I/O GTX收发器)硬复位。复位信号发出后,核尝试进行链路初始化并恢复到正常工作状态。在典型的端点应用中,通常存在应连接到sys_reset_n的边带复位信号。系统输入时钟的频率必须是100MHz或250MHz,在Core Generator的GUI中选定。PCI-Express系统的时钟控制方式有两种:其一就是使用同步实在哦好难过控制,其中所有器件共用一个时钟源,

另一种是使用非同步始终控制,其中各器件使用自己的时钟源[7]。

PCI-Express接口

PCI Express (PCI_EXP) 接口信号由按多个通道组织的收发差分信号对组成。每个 PCI Express 通道由一对发送差分信号 {pci_exp_txp、pci_exp_txn} 和一对接收差分信号 {pci_exp_rxp、pci_exp_rxn} 组成。一通道核仅支持通道 0;四通道核支持通道 0-3;八通道核支持通道 0-7。

事务接口

事务 (TRN) 接口为用户设计提供生成和使用 TLP 的机制,分为共用事务接口、发送实物接口以及接收事务接口。

配置接口

配置 (CFG) 接口供用户设计用来检查 Endpoint for PCIe 配置空间的状态。用户提供一个 10 位配置地址,该配置地址选择 1024 个配置空间双字(DWORD) 寄存器之一。端点经 32 位数据输出端口返回所选寄存器的状态。

三、PIO传输测试

PCI Express 系统主 CPU 通常使用程控输入输出 (PIO) 事务来访问 PCI Express 架构中的存储器映射输入输出 (MMIO) 和配置映射输入输出 (CMIO) 位置。Endpoint for PCI Express 接受存储器和 IO 写事务,并使用带数据完成型事务来响应存储器和 IO 读事务。

由 CORE Generator 生成的 Endpoint for PCIe 中随附 PIO 示例设计(PIO 设计),可以通过业已成熟的现成设计即可方便地构建系统板,进而验证板的链路和功能。本测试将继续使用Virtex5芯片开发板作为硬件,调用其内核实现测试。图7为PCI-Express总线的架构组件。

图7 PCI-E系统概述

当 CPU 发出向 MMIO 地址存储寄存器的命令时,数据向下游移动。根联合体通常会生成一个具有相应 MMIO 位置地址、字节使能和寄存器内容的存储器写 TLP。Endpoint 接收存储器写 TLP 并更新相应的本地寄存器后,事务即终止。

当 CPU 发出从 MMIO 地址加载寄存器的命令时,数据向上游移动。根联合体通常会生成一个具有相应 MMIO 位置地址和字节使能的存储器读 TLP。Endpoint 在收到存储器读 TLP 后会生成带数据完成型 TLP。完成包传送到根联合体,有效载荷加载至目标寄存器后,事务即完成。

图8所示为 PIO 设计的各种组件,分为四大部分:TX 引擎、RX 引擎、存储器访问控制器和电源管理关闭控制器。

图8 PIO 设计组件

接收通路

图9所示为 PIO_64_RX_ENGINE 模块。模块的数据通路必须与正在使用的核的数据通路相匹配。这些模块与 Endpoint for PCIe 事务接收 (trn_r*) 接口相连接。

图9 Rx 引擎

PIO_64_RX_ENGINE 模块接收并解析输入的读和写 TLP。RX 引擎解析 1 DWORD 的 64位可寻址存储器和 IO 读请求。RX 状态机从 TLP 中提取所需信息并将其传送到存储器控制器。 RX 引擎解析 1 DWORD 的64 位可寻址存储器和IO 写请求。RX 状态机从 TLP 中提取所需信息并将其传送到存储器控制器。

发射通路

图10所示为 PIO_64_TX_ENGINE模块。模块的数据通路必须与正在使用的核的数据通路相匹配。这些模块与核事务发射 (trn_r*) 接口相连接。

图10 Tx 引擎

PIO_64_TX_ENGINE模块为接收到的存储器和 IO 读 TLP 生成完成包。PIO

设计不生成出站读或写请求。不过,用户可以添加此功能,以进一步定制设计。PIO_64_TX_ENGINE 模块生成完成包来响应 1 DWORD 的 64 位可寻址存储器和IO 读请求。生成该完成包所需的信息会传送到 TX 引擎。完成包发出后,TX 引擎将 compl_done_i 输出置为有效,指示 RX 引擎可将 trn_rdst_rdy_n 置为有效并继续接收 TLP。

Endpoint 存储器

图11 EP 存储器访问

图11所示为 PIO_EP_MEM_ACCESS 模块。此模块包含 Endpoint 存储器空间。PIO_EP_MEM_ACCESS 模块处理从入站存储器和 IO 写 TLP 写入存储器的数据,并使用存储器中的数据读来响应存储器和 IO 读 TLP。EP_MEM 模块根据从RX 引擎接收到的信息,处理 1 DWORD 的 64 位可寻址存储器和 IO 写请求。存储器控制器在处理写请求期间会将 wr_busy_o 输出置为有效,以指示其处于忙碌状态。1 DWORD 的 64 位存储器和 IO 读请求均根据以下输入处理。读请求处理完毕后,数据在 rd_data_o[63:0]上返回。

PIO 读事务

图12所示为对 PIO 设计的连续存储器读请求。完整接收第一个 TLP 后,接收引擎将 trn_rdst_rdy_n 置为无效。只有发射引擎将 compl_done_o 置为有效,指示第一个请求的完成包已成功发送后,才会接受下一个读事务。

图12 连续读事务

PIO 写事务

下图所示为对 PIO 设计的连续存储器写请求。仅当存储器访问单元将wr_busy_o 置为无效,指示与第一个请求相关的数据已成功写入存储器窗口后,

才会接受下一个写事务。下图为逻辑分析仪输出的写事务时序图

图13 连续写事务

四、测试结论与总结

PIO 设计展示了 Endpoint for PCI-Express 及其接口功能。经过读写事务的测试以及收发波形的分析对比,可以得出结论:通过Xilinx Virtex5 LXT平台设计的PCI-Express总线接口完全符合协议的标准,设计达到与其预期目标。

经过两个多月的学习和开发工作,我受益匪浅。不仅学会了关于Xilinx FPGA 的基本设计流程和方法,还深刻地理解了PCI-Express总线的拓扑结构及其特性,并且对ISE10.1以及Verilog HDL设计语言也进行了一定程度的学习,对硬件的电子开发技术基本入门,在理论和实践两方面都受益颇多。于此同时,此项难度巨大的设计工程也对我的意志有了一定的磨练,经历多次的失败和错误之后才得出此项成果,深感来之不易。

本设计经过传输测试后证明,已经达到PCI-Express总线的传输标准。采用此设计可以有效地缩短研发周期,降低研发风险。但此类的开发板一般价格较高,并不适合大批量应用。此为其不足之处。

五、主要参考文献

[1]刘福奇,刘波.Verilog HDL应用程序设计实例精讲.北京:电子工业出版社,2009

[2]马鸣锦,朱剑兵,何红旗.PCI、PCI-X和PCI-Express的原理及体系结构.北京:清华大学出版社,2007

[3]田耘.徐文波.胡彬.Xilinx ISE Design Suite 10.x FPGA开发指南-逻辑设计篇.北京:人民邮电出版社,2008

[4]田耘.徐文波.胡彬.Xilinx ISE Design Suite 10.x FPGA开发指南-DSP嵌入式与高速传输篇.北京:人民邮电出版社,2008

[5]潘松.黄继业.EDA技术实用教程(第二版).北京:科学出版社,2008

[6]孙静.PCIE接口芯片中的编码及解码电路设计:[硕士学位论文].沈阳;沈阳工业大学,2008

[7]胡鹏.新一代高速1/0互连PCI-Express接口设计:[硕士学位论文],北京;国防科技大学,2005

服务总线接口规范分析解析

安徽电信服务总线接口规范 安徽电信有限公司 2014年02月

版本记录 第1章概述 (4) 1.1概述 (4) 1.2目标 (4) 1.3规范使用对象及说明 (4) 1.4名词解释 (4) 第2章服务设计原则 (5) 2.1接口协议统一原则 (5) 2.2数据格式统一原则 (6) 2.3服务定义唯一性原则 (6) 2.4服务无状态原则 (6)

2.5服务部署原则 (6) 2.6服务组合原则 (6) 2.7报文内容处理的原则 (7) 2.8出入参设计原则 (7) 2.9规则校验的原则 (8) 2.10数据量原则 (8) 2.11同步调用原则 (8) 2.12统一入口原则 (8) 2.13持久化原则 (8) 第3章服务接入规范 (9) 3.1调用方式 (9) 3.2参数说明 (10) 3.2.1 系统级参数 (10) 3.3返回业务功能 (12) 第4章安全控制 (12) 4.1访问鉴权 (12)

4.2传输加密 (13) 第5章异常分类编码 (13) 第6章服务注册、注销、变更、调用流程 (15) 6.1服务注册的流程 (15) 6.2服务注册的内容 (15) 6.3测试环境服务注册的流程 (16) 第7章服务治理 (16) 7.1目标 (16) 7.2检查方法 (17) 7.3服务监控的指标 (18) 7.4服务目录树 (19)

第1章概述 1.1概述 本规范明确了安徽电信服务总线接入及服务使用的标准和规范,为服务使用方和服务提供方提供开发参考。 1.2目标 本规范为了指导各业务系统与服务总线平台的对接,实现以下目标: 1)当服务总线接入业务系统服务时,为该服务提供方提供开 发依据。 2)当服务使用方调用服务总线提供的服务时,为该服务使用 方提供开发依据。 3)为服务使用过程中安全及控制提供标准和参考。 1.3规范使用对象及说明 本规范适用于所有新建或改造的服务接口,均需要遵守本规范约定。 1.4名词解释

总线的接口电路设计

PCI-Express总线的接口电路设计 王福泽 (天津工业大学) 一、 课题背景 计算机I/O技术在高性能计算发展中始终是一个关键技术。其技术特性决定 了计算机I/O的处理能力,进而决定了计算机的整体性能以及应用环境。从根本 上来说,无论现在还是将来,I/O技术都将制约着计算机技术的应用与发展,尤 其在高端计算领域。近年来随着高端计算市场的日益活跃,高性能I/O技术之争 也愈演愈烈。当计算机运算处理能力与总线数据传输速度的矛盾日益突出时,新 的总线技术便应运而生。在过去的十几年间,PCI(Peripheral component Interconnect)总线是成功的,它的平行总线执行机制现在看来依然具有很高的 先进性,但其带宽却早已露出疲态。PCI总线分有六种规格(表1所示),能提供133MBps到2131MBps的数据传输速率,而对于现有高性能产品例如万兆以太网 或者光纤通信,传统的PCI的数据传输速率早已入不敷出[4]。 表1 PCI总线六种规格 总线类型 总线形式 时钟频率 峰值带宽 每条总线上板卡插槽数 PCI32位 并行 33MHz 133MB/s 4-5 PCI32位 并行 66MHz 266MB/s 1-2 PCI-X 32位 并行 66MHz 266MB/s 4 PCI-X 32位 并行 133MHz 533MB/s 1-2 PCI-X 32位 并行 266MHz 1066MB/s 1 PCI-X 32位 并行 533MHz 2131MB/s 1 对于64位总线实现,上述所有带宽加倍 对于64位总线实现,上述所有带宽加倍仔细分析传统的PCI信号技术,可 发现并行式总线已逐渐走近其性能的极限,该种总线已经无法轻易地提升频率或 降低电压以提高数据传输率:其时钟和数据的同步传输方式受到信号偏移及PCB 布局的限制。高速串行总线的提出,成功的解决了这些问题,其代表应用就是PCI Express。PCI Express采用的串行方式,并且真正使用“电压差分传输” 即是两条信号线,以相互间的电压差作为逻辑“0”,“1”的表示,以此方式传输 可以将传输频率作极高的提升,使信号容易读取,噪声影响降低。由于是差分传输,所以每两条信号线才能单向传送1比特,即一根信号线为正、另一根信号线 为负,发送互为反相的信号,每一个“1比特”的两条信号线称为一个差分对。 按PCI Express技术规范规定,一个差分对的传输速率为2.5Gbps。实际使用中,

完整版工业自动化领域各种总线协议规范接口

+接口+协议+规范工业自动化领域各种总线 工业自动化总标识特点简介 ASI 用于下位控制级的传感器/执行器总线【整理】ASI接口/协议 /规范用于将传感器和执行器连接AS-interface AS 至上位控制层,布线简单、经济。IEC EN 50295 符合国际标准和interface 标准。62026-2 传感器接执行器/AS-i = AS-Interface(口)是用于连接执行器和传感器的现 场总线通讯方案。BACnet==楼【整理】工业自动Building Automation Control Network 化之楼宇自动化之宇自动控制网.

用于执行器/传感器领域的多主站总线 对总线带宽的有效利用使得CANopen能 够在数据传输速率相对较低的情况下实现较短的系统响应时间。CAN 总线的主 要优点有:数据安全性高,能够保留多主站能力。 CC-Link 主要针对亚洲市场的现场总线 CC-Link(Control & Communication

Link,控制与通信链路)是一种开放式总线系统,用于控制级和现场总线级之间的通讯,应用范围主要为亚洲地区。 ControlNet 标准化现场总线 ControlNet 是一种开放式标准现场总线系统。该总线协议允许循环数据和非循 DALI 楼宇自动化领域的通讯标准【整理】工业自动)是一种跨越厂商标准 (IEC60929DALI 化总线之楼宇自动化之照明接口:的协议,其目的是在照明应用中确保电子DALI1-镇流器的互用性。这个新标准用于替代调光器接口。10VDigital ,数字可寻址照明接口(DALI)是一种楼Addressable Lighting Interface化

以太网EMC接口电路设计与PCB设计说明

以太网EMC接口电路设计及PCB设计 我们现今使用的网络接口均为以太网接口,目前大部分处理器都支持以太网口。目前以太网按照速率主要包括10M、10/100M、1000M三种接口,10M应用已经很少,基本为10/100M所代替。目前我司产品的以太网接口类型主要采用双绞线的RJ45接口,且基本应用于工控领域,因工控领域的特殊性,所以我们对以太网的器件选型以及PCB设计相当考究。从硬件的角度看,以太网接口电路主要由MAC(Media Access Controlleroler)控制和物理层接口(Physical Layer,PHY)两大部分构成。大部分处理器内部包含了以太网MAC控制,但并不提供物理层接口,故需外接一片物理芯片以提供以太网的接入通道。面对如此复杂的接口电路,相信各位硬件工程师们都想知道该硬件电路如何在PCB上实现。 下图1以太网的典型应用。我们的PCB设计基本是按照这个框图来布局布线,下面我们就以这个框图详解以太网有关的布局布线要点。 图1 以太网典型应用 1.图2网口变压器没有集成在网口连接器里的参考电路PCB布局、布线图,下面就以图2介绍以太网电路的布局、布线需注意的要点。 图2 变压器没有集成在网口连接器的电路PCB布局、布线参考 a)RJ45和变压器之间的距离尽可能的短,晶振远离接口、PCB边缘和其他的高频设备、走线或磁性元件周围,PHY层芯片和变压器之间的距离尽可能短,但有时为了

顾全整体布局,这一点可能比较难满足,但他们之间的距离最大约10~12cm,器件布局的原则是通常按照信号流向放置,切不可绕来绕去; b)PHY层芯片的电源滤波按照要芯片要求设计,通常每个电源端都需放置一个退耦电容,他们可以为信号提供一个低阻抗通路,减小电源和地平面间的谐振,为了让电容起到去耦和旁路的作用,故要保证退耦和旁路电容由电容、走线、过孔、焊盘组成的环路面积尽量小,保证引线电感尽量小; c)网口变压器PHY层芯片侧中心抽头对地的滤波电容要尽量靠近变压器管脚,保证引线最短,分布电感最小; d)网口变压器接口侧的共模电阻和高压电容靠近中心抽头放置,走线短而粗(≥15mil); e)变压器的两边需要割地:即RJ45连接座和变压器的次级线圈用单独的隔离地,隔离区域100mil以上,且在这个隔离区域下没有电源和地层存在。这样做分割处理,就是为了达到初、次级的隔离,控制源端的干扰通过参考平面耦合到次级; f)指示灯的电源线和驱动信号线相邻走线,尽量减小环路面积。指示灯和差分线要进行必要的隔离,两者要保证足够的距离,如有空间可用GND隔开; g)用于连接GND和PGND的电阻及电容需放置地分割区域。 2.以太网的信号线是以差分对(Rx±、Tx±)的形式存在,差分线具有很强共模抑制能力,抗干扰能力强,但是如果布线不当,将会带来严重的信号完整性问题。下面我们来一一介绍差分线的处理要点: a)优先绘制Rx±、Tx±差分对,尽量保持差分对平行、等长、短距,避免过孔、交叉。由于管脚分布、过孔、以及走线空间等因素存在使得差分线长易不匹配,时序会发生偏移,还会引入共模干扰,降低信号质量。所以,相应的要对差分对不匹配的情况作出补偿,使其线长匹配,长度差通常控制在5mil以内,补偿原则是哪里出现长度差补偿哪里; b)当速度要求高时需对Rx±、Tx±差分对进行阻抗控制,通常阻抗控制在100Ω±10%; c)差分信号终端电阻(49.9Ω,有的PHY层芯片可能没有)必须靠近PHY层芯片的Rx±、Tx±管脚放置,这样能更好的消除通信电缆中的信号反射,此电阻有些接电源,有些通过电容接地,这是由PHY芯片决定的; d)差分线对上的滤波电容必须对称放置,否则差模可能转成共模,带来共模噪声,且其走线时不能有stub ,这样才能对高频噪声有良好的抑制能力。

常见串口接口电路设计集锦

常见串口接口电路设计集锦 六种常用串口接口电路1、并口接口(分立元件) 适用于Windows 95/98/Me 操作系统。这个电路与FMS 随软件提供的电路比多了一个200K 的电阻,这个主要是为了与JR 的摇控器连接,因为JR 的摇控器教练口好象是集电极开路设计的,需要加一只上拉电阻才能正常工作。 不过电路还是满简单的,用的元件也很少,很适合无线电水平不太高的朋友们 制作,只是不能用于Win2000/XP 上有点让人遗憾。 2、串口接口(分立元件)字串5 适用于Windows 95/98/Me 操作系统,电路也不是很复杂,当然元件比并口电路多了一些,而且串口的外壳比并口小很多,如何把这些元件都放到小 小的外壳里免不了要大家好好考虑一下了。当做体积小也是它的最大的优点, 而且不用占用电脑并口,因为现在还有一些打印机还是要用并口的。缺点同样 是不支持Win2000/XP。 3、串行PIC 接口(使用PIC12C508 单片机)字串9 适用于Windows 95/98/Me/2000/XP 操作系统。电路简单,只是用到MicroChip 公司的PIC12C508 型单片机,免不了要用到编程器向芯片里写程序了,这个东西一般朋友可能没有,不过大多卖单片机的地方都有编程器,你只 要拿张软盘把需要用的HEX 文件拷去让老板帮你写就可以了。这个接口最大 的优点就是支Win2000/XP 操作系统,还可以用PPJOY 这个软件来用摇控器虚拟游戏控制器玩电脑游戏。 4、25 针串行PIC 接口(使用PIC12C508 单片机) 适用于Windows 95/98/Me/2000/XP 操作系统。电路同9 针的接口基本一样,只不过是接25 针串口的,现在用的不是很多了。

ESB企业服务总线接口规范

企业服务总线系统(ESB) 技术白皮书 [V1.0.1115] 厦门博立特有限公司 版权所有 保留所有权利

目录 1.前言 (4) 2 .ESB简介 (4) 3. ESB主要功能和特点 (6) 3.1.ESB主要功能: (6) 3.1.ESB主要特点: (7) 4.ESB接口设计 (8) 4.1 总体设计框图 (8) 4.2 技术规范 (8) 4.3 消息传输流程 (8) 4.4 文件传输流程 (8) 4.5 MsgService接口说明 (8) 4.5.1 登陆到ESB(Login) (8) 4.5.1.1 服务.NET原型 (8) 4.5.1.2 传入参数 (9) 4.5.1.3 返回参数 (9) 4.5.1.4 服务说明 (9) 4.5.2 发送消息到ESB(SendMessage) (9) 4.5.2.1 服务.NET原型 (9) 4.5.2.2 传入参数 (10) 4.5.2.3 返回参数 (10) 4.5.2.4 服务说明 (10) 4.5.3 从ESB接收消息(ReceiveMessage) (10) 4.5.3.1 服务.NET原型 (10) 4.5.3.2 传入参数 (11) 4.5.3.3 返回参数 (11) 4.5.3.4 服务说明 (11) 4.5.4 发送确认消息到ESB(AcknowledgeMessage) (11) 4.5.4.1 服务.NET原型 (11)

4.5.4.2 传入参数 (11) 4.5.4.3 返回参数 (12) 4.5.4.4 服务说明 (12) 5.附录A 返回代码对照表 (12)

1.前言 随着信息技术的不断发展,企业、政府部门等在信息化建设上投入了大量的资金、人力,逐步形成了适合自身某些部门或某些业务需要的管理信息系统,如办公自动化、客户关系管理CRM、企业资源计划ERP、生产制造系统等,这些管理信息系统,在企业和政府某些部门或业务的管理上,发挥了信息电子化、流程自动化、管理科学化的重要作用。 但是,企业和政府现有的管理信息系统,由于投入的时间、使用的部门、生产的厂家及实现技术等各不相同,造成企业和政府现有的应用信息系统各自独立运行,数据不能共享,各自业务流程不能自动衔接,造成企业和政府内部许多自成体系的信息化孤岛,各个应用系统不能相互协作,形成统一高效的有机整体。 企业应用集成,英文名称为Enterprise Application Integration,简称EAI,是为了解决企业和政府现有多种应用系统不能互连互通、数据共享、业务流程协调统一的问题,将异构的两个或更多的硬件、平台及应用系统进行无缝集成,使它们形成一个统一的整体。 企业服务总线(Enterprise Service Bus,缩写ESB),是面向服务架构的骨干,在完成服务的接入,服务间的通信和交互基础上,还提供安全性、可靠性、高性能的服务能力保障。采用SOA架构,基于ESB总线进行企业应用集成,应用系统之间的交互通过总线进行,这样可以降低应用系统、各个组件及相关技术的耦合度,消除应用系统点对点集成瓶颈,降低集成开发难度,提高复用,增进系统开发和运行效率,便于业务系统灵活重构,快速适应业务及流程变化需要。 2 .ESB简介 ESB作为博立特科技公司的企业应用集成产品,主要功能是在两个或更多的异构系统(如不同的数据库、消息中间件、ERP或CRM等)之间进行资源整合,实现互连互通、数据共享、业务流程协调统一等功能,构建灵活可扩展的分布式企业应用。

数字信号光耦合器应用电路设计

2008年10月第10期电子测试 EL ECTRONIC TEST Oct.2008No.10 数字信号光耦合器应用电路设计 田德恒 (莱芜职业技术学院信息工程系 莱芜 271100) 摘 要:较强的输入信号可直接驱动光耦的发光二极管,较弱的则需放大后才能驱动光耦。在光耦光敏三极管的集电极或发射极直接接负载电阻即可满足较小的负载要求;在光耦光敏三极管的发射极加三极管放大驱动,通过两只光电耦合器构成的推挽式电路以及通过增加光敏三极管基极正反馈,既达到较强的负载能力,提高了功率接口的抗干扰能力,克服了光耦的输出功率不足的缺点,又提高光耦的开关速度,克服了由于光耦自身存在的分布电容,对传输速度造成影响。最后给出了光耦合器在数字电路中应用示例。关键词:数字信号;光电耦合器;输入电路;输出电路中图分类号:TP211 文献标识码:B Applied circuit design of optoelect ronic coupler to t he digital signal Tian Deheng (Dept of Information Engineering ,Lai Wu Vocational College ,Laiwu 271100,China ) Abstract :The light 2emitting diode of optocoupler can be directly drived by stro nger inp ut sig 2nals ,t he weaker t he inp ut signal can be enlarged before driving optocoupler.Connecting direct 2ly load resistance wit h t he collector or emitter of p hotot ransistor to meet smaller load require 2ment s ;drover by t he amplifier triode on t he emitter of p hotot ransistor ,p ush 2p ull circuit s con 2sisting of two optocoupler as well as positive feedback added to base of t he p hotot ransistor not o nly achieve st rong load capacity and enhance t he power of t he interface anti 2jamming capabili 2ty ,but also overcome t he shortcomings of t he scant outp ut power ,increase t he switching speed ,overcome effect on t he speed of t he t ransmission due to t he distribution of capacitance.Finally ,t he application example of t he optocoupler in t he digital circuit is given.K eyw ords :digital signal ;optoelect ronic coupler ;inp ut circuit ;outp ut circuit 0 引 言 光电耦合器是一种把发光元件和光敏元件封 装在同一壳体内,中间通过“电2光2电”转换来传输 电信号的半导体光电子器件。光耦合器的主要优点是单向传输信号,输入端与输出端完全实现了电气隔离,抗干扰能力强,使用寿命长,传输效率高。它广泛用于电平转换、信号隔离、级间隔离、开关电

USB接口EMC设计方案

U S B2.0接口E M C设计方案一、接口概述 USB?通用串行总线(英文:Universal?Serial?Bus,简称USB)是连接外部装置的一个串口汇流排标准,在计算机上使用广泛,但也可以用在机顶盒和游戏机上,补充标准On-The-Go(?OTG)使其能够用于在便携装置之间直接交换资料。USB接口的电磁兼容性能关系到设备稳定行与数据传输的准确性,赛盛技术应用电磁兼容设计平台(EDP)软件从接口原理图、结构设计,线缆设计三个方面来设计USB2.0接口的EMC设计方案 二、接口电路原理图的EMC设计 本方案由电磁兼容设计平台(EDP)软件自动生成 1. USB 2.0接口防静电设计 图1 USB 2.0接口防静电设计 接口电路设计概述: 本方案从EMC原理上,进行了相关的抑制干扰和抗敏感度的设计;从设计层次解决EMC问题。 电路EMC设计说明: (1) 电路滤波设计要点: L1为共模滤波电感,用于滤除差分信号上的共模干扰; L2为滤波磁珠,用于滤除为电源上的干扰; C1、C2为电源滤波电容,滤除电源上的干扰。 L1共模电感阻抗选择范围为60Ω/100MHz ~120Ω/100MHz,典型值选取90Ω/100MHz; L2磁珠阻抗范围为100Ω/100MHz ~1000Ω/100MHz,典型值选取600Ω/100MHz ;磁珠在选取时通流量应符合电路电流的要求,磁珠推荐使用电源用磁珠; C1、C2两个电容在取值时要相差100倍,典型值为10uF、0.1uF;小电容用滤除电源上的高频干扰,大电容用于滤除电源线上的纹波干扰; C3为接口地和数字地之间的跨接电容,典型取值为1000pF,耐压要求达到2KV以上,C3容值可根据测试情况进行调整; (2)电路防护设计要点 D1、D2和D3组成USB接口防护电路,能快速泄放静电干扰,防止在热拔插过程中产生的大量干扰能量对电路进行冲击,导致内部电路工作异常。 D1、D2、D3选用TVS,TVS反向关断电压为5V;TVS管的结电容对信号传输频率有一定的影响,USB2.0的TVS结电容要求小于5pF。 接口电路设计备注: 如果设备为金属外壳,同时单板可以独立的划分出接口地,那么金属外壳与接口地直接电气连接,且单板地与接口地通过1000pF电容相连; 如果设备为非金属外壳,那么接口地PGND与单板地GND直接电气连接。

Q/GDW 622-2011 电力系统简单服务接口规范

电力系统简单服务接口规范 1范围 本标准提出了应用于电力系统的简单服务接口规范,以字符串方式描述面向服务消费者和服务提供者的语法、语义规则及服务调用接口规范。本规范适用于访问简单服务的应用场合。 2规范性引用文件 下列文件对于本文的应用是必不可少的。凡是注日期的引用文件,仅注日期的版本适用于本文件。凡是不注日期的引用文件,其最新版本(包括所有的修改单)适用于本文件。 GB/T 16262.1—2006:信息技术抽象语法记法一 (ASN.1) 第1部分:基本记法规范 Web Services Description Language (WSDL) 1.1 https://www.360docs.net/doc/5010104805.html,/TR/wsdl.html:web服务描述语言 3术语和定义 下列术语和定义适用于本标准。 3.1 服务Service 服务提供者完成一组工作,为服务消费者交付所需的最终结果。最终结果通常会使使用者的状态发生变化,但也可能使提供者的状态改变,或者双方都产生变化。 3.2 服务消费者Service Consumer 根据服务接口描述访问服务的实体 3.3 服务提供者Service Provider 实现一定功能并提供访问接口描述的实体 3.4 WSDL Web服务描述语言(Web Service Description Language) 3.5 域Domain 电力系统中不同级别的调度机构 3.6 简单服务Simple Service 能够相对独立运行具有简单的输入参数和输出结果的应用 4符号定义和语法规范 4.1符号定义 WSDL是目前唯一的用于Web服务访问的工业标准,通过使用复杂的语法规则来实现服务的描述和访问。本规范参考了WSDL语言,提出了用于电力系统的简单服务接口规范,提供服务访问的功能并满足电力系统对效率的要求。表1是简单服务接口规范的符号定义,扩充了类型描述符、路径分隔符、

几种典型接口电路(485)

典型接口电路EMC设计 一、以太网接口EMI设计 100M网口设计时必须设计Bob smith 电路:可以产生10dB的共模EMI衰减,为了更好的抑制共模信号通过线缆对外的辐射应注意下面几点: 1 、不用的RJ45管脚4 、5、7、8按下图的方法处理。 2 、物理芯片侧的变压器中心抽头需通过0.01uF-0.1uF的电容接地。 3 、物理芯片侧的差模电阻(收端)应等分为二(100分为两个49.9),中心点通过1000pF 电容接地。 以太网口Bob smith电路原理图 以82559为例说明网口设计PCB注意点,布局如下: 以太网口布局示意图

A、B要求尽量短,A不得超过1英寸,B可以根据实际情况放宽。接口变压器PCB设计如下: 以太网口变压器布局示意图 布局要求: PCB布局示意图 布线要求: 1、变压器下面全部掏空处理,其余隔离带的宽度大于100mil; 2、连接器与隔离变压器之间距离小于1000mil; 3、晶振距离接口变压器和板边大于1000mil; 4、灯线不要走到变压器下面,并且尽量不要与差分信号线同层走线,如果同层走线,需要与差分信号线相距30mil以上; 5、差分信号线与变压器输出侧的过孔距离大于40mil。

二、以太网口的防护设计 加防护电路的设计: 增加防护器件电路原理图 以上器件选型要求: 1、变压器要选用隔离耐压3000Vac要求的。 2、气体放电管尽量选用3端气体放电管,启动电压为90V的; 3、TVS管选用SLV2.8-4; 三、485接口电路设计 对于出户外的485端口,进行如下设计,采取气体放电管加TVS管加限流电阻组合方式。选用90V陶瓷管(3R090)可承受10/700us,8KV雷击测试;64V固体管(P0640)只能承受10/700us,3KV雷击测试 。TVS的选择为P6KE6.8CA ,去耦电阻选择为10Ω/1W 。

新型人机交互接口电路的设计

摘要主要介绍了TI公司的新型的16位超低功耗Flash型h6N30F44X系列单片机的结构、特性和功能及液晶显示器LCD的发光原理和类型,讨论了该系列单片机与ILD及键盘的人机接口电路的设计方案和相应的软件的实现方法,最后给出它在体内电刺激器的应用实例。 关键词单片机;MSP430;LCD;人机交互接口 1引言 在当今的各种实时自动控制和智能化仪器仪表中,人机交互是不可缺少的一部分。一般而言,人机交互是由系统配置的外部设备来完成,但其实现方式有两种:一种是由MCU力口驱动芯片实现,如键盘显示控制芯片SK5279A,串行数据传输数码显示驱动芯片MAX7219等等,这时显然MCU没有LCD的驱动功能。另一种就是MCU本身具有驱动功能,它通过数据总线与控制信号直接采用存储器访问形式或I/O设备访问形式控制键盘和LCD实现人机对话。这里的MCU主要有世界各大单片机生产厂商开发的各种单片机,其中TI公司的MSP430系列因其许多独特的特性引起许多研究人员的特别关注,在国内外的发展应用正逐步走向成熟。 2LCD简介 LCD(Liquid Crystal Display),即液晶显示器。液晶显示是通过环境光来显示信息的,它本身并不发光,因而功耗很低,只要求液晶周围有足够的光强。LCD是人与机器沟通的重要界面,早期以显像管(CRT/C athode Ray Tube)显示器为主,但随着科技不断进步,各种显示技术如雨后春笋般诞生。LCD由于具有轻薄短小、低耗电量、无辐射危险、平面直角显示以 及影像稳定不闪烁等优势,逐渐占据显示的主流地位。 LCD的类型,根据其分类方式的不同而不同。如根据LCD显示内容的不同可以分为段式LCD和点阵L CD。根据LCD驱动方式的不同可以分为静态驱动和多路驱动。 3MSP430F44X简介 MSP430F44X系列是TI公司最新推出的具有超低功耗特性的Flash型16位RISC指令集单片机[2]。该系列单片机性价比相当高,在系统设计、开发调试及实际应用上都表现出较明显的优势。它主要应用在各种要求极低功率消耗的场合,特别适合用于智能测量仪器、各种医疗器械、智能化家用电器和电池供电便携设备产品之中。 3.1系统结构 MSP430F44X的系统结构,主要包括:CPU、程序存储器(ROM)、数据存储器(RAM)、FLL+时钟系统(片内DCO+晶体振荡器)、看门狗定时器/通用目的定时器(WatchDog)、ADCl2(12位A/D)、比较器A(精确的模拟比较器,常用于斜边(Slope)A/D转换)、复位电压控制/电源电压管理、基本定时器(Basic Timerl)、定时器(Timer-a和Timer-B)、LCD控制器/比较器(多达160段)、硬件乘法器、I/O口和串行口[4]。系列中各种具体的型号稍有差别。在本次设计中,具体选择MSP430F449作为人机接口电路的设计具有许多独到的优势。这一点,读者可以根据TI公司相关的数据手册进行比较。 3.2片内外模块特性 MSP430F44X具有丰富的片内外围模块,其明显的特点是:具有48条I/0口线的6个并行口P1-P6,其中P1、p2具有中断能力,同时具有2个可用于UART/SPI模式选择的串行口(USART0和USARTl);内含12位的A/D转换器ADCl2,快速执行8×8、8×16、16×16乘法操作并立即得到结果的硬件乘法器;多达160段的LCD控制器/比较器,可以实现多种方式的驱动显示;可以实现UART、PWM、斜坡ADC 的16位Timer-A和16位Timer-B;非常灵活的时钟系统,既可用32768Hz的钟表晶振产生低频时钟,也可以用450kHz-8MHz的晶体产生高频时钟,同时还可以使用外部时钟源或者用不同控制频率的DCO;多达几十kB的Flash空间,这样数据既可以保存在片内的Flash信息存储器,也可保存在程序的Hash中的剩余空间。 4接口电路设计 4.1接口电路简图及说明 典型应用电路示意图。在该图中,LCD类型和键盘种类及数目的选择、下拉电阻的数值大小都必须认真

以太网通信接口电路设计规范

目录 1目的 (3) 2范围 (3) 3定义 (3) 3.1以太网名词范围定义 (3) 3.2缩略语和英文名词解释 (3) 4引用标准和参考资料 (4) 5以太网物理层电路设计规范 (4) 5.1:10M物理层芯片特点 (4) 5.1.1:10M物理层芯片的分层模型 (4) 5.1.2:10M物理层芯片的接口 (5) 5.1.3:10M物理层芯片的发展 (6) 5.2:100M物理层芯片特点 (6) 5.2.1:100M物理层芯片和10M物理层芯片的不同 (6) 5.2.2:100M物理层芯片的分层模型 (6) 5.2.3:100M物理层数据的发送和接收过程 (8) 5.2.4:100M物理层芯片的寄存器分析 (8) 5.2.5:100M物理层芯片的自协商技术 (10) 5.2.5.1:自商技术概述 (10) 5.2.5.2:自协商技术的功能规范 (11) 5.2.5.3:自协商技术中的信息编码 (11) 5.2.5.4:自协商功能的寄存器控制 (14) 5.2.6:100M物理层芯片的接口信号管脚 (15) 5.3:典型物理层器件分析 (16) 5.4:多口物理层器件分析 (16) 5.4.1:多口物理层器件的介绍 (16) 5.4.2:典型多口物理层器件分析。 (17) 6以太网MAC层接口电路设计规范 (17) 6.1:单口MAC层芯片简介 (17) 6.2:以太网MAC层的技术标准 (18) 6.3:单口MAC层芯片的模块和接口 (19) 6.4:单口MAC层芯片的使用范例 (20) 71000M以太网(单口)接口电路设计规范 (21) 8以太网交换芯片电路设计规范 (21) 8.1:以太网交换芯片的特点 (21) 8.1.1:以太网交换芯片的发展过程 (21) 8.1.2:以太网交换芯片的特性 (22) 8.2:以太网交换芯片的接口 (22) 8.3:MII接口分析 (23) 8.3.1:MII发送数据信号接口 (24) 8.3.2:MII接收数据信号接口 (25) 8.3.3:PHY侧状态指示信号接口 (25) 8.3.4:MII的管理信号MDIO接口 (25) 8.4:以太网交换芯片电路设计要点 (27) 8.5:以太网交换芯片典型电路 (27) 8.5.1:以太网交换芯片典型电路一 (28)

基于CAN总线的接口电路设计_侯明

2008年第07期,第41卷 通 信 技 术 Vol.41,No.07,2008 总第199期Communications Technology No.199,Totally 基于CAN总线的接口电路设计 侯 明①, 杜 奕② (①昆明理工大学 信息工程与自动化学院,云南 昆明 650031;②昆明理工大学 应用技术学院,云南 昆明 650031) 【摘要】文中介绍了CAN总线的主要性能及特点,CAN总线在实际工业应用中的总体结构,同时给出了CAN总线协议转换器的硬件设计方法和通信协议。主要研究了CAN总线接口电路设计,所设计的总线接口电路由微处理器、CAN控制器、CAN总线收发器组成,并且详细介绍了CAN控制器、CAN收发器的功能以及CAN总线接口的硬件电路和硬件条件下的软件设计,为后续CAN 总线接口电路的应用打下了基础。 【关键词】CAN总线;SJA1000;接口 【中图分类号】TP29 【文献标识码】A【文章编号】1002-0802(2008)07-0138-03 Interface Circuit Design Based on CAN Bus HOU Ming①, DU Yi② (①College of Information Engineering and Automation Kunming University of Science and Engineering, Kunming Yunnan 650003, China; ②College of Applied Technology, Kunming University of Science and Engineering Kunming Yunnan 650003, China) 【Abstract】In this paper, the main CAN bus performance and features are presented, including the general structure of the CAN bus used in industrial application, and the hardware design methods of the CAN bus protocol converters and communication protocols are also given. This paper discusses the main interface circuit design of CAN Bus, which consists of microprocessor, CAN controller, CAN bus transceiver, and describes in detail the CAN controller, CAN transceiver of the CAN Bus interface, including the features of the hardware and the software design under the conditions of the hardware design. All these lay a foundation for the application of follow-up CAN. 【Key words】CAN bus; SJA1000; interface 0 引言 CAN(Controller Area Network)即控制器局域网络,是一种高性能、高可靠性、易开发和低成本的现场总线,是德国Bosch公司为解决现代汽车中众多的控制与测试仪器之间的数据交换而开发的一种串行数据通信协议。它是一种多主总线,通信介质可以是双绞线、同轴电缆或光导纤维,通信速率可达1 Mb/s,距离可达10 km。CAN协议的一个最大特点是废除了传统的站地址编码,而代之以对通信数据块进行编码,使网络内的节点个数在理论上不受限制。由于CAN总线具有较强的纠错能力,支持差分收发,因而适合高干扰环境,并具有较远的传输距离。因此,CAN协议对于许多领域的分布式测控很有吸引力。 CAN总线以目前技术条件较成熟的IS0/0SI模型为基础,与别的网络相比,它的信息传递的格式为报文。报文的长度可以不同,但都是有限的。当总线空闲时任何已连接的单元都可以开始发新的报文,报文以全网广播方式散发出去。各接收站根据报文的内容而不是地址进行判决,不需在信息中加入地址。 目前汽车上的网络连接方式主要采用2条CAN,一条用于驱动系统的高速CAN,速率达到500 kb/s;另一条用于车身系统的低速CAN,速率是100 kb/s。驱动系统CAN主要连接对象是发动机控制器(ECU)、ABS控制器、安全气囊控制器、组合仪表等等,它们的基本特征相同,都是控制与汽车行驶直接相关的系统。车身系统CAN主要连接和控制的汽车 收稿日期:2008-05-19。 作者简介:侯 明(1974-),男,讲师,主要研究方向为计算机硬件控制;杜 奕(1977-),男,讲师,主要研究方向为信息融合。 138

用户接口电路的设计

黄冈师范学院程控交换提高型实验 2011年5 月11日

目录 中文摘要 英文摘要 一.引言 1.1用户接口电路简介 (3) 1.2课程设计的目的 (3) 1.3课程设计内容 (3) 1.4课程设计要求 (4) 二.电路工作过程 2.1用户接口电路功能 (4) 2.2PBL38710芯片功能及使用 (5) 2.3PCM编译码器TP3067 (6) 三.用户线接口电路原理 3.1用户线接口电路原理 (7) 四.总结和心得 (9) 五.参考文献 (9)

摘要:利用用户线接口电路选用的是PBL38710和TP3067芯片对用户接口电路进行设计,PBL38710是2/4线厚膜混合用户线接口电路,PCM编译码电路中的器件为美国国家半导体公司的TP3067。 summary::line circuit is pbl38710 and tp3067 chips to the user interface design, pbl38710 circuitry for two to four lines of the user interface to a thick wire circuits, and pcm compiled code in the circuit device for the united nations. the semiconductor firms tp3067。 关键词:用户接口、PBL38710、TP3067 Keywords :user interface, PBL38710, TP3067 一、引言 1.1. 用户接口电路 用户电路也可称为用户线接口电路。任何交换机都具有用户线接口电路。根据用户电话机的不同类型,用户接口电路分为模拟用户接口电路和数字用户接口电路两种。 模拟用户线接口电路在实现上的最大压力是应能承受馈电、铃流和外界干扰等高压大电流的冲击,基于实现和应用上的考虑,通常将BORSCHT功能中过压保护由外接元器件完成,编译码器部分另外单成一体,集成为编译码器(CODEC),其余功能由集成模拟SLIC完成。 用户电路的作用是实现各种用户线与交换之间的连接,通常又称为用户线接口电路(SLIC,Subscriber Line Interface Circuit)。根据交换机制式和应用环境的不同,用户电路也有多种类型,对于程控数字交换机来说,目前主要有与模拟话机连接的模拟用户线电路(ALC)及与数字话机,数据终端(或终端适配器)连接的数字用户线电路(DLC)。 1.2 课程设计目的 1、全面了解用户电路的功能及其实现方法 2、熟悉用户电路接口电路PBL3871和PCM编译码集成电路TP3067的电路组成和使用方法。 3、掌握模拟用户接口电路和PCM编译码器在程控交换机中的作用,进一步加深对用户模块七个功能BORSCHT的理解。

I2C总线接口电路设计..

FPGA与I2C总线器件接口电路设计 利用FPGA模拟I2C总线协议对I2C总线接口器件AT24C256 进行读写操作。利用按键输入读写命令和相应的地址、数据,对芯片进行读写操作,读写的数据用数码管显示。 一、I2C总线接口电路设计分析 1. I2C 总线协议 I2C 总线的两根通信线,一根是串行数据线SDA,另一根是串行时钟线SCL。多个符合I2C总线标准的器件都可以通过同一条I2C总线进行通信,而不需要额外的地址译码器。每个连接到总线上的器件都有一个唯一的地址作为识别的标志,都可以发送或接收数据。I2C 总线通信速率受主机控制,标准模式下可达100kbit/s。 一般具有I2C总线的器件其SDA、SCL引脚都为集电极(或漏极)开路结构。因此实际使用时,SDA 和SCL信号线必须加3~10K的上拉电阻。总线空闲时均保持高平。I2C总线接法如图1所示。 图1 I2C总线连接示意图 (1) I2C的主机和从机,发送器和接收器 产生I2C总线时钟信号和起始、停止控制信号的器件,称为主机,被主机寻址的器件称为从机。 任何将数据传送到I2C总线的器件称为发送器,任何从I2C总线接收数据的器件称为接收器。 主机和从机都可作为发送数据器件和接收数据器件。 (2) I2C 总线上数据的有效性: 时钟线SCL为高电平时,数据线SDA的任何电平变化将被看作总线的起始或停止信号; 在数据传送过程中,当时钟线SCL为高电平时,数据线SDA必须保持稳定状态,不允许有跳变;数据线SDA的状态只能在SCL低电平期间才能改变。即进行串行传送数据时,在SCL高电平期间传送位数据,低电平期间准备数据。 (3) 从机地址 I2C总线不需要额外的片选信号或地址译码。多个I2C总线接口器件可连接到一条I2C总线上,它们之间通过地址来区分。主机是主控制器件,只有一个主机的不需要地址。其它器件均为从机,均有器件地址,但必须保证同一条I2C总线上的器件地址不能重复。一般从机地址由7位地址位和1位读写位组成,地址位为高7位,读写位为最低位。读写位为0时,表示主机将向从机写入数据;读写位为1时,表示主机将要从从机读取数据。 (4) I2C 总线的通信时序

电路设计中必须掌握的7个常用接口知识

电路设计中必须掌握的7个常用接口知识 我们知道,在电路系统的各个子模块进行数据交换时可能会存在一些问题导致信号无法正常、高质量地“流通”,例如有时电路子模块各自的工作时序有偏差(如CPU与外设)或者各自的信号类型不一致(如传感器检测光信号)等,这时我们应该考虑通过相应的接口方式来很好地处理这个问题。 下面就电路设计中7个常用的接口类型的关键点进行说明一下: (1)TTL电平接口: 这个接口类型基本是老生常谈的吧,从上大学学习模拟电路、数字电路开始,对于一般的电路设计,TTL电平接口基本就脱不了“干系”!它的速度一般限制在30MHz以内,这是由于BJT的输入端存在几个pF的输入电容的缘故(构成一个LPF),输入信号超过一定频率的话,信号就将“丢失”。它的驱动能力一般最大为几十个毫安。正常工作的信号电压一般较高,要是把它和信号电压较低的ECL电路接近时会产生比较明显的串扰问题。 (2)CMOS电平接口: 我们对它也不陌生,也是经常和它打交道了,一些关于CMOS的半导体特性在这里就不必啰嗦了。许多人都知道的是,正常情况下CMOS的功耗和抗干扰能力远优于TTL。但是!鲜为人知的是,在高转换频率时,CMOS系列实际上却比TTL消耗更多的功率,至于为什么是这样,请去问半导体物理理论吧。由于CMOS的工作电压目前已经可以很小了,有的FPGA 内核工作电压甚至接近1.5V,这样就使得电平之间的噪声容限比TTL小了很多,因此更加加重了由于电压波动而引发的信号判断错误。众所周知,CMOS电路的输入阻抗是很高的,因此,它的耦合电容容量可以很小,而不需要使用大的电解电容器了。由于CMOS电路通常驱动能力较弱,所以必须先进行TTL转换后再驱动ECL电路。此外,设计CMOS接口电路时,要注意避免容性负载过重,否则的话会使得上升时间变慢,而且驱动器件的功耗也将增加(因为容性负载并不耗费功率)。 (3)ECL电平接口: 这可是计算机系统内部的老朋友啊!因为它的速度“跑”得够快,甚至可以跑到几百MHz!这是由于ECL内部的BJT在导通时并没有处于饱和状态,这样就可以减少BJT的导通和截止时间,工作速度自然也就可以提上去了。But,这是要付出代价的!它的致命伤:功耗较大!它引发的EMI问题也就值得考虑了,抗干扰能力也就好不到哪去了,要是谁能够折中好这两点因素的话,那么他(她)就该发大财了。还有要注意的是,一般ECL集成电路是需要负电源供电的,也就是说它的输出电压为负值,这时就需要专门的电平移动电路了。 (4)RS-232电平接口: 玩电子技术的基本没有谁不知道它的了(除非他或她只是电子技术专业的“门外汉”)。它是低速串行通信接口标准,要注意的是,它的电平标准有点“反常”:高电平为-12V,而低电平为+12V。So,当我们试图通过计算机与外设进行通信时,一个电平转换芯片MAX232自然是少不了的了。但是我们得清醒地意识到它的一些缺点,例如数据传输速度还是比较慢、传输距离也较短等。 (5)差分平衡电平接口: 它是用一对接线端A和B的相对输出电压(uA-uB)来表示信号的,一般情况下,这个差分信号会在信号传输时经过一个复杂的噪声环境,导致两根线上都产生基本上相同数量的噪声,而在接收端将会把噪声的能量给抵消掉,因此它能够实现较远距离、较高速率的传输。工业上常用的RS-485接口采用的就是差分传输方式,它具有很好的抗共模干扰能力。 (6)光隔离接口: 光电耦合是以光信号为媒介来实现电信号的耦合和传递的,它的“好处”就是能够实现电气隔