(完整word版)西工大,西电孙肖子版模电第六章复频域系统函数与系统模拟--答案

第六章 习 题

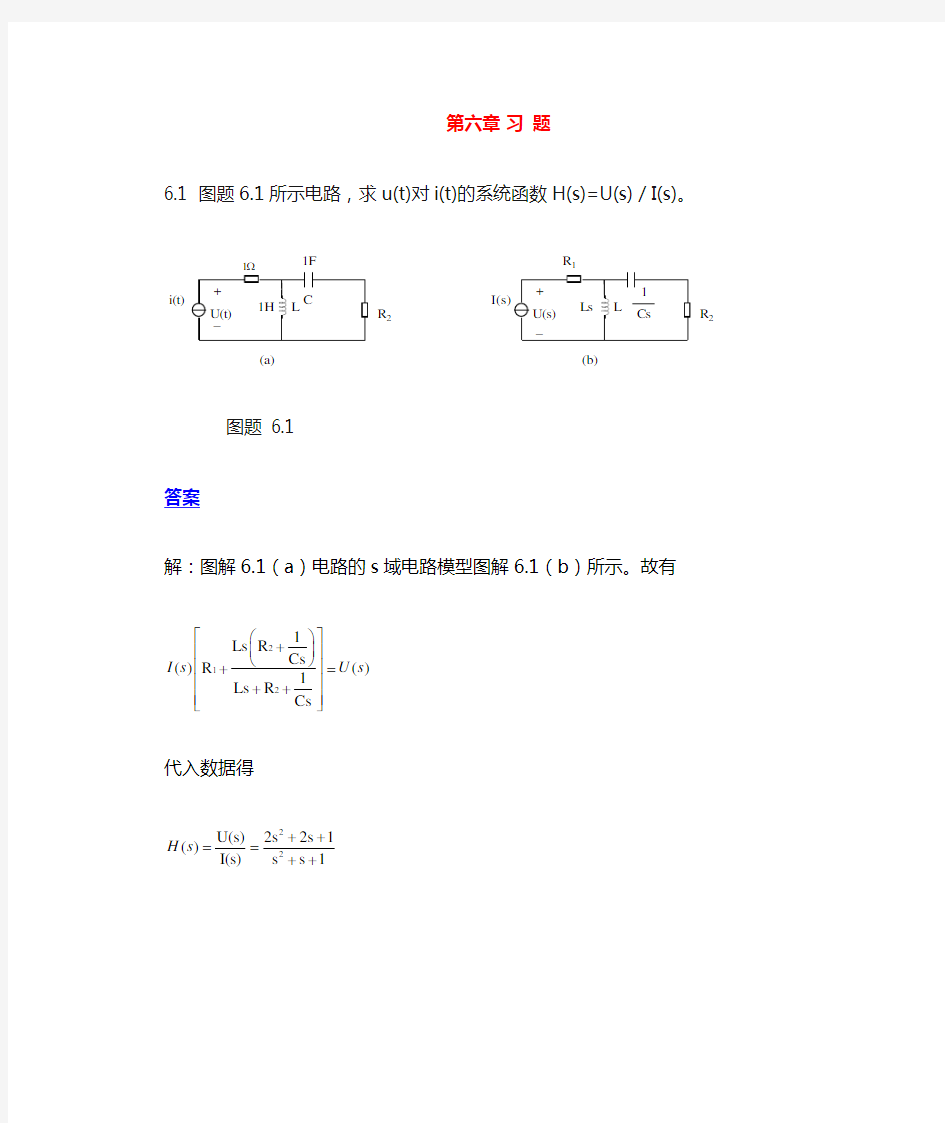

6.1 图题6.1所示电路,求u(t)对i(t)的系统函数H(s)=U(s)

/I(s)。

i(t)

(a)

R 2

1F

I(s)

(b)

R 2

R

图题 6.1

答案

解:图解6.1(a )电路的s 域电路模型图解6.1(b )所示。故

有

2121Ls R Cs ()R ()1Ls R Cs I s U s ???

?+ ???????+

=??++

????

代入数据得

22

U(s)2s 2s 1()I(s)s s 1H s ++==++

(a)

F 1Ω

1

R1

(b)

1

图题 6.2

6.2 图解6.2(a )所示电路,求()t u 2对()t u 1的

系统函数)s (U )

s (U )s (H 12=

。

答案

解:图解6.2(a )所示电路的s 域电路模型如图解6.2(b )所

示。故有

22

122

U (s)Ls R H(s)1U (s)Ls R R

Cs +=

=

+++

代入数据得

()()35s s 2s

s s U s U )s (H 2212+++=

=

6.3 已知系统的单位冲激响应

5()5()t h t te U t -=,零状态响应55()()2()5()t t y t U t e U t te U t --=++。求系统的激励

f(t)。 答案

解:

()5s 5s h +=

()25s 55s 2s 1)s (Y ++

++=

故得激励f(t)的像函数为

()5s 1s 1535s 55s 55s 2s 1)s (H )s (Y )s (F 2++

+=+++

++==

故得

()-5t -5t 33

()δ(t)U(t)e U(t)δ(t)1e U(t)

55f t =++=++

6.4 已知系统函数55s s 5

s )s (H 22+++=,初始状态为

()00y =-

,()

-20y /=-。

(1).求系统的单位冲激响应h(t);

(2). 当激励f(t)=δ(t)时,求系统的全响应y(t); (3)当激励f(t)=U(t)时,求系统的全响应y(t)。

答案

解: (1)

()()()41s 2

12s 1s 2s 152s s s 2155s s 5s )s (H 22222+++

+++-+=++-+=+++=

故

())t (U 2sin2t cos2t 2e -δ(t))t (sinU e )t (costU 2e -δ(t)h(t)-2t -2t -2t -=+=

(2)系统的微分方程为

()()()()()t 5f t f t 5y t 2y t y //////+=++

对上式等号两边同时求拉普拉斯变换,并考虑到拉普拉斯变换的

微分性质,有

()()()

s

(5F )s (F s )s (5Y 02y )s (2sY 0y 0sy )s (Y s 2/2+=+-+----- ①

今 (),20y ,0)0(y ,1)s (F /-===-

- 代入上式得

()()41s 1s 2152s s 3s )s (Y 222+++-=+++=

故得全响应为

)t (costU 2e -δ(t))t (y -t =

(3)将 ()

2

0y ,0)0(y ,s 1

)s (F /-===-- 代入上式①,有

()

()41s 2

2s 155s s s 52s s )s (Y 222++?

-=+++-=

故得全响应为

()

)t (U sin2t 2e 1)t (y t --=

6.5 图题6.5所示电路。 (1)求电路的单位冲激响应h(t);

(2)今欲使电路的零输入响应x u (t)=h(t),求电路的初始状态

()-0i 和()-0u ;

(3)今欲使电路的单位阶跃响应g(t)=U(t),求电路的初始状态

()

-0i 和()

-0u 。

答案

解(1)零状态条件下的s 域电路模型如图解6.5(b )所示。故

根据该图得

()()()2

21s 1

12s s 1s 1s 2s

1s F s U )s (H +=

++=++==

故得单位冲激响应为

()V )t (U te )t (h t -=

(2)非零状态条件下求零输入响应()t u x 的s 域电路模型如图6.5

(c )所示。故

()()()

()

-

-

-+?++-=0u s 1s 1s 1s 20u s 1

0i s u x

+

-

(a)

)

s (U

(b)

)

s (U

+

-

(c)

)

s ()

0(i -

+

-

(d)

)

s ()

0(i -+

图解6.5

依题意要求,应使()),s (H s U x =即应有

()2

1s 1)0(u s 1s 1s 1s 2)

0(u s 1

)0(i +=+?++----

从而有

(2)(0)(0)1s u i --++= (0)0,(0)1u i A --==

(3)非零状态条件下求电路单位阶跃响应g (t )的s 域电路模

型,如图解6.5(d )所示。故

)

0(u s 1s 1s 1s 2)

0(u s 1

)0(i s 1)s (G ---+?++-+=

依题意要求,应使

,

s 1

)s (G =即应有 s 1)0(u s 1s 1s 1s 2)

0(u s 1

)0(i s 1=

+?++-+---

从而有 ()()()2s 0i 0u 2s +=++-

-

故得 ()()00i ,1V 0u ==-

-

6.6 图题6.6所示电路。(1)求

()()21U s ()U s H s =

;

(2)若()()1F,C ,V )t (cos2tU t u 1==求零状态响应()t u 2;

(3)在()t u 1不变的条件下,为使响应()t u 2中不存在正弦稳态响

应,求C 的值及此时的响应()t u 2。

()

a

答案

()

s ()

b

解(1)图解6.6(a )电路的s 域电路模型如图题6.6(b )所示。

故

()C

1s C 2s C

1s Cs

1

s Cs 1s 212

1s H 22++

+=+?+

=

(2)

(),1F C ,4s s

s U 2

1=+=

则

()()22221s 1

s 12s s 1s s H ++=

+++=

故

()()()()()()j2s K j2s K 1s K 1s K 4s s 1s 1s s U s H s U 32

1221122212-+

+++++=+?++==

()

()(

)

()521s 4

s 1s s 1s

K 2

222

11-

=++++=

(1s -=)

(

)

()(

)

()25

161s 4s 1s s 1s ds d K 1s 222212=?

?????++++=-=

()

()()()()103

J2s j2s j2s 1s s 1s

K j2

s 22

2=

+-+++=

-=。

1.53-

10

3

K K 23=

=。

1.53-

故得

()t t j2t j53.1j2t j53.1221633u t te e e e e e 5251010----=-+++=

。。

()()()t 383t e cos 2t 53.1u t V 255-?

??

????-++?? ?

??????14424431

4243正弦稳态响应瞬态响应

(3)

()()()4

s s C

1

s C 2s C

1s s U s H s U 22212+?

++

+=

=

由此式可见,欲使()t u 2中不存在正弦稳态响应,就必须有

,4s C 1

s 22+=+

故得25F .0C =。代入上式有

()324s 077

.0324s 077.148s s s s U 22-+-+

++=++=

故得

()()()()()V t U 077e .0077e .1t u t

324t 3242???

?????-=--+-4444434444421瞬态响应

6.7 图题6.7所示电路。

(1)求

()

()s U s U )s (H 12=

;

(2)求K 满足什么条件时系统稳定; (3)求K=2时,系统的单位冲激响应h(t)。

)

图解 6.7

答案

解(1)对节点①列写KCL 方程为

()()s U s sKU -δ(s)s s 1s 111=?

?????????+++

又

()???

??+=

s 11s 1s U δ(s)

()()s KU s U 2=

以上三式联解得

()()()()1s K 3s K

s U s U s H 2

12+-+==

(2)当K <3时,()s H 的极点位于s 平面的左半开平面,系统稳

定。

(3)当K=2时,

()222222321s 2

3

32

22321s 21s s 2s H ????

??+??? ??+??=???? ??+??? ??+=++=

故得

()

V )t (tU 23

sin e 34)t (h t 21-=

6.8 已知系统函数

64s s 5

s )s (H 2+++=

。

(1)写出描述系统响应y(t)与激励f(t)关系的微分方程; (2)画出系统的一种时域模拟图;

(3)若系统的初始状态为()

10y ,2)0(y /==--,激励

()t U e )t (f t -=,求系统的零状态响应()t y f ,零输入响应()t y x ,

全响应y(t)。

答案

解(1)因

()()()65s s 5s s F s Y s H 2

+++==

故得系统的微分方程为

()()()()()t 5f t f t 6y t 5y t y ////+=++

(2)该系统的一种时域模拟图如图题6.8所示。

图解6.8

(3)求零状态响应()t y f

()1s 1s F +=

故

()()()()

()()()3s 1

2s 31s 23s 2s 1s 5s 65s s 1s 5s s H s F Y 2f ++

+-++=++++=++++=

=

故得

()()

()t U e 3e 2e t y 3t

2t t f ---+-= (4)求零输入响应()t y x

系统的特征方程为065s s 2

=++,故得特征根为.

3p 2,p 21-=-=故得零输入响应的通解形式为

()3t 22t 1x e A e A t y --+=

又 ()3t 22t 1x

/

e 3A e 2A t y

----=

故有

{()()()()

13A 2A 0y 0y 2

A A 0y 0yy 21//

x 21x =--===+==+

+++ 联解得5A ,7A 21-==故得零输入响应为

()()()()()()

()4

4444444211443

4421瞬态响应

自由响应2

t U 4e 4e t U e 3e 2e t U 5e 7e t y 3t 2t 3t 2t t 3t 2t x -------+-=+-+-=6.9 已知系统的框图如图题6.9所示,求系统函数

()()()s F s Y s H =

,

并画出一种s 域模拟图。

)

s

()

a

答案

()

b

解

()()()()s Y

2

s

1

s

Y

s

1

1

s

1

s

Y

s

1

s

F=

+

?

?

?

?

?

?

+

+

??

?

??

?

+

故解得

()

2

s

3s

s

s

s

H

2

3-

+

+

=

其中一种s域模拟如图解6.9(b)所示。

6.10已知系统的框图如图题6.10所示。

(1)欲使系统函数

()()

()6

5s

s

s

s

F

s

Y

s

H

2+

+

=

=

,试求a,b的值;

(2)当a=2时,欲使系统为稳定系统,求b的取值范围;

(3)若系统函数仍为(1)中的H(s),求系统的单位阶跃响应g(t)。

图题6.10

答案

解(1)

()()

()()

()s

Y

a

s

1

s

s

s

Y

s

b

s

F=

+

+

??

?

??

?

-

解得

()()

()()()b

a

s

1

a

s

s

s

F

s

Y

s

H

2+

+

+

+

=

=

故有

()()b

a

s

1

a

s

s

6

5s

s

s

2

2+

+

+

+

=

+

+

故有 ??

?=+=+6b a 51a 解得a=4,b=2.

当a=2时,

()b 23s s s

s H 2+++=

故欲系统为稳定系统,就必须有2+b >0,b >-2.

(3)

()s 1

s F =

,故

()()()3s 1

-2s 165s s 1s 165s s s s F s H s G 22++

+=++=?++=

=

故得系统的单位阶跃响应为

()()

()t U e e t g 3t 2t ---=

6.11 已知系统的框图如图题6.11所示。

(1)求系统函数

()()()s F s Y s H =

;

(2)欲使系统为稳定系统,求K 的取值范围;

(3)在临界稳定条件下,求系统的单位冲激响应h(t)。

)

s

图题6.11

答案

解(1)

()()[]

()s Y K 44s s s

s Y s F 2

=?+++

解得

()()()()4s K 4s Ks s F s Y s H 2

+-+==

(2)欲为稳定系统,则必须有0k 4?-,故4k ?。 (3)当K=4时 ,系统为临稳定,即

()4s 4s s H 2+=

故得临界稳定条件下的单位冲激响应应为

()()t 4cos2tU t h =

6.12 图题6.12所示为H(s)的零、极点分布图,且知

()

20h =+。求该系统的H(s)。

答案

图题6.12

解

()()()()()()()()()()()()()()279s 3s s 5

4s s H

9s 3s 12s H j3s j3s 3s j12s j12s H p s p s p s z s z s H s H 232022

00321210+++++=++++=+-+++-+=-----=

又有

2279s 3s s 5

4s s lim H )s (lim sH )0(h 2

320S =+++++==+

即

2)0(h =

故得

()

279s 3s s 5

4s s 2)s (H 23

2+++++=

6.13 已知系统的微分方程为

()()()()()()t f t f t y t y t y t y 3485///////+=+++

(1)求系统函数

()()()s F s Y s H =

;

(2)画出系统的三种形式的信号流图。

答案

解 (1)

()()()()()223113

4852+++=

++++==

s s s s s s s s F s Y s H

(2)直接形式的信号流图如图题6.13(a )所示。

(3)

()212311+?

++?+=

s s s s s H

级联形式的信号流图如图题6.13(b )所示。 (4)

()()??? ??-+-+++=+-++-++=

22121122221122s s s s s s s H

并联形式的信号流图如图题6.13(c )所示。

(a)

1

-2

(b)

s

1

2s -1

(c)

6.14 已知系统的信号流图如图题6.14(a )所示。

(1) 求系统函数

()()

()s F s Y s H =

及单位冲激响应

)(t h ;

(2) 写出系统的微分方程;

(3) 画出与)(s H 相对应的一种等效电路,并求

出电路元件的值

(a )

答案

解 (1)

()()()()()11

3133432+=

+++=+++==

s s s s s s s s F s Y s H

故得系统的单位冲激响应为

)()(t U e t h t -=

(2)系统的微分方程为

()()()()()t f t f t y t y t y 334////+=++ 注意,写系统的微分方程时,)(s H 分子与分母中的公因式不能约

去。

(3)

s s s

s

s s

s H 313313431)(+

+++=

+

++

=

根据上式即可画出与之对应的一种等效电路,如图题6.14(b )

所示,与之相对应的时域电路则如图

题6.14(c )所示。

(a )

(b)

Ω

3)

(c)

Ω

3)

图解 6 -

14

6.15 图题6.15(a )所示系统,其中

()()(),,31s

e s H t U t h -==大系统的()()12)(--=t U t t h 。求子系统的单位

冲激响应()t h 2。

解 图题6.15(a )系统的s 域系统如图6.15(b )所示。故大

系统的系统函数为

西北工业大学数电实验报告一Quartus和 Multisim

数字电子技术基础 实验报告 题目:实验一TTL集成门电路逻辑变换 小组成员: 小组成员:

实验一TTL集成门电路逻辑变换 一、实验目的 通过完成所要求的实验内容,来熟练掌握运用TTL集成门电路逻辑变换的基本原理,充分了解 Multisim 软件的仿真技术和QuartusII 软件的绘制原理图、编译程序、波形仿真等功能及将程序写入开发板的全体流程步骤,深入学习数字电路在实践运用中所面临的场景,进而为后续对数字电路更深层次的使用及实验打下良好铺垫。 二、实验要求 要求一:测试与非门逻辑功能。用MULTISIM软件仿真后,再用 FPGA实现电路测试逻辑功能 要求二:用与非门实现“与”逻辑。用 MULTISIM软件仿真后,再用 FPGA实现电路测试逻辑功能 要求三:用与非门实现“或”逻辑。用 MULTISIM软件仿真后,再用 FPGA实现电路测试逻辑功能 要求四:用与非门实现“异或”逻辑。用 MULTISIM软件仿真后,再用 FPGA实现电路测试逻辑功能 要求五:用门电路设计实现一位全加器。用MULTISIM软件仿真后,再用 FPGA 实现电路测试逻辑功能 三、实验设备 (1)电脑一台; (2)数字电路实验箱; (3)数据线一根。

四、实验原理 Multisim 的模拟电路编程原理 Quartus II的模拟电路编译、波形仿真及目标器件写入的基本应用数字电路逻辑表达式转换的基本知识 五、实验内容 1、(要求一) (1)逻辑表达式变换过程 (2)原理图(Multisim和QuartusII中绘制的原理图): (3)波形仿真: (4)记录电路输出结果 2、(要求二) (1)逻辑表达式变换过程 (2)原理图(Multisim和QuartusII中绘制的原理图): (3)波形仿真:

西北工业大学材料科学与工程专业简介

材料科学与工程 1.培养目标 培养在金属材料、无机非金属材料、光电信息功能材料、电子材料与器件、复合材料领域的科学与工程方面具有较宽基础知识、从事材料设计、研究、开发和技术管理的高级工程技术人才。 2.课程设置 主要课程:材料科学基础、物理化学、材料工程基础、材料现代研究方法、金属材料、光电材料、功能材料、复合材料、电子技术与控制、计算机系列课程等。 3.深造与就业方向 毕业生可继续攻读本专业及相关专业的硕士研究生,近三年本科考取研究生比例60%以上。 毕业生就业实行双向选择,毕业后可到研究所、企业从事科学研究、设计、生产管理、工程技术应用及高等院校的教学工作。 4.学制/学位 本科四年制/工学学士 材料科学与工程专业四年制本科培养方案 Cultivating Scheme of 4-year Undergraduate Course- Material and Enginee ring Speciality 一、培养目标 本专业培养具备金属材料及无机非金属材料科学与工程方面的知识,能在材料制备、成型加工、材料结构研究与分析等领域从事科学研究、技术开发、工艺和设备设计、生产及经营管理等方面工作的高级工程技术人才。

Ⅰ.Scheme Objectives The objectives of this scheme are to provide students of this major with t he technology and engineering knowledge of metal and inorganic-nonmetal mat erials, in order to make them outstanding engineers who are capable of underta king works of science research, technique and appliance design, manufacturing process management. 二、培养要求 本专业学生主要学习材料科学及各类材料加工工艺的基础理论与技术和有关设备的设计方法,受到现代机械工程师的基本训练,具有从事材料制备、加工成型研究、进行各类材料加工工艺及设备设计、生产组织管理的基本能力。Ⅱ.Requirements Students of this speciality shall learn the basic theories of material science and methods of material processing and how to design related equipment. The y also shall be trained to be modern mechanic engineers who are capable of d oing research works about material fabricating, forming, processing and related equipment design. At same time, they also should have the ability of fundame ntal management of manufacture process. 毕业生应获得以下几方面的知识和能力: Student of this major must fulfill the following requirements: (1)具有较扎实的自然科学基础,较好的人文、艺术和社会科学基础及正确运用本国语言、文字的表达能力; (2)具有较系统地掌握本专业领域宽广的理论基础知识,主要包括材料科学、力学、机械学、电工与电子技术、计算机系列课程、热加工工艺基础、自动化基础、市场经济及企业管理等基础知识; (3)具有本专业必需的计算、测试、文献检索能力和基本工艺操作等基本技能及较强的计算机和外语应用能力;

西北工业大学博士入学考试材料物理、材料综合复习题

2001博士秋季入学考试试题 1(16分)共价键的数目(为配位电子数)和方向(电子云密度最大方向)取决于什么?利用杂化轨道理论解释金刚石(sp 3)结构中的共价键,并计算碳的sp 3键的键角(109.28)。 2(12分)离子晶体在平衡时的结合能为:)11(80020n R NMe U E b -==πε,M 称为马德隆常数。试解释M 的意义。(西工大固体物理P41;M 是与晶体结构有关的常数) 3(12分)试比较经典的和量子的金属自由电子理论。(方俊鑫P285;黄昆P275) 4(12分)举例说明能带理论在解释固体材料有关性质(绝缘、半导、导体)、设计新材料中的应用。(西工大P111) 5(12分)解释金属及半导体的电阻率(高温时、低温时)随温度变化的规律。(西工大P192)

6(12分)分析固体表面的成分可采用那些分析技术和方法。(电子能谱:光电子能谱、俄歇电子、离子中和谱;离子谱:低能离子散射、高能离子散射、二次离子质谱、溅射中性粒子谱、致脱附离子角分布) 7(12分)晶体致的电缺陷有那些类型?分析其形成原因及对晶体性质的影响。(西工大P149、151) 8(12分)简述物质超到态的主要特征。(西工大P206、零电阻,充合抗磁) 答:1,低能电子衍射;2,表面敏感扩展X 吸收精细结构;3,场离子显微镜;4,电子显微镜;5,投射电子显微镜,扫描电子显微镜;6,扫描隧道显微镜;7,原子力显微镜;8,摩擦力显微镜 2001博士春季入学考试试题 1(16)N 对离子组成的NaCl 晶体的总互作用势能为 ??????-=R e R B N R U n 024)(πεα 其中α是马德隆常数,B 为晶格参量,n 为玻恩指数。 (1) 证明平衡原子间距为n e B R n 2 0104απε=- (2) 证明平衡时的结合能为)11(4)(0020n R Ne R U --=πεα

西工大数字集成电路实验报告_实验2反相器代码

1. 2. 计算出这个电路的V OH V OL 及V IH V IL 。(计算可先排除速度饱和的 可能) V in =0时,V OH = V in=时,假设NMOS 工作在临界饱和区: A I V R I v V V V A I V V L W K I D out L D T in out D T in D 61142`1073.55.207.243.05.21039.7)(2/--?=?+=?????=-=-=?=?-?=这样的话根据 D D I I <1,器件实际工作在线性区 ?????????=+=--=v V V R I V V V V L W K I in OL L D OL OL T in D 5.25.2]2)[(2` 6`10115-?=K 将, 5.0/5.1=L W ,43.0=T V 代入kohm R L 75= 解得: =OL V 由图得:V OH =, V OL =. 当out in V V =时,NMOS 工作在饱和区 ?????+=-?=out L D T in D V R I V V L W K I 5.2)(2/2`

反相器阈值电压===out in M V V V 此时 -6.8978)43.0(875.255.2,)43.0(9375.125.22=--== --=in Vin Vout in out V d d g V V ???????=--==+=0.5458||0.9082||g V V V V g V V V M OH M IL M M IH 由图得:V IH =, V IL =. SP 文件: .TITLE CMOS INVERTER .options probe .options tnom=25 .options ingold=2 limpts=30000 method=gear .options lvltim=2 imax=20 gmindc= .protect .lib'C:\synopsys\' TT .unprotect .global vdd Mn out in 0 0 NMOS W= L= *(工艺中要求尺寸最大) RL OUT VDD 75k VDD VDD 0 VIN IN 0 0

西工大2017年数字集成电路设计实验课实验一

实验四 译码器的设计及延迟估算 1、 设计译码器并估算延迟 设计一个用于16bit 寄存器堆的译码器,每一个寄存器有32bit 的宽度,每个bit 的寄存器单元形成的负载可以等效为3个单位化的晶体管(后面提到负载都为单位化后的负载)。 译码器的结构可参考典型的4-16译码器 译码器和寄存器堆的连接情况(Output 输出为1的一行寄存器被选中) ① 假定4个寄存器地址位的正反8个输入信号,每个信号的输入负载可以等效为10。确定 译码器的级数,并计算相关逻辑努力,以此来确定每一级中晶体管的尺寸(相当于多少个单位化的晶体管)及整个译码电路的延迟(以单位反相器的延迟的本征延迟Tp0为单位)。 解: 96332,10int =?==ext g C C C ,9.696/10F ==? 假定每一级的逻辑努力:G=1,又因为分支努力(每个信号连接8个与非门): 81*8*1B ==, 路径努力8.7686.91=??==GFB H 所以,使用最优锥形系数就可得到最佳的电路级数39.36.3ln 8.76ln 6.3ln ln ===H N ,故N 取3级。 因为逻辑努力:2121G =??=,路径努力:6.15386.92=??==GFB H 则使得路径延时最小的门努力 36.5)6.153(3/1===N H h 。 所以: . 36.5136.5,68.2236.5, 36.5136.5132211=========g h f g h f g h f

故第一级晶体管尺寸为7.68 1036.5=?; 第二级尺寸为956.1768.27.6=?; 第三级尺寸为96244.9636.5956.17≈=?。 故延迟为:0008.22)36.5136.5436.51(p p p t t t =+++++= ② 如果在四个寄存器地址输入的时候,只有正信号,反信号必须从正信号来获得。每个正信号的输入的等效负载为20,使用与①中同样的译码结构,在这种条件下确定晶体管的大小并评估延迟(以单位反相器的延迟的本征延迟Tp0为单位)。 解:因为输入时通过两级反相器,使这两个反相器分摊原来单个反相器的等效扇出,将两级反相器等效为一级,故其逻辑努力32.236.5h ==, 故36.5,68.2,32.2,32.24321====f f f f 所以: 第一级尺寸为:()9.2832.210=?; 第二级尺寸为:728.632.29.2=?; 第三级尺寸为:03.1868.2728.6=?; 第四级尺寸为:65.9636.503.18=? 正信号通路的延迟为:()0036.2236.5136.5436.5132.2132.2p p p t t t =++++++++= 反信号通路情况与上问相同,延迟为0008.22)36.5136.5436.51(p p p t t t =+++++= 2、 根据单位反相器(NMOS:W=0.5u L=0.5u PMOS:W=1.8u L=0.5u),设计出实 际电路,并仿真1题中第一问的路径延迟。 设计出实际电路如下:

西北工业大学《材料科学基础》课后题答案

1. 有关晶面及晶向附图2.1所示。 2. 见附图2.2所示。 3. {100}=(100)十(010)+(001),共3个等价面。 {110}=(110)十(101)+(101)+(011)+(011)+(110),共6个等价面。

{111}=(111)+(111)+(111)+(111),共4个等价面。 )121()112()112()211()112()121( ) 211()121()211()211()121()112(}112{+++++++++++= 共12个等价面。 4. 单位晶胞的体积为V Cu =0.14 nm 3(或1.4×10-28m 3) 5. (1)0.088 nm ;(2)0.100 nm 。 6. Cu 原子的线密度为2.77×106个原子/mm 。 Fe 原子的线密度为3.50×106个原子/mm 。 7. 1.6l ×l013个原子/mm 2;1.14X1013个原子/mm 2;1.86×1013个原子/mm 2。 8. (1) 5.29×1028个矽原子/m 3; (2) 0.33。 9. 9. 0.4×10-18/个原子。 10. 1.06×1014倍。 11. (1) 这种看法不正确。在位错环运动移出晶体后,滑移面上、下两部分晶体相对移动的距离是由其柏氏矢量决定的。位错环的柏氏矢量为b ,故其相对滑移了一个b 的距离。 (2) A'B'为右螺型位错,C'D'为左螺型位错;B'C'为正刃型位错,D'A'为负刃型位错。位错运动移出晶体后滑移方向及滑移量如附图2.3所示。 12. (1)应沿滑移面上、下两部分晶体施加一切应力τ0,的方向应与de 位 错线平行。 (2)在上述切应力作用下,位错线de 将向左(或右)移动,即沿着与位错线de 垂直的方向(且在滑移面上)移动。在位错线沿滑移面旋转360°后,在晶体表面沿柏氏矢量方向产生宽度为一个b 的台阶。

西工大-数电实验-第二次实验-实验报告

数电实验2 一.实验目的 1.学习并掌握硬件描述语言(VHDL 或 Verilog HDL);熟悉门电路的逻辑功能,并用硬件描述语言实现门电路的设计。 2.熟悉中规模器件译码器的逻辑功能,用硬件描述语言实现其设计。 3.熟悉时序电路计数器的逻辑功能,用硬件描述语言实现其设计。 4.熟悉分频电路的逻辑功能,并用硬件描述语言实现其设计。 二.实验设备 1.Quartus开发环境 2.ED0开发板 三.实验内容 要求1:编写一个异或门逻辑电路,编译程序如下。 1)用 QuartusII 波形仿真验证; 2)下载到DE0 开发板验证。 要求2:编写一个将二进制码转换成 0-F 的七段码译码器。 1)用 QuartusII 波形仿真验证; 2)下载到 DE0 开发板,利用开发板上的数码管验证。 要求3:编写一个计数器。 1)用QuartusII 波形仿真验证; 2)下载到 DE0 开发板验证。 要求4:编写一个能实现占空比 50%的 5M 和50M 分频器即两个输出,输出信号频率分别为 10Hz 和 1Hz。 1)下载到 DE0 开发板验证。(提示:利用 DE0 板上已有的 50M 晶振作为输入信号,通过开发板上两个的 LED 灯观察输出信号)。 2)电路框图如下: 扩展内容:利用已经实现的 VHDL 模块文件,采用原理图方法,实现 0-F 计数自动循环显示,频率 10Hz。(提示:如何将 VHDL 模块文件在逻辑原理图中应用,参考参考内容 5) 四.实验原理 1.实验1实现异或门逻辑电路,VHDL源代码如下: LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL;

材料专业全国排名1

材料物理与化学是一门以物理、化学和数学等自然科学为基础,从分子、原子、电子等多层次上研究材料的物理、化学行为与规律,致力于先进材料与相关器件研究开发的学科。 材料学以理论物理、凝聚态物理和固体化学等为理论基础,应用现代物理与化学研究方法和计算技术,研究材料科学中的物理与化学问题,着重研究材料的微观组织结构和转变规律,以及他们与材料的各种物理、化学性能之间的关系,并运用这些规律改进材料性能,研制新型材料,发展材料科学的基础理论,探索从基本理论出发进行材料设计,着重现代物理和化学的新概念、新方法在材料研究中的应用。 材料加工工程 主要研究内容涉及高分子材料的加工成型原理、工艺学,先进复合材料制备科学与成型技术、原理,无机非金属材料的加工技术及原理,先进的聚合物加工设备设计学,弹性体配合与改性科学,高分子材料的反应加工技术、原理,高分子材料改性科学与技术等方面。 材料专业全国排名 材料专业全国排名 材料学(160) 排名学校名称等级排名学校名称等级排名学校名称等级 1 清华大学A+ 1 2 四川大学 A 2 3 燕山大学 A 2 西北工业大学A+ 1 3 山东大学 A 2 4 吉林大学 A 3 北京科技大学A+ 1 4 武汉理工大学 A 2 5 上海大学 A 4 上海交通大学A+ 1 5 西安交通大学 A 2 6 重庆大学 A 5 哈尔滨工业大学A+ 1 6 北京化工大学 A 2 7 大连理工大 学 A 6 同济大学A+ 1 7 北京工业大学 A 2 8 湖南大学 A 7 东北大学A+ 18 中国科学技术大 学 A 29 华中科技大 学 A 8 北京航空航天大 学 A+ 19 天津大学 A 30 昆明理工大 学 A 9 浙江大学 A 20 东华大学 A 31 北京理工大 学 A 10 华南理工大学 A 21 南京理工大学 A 32 武汉科技大 学 A 11 中南大学 A 22 合肥工业大学 A

西工大2020年4月《数字电子技术》作业机考参考答案

西工大2020年4月《数字电子技术》作业机考参考答案 试卷总分:100 得分:98 一、单选题(共25 道试题,共50 分) 完整答案:wangjiaofudao 1.{ A.{ B.{

C.{

D.{

正确答案:A 2.十进制数27.5对应的二进制数是()。 A.11010.1 B.11011.1 C.10011.01 D.11001.01 正确答案:B 3.{ A.0,2,4,5,6,7,13 B.0,1,2,5,6,7,13 C.0,2,4,5,6,9,13 D.2,4,5,6,7,11,13 正确答案:A 4.设计10进制计数器,至少需要()级触发器。 A.10 B.4 C.5 D.2 正确答案:B 5.{ A.

B.

C.

D.

正确答案:

6. A.AB B.1 C.0 D. B.{

C.{

D.{

正确答案: 9.二进制数11001.1对应的八进制数是()。 A.62.1 B.62.4 C.31.4 D.31.1 正确答案: 10.{ A.4 B.5 C.6 D.7 正确答案: 11.{ A.0,2,3,5,6 B.4,6,7

C.4,5,6 D.0,1,2,3,5 正确答案: 12.{ A.{ B.{

C.{

D.{

正确答案: 13.{ A.4 B.5 C.6 D.7 正确答案:B 14.四个变量的卡诺图中,逻辑上不相邻的一组最小项为()。 A.

B.

C.

D.

正确答案: 15.{ A.15 B.9 C.8 D.7 正确答案: 16.{ A.

B.

C.

D.

正确答案:

西北工业大学材料学院材料科学与工程专业832材料科学基础考研资料

关于考研,2015你下定决心了吗?做好准备迎接它的到来了吗?愿意花上一年甚至更多的时间全心投入到这场艰苦的战役中了吗?也 许你还在犹豫、也许你陷入迷茫,但千万不要让时间犹豫、迷茫中溜走。在学习上,历经了高考的拼搏,考研也许是最后的一次。未来的路在你脚下,要坚信自己认真的抉择永远是正确。 《弘毅胜卷》的特点: 1.“最全”:本资料把参考书可能考到的知识点都全部列出,并做了详细的讲解,并对历年真题进行透彻的解析; 2.“最简”:为不增加考生负担,对考点的讲解,尽量做到精简,除去了教材繁琐臃肿的语言,直击要害; 3.“最具实用性”:各高校考题的重复率非常高。针对此规律,本资料将专业涉及到的真题举例附在每个考点后面,方便大家查阅。 4.“最具时效性”:本资料会根据最新的招生简章和目录、最新的参考书目和考试大纲对资料进行及时调整、更新,让弘毅胜卷臻于完善! 提醒:为保证产品质量,我们在反盗版技术上投入了很大人力物力,首先在阅读体验上远远超越盗版资料(加了水印和红白页,复印基本看不清楚),同时弘毅考研每年均根据当年最新考试要求进行改版升级并提供超值的售后服务,并将后续重要资料分期发送,盗版将丢失这些重

要资料,请考生务必谨慎辨别,不要为了省一点小钱购买其他机构或个人销售的盗版材料而耽误备考,甚至影响前途的大事情。同时也请大家支持正版,你们一如既往的支持,是我们一直大力度的投入开发的动力。 如果亲在考研路上需要小伙伴,欢迎加入西北工业大学考研群:【140906749】 考试科目:832材料科学基础 适用专业:材料科学与工程 1、西北工业大学材料学院材料科学与工程专业课考研复习指南2015版 学院实力分析、专业信息介绍、历年报录统计、就业情况/发展前景、学费与奖学金、导师情况/出题老师、推荐参考书目、考试情况分析、备考复习建议、复试分数线、复试比例及实施办法、复试参考书目、复试准备和参考策略等其他常见问题。 2、832材料科学基础【08-12年】真题及答案(赠送14回忆版电子档真题)

西工大数电实验报告——计数器及其应用

计数器及其应用 班级:03051001班 学号: 姓名: 同组成员: 一、 实验目的 1. 熟悉常用中规模计数器的逻辑功能。 2. 掌握二进制计数器和十进制计数器的工作原理和使用方法。 3. 运用集成计数器构成1/N 分频器。 二、 实验设备 数字电路试验箱、函数信号发生器、数字双踪示波器、74LS90 三、 实验原理 计数是一种最简单基本运算,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。计数器按计数进制有:二进制计数器,十进制计数器和任意进制计数器;按计数单元中触发器所接收计数脉冲和翻转顺序分有:异步计数器,同步计数器;按计数功能分有:加法计数器,减法计数器,可逆(双向)计数器等。 目前,TTL 和CMOS 电路中计数器的种类很多,大多数都具有清零和预置功能,使用者根据器件手册就能正确地运用这些器件。实验中用到异步清零二-五-十进制异步计数器74LS90。 74LS90是一块二-五-十进制异步计数器,外形为双列直插,引脚排列如图(1)所示,逻辑符号如图(2)所示,图中的NC 表示此脚为空脚,不接线,它由四个主从JK 触发器和一些附加门电路组成,其中一个触发器构成一位二进制计数器;另三个触发器构成异步五进制计数器。在74LS90计数器电路中,设有专用置“0”端 ) 1(0R 、 ) 2(0R 和置“9”端 ) 1(9S 、 ) 2(9S 。其中 ) 1(0R 、 ) 2(0R 为两个异步清零端, ) 1(9S 、 ) 2(9S 为两个异步置9端,CP1、CP2为两个 时钟输入端,Q0~Q3为计数输出端,74LS90的功能表见表(1),由此可知:当R1=R2=S1=S2=0时,时钟从CP1引入,Q0输出为二进制;时钟从CP2引入,Q3输出为五进制;时钟从CP1引入,而Q0接CP2 ,即二进制的输出

西工大数字电路实验报告——实验六

实验六:计数器及其应用 一. 实验目的: 1. 熟悉常用中规模计数器的逻辑功能。 2. 掌握时序电路一般设计方法。 3. 能够应用时序电路解决实际问题。 二. 实验设备: 数字电路试验箱,数字双踪示波器,函数信号发生器,74LS161,,74LS00及Multisim 仿真软件。 三. 实验原理: 计数是一种最简单基本运算,计数器在数字系统中主要是对脉冲的个数进行计数,以实现测量、计数和控制的功能,同时兼有分频功能。计数器按计数进制有:二进制计数器,十进制计数器和任意进制计数器;按计数单元中触发器所接收计数脉冲和翻转顺序分有:异步计数器,同步计数器;按计数功能分有:加法计数器,减法计数器,可逆(双向)计数器等。 目前,TTL 和CMOS 电路中计数器的种类很多,大多数都具有清零和预置功能,使用者根据器件手册就能正确地运用这些器件。实验中用到异步清零同步置数四位二进制计数器74LS161。 74LS161为异步清零计数器,即端输入低电平,不受CP 控制,输出端立即全部为“0”。74LS161具有同步置数功能,在端无效时,端输入低电平,在时钟共同作用下,CP 上跳后计数器状态等于预置输入 , 即同步预置功能。和都无效,T 或P 任意一个为低电平,计数器处于保持状态,即输出状态不变。只有四个控制输入都为高电平,计数器才实现16加法计数。74LS161引脚排列如图(1)所示,表(1)为它的功能表。 图(1) r C r C D L 3210D D D D r C D L

1 0 ↑ D C B A 1 0 1 0 1 1 1 ↑ 表(1) 四.实验内容: 1.用74LS161和74LS00实现两种置数方式的十进制计数。 (1)异步置数法: 利用芯片的预置功能,可以实现M=10进制计数器,M=16-N=10,其中N=6(二 进制为0110)为预置数。将0110送到输入端D3D2D1D0,计数器开始从0110 开始计数,在CP脉冲下一直计数到1111,此时,从进位端Qc输出1,经 非门送到Ld端,呈置数状态。还可以将D3D2D1D0全部接地,当输出值为 1001(十进制的9)时,两个输出端Q3和Q0经与非门送到Ld端,呈置数状 态。第二种方式的电路连接如下图上半部分: (2)同步清零法: 当计数器计数到1010(十进制10)的时候,Q3和Q1经与非门输出,使复位 端Cr为0,从而计数器从执行计数变为复位状态,其电路连接如上图下半 部分: 2.用74LS161和74LS00实现两种级联方式24进制计数。 因为M=24>16,所以才用两片74LS161计数器级联实现24进制计数。使第一片 计数器连接成异步置数法的10进制计数器,当Q3和Q1经与非门输出0时,

西工大 数字集成电路实验一

数字集成电路实验报告 西北工业大学2014年5月5日星期一

实验一、反相器链的参数模拟下图反相器中的MOS管L=0.5u,W=1.2u。试建立反相器子电路,并考察子电路的VTC特性。建立完整电路后,分析该反相器链的直流传输特性、时序特性及带负载能力(负载为电容0.5P 1P 2P)。 第一步:设计反相器单元 Vdd

第二步:写出输入文件,执行DC分析获得反相器的VTC特性图由曲线可得,单个反相器的开关阈值为2.15V 第三步写出SUBCKT并实例化三个,来实现反相器链对反相器链执行DC扫描。 第四步执行measure 命令测量延迟时间。

由仿真所得的list文件可得: tdelay= 1.8323E-09 targ= 1.2332E-08 trig= 1.0500E-08 第五步考察电路带容性负载的能力,同学们自己完成(提示:建立DATA包含三个容值,瞬态分析时执行SWEEP DATA=DATANM) tdelay= 9.6262E-13 targ= 1.0501E-08 trig= 1.0500E-08 代码附录:

.TITLE 1.2UM CMOS INVERTER .options probe .options tnom=25 .options ingold=2 limpts=30000 method=gear .options lvltim=2 imax=20 gmindc=1.0e-12 .protect .lib'C:\Eric\Digital Integrated Circuit\experiment 1\cmos25_level49.lib' TT .unprotect .global vdd Mn out in 0 0 NMOS W=1.2u L=0.5u *(工艺中要求尺寸最大0.5u)Mp out in vdd vdd PMOS W=3u L=0.5u * 此处W需做更改) CL OUT 0 0.5PF vdd vdd 0 5V vin in 0 PULSE(0 5V 10NS 1N 1N 50N 100N) .DC vin 0 5V 0.1V .op .probe dc v(out) .end .TITLE 1.2UM CMOS INVERTER CHAIN .options probe

西工大数电实验报告实验三

实验三.基于Quartus II的硬件描述语言电路设计 要求1:学习并掌握硬件描述语言(VHDL 或Verilog HDL);熟悉门电路的逻辑功能,并用硬件描述语言实现门电路的设计。参考“参考内容1”中给出的与门源程序,编写一个异或门逻辑电路。 1)用QuartusII 波形仿真验证; 2)下载到DE0 开发板验证。 要求2:熟悉中规模器件译码器的逻辑功能,用硬件描述语言实现其设计。参考“参考内容2”中给出的将8421BCD 码转换成0-9 的七段码译码器源程序,编写一个将二进制码转换成0-F 的七段码译码器。 1)用QuartusII 波形仿真验证; 2)下载到DE0 开发板,利用开发板上的数码管验证。 要求3:熟悉时序电路计数器的逻辑功能,用硬件描述语言实现其设计。参考“参考内容3”中给出的四位二进制加减计数器的源程序,编写一个计数器。 1)用QuartusII 波形仿真验证; 2)下载到DE0 开发板验证。 要求4:熟悉分频电路的逻辑功能,并用硬件描述语言实现其设计。参考“参考内容4”中给出的50M 分频器的源程序,编写一个能实现占空比50%的5M 和50M分频器即两个输出,输出信号频率分别为10Hz 和1Hz。 1)下载到DE0 开发板验证。(提示:利用DE0 板上已有的50M 晶振作为输入信号,通过开发板上两个的LED 灯观察输出信号)。电路框图如下: 要求五:扩展内容:利用已经实现的VHDL 模块文件,采用原理图方法,实现0-F 计数自动循环显示,频率10Hz。(提示:如何将VHDL 模块文件在逻辑原理图中应用,参考参考内容5) 一.实验内容与结果 (一)异或门逻辑电路设计 1.异或门逻辑vhdl程序 LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY yihuo IS PORT(A,B:IN STD_LOGIC; C:OUT STD_LOGIC); END yihuo; ARCHITECTURE fwm OF yihuo IS BEGIN C<=A XOR B; END; 2.Quartus II波形仿真即结果

西工大数电实验报告_实验一TTL集成逻辑门电路参数测试

实验一TTL集成逻辑门电路参数测试 姓名:同组: 一、实验目的: (1)加深了解TTL逻辑门的参数意义。 (2)掌握TTL逻辑门电路的主要参数及测量方法。 (3)认识各种电路及掌握空闲端处理方法。 二、实验设备: 数字电路实验箱,数字双踪示波器,函数信号发生器,数字万用表,74LS00,电位器,电阻。 三、实验原理: 门电路是数字逻辑电路的基本组成单元,目前使用最普遍的双极型数字集成电路是TTL逻辑门电路。 1) 用示波器测量实验箱的电源输出。 2) 用函数信号发生器产生频率1.5KHz信号,其峰峰值为5.0V,偏移为0V。使用示波器测量该信号(脉冲宽度、周期、幅度和占空比)。切换示波器耦合方式(AC或DC),观察示波器波形显示的异同。 3)调节信号偏移(1V、1.2V、2.5V),切换示波器耦合方式(AC 或DC),观察示波器波形显示的异同。分析信号偏移功能的作用。 TTL集成电路的使用规则: (1)插集成块时,要认清定位标记,不得插反。 (2)使用电源电压范围为+4.5V~+5.5V。实验中要求使用

Vcc=+5V。电源极性不允许接错。 (3)空闲输入端处理方法,悬空,相当于正逻辑“1”,一般小规模集成电路的数据 输入端允许悬空处理。但易受外界干扰,导致电路逻辑功能不正常。因此,对于接有长线的输入端,中规模以上的集成电路和使用集成电路较多的复杂电路,所有控制输入端必须按逻辑要求接入电路,不允许悬空。 (4)输入端通过电阻接地,电阻值的大小将直接影响电路所处状态。 (5)输出端不允许并联使用(三态门和OC门除外),否则不仅会使电路逻辑功能混 乱,并会导致器件损坏。 (6)输出端不允许直接接电源Vcc,不允许直接接地,否则会损坏器件。 四、实验内容: 1) 用示波器测量实验箱的电源输出。 2) 用函数信号发生器产生频率1.5KHz信号,其峰峰值为5.0V,偏移为0V。使用示波器测量该信号(脉冲宽度、周期、幅度和占空比)。切换示波器耦合方式(AC或DC),观察示波器波形显示的异同。3)调节信号偏移(1V、1.2V、2.5V),切换示波器耦合方式(AC或DC),观察示波器波形显示的异同。分析信号偏移功能的作用。 4) TTL集成逻辑门(74LS00)的电压传输特性测量。

2017中国材料大会-西北工业大学凝固技术国家重点实验室

2017中国材料大会 E04 凝固科学与技术 分会主席:李金山、翟启杰、苏彦庆、王同敏、李建国、王海鹏、陈玉勇、陈光、赵九洲、惠希东 单元E04-1:7月9日上午 主持人:李建国 地点:ROOM B2N17 10:00-10:25 E04-01 (invited) 小平面生长合金凝固的择优取向和组织调控 蒋成保 北京航空航天大学 10:25-10:50 E04-02 (invited) 定向凝固铝合金中羽毛状孪生枝晶的凝固与生长李双明,杨鲁岩,钟宏,傅恒志 西北工业大学710072 10:50-11:15 E04-03 (invited) Solidification of Al alloys investigated by advanced electron microscopy Priv.-Doz. , Dr. Jiehua Li Institute of Casting Research, Montanuniversit?t Leoben, A-8700, Leoben, Austria 11:15-11:30 E04-04 柱状晶-等轴晶转变的熔断机制研究 徐贲,吴凌康 清华大学材料学院100084 11:30-11:45 E04-05 强磁场对Co基合金过冷熔体形核过程的影响 王军1,李金山1,Eric BEAUGNON 2,3 1. 西北工业大学凝固技术国家重点实验室,西安710072 2. Univ. Grenoble Alps, LNCMI, F-38000 Grenoble, France 3. CNRS, LNCMI, F-38000 Grenoble, France 11:45-12:00 E04-06 气动悬浮熔炼试样温度梯度控制及BaTi2O5陶瓷深过冷凝固组织葛璇,胡侨丹,李建国 上海交通大学200240 单元E04-2:7月9日上午 主持人:王海鹏 地点:ROOM B2N14 10:00-10:25 E04-07 (invited) 定向凝固与钛铝单晶 陈光 南京理工大学 10:25-10:50 E04-08 (invited) 层状铝合金复合材料连铸坯制备过程的模拟与实验研究 王同敏 大连理工大学 10:50-11:05 E04-09 轻合金二次复合挤压铸造技术及应用 侯华,陈利文,闫峰,赵宇宏 中北大学材料科学与工程学院,太原030051 11:05-11:20 E04-10 定向凝固铝合金枝晶生长取向的演变 陈忠伟,高建平 西北工业大学710072 11:20-11:35 E04-11 Al/Ni-液/固界面反应体系中氢气泡的同步辐射动态实时表征 丁宗业,胡侨丹,卢温泉,孙思宇,夏明许,李建国 上海交通大学200240 11:35-11:50 E04-12 铝合金半固态浆料微观组织元胞法模拟研究 屈文英,张帆,李大全,罗敏,杨志宇,张永忠北京有色金属研究总院101407

2017年西北工业大学 874信号系统与数字电路 硕士研究生考试大纲

题号:847《信号系统与数字电路》 考试大纲 一、 考试内容: (一)“信号与系统”复习大纲: 1、信号与系统的基本概念:常用连续信号的时域特征;信号的能量及平均功率;信号的几种重要分解;信号的变换与运算;线性时不变系统基本性质。 2、连续信号频域分析:频谱密度函数的概念;傅立叶变换及反变换的物理含义;常用非周期信号的频谱函数;周期信号的频谱函数;付立叶变换的性质及其应用。 3、连续系统频域分析:频域系统函数H(jω)及其求法;系统频率特性的物理含义;系统零状态响应的频域求解;理想低通滤波器及其特性;信号不失真传输条件;抽样定理及其应用。 4、连续系统复频域分析:拉氏变换及其基本性质;拉氏反变换求解;s域的电路模型和电路定律;线性时不变系统的复频域分析。 5、复频域系统函数H(s):H(s)定义、物理意义、求法及其应用;系统模拟框图与信号流图;系统稳定性判定、系统频率特性及正弦稳态响应的求解;梅森公式及其应用。 6、离散信号与系统时域分析:常用离散信号的时域特征;信号的能量及平均功率;信号的几种重要分解;离散信号时域变换、运算以及卷积求和;线性时不变离散系统的性质;零输入响应、零状态响应、单位序列响应的求解。 7、离散系统Z域分析:Z变换及其基本性质;Z反变换;系统Z域分析;系统函数H(z)定义、物理意义、求法及其应用;离散系统模拟框图与信号流图;离散系统稳定性判定、系统频率特性及正弦稳态响应的求解;梅森公式及其应用。 (二)“数字电路”复习大纲: 1、数制和编码以及逻辑代数基础:常用的数制和编码;二进制算术运算;不同数制间的相互转换;三种基本逻辑运算;逻辑代数的基本定律和定理;逻辑函数的几种描述方式及其相互转化;逻辑函数的化简(基于公式和基于卡诺图)。

西北工业大学_数字电子技术基础_实验报告_实验3

数字电子技术基础第三次实验报告 、描述Quartusll 软件基本使用步骤 ① 编写Verilog 代码,用文本编辑器正确编写源文件 ,并经modelsim 仿真确认该电路 设计正确。 ② 打开Quartusll 软件,新建工程New project (注意工程名和设计文件的 module 名保 持一致),选择和开发板一致的 FPGA 器件型号。 ■■pww n ④编译,Start Compilation ,编译源文件(如有错误修改后,重新编译) 。 I —f 1 UuM-JI 工 HfiaMi ■sm ?MITmHL 1 】it A** 5 Kii atiT^u^ri :i& 1 u ■审3T1 H ? ”峠if - Ik r irM "小"= ③添加文件,点击 file->open,之后选择要添加的文件,并勾选 Add file to current project. ■ 5 r-w in ¥ 口

X. I M ■ tWIR fetawej . MtamM* E?Maa4inrv*nn ? 1 Tl n . ■ EGvi I IPHIWIV E R H F 4- xsffl ECA -iha W M ni WmUAf ⑤查看电路结构,使用 Tool->RTL viewer 工具查看电路图结构,是否和预期设计一致。 rp M. Oi* > 1 JiMiMdaOML 实验一、反相器链 实验要求:下图反相器中的MOS 管L=0.5u ,W=1.2u 。试建立反相器子电路,并考察子电路的VTC 特性。建立完整电路后,分析该反相器链的直流传输特性、时序特性及带负载能力(负载为电容0.5P 1P 2P )。 一、设计反相器单元 Vout Vdd 二、写出输入文件,执行DC 分析获得反相器的VTC 特性图 Sp 文件: .TITLE 1.2UM CMOS INVERTER .options probe .options tnom=25 .options ingold=2 limpts=30000 method=gear .options lvltim=2 imax=20 gmindc=1.0e-12 .protect .lib'C:\synopsys\cmos25_level49.lib' TT .unprotect .global vdd Mn out in 0 0 NMOS W=1.2u L=0.5u *(工艺中要求尺寸最大0.5u) Mp out in vdd vdd PMOS W=2.4u L=0.5u * 此处W需做更改) CL OUT 0 0.5PF VDD VDD 0 5V VIN IN 0 PULSE(0 5V 10NS 1N 1N 50N 100N) .DC VIN 0 5V 0.1V .op .probe dc v(out) .end 仿真结果: 三、写出SUBCKT并实例化三个,来实现反相器链对反相器链执行DC扫描。 Sp文件: .TITLE 1.2UM CMOS INVERTER CHAIN .options probe .options tnom=25西工大数字集成电路实验报告 数集实验1