ADC0809驱动FPGA实现的verilog程序

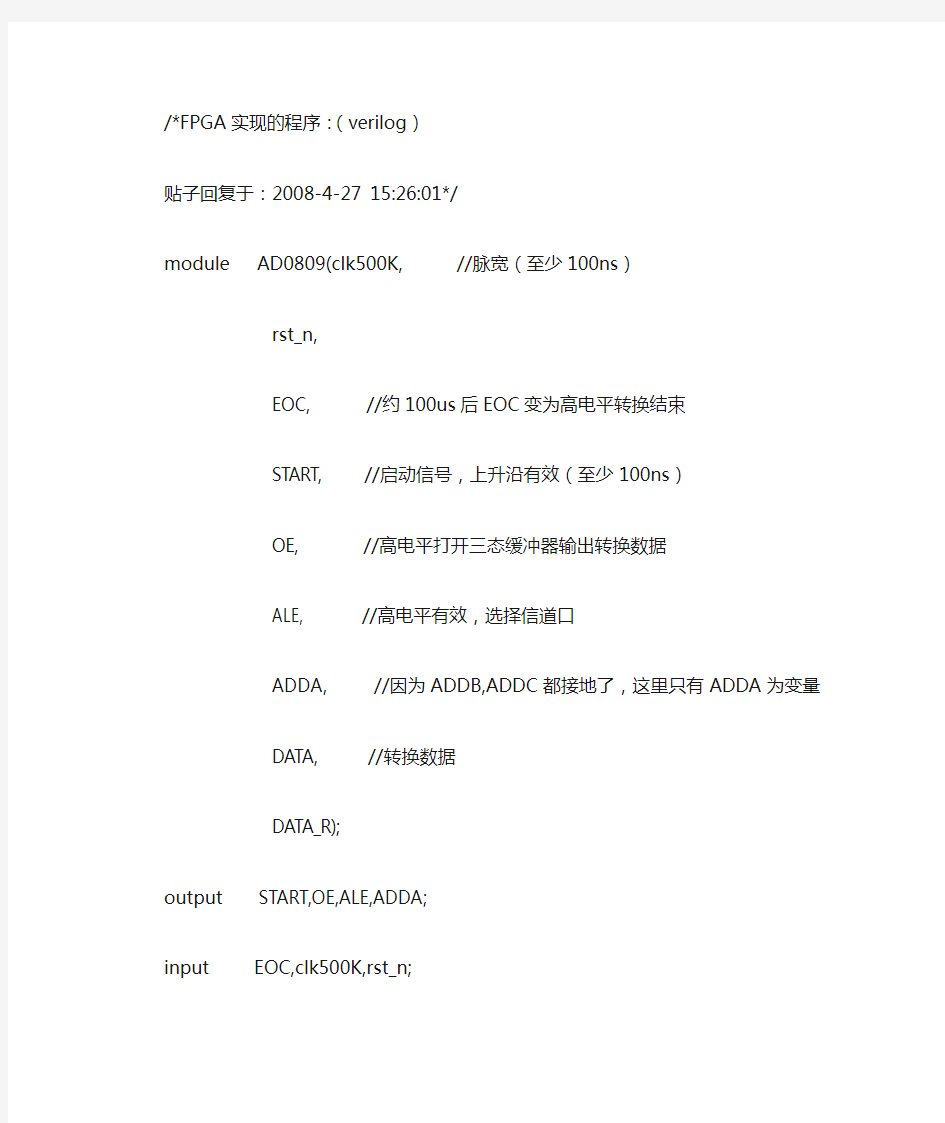

/*FPGA实现的程序:(verilog)

贴子回复于:2008-4-27 15:26:01*/

module AD0809(clk500K, //脉宽(至少100ns)

rst_n,

EOC, //约100us后EOC变为高电平转换结束

START, //启动信号,上升沿有效(至少100ns)

OE, //高电平打开三态缓冲器输出转换数据

ALE, //高电平有效,选择信道口

ADDA, //因为ADDB,ADDC都接地了,这里只有ADDA为变量

DATA, //转换数据

DATA_R);

output START,OE,ALE,ADDA;

input EOC,clk500K,rst_n;

input[7:0] DATA;

output[7:0] DATA_R;

reg START,OE,ALE,ADDA;

reg[7:0] DATA_R;

reg[4:0] CS,NS;

parameter

IDLE=5'b00001,START_H=5'b00010,START_L=5'b00100,CHECK_END=5'b01000,GET_DATA=5'b100 00;

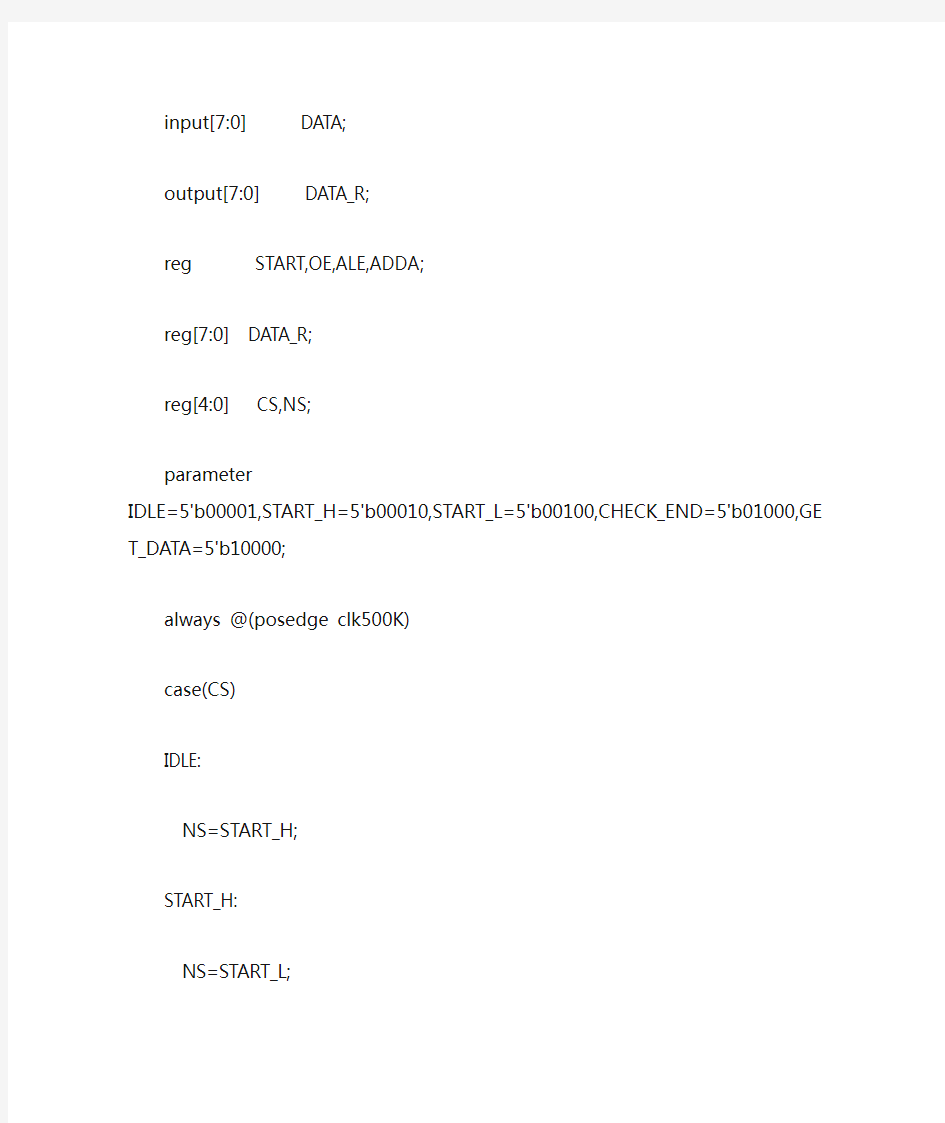

always @(posedge clk500K)

case(CS)

IDLE:

NS=START_H;

START_H:

NS=START_L;

START_L:

NS=CHECK_END;

CHECK_END:

if(EOC)

NS=GET_DATA;

else

NS=CHECK_END;

GET_DATA:

NS=IDLE;

default:

NS=IDLE;

endcase

always @(posedge clk500K)

if(!rst_n)

CS<=IDLE;

else

CS<=NS;

always @(posedge clk500K)

case(NS)

IDLE:

begin

OE<=0;

START<=0;

ALE<=0;ADDA<=1;

end

START_H:

begin

OE<=0;

START<=1; //产生启动信号

ALE<=1;

ADDA<=1;//选择信道口IN0

end

START_L:

begin

OE<=0;

START<=0;

ALE<=1;//启动信号脉宽要足够长,在启动的时候ALE要一直有效end

CHECK_END:

begin

OE<=0;

START<=0;

ALE<=0;

end

GET_DATA:

begin

OE<=1; //高电平打开三态缓冲器输出转换数据

DATA_R<=DATA;//提取转换数据

START<=0;

ALE<=0;

end

default:

begin

OE<=0;

START<=0;

ALE<=0;

ADDA<=0;

end

endcase

endmodule

ad0809是根据逐位逼近的方法产生数据的。。

参考电压为0-5V的话。以0809八位255的转换精度每一位的电压值为(5-0)/255≈0.0196V 设输入电压为X则:

X-27*0.0196>=0则AD7=1否则AD7=0。

X-26*0.0196>=0则AD6=1否则AD6=0。

。

。

。

X-20*0.0196>=0则AD0=1否则AD0=0。

(27指2的7次方。26-------20同理)

若参考电压为0-1V

(1-0)/255≈0.0039V精度自然高了。。可测量范围小了。

状态机要写成3段式的(这是最标准的写法),即

...

always @(posedge clk or negedge rst_n)

...

current_state <= next_state;

...

always @ (current_state ...)

...

case(current_state)

...

s1:

if ...

next_state = s2;

...

...

always @(posedge clk or negedge rst_n)

...

else

a <= 1'b0;

c <= 1'b0;

c <= 1'b0; //赋默认值

case(current_state)

s1:

a <= 1'b0; //由于上面赋了默认值,这里就不用再对

b 、c赋值了(b、c在该状态为0,不会产生锁存器,下同)

s2:

b <= 1'b1;

s3:

c <= 1'b1;

default:

...

...

VerilogHDL经典程序非常适合新手

一、2线-4线译码器 module counter4(q1,q0,ncr,cp); input cp,ncr; output q1,q0; reg q1,q0; always@(posedge cp or negedge ncr) begin if(~ncr){q1,q0}<=2'b00; else{q1,q0}<={q1,q0}+1'b1; end endmodule 二、4选1数据选择器 module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0; output y; reg y; always@(a1or a0) begin case({a1,a0}) 2'b00:y=i0; 2'b01:y=i1; 2'b10:y=i2; 2'b11:y=i3; default:y=0; 一、2线-4线译码器 module counter4(q1,q0,ncr,cp); input cp,ncr; output q1,q0; reg q1,q0; always@(posedge cp or negedge ncr) begin if(~ncr){q1,q0}<=2'b00; else{q1,q0}<={q1,q0}+1'b1; end endmodule 二、4选1数据选择器 module selector4_1(i0,i1,i2,i3,a1,a0,y); input i0,i1,i2,i3,a1,a0; output y; reg y; always@(a1or a0) begin case({a1,a0}) 2'b00:y=i0;

基于FPGA的Verilog HDL数字钟设计 -

基于FPGA的Verilog HDL数字钟设计 专业班级姓名学号 一、实验目的 1.掌握可编程逻辑器件的应用开发技术——设计输入、编译、仿真和器件编程; 2.熟悉一种EDA软件使用; 3.掌握Verilog设计方法; 4.掌握分模块分层次的设计方法; 5.用Verilog完成一个多功能数字钟设计; 6.学会FPGA的仿真。 二、实验要求 ?功能要求: 利用实验板设计实现一个能显示时分秒的多功能电子钟,基本功能: 1)准确计时,以数字形式显示时、分、秒,可通过按键选择当前显示时间范围模式; 2)计时时间范围00:00:00-23:59:59 3)可实现校正时间功能; 4)可通过实现时钟复位功能:00:00:00 扩展功能: 5)定时报:时间自定(不要求改变),闹1分钟(1kHz)---利用板上LED或外接电路实现。 6)仿广播电台正点报时:XX:59:[51,53,55,57(500Hz);59(1kHz)] ---用板上LED或外接 7)报整点时数:XX:00:[00.5-XX.5](1kHz),自动、手动---用板上LED或外接 8)手动输入校时; 9)手动输入定时闹钟; 10)万年历; 11)其他扩展功能; ?设计步骤与要求: 1)计算并说明采用Basys2实验板时钟50MHz实现系统功能的基本原理。 2)在Xilinx ISE13.1 软件中,利用层次化方法,设计实现模一百计数及显示的电路系 统,设计模块间的连接调用关系,编写并输入所设计的源程序文件。 3)对源程序进行编译及仿真分析(注意合理设置,以便能够在验证逻辑的基础上尽快 得出仿真结果)。 4)输入管脚约束文件,对设计项目进行编译与逻辑综合,生成下载所需.bit文件。 5)在Basys2实验板上下载所生成的.bit文件,观察验证所设计的电路功能。

linux下的fpga驱动

#ifndef _FPGA_H_ #define _FPGA_H_ #define INTMSK (0x4A000008) #define EINTMASK (0x560000A4) #define S3C2410_ENABLE_EINT8_23 (~(1<<5)) #define S3C2410_ENABLE_EINT18 (~(1<<18)) #undef PDEBUG /* undef it, just in case */ #define DEBUG //调试时添加此行程序,实际产品中需要注释掉 #ifdef DEBUG # define PDEBUG(fmt, args...) printk( KERN_WARNING "fpga: " fmt, ## args) #else # define PDEBUG(fmt, args...) /* not debugging: nothing */ #endif #define DEVICE_NAME "FPGA" #ifndef FPGA_NR_DEVS #define FPGA_NR_DEVS 1 /*设备数*/ #endif #define FPGAMEM_SIZE 1024/*FPGA每次产生中断可以读取到缓存的数据大小*/ #define FPGACMD_SIZE 3 /*FPGA每次产生中断可以读取到缓存的数据大小*/ #define FPGA_ADDR_START (0x08000000) //nGCS1地址 #define FPGA_ADDR_SIZE 0x30 //申请IO内存的大小 #define FPGA_ADDR_DATA 0x10 //FPGA数据寄存器偏移地址 #define FPGA_ADDR_CMD 0x14 //FPGA命令寄存器偏移地址 /* 定义幻数,定义一个字符,8位,用于检测是否是这类设备,ioctl-number.txt中给出了已经使用的幻数,定义的时候注意避免冲突*/ #define FPGA_IOC 'k' /* 定义命令,这里的命令都是unsigned int类型*/ #define FPGA_IOC_ALLON _IO(FPGA_IOC, 0) // #define FPGA_IOC_ALLDOWN _IO(FPGA_IOC, 1) // #define FPGA_IOC_SET _IOW(FPGA_IOC, 2, int) // #define FPGA_IOC_CLEAR _IOW(FPGA_IOC, 3, int)// #define FPGA_IOC_MAXNR 4 //定义命令的最大序列号

基于FPGA直流电动机驱动的设计

河南大学2014届本科毕业论文 论文题目 基于FPGA直流电动机驱动的设计 论文作者姓名:______________ 作者学号:___1003618004_______ 所在学院:民生学院 所学专业:_电子信息科学与技术_ 导师姓名职称:___ _______ 论文完成时间: 2014年04月24日 _ I

河南大学民生学院本科毕业论文 目录 摘要: ..................................................................................... 错误!未定义书签。 0 前言 (2) 1 绪论 (2) 1.1 课题的来源 (2) 1.2 课题研究的目的及意义 (3) 1.3 课题国内外研究现状 (4) 1.4 课题实质性展现 (4) 2直流电动机的概括 (4) 2.1 直流电动机的基本构成 (4) 2.2 直流电动机的工作原理 (5) 2.3 直流电动机的性能 (6) 3 直流电动机的控制及PWM(脉宽调制) (7) 3.1 控制器的控制电路 (7) 3.2 转子位置传感器 (8) 3.3 直流电动机的控制原理详解 (9) 3.4 直流电机转速控制与PWM脉宽调制 (11) 4 FPGA及其组成的控制器 (12) 4.1 FPGA芯片 (13) 4.2 VHDL硬件描述语言 (14) 4.3 运用FPGA来实现对直流电动机的控制 (15) 4.4 PWM(脉宽调制信号) (16) 4.5速度检测 (19) 5 结论 (20) 参考文献 (20) II

基于FPGA的直流电机驱动的设计 电子信息技术在如今的社会中已然达到迅猛发展阶段,国家也在大力加强电子商务领域的引导性投资,可见其在当今社会中的重要性。 电子技术的发展方向。可以说模拟电子技术是电子技术的根本,在调制解调,功率放大,信号放大、整流稳压等电路方面具有非常重要作用,移动通信等领域都不可或缺。电子技术的另外一个重要组成部分数字电子技术同等重要的,和模拟电子技术相对比,数字电子技术具有稳定性好,精度高,抗干扰性强的优势。也正是因为数字电子的这些优势使得它在一些领域的发展更胜于模拟电子,数字滤波器就是一个很好的证明。 数字电子技术目前也在向两个截然相反的方向发展,一是基于通用处理器的软件开发技术,如单片机、bps等技术,它们是在一个通用处理器的基础上结合少量的硬件电路设计来完成系统的硬件电路,而将主要精力集中在算法、数据处理等软件层次上的系统方法。另一个方向是基于CPLD/FPGA的可编程逻辑器件的系统开发,其特点是将算法、数据加工等工作全部融入系统的硬件设计当中,在“线与线的互联”当中完成对数据的加工。 单片机微处理器作为核心来实现直流电机的控制已然跟不上时代发展的需求。由此电机控制器也由模拟分立原件构成的电路向数模混合、全数字方向发展。此文章主要研究了FPGA芯片在直流电机控制器中的作用。文章详细的介绍了直流电机的类型、结构、工作原理、PWM调速原理和FPGA集成芯片。后对所需应用的硬件语言VHDL方面知识也进行了介绍。从而为论文的具体设计部分提供了理论基础。FPGA的电机控制中,最基本的作用有三:组合逻辑、计数器、状态机。 关键词: FPGA芯片;直流电机;硬件描述语言(VHDL);PWM;现场可编程门阵列 DC motor driven FPGA-based design Electronic information technology in today's society has already reached the rapid development stage, countries are vigorously strengthen the field of electronic commerce to guide investment, and its importance in today's society . Direction of development of electronic technology. It can be said analog electronics technology is the fundamental electronic technology, the modem, power amplification, signal amplification, rectification regulators and other aspects of the circuit has a very important role in areas such as mobile communications are indispensable. Another important part of the digital electronic technology as important as electronic technology, and the relative ratio of analog electronics, digital electronics technology has good stability, high accuracy, strong anti-interference advantages. It is also because of these advantages make it the development of digital electronics in some areas more than analog electronics, digital filter is a good proof. Digital electronic technology is also currently the two diametrically opposite 1

74LS138Verilog源码

`timescale 1ns / 1ps ////////////////////////////////////////////////////////////////////////////////// // Company: // Engineer: // // Create Date: 2020/02/28 13:40:03 // Design Name: // Module Name: _74ls138 // Project Name: // Target Devices: // Tool Versions: // Description: // // Dependencies: // // Revision: // Revision 0.01 - File Created // Additional Comments: // ////////////////////////////////////////////////////////////////////////////////// module _74ls138(nE1,nE2,E3,B,nY); input nE1,nE2,E3; input [2:0]B; output[7:0]nY; reg[7:0]nY; always@(nE1,nE2,E3,B) if(!nE1 && !nE2 && E3) begin case(B) 3'b000: nY = 8'b1111_1110; 3'b001: nY = 8'b1111_1101; 3'b010: nY = 8'b1111_1011; 3'b011: nY = 8'b1111_0111; 3'b100: nY = 8'b1110_1111; 3'b101: nY = 8'b1101_1111; 3'b110: nY = 8'b1011_1111; 3'b111: nY = 8'b0111_1111; default:nY = 8'b1111_1111; endcase end

(完整版)Verilog实现的基于FPGA的五层楼电梯运行控制逻辑毕业设计论文

五层楼电梯运行控制逻辑设计 摘要:电梯是高层建筑不可缺少的运输工具,用于垂直运送乘客和货物,传统的电梯控制系统主要采用继电器,接触器进行控制,其缺点是触点多,故障率高、可靠性差、维修工作量大等,本设计根据电梯自动控制的要求利用Verilog语言编写并完成系统设计,在利用软件仿真之后,下载到了FPGA上进行硬件仿真。FPGA(Field-Programmable Gate Array),即现场可编程门阵列,它是在PAL、GAL、CPLD等可编程器件的基础上进一步发展的产物。它是作为专用集成电路(ASIC)领域中的一种半定制电路而出现的,既解决了定制电路的不足,又克服了之前的可编程器件门电路数有限及速度上的缺点。 关键词:电梯控制FPGA Verilog软件设计硬件设计 在当今社会,随着城市建设的不断发展,高层建筑的不断增多,电梯作为高层建筑中垂直运行的交通工具已与人们的日常生活密不可分。目前电梯控制系统主要有三种控制方式:继电路控制系统(早期安装的电梯多位继电器控制系统),FPGACPLD [1] 的控制系统、微机控制系统。继电器控制系统由于故障率高、可靠性差、控制方式不灵活以及消耗功率大等缺点,目前已逐渐被淘汰,而微机控制系统虽在智能控制方面有较强的功能,但也存在抗扰性差,系统设计复杂,一般维修人员难以掌握其维修技术等缺陷。而FPGACPLD控制系统由于运行可靠性高,使用维修方便,抗干扰性强,设计和调试周期较短等优点 [2] ,倍受人们重视等优点,已经成为目前在电梯控制系统中使用最多的控制方式,目前也广泛用于传

统继电器控制系统的技术改造。 随着现代化城市的高度发展,每天都有大量人流及物流需要输送,因此在实际工程应用中电梯的性能指标相当重要,主要体现在:可靠性,安全性,便捷快速性。电梯的可靠性非常重要,直接或间接的影响着人们的生产,生活,而电梯的故障主要表现在电力拖动控制系统中,因此要提高可靠性也要从电力拖动控制系统入手。 本次设计尝试用Verilog实现电梯控制器部分,进行了多层次的电梯控制,也进行了软件及硬件上的仿真验证,时序分析以保证设计的正确。在设计中先用软件进行模拟仿真,然后又下载到FPGA开发板上进行硬件仿真,以确保设计的正确性。 1电梯的设计分析 1.1 系统的需求分析及系统描述 设计一个电梯运行控器,该电梯有5层楼,设计的电梯调度算法满足提高服务质量、降低运行成本的原则;电梯的内部有一个控制面板,它负责按下请求到的楼层,并且显示当前尚未完成的目的地请求,当到达该楼层以后自动撤销本楼层的请求,即将面板灯熄灭;除1层和5层分别只有上和下按钮外,其余每个楼层(电梯门口旁)的召唤面板都有两个按钮,分别指示上楼和下楼请求。当按下后,对应按钮灯亮。如果电梯已经到达该楼层,按钮灯熄灭;电梯的外部面板会显示电梯当前所在的楼层,及上行还是下行(暂停显示刚才运行时的状态);电梯向一个方向运行时,只对本方向前方的请求进行应答,直到本方向前方无请求时,才对反方向的请求进行应答。当前内部控制面板上有的请求,只要经过所在楼层均会立即响应.

全数字锁相环的verilog源代码讲解

支持论坛发展帖出全数字锁相环的verilog源代码,仿真已通过 module dpll(reset,clk,signal_in,signal_out,syn; parameter para_K=4; parameter para_N=16; input reset; input clk; input signal_in; output signal_out; output syn; reg signal_out; reg dpout; reg delclk; reg addclk; reg add_del_clkout; reg [7:0]up_down_cnt; reg [2:0]cnt8; reg [8:0]cnt_N; reg syn; reg dpout_delay; reg [8:0]cnt_dpout_high; reg [8:0]cnt_dpout_low; /******phase detector*****/ always@(signal_in or signal_out begin dpout<=signal_in^signal_out; end /******synchronization establish detector*****/ always@(posedge clk or negedge reset begin if(!reset dpout_delay<='b0; else dpout_delay<=dpout; end always@(posedge clk or negedge reset begin if(!reset begin cnt_dpout_high<='b0; cnt_dpout_low<='b0; end else if(dpout if(dpout_delay==0 cnt_dpout_high<='b0; else if(cnt_dpout_high==8'b11111111 cnt_dpout_high<='b0; else cnt_dpout_high<=cnt_dpout_high+1; else if(!dpout if(dpout_delay==1 cnt_dpout_low<='b0; else if(cnt_dpout_low==8'b11111111 cnt_dpout_low<='b0; else cnt_dpout_low<=cnt_dpout_low+1; end always@(posedge clk or negedge reset begin if(!reset syn<='b0; else if((dpout&&!dpout_delay||(!dpout&&dpout_delay if(cnt_dpout_high[8:0]-cnt_dpout_low[8:0]<=4||cnt_dpout_low[8:0]- cnt_dpout_high[8:0]<=4 syn<='b1; else syn<='b0; end /****up down couter with mod=K****/ always@(posedge clk or negedge reset begin if(!reset begin delclk<='b0; addclk<='b0; up_down_cnt<='b00000000; end else begin if(!dpout begin delclk<='b0; if(up_down_cnt==para_K-1 begin up_down_cnt<='b00000000; addclk<='b0; end else begin up_down_cnt<=up_down_cnt+1; addclk<='b0; end end else begin addclk<='b0; if(up_down_cnt=='b0 begin up_down_cnt<=para_K-1; delclk<='b0; end else if(up_down_cnt==1 begin delclk<='b1; up_down_cnt<=up_down_cnt-1; end else up_down_cnt<=up_down_cnt-1; end end end /******add and delete clk*****/ always@(posedge clk or negedge reset begin if(!reset begin cnt8<='b000; end else begin if(cnt8=='b111 begin cnt8<='b000; end else if(addclk&&!syn begin cnt8<=cnt8+2; end else if(delclk&&!syn

基于FPGA的verilog的电子密码锁设计

一、概述 1.1 电子密码锁的现状 随着我国对外开放的不断深入,高档建筑发展很快,高档密码锁具市场的前景乐观。我国密码锁具行业对密码锁具高新技术的投入正逐年增大,高档密码锁的市场需求也逐年增加。在安防工程中,锁具产品是关系到整个系统安全性的重要设备,所以锁具产品的优劣也关系了整个安防工程的质量和验收。 目前,市场上比较先进的智能电子密码锁分别有:IC卡电子密码锁、射频卡式电子密码锁、红外遥控电子密码锁、指纹识别电子密码锁和瞳孔识别电子密码锁等。IC卡电子密码锁成本低,体积小,卡片本身无须电源等优点占领了一定的市场份额,但是由于有机械接触,会产生接触磨损,而且使用不太方便,在一定程度上限制了它的应用;射频卡式电子密码锁是非接触式电子密码锁,成本也不太高,体积跟IC卡密码锁相当,卡片使用感应电源,重量很轻,技术成熟,受到了广泛的欢迎,但是与IC卡电子密码锁相比,成本偏高;指纹识别电子密码锁和瞳孔识别电子密码锁可靠性很高,安全性是目前应用系统中最高的,但是成本高昂,还没进入大众化使用阶段。 在国外,美国、日本、德国的电子密码锁保密性较好,并结合感应卡技术,生物识别技术,使电子密码锁系统得到了飞跃式的发展。这几个国家的密码锁识别的密码更复杂,并且综合性比较好,已经进入了成熟期,出现了感应卡式密码锁,指纹式密码锁,虹膜密码锁,面部识别密码锁,序列混乱的键盘密码锁等各种技术的系统,它们在安全性,方便性,易管理性等方面都各有特长,新型的电子密码锁系统的应用也越来越广。 基于FPGA的电子密码锁是新型现代化安全管理系统,它集微机自动识别技术和现代安全管理措施为一体,它涉及电子,机械,计算机技术,通讯技术,生物技术等诸多新技术。它是解决重要部门出入口实现安全防范管理的有效措施,适用各种场合,如银行、宾馆、机房、军械库、机要室、办公间、智能化小区、工厂、家庭等。 在数字技术网络技术飞速发展的今天,电子密码锁技术得到了迅猛的发展。它早已超越了单纯的门道及钥匙管理,逐渐发展成为一套完整的出入管理系统。它在工作环境安全、人事考勤管理等行政管理工作中发挥着巨大的作用。在该系统的基础上增加相应的辅助设备可以进行电梯控制、车辆进出控制,物业消防监控、餐饮收费、私家车库管理等,真正实现区域内一卡智能管理。

verilog有限状态机实验报告(附源代码)

有限状态机实验报告 一、实验目的 ●进一步学习时序逻辑电路 ●了解有限状态机的工作原理 ●学会使用“三段式”有限状态机设计电路 ●掌握按键去抖动、信号取边沿等处理技巧 二、实验内容 用三段式有限状态机实现序列检测功能电路 a)按从高位到低位逐位串行输入一个序列,输入用拨动开关实现。 b)每当检测到序列“1101”(不重叠)时,LED指示灯亮,否则灭,例如 i.输入:1 1 0 1 1 0 1 1 0 1 ii.输出:0 0 0 1 0 0 0 0 0 1 c)用八段数码管显示最后输入的四个数,每输入一个数,数码管变化一次 d)按键按下的瞬间将拨动开关状态锁存 i.注意防抖动(按键按下瞬间可能会有多次的电平跳变) 三、实验结果 1.Rst_n为0时数码管显示0000,led灯不亮,rst_n拨为1,可以开始输入,将输 入的开关拨到1,按下按钮,数码管示数变为0001,之后一次类推分别输入1, 0,1,按下按钮后,数码管为1101,LED灯亮,再输入1,LED灯灭,之后再输 入0,1(即共输入1101101使1101重叠,第二次LED灯不亮),之后单独输入

1101,LED灯亮 2.仿真图像 刚启动时使用rst_n 一段时间后 其中Y代表输出,即控制led灯的信号,sel表示数码管的选择信号,seg表示数码管信号 四、实验分析 1、实验基本结构

其中状态机部分使用三段式结构: 2、整体结构为:

建立一下模块: Anti_dither.v 输入按键信号和时钟信号,输出去除抖动的按键信号生成的脉冲信号op 这一模块实现思路是利用按钮按下时会持续10ms以上而上下抖动时接触时间不超过10ms来给向下接触的时间计时,达到上限时间才产生输出。 Num.v 输入op和序列输入信号A,时钟信号clk和复位信号,复位信号将num置零,否则若收到脉冲信号则将num左移一位并将输入存进最后一位。输出的num即为即将在数码管上显示的值 Scan.v 输入时钟信号,对其降频以产生1ms一次的扫描信号。 Trigger.v 这一模块即为状态机模块,按三段式书写。 整个模块的输入为时钟信号,脉冲信号,序列输入变量,复位信号,输出LED灯控制信号Y。 第一段是状态转换模块,为时序逻辑电路,功能是描述次态寄存器迁移到现态寄存器。即如果收到复位信号将现态置零,否则将上次得到的next_state赋给current_state。

基于FPGA的VerilogHDL数字钟设计

基于FPGA的Verilog-HDL数字钟设计--

————————————————————————————————作者:————————————————————————————————日期:

基于FPGA的Verilog HDL数字钟设计 专业班级姓名学号 一、实验目的 1.掌握可编程逻辑器件的应用开发技术——设计输入、编译、仿真和器件编程; 2.熟悉一种EDA软件使用; 3.掌握Verilog设计方法; 4.掌握分模块分层次的设计方法; 5.用Verilog完成一个多功能数字钟设计; 6.学会FPGA的仿真。 二、实验要求 功能要求: 利用实验板设计实现一个能显示时分秒的多功能电子钟,基本功能: 1)准确计时,以数字形式显示时、分、秒,可通过按键选择当前显示时间范围模式; 2)计时时间范围00:00:00-23:59:59 3)可实现校正时间功能; 4)可通过实现时钟复位功能:00:00:00 扩展功能: 5)定时报:时间自定(不要求改变),闹1分钟(1kHz)---利用板上LED或外接电路实现。 6)仿广播电台正点报时:XX:59:[51,53,55,57(500Hz);59(1kHz)] ---用板上LED或外接 7)报整点时数:XX:00:[00.5-XX.5](1kHz),自动、手动---用板上LED或外接

8)手动输入校时; 9)手动输入定时闹钟; 10)万年历; 11)其他扩展功能; 设计步骤与要求: 1)计算并说明采用Basys2实验板时钟50MHz实现系统功能的基本原理。 2)在Xilinx ISE13.1 软件中,利用层次化方法,设计实现模一百计数及显示的电路系 统,设计模块间的连接调用关系,编写并输入所设计的源程序文件。 3)对源程序进行编译及仿真分析(注意合理设置,以便能够在验证逻辑的基础上尽快 得出仿真结果)。 4)输入管脚约束文件,对设计项目进行编译与逻辑综合,生成下载所需.bit文件。 5)在Basys2实验板上下载所生成的.bit文件,观察验证所设计的电路功能。 三、实验设计 功能说明:实现时钟,时间校时,闹铃定时,秒表计时等功能 1.时钟功能:完成分钟/小时的正确计数并显示;秒的显示用LED灯的闪烁做指示; 时钟利用4位数码管显示时分; 2.闹钟定时:实现定时提醒及定时报时,利用LED灯代替扬声器发出报时声音; 3.时钟校时:当认为时钟不准确时,可以分别对分钟和小时位的值进行调整; 4.秒表功能:利用4个数码管完成秒表显示:可以实现清零、暂停并记录时间等功能。 秒表利用4位数码管计数; 方案说明:本次设计由时钟模块和译码模块组成。时钟模块中50MHz的系统时钟clk分频产

Xilinx FPGA PCIE Linux驱动程序

// (c) Copyright 2009 聳2009 Xilinx, Inc. All rights reserved. // // This file contains confidential and proprietary information // of Xilinx, Inc. and is protected under U.S. and // international copyright and other intellectual property // laws. // // DISCLAIMER // This disclaimer is not a license and does not grant any // rights to the materials distributed herewith. Except as // otherwise provided in a valid license issued to you by // Xilinx, and to the maximum extent permitted by applicable // law: (1) THESE MATERIALS ARE MADE AVAILABLE "AS IS" AND // WITH ALL FAULTS, AND XILINX HEREBY DISCLAIMS ALL WARRANTIES // AND CONDITIONS, EXPRESS, IMPLIED, OR STATUTORY, INCLUDING // BUT NOT LIMITED TO WARRANTIES OF MERCHANTABILITY, NON- // INFRINGEMENT, OR FITNESS FOR ANY PARTICULAR PURPOSE; and // (2) Xilinx shall not be liable (whether in contract or tort, // including negligence, or under any other theory of // liability) for any loss or damage of any kind or nature // related to, arising under or in connection with these // materials, including for any direct, or any indirect, // special, incidental, or consequential loss or damage // (including loss of data, profits, goodwill, or any type of // loss or damage suffered as a result of any action brought // by a third party) even if such damage or loss was // reasonably foreseeable or Xilinx had been advised of the // possibility of the same. // // CRITICAL APPLICATIONS // Xilinx products are not designed or intended to be fail- // safe, or for use in any application requiring fail-safe // performance, such as life-support or safety devices or // systems, Class III medical devices, nuclear facilities, // applications related to the deployment of airbags, or any // other applications that could lead to death, personal // injury, or severe property or environmental damage // (individually and collectively, "Critical // Applications"). Customer assumes the sole risk and // liability of any use of Xilinx products in Critical // Applications, subject only to applicable laws and // regulations governing limitations on product liability. // // THIS COPYRIGHT NOTICE AND DISCLAIMER MUST BE RETAINED AS // PART OF THIS FILE AT ALL TIMES. //-------------------------------------------------------------------------------- //-- Filename: xbmd.c //-- //-- Description: XBMD device driver. //-- //-- XBMD is an example Red Hat device driver which exercises XBMD design //-- Device driver has been tested on Red Hat Fedora FC9 2.6.15. //--------------------------------------------------------------------------------

第10章例题verilog源代码(夏宇闻版)

第十章例题 module add_4( X, Y, sum, C); input [3 : 0] X, Y; output [3: 0] sum; output C; assign {C, Sum } = X + Y; endmodule //而16位加法器只需要扩大位数即可,见下例: module add_16( X, Y, sum, C); input [15 : 0] X, Y; output [15 : 0] sum; output C; assign {C, Sum } = X + Y; endmodule 快速乘法器常采用网格形式的迭带阵列结构,图10.3示出两个四位二进制数相乘的结构图,//用Verilog HDL来描述乘法器是相当容易的,只需要把运算表达式写出就可以了,见下例。module mult_4( X, Y, Product); input [3 : 0] X, Y; output [7 : 0] Product; assign Product = X * Y; endmodule // 而8位乘法器只需要扩大位数即可,见下例: module mult_8( X, Y, Product); input [7 : 0] X, Y; output [15 : 0] Product; assign Product = X * Y; endmodule

// 下面就是一个位数可以由用户定义的比较电路模块: module compare_n ( X, Y, XGY, XSY, XEY); input [width-1:0] X, Y; output XGY, XSY, XEY; reg XGY, XSY, XEY; parameter width = 8; always @ ( X or Y ) // 每当X 或Y 变化时 begin if ( X = = Y ) XEY = 1; // 设置X 等于Y的信号为1 else XEY = 0; if (X > Y) XGY = 1; // 设置X 大于Y的信号为1 else XGY = 0; if (X < Y) XSY = 1; // 设置X 小于Y的信号为1 else XSY = 0; end endmodule //下面就是带使能控制信号(nCS)的数据位宽可以由用户定义的(8位)八路数据通道选择器模块: module Mux_8( addr,in1, in2, in3, in4, in5, in6, in7, in8, Mout, nCS); input [2:0] addr; input [width-1:0] in1, in2, in3, in4, in5, in6, in7, in8; input nCS; output [width-1:0] Mout; parameter width = 8; always @ (addr or in1 or in2 or in3 or in4 or in5 or in6 or in7 or in8 or nCS) begin if (!nCS) //nCS 低电平使多路选择器工作 case(addr) 3’b000: Mout = in1; 3’b001: Mout = in2; 3’b010: Mout = in3; 3’b011: Mout = in4;

基于FPGA的SDRAM实验Verilog源代码

// megafunction wizard: %ALTPLL% // GENERATION: STANDARD // VERSION: WM1.0 // MODULE: altpll // ============================================================ // File Name: clk_ctrl.v // Megafunction Name(s): // altpll // // Simulation Library Files(s): // altera_mf // ============================================================ // ************************************************************ // THIS IS A WIZARD-GENERATED FILE. DO NOT EDIT THIS FILE! // // 11.0 Build 208 07/03/2011 SP 1 SJ Full Version // ************************************************************ //Copyright (C) 1991-2011 Altera Corporation //Your use of Altera Corporation's design tools, logic functions //and other software and tools, and its AMPP partner logic //functions, and any output files from any of the foregoing //(including device programming or simulation files), and any //associated documentation or information are expressly subject //to the terms and conditions of the Altera Program License //Subscription Agreement, Altera MegaCore Function License //Agreement, or other applicable license agreement, including, //without limitation, that your use is for the sole purpose of //programming logic devices manufactured by Altera and sold by //Altera or its authorized distributors. Please refer to the //applicable agreement for further details. // synopsystranslate_off `timescale 1 ps / 1 ps // synopsystranslate_on moduleclk_ctrl ( areset, inclk0, c0, c1, c2,

(硬件实现代图)FPGA驱动LCD1602

作者:Lumin QQ:474062042(有改进的地方,希望大家告诉我一下) 于成都理工大学 说明:该驱动只是用来练习状态机,所以没有追求高速度,时钟是分频到毫秒级处理 实际效果: 显示我的英文名Lumin 引脚定义: 大家需要关心的是三个控制线RS,RW,EN 数据总线DATA

驱动的顶层模块及其端口定义 设计思路: 1.该设计使用了一个状态机,实现LCD1602显示字符功能 2. 时序图 关于r/w: 因为液晶只需要写不需要读,所以RW=0,表示液晶一直处于写状态 写命令时: 首先RS=0,E=0同时数据出线在总线上面,延时一段时间,等待数据稳定然后E一个上升沿并保持一段时间,然后拉低为下一次写准备写数据时: 首先RS=1,E=0同时数据出线在总线上面,延时一段时间,等待数据稳定然后E一个上升沿并保持一段时间,然后拉低为下一次写准备 3. 状态机设计状态机设计方法 我在很多书上看了状态机什么经典的三段式,两段式状态机写法。实践来都不好用,可能自己学的不好(知道问题的给我说下)。后面自己发明了一种,现在写了好几驱动,都正确的。模板下面。 TYPE STATE IS(s0,s1,s2,s3);-- 举例只用4个状态 SIGNAL Current_State :STATE:=s0;-- 模板不要NEXT_STATA,我实践来要NEXT_STATA的不好用SIGNAL s0_delay:INTEGER RANGE 1 TO 1000;-- 有多少状态就多少个状态延时信号,如果该状

态不延时,最后不要就 SIGNAL s1_delay:INTEGER RANGE 1 TO 1000; SIGNAL s2_delay:INTEGER RANGE 1 TO 1000; SIGNAL s3_delay:INTEGER RANGE 1 TO 1000; process(Temp_1ms,Current_State) begin if(rising_edge(Temp_1ms)) then case Current_State when s0 =>Lcd_rs<='0'; Lcd_en<='0';data <=x"00" if( s0_delay=100) then Current_State<=s1;--靠颜色的这段话来控制每个状态延时多久怎么走。 s0_delay<=0; else s0_delay<=s0_delay+1; end if; end case; end if; end process; 4. 状态机设计