SystemVerilog语言简介3

SystemVerilog语言简介(三)

15. 强制类型转换

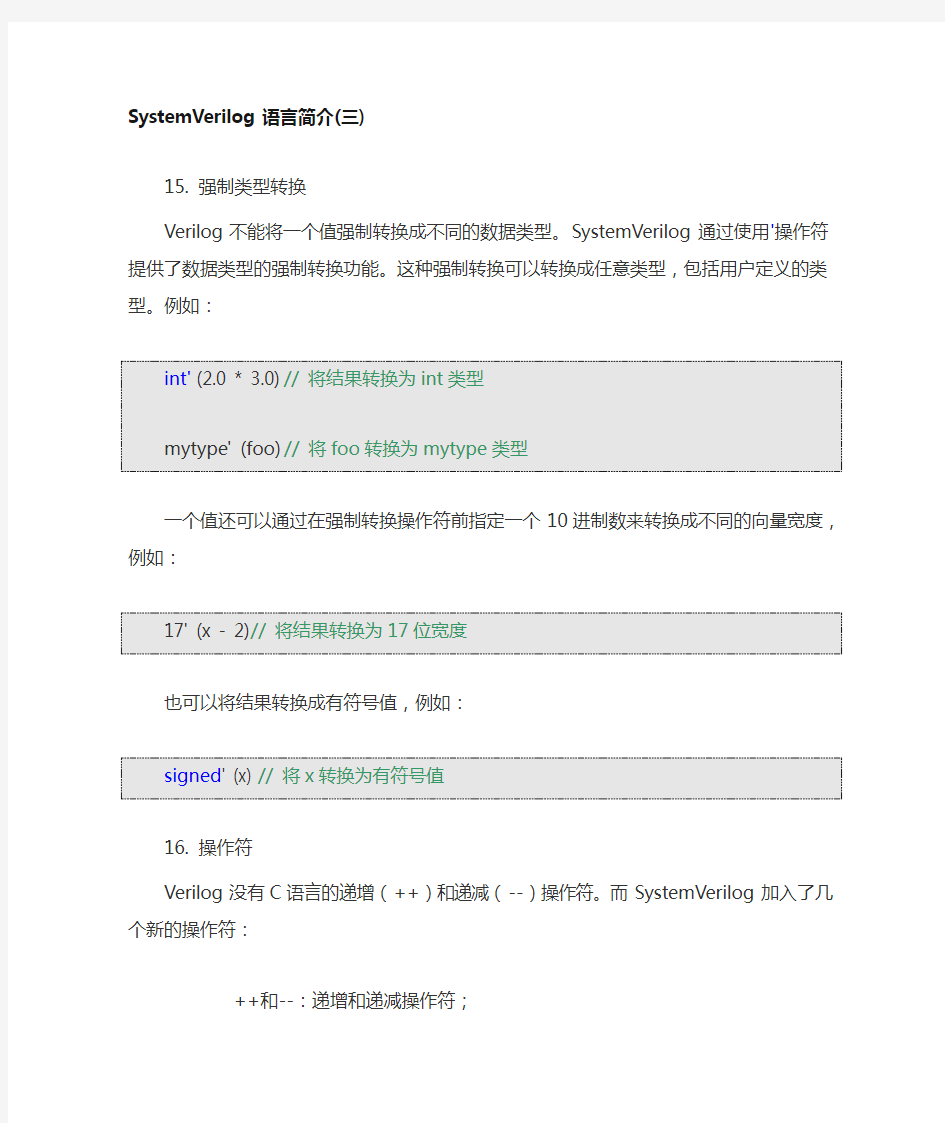

Verilog不能将一个值强制转换成不同的数据类型。SystemVerilog通过使用'操作符提供了数据类型的强制转换功能。这种强制转换可以转换成任意类型,包括用户定义的类型。例如:

int' (2.0 * 3.0) // 将结果转换为int类型

mytype' (foo) // 将foo转换为mytype类型

一个值还可以通过在强制转换操作符前指定一个10进制数来转换成不同的向量宽度,例如:

17'(x - 2) // 将结果转换为17位宽度

也可以将结果转换成有符号值,例如:

signed' (x) // 将x转换为有符号值

16. 操作符

Verilog没有C语言的递增(++)和递减(--)操作符。而SystemVerilog 加入了几个新的操作符:

●++和--:递增和递减操作符;

●+=、-=、*=、/=、%=、&=、^=、|=、<<=、>>=、<<<=和>>>=赋值

操作符;

17. 唯一性和优先级决定语句

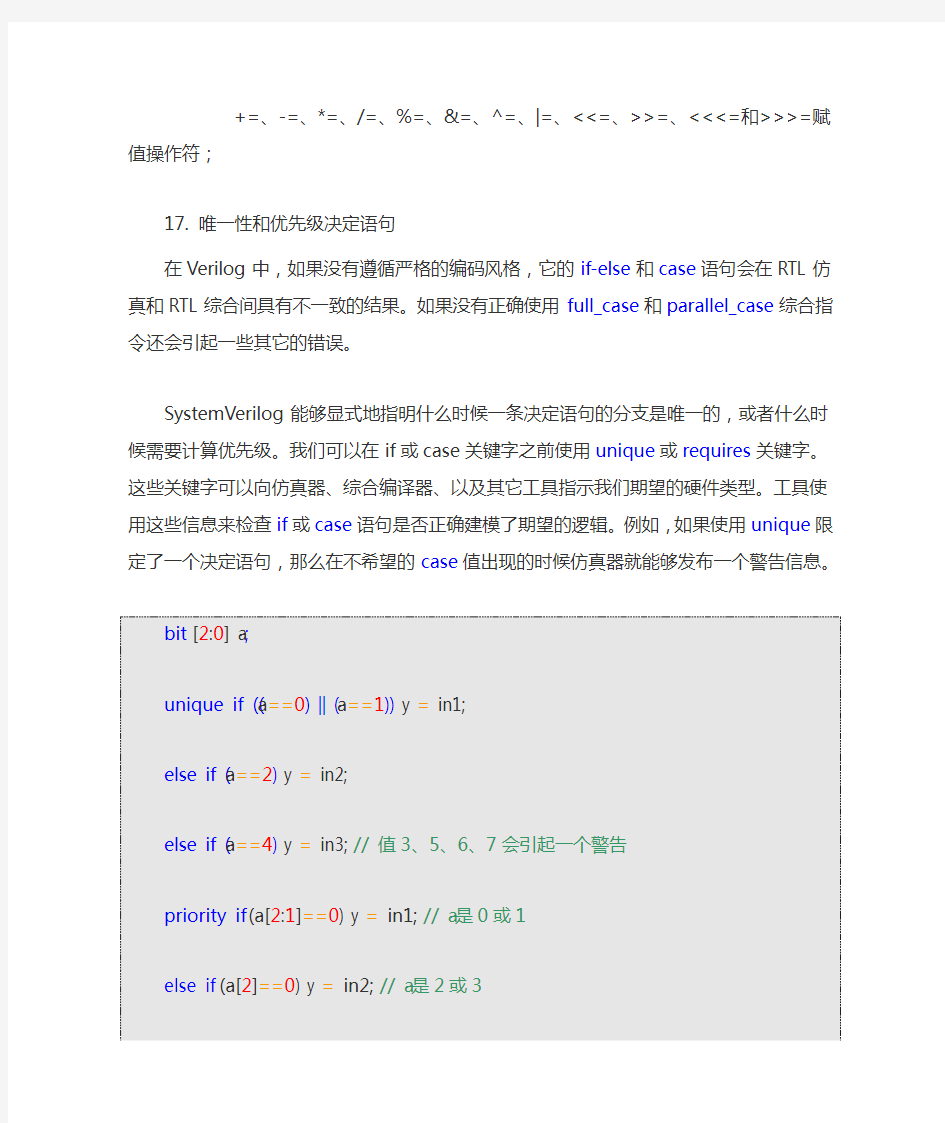

在Verilog中,如果没有遵循严格的编码风格,它的if-else和case语句会在RTL仿真和RTL综合间具有不一致的结果。如果没有正确使用full_case和parallel_case综合指令还会引起一些其它的错误。

SystemVerilog能够显式地指明什么时候一条决定语句的分支是唯一的,或者什么时候需要计算优先级。我们可以在if或case关键字之前使用unique或requires关键字。这些关键字可以向仿真器、综合编译器、以及其它工具指示我们期望的硬件类型。工具使用这些信息来检查if或case语句是否正确建模了期望的逻辑。例如,如果使用unique限定了一个决定语句,那么在不希望的case 值出现的时候仿真器就能够发布一个警告信息。

bit [2:0] a;

unique if ((a==0) || (a==1)) y = in1;

else if (a==2) y = in2;

else if (a==4) y = in3; // 值3、5、6、7会引起一个警告

priority if (a[2:1]==0) y = in1; // a是0或1

else if (a[2]==0) y = in2; // a是2或3

else y = in3; // 如果a为其他的值

unique case (a)

0, 1: y = in1;

2: y = in2;

4: y = in3;

endcase // 值3、5、6、7会引起一个警告

priority casez (a)

2'b00? : y = in1; // a是0或1

2'b0?? : y = in2; // a是2或3

default : y = in3; //如果a为其他的值

endcase

18. 底部检测的循环

Verilog包含for、while和repeat循环,这几个循环都是在循环的起始处检测循环条件。SystemVerilog加入了一个do-while循环,这种循环在执行语句的结尾处检测循环条件。

19. 跳转语句

在语句的执行过程中,C语言提供了几种方式来跳转到新的语句,包括:return、break、continue和goto。在Verilog中除了通过使用disable语句跳转到语句组的尾部外,没有提供任何其它跳转语句。使用disable语句执行中止和继续功能要求加入块的名字,并且会产生不直观的代码。SystemVerilog加入了C语言的break和continue关键字,这两个关键字不要求使用块名字。另外,SystemVerilog还加入了一个return关键字,它可以用来在任何执行点上退出一个任务或函数。

●break:退出一个循环,与C语言相同;

●continue:跳转到一个循环的尾部,与C语言相同;

●return表达式:退出一个函数;

●return:退出一个任务或void类型的函数。

SystemVerilog没有包含C语言中的goto语句。

20. 块名字和语句标签

在Verilog中,我们可以通过在begin或fork关键字之后指定名字来为begin-end或fork-jion语句指定名字。这个指定的名字代表整个语句块。SystemVerilog还允许在end或jion关键字之后指定一个匹配的块名字。这种机制很容易将end或jion与对应的begin或fork联系起来,尤其是在一个长的块或嵌套的块中。块结尾处的名字是可选的,但如果使用的话,它必须与块起始处的名字相同。例如:

begin: foo // 在begin之后的块名字

…

fork: bar // 具有名字的嵌套的块

…

jion: bar // 必须具有相同的名字

…

end: foo // 必须具有相同的名字

SystemVerilog还允许像C语言一样为单个语句设置标签。语句标签放置在语句的前面,用来标识这条语句。例如:

initial begin

test1: read_enable = 0;

…

test2: for (i=0; i<=255; i++)

…

end

21. 对事件控制的增强

Verilog使用@标记来控制基于特定事件的执行流,SystemVerilog增强了@事件控制。

●有条件的事件控制

@标记的一个基本应用就是推断一个具有使能输入的锁存器。下面的例子演示了一个锁存器建模的基本风格。

always @(data or en)

if (en) y <= data;

这种编码风格对仿真来说是效率低下的,因为即使在使能输入无效的时候,数据输入的每次改变都会触发事件控制。

SystemVerilog在事件控制中加入了一个iff条件。只有iff条件为真的条件下,事件控制才会被触发。通过将使能判断移入到事件控制里面,使得只有在锁存器输出能够改变的时候事件控制才会被触发。例如:

always @(a or en iff en==1)

y <= a;

●事件控制中的表达式

Verilog允许在@事件控制列表中使用表达式,例如:

always @((a * b))

always @(memory[address])

在第一个例子中,是当操作数发生改变的时候还是只有当运算结果发生改变的时候才会触发事件控制?在第二个例子中,是当memory的地址发生变化的时候还是只有当memory的值发生变化的时候才会触发事件控制?当@事件控制中包含表达式的时候,IEEE Verilog标准允许仿真器进行不同的优化。这就可能导致在不同的仿真器间有不同的仿真结果,可能还会导致仿真与综合之间的结果不一致。SystemVerilog加入了一个changed关键字,在事件控制列表中它被用作一个修饰符。@(changed (表达式))能够显式地定义只有当表达式的结果发生改变的时候才会触发事件控制。例如:

always @(changed (a * b))

always @(changed memory[address])

●事件控制中的赋值

Verilog不允许在事件控制中使用赋值。SystemVerilog允许在事件控制中使用赋值表达式。事件控制仅仅敏感于赋值表达式右侧的变化。例如:always @(y = a * b)

22. 新的过程

Verilog使用always过程来表示时序逻辑、组合逻辑和锁存逻辑的RTL模型。综合工具和其它软件工具必须根据过程起始处的事件控制列表以及过程内的语句来推断always过程的意图。这种推断会导致仿真结果和综合结果之间的不一致。SystemVerilog增加了三个新的过程来显式地指示逻辑的意图。

●always_ff:表示时序逻辑的过程;

●always_comb:表示组合逻辑的过程;

●always_latch:表示锁存逻辑的过程。

例如:

always_comb @(a or b or sel) begin

if (sel) y = a;

else y = b;

end

软件工具能够检查事件控制敏感列表和过程的内容来保证逻辑的功能匹配过程的类型。例如,工具能够检查一个always_comb过程能够敏感过程内读取的所有外部值,对逻辑的每一个分支的相同变量进行赋值,并且检查分支是否覆盖了所有可能的条件。如果任何一个条件没有满足,软件工具均会报告该过程没有正确建模组合逻辑。

北京语言大学翻译硕士各细分专业以及学费介绍

北京语言大学翻译硕士各细分专业以及 学费介绍 翻译硕士专业学位研究生,即MTI(Master of Translation and Interpreting)是为了适应市场经济对应用型高层次专门人才的需求,国务院学位委员会于2007年1月批准设置的一种专业学位。2008年开始招生,2009年面向应届本科毕业生招生。 MTI教育重视实践环节,强调翻译实践能力的培养。翻译硕士专业学位的培养目标为具有专业口笔译能力的高级翻译人才。翻译硕士专业学位获得者应具有较强的语言运用能力、熟练地翻译技能和宽广的知识面,能够胜任不同专业领域所需的高级翻译工作。 全日制MTI招生对象为具有国民教育序列大学本科学历(或本科同等学力)人员,具有良好的双语基础。作为我国专业硕士之一,MTI不仅面向英语专业的考生,同时也鼓励非外语专业毕业生及有口笔译时间经验者报考,其中非外语专业的毕业生更受到报考院校的欢迎。 北语翻译硕士全日制学费总额为18000,学制为两年。 北语翻译硕士的培养目标是培养适应中国政治、经济、文化、体育、建筑等领域所需要的高层次、高素质、高技能的应用型口笔译人才。 专业方向 ①英语笔译、英语口译 考试科目为: 1.思想政治理论 2.翻译硕士英语 3.英语翻译基础 4.汉语写作与百科知识 ②日语笔译、日语口译 考试科目为: 1.思想政治理论 2.翻译硕士日语 3.日语翻译基础 4.汉语写作与百科知识 ③法语笔译、法语口译 考试科目为: 1.思想政治理论 2.翻译硕士法语 3.法语翻译基础 4.汉语写作与百科知识 ④朝鲜语笔译、朝鲜语口译 考试科目为: 1.思想政治理论 2.翻译硕士朝鲜语 3.朝鲜语翻译基础 4.汉语写作与百科知识

北语语用专业00-15年初试真命题(语言知识学习学概论)

北京语言大学语用专业00--15年语言学概论考研真题 2015年 1.名词解释—自源文字,组合关系,语境义,语义场,形态,音质音位 2.判断并说明理由 (1)组合,聚合关系不仅仅存在于语法中。 (2)每一种语言或方言中的音位都处于双向聚合群中。 (3)语素和词不仅是词汇单位,也是语法单位。 (4)地域方言和社会方言的差别只表现在词汇系统中。 3.分析题 (1)写出普通话中a的四个音位变体,并分析这四个音位变体是如何产生。 (2)方言根据不同的角度可以分为哪些类型?并分析随着社会的发展,地域方言会有什么发展趋势。 (3)什么是借词?根据下面的例子归纳借词的类型。剑桥,茶道,啤酒,基因,俱乐部,克隆,罗曼蒂克,CPU,霓虹灯 (4)分析下列“老”和“子”哪些属于词根语素,哪些属于词缀语素 老板,老鹰,老汉,老式,老化,老公 孩子,电子,棋子,模子, (5)用层次分析法分析句子,并分析"V在"划分的理由 我和哥哥确实都生在河北石家庄。 我的老板王立出生在首都北京。

4.简答题 (1)区别特征是不是等同于发音特征?如何确定具体某个辅音音位的区别特征? (2)什么是词缀?什么是词尾?说说它们之间的主要区别。 (3)什么是变换分析?用具体例子说明如何用变换分析消解多义结构。 5.论述题 (1)以一个具体语言为例说明语言中语法演变的具体表现。 (2)什么是语言换用和底层遗留?说明底层遗留产生的原因以及具体体现。 2014年 语言学概论 一、名词解释并举例。 社会方言地域方言语义特征语义指向音素音位 表音素文字表音位文字单纯词合成词组合关系聚合关系 同化异化隐喻换喻 二、选择 1、语言层次的上层包括 A、音位、语素、词语、短语 B、音位、语素、词语 C、音素、语素、词语 D、语素、词语、短语、句子 2、波浪理论提出者A A、施密特 B、葆朴 C、 D、 3、辅助性交际工具有B

SystemVerilog

SystemVerilog 语言简介 SystemVerilog 是一种硬件描述和验证语言(HDVL),它基于 IEEE 1364-2001 Verilog 硬件描述语言 (HDL) 并对其进行了扩展, , 包括扩充了 C 语言数据类型、结构、压缩和非压缩数组、 接口、断 言等等, 这些都使得 SystemVerilog 在一个更高的抽象层次上提高了 设计建模的能力。SystemVerilog 由 Accellera 开发,它主要定位在 芯片的实现和验证流程上, 并为系统级的设计流程提供了强大的连接 能力。 下面我们从几个方面对 SystemVerilog 所作的增强进行简要的 介绍, 期望能够通过这个介绍使大家对 SystemVerilog 有一个概括性 的了解。 1. 接口(Interface) Verilog 模块之间的连接是通过模块端口进行的。为了给组成设 计的各个模块定义端口, 我们必须对期望的硬件设计有一个详细的认 识。不幸的是,在设计的早期,我们很难把握设计的细节。而且,一 旦模块的端口定义完成后,我们也很难改变端口的配置。另外,一个 设计中的许多模块往往具有相同的端口定义,在 Verilog 中,我们必 须在每个模块中进行相同的定义,这为我们增加了无谓的工作量。 SystemVerilog 提供了一个新的、高层抽象的模块连接,这个连 接被称为接口(Interface)。接口在关键字 interface 和 endinterface 之间定义,它独立于模块。接口在模块中就像一个单一的端口一样使 用。在最简单的形式下,一个接口可以认为是一组线网。例如,可以 将 PCI 总线的所有信号绑定在一起组成一个接口。通过使用接口, 我们在进行一个设计的时候可以不需要首先建立各个模块间的互连。 随着设计的深入,各个设计细节也会变得越来越清晰,而接口内的信 号也会很容易地表示出来。当接口发生变化时,这些变化也会在使用 该接口的所有模块中反映出来,而无需更改每一个模块。 下面是一个 接口的使用实例: interface chip_bus; // 定义接口 wire read_request, read_grant; wire [7:0] address, data; endinterface: chip_bus

更多免费资料下载请进: https://www.360docs.net/doc/6411535710.html, 中国最大的免费课件资料库

北京语言大学简介 Beijing Language and Culture University.doc

北京语言大学简介 北京语言大学是中国教育部直属高等学校,是在周恩来总理的亲自关怀下建立的,创办于1962年。1964年6月定名为北京语言学院,1974年毛泽东主席为学校题写校名,1996年6月更名为北京语言文化大学,2002年校名简化为北京语言大学。 北京语言大学是中国唯一一所以对来华留学生进行汉语、中华文化教育为主要任务的国际型大学,素有“小联合国”之称;学校对中国学生进行外语、中文、信息科学、金融等专业教育,同时承担着培养汉语师资、出国留学预备人员出国前的外语培训工作等任务。经过五十多年的发展,北语已经发展成为一所以语言教学与研究为特色和优势,中文、外语及相关学科协同发展的多科性大学,已成为我国中外语言、文化研究的学术重镇和培养涉外高级人才的摇篮。2014年,学校明确了建设世界一流语言大学的奋斗目标和构筑四大学术方阵的战略构想。 北京语言大学从事汉语国际教育和中华文化教育历史最长,规模最大,师资力量最雄厚。迄今为止,学校已经为世界上176个国家和地区培养了16万余名懂汉语、熟悉中华文化的外国留学生。其中很多校友已经成为学界、政界、商界的知名人士。现任联合国副秘书长、联合国日内瓦办事处总干事卡塞姆?托卡耶夫,埃塞俄比亚总统穆拉图?特肖梅?沃图,哈萨克斯坦政府总理卡里姆?马西莫夫,俄罗斯外交部副部长伊戈尔?莫尔古洛夫,德国汉学家顾彬,美国物理学家、诺贝尔奖获得者埃里克?康奈尔等知名人士都曾在北语学习过。此外,北语还为中国培养了数以十万计的优秀人才,其中包括大批在出国留学人员培训部接受过专门外语培训的公派留学人员,现在他们多已成为国家各个领域的栋梁。 20世纪90年代以来,北语一方面保持在汉语国际教育领域的特色和优势,另一方面,积极发展相关学科,学科涵盖文学、经济学、法学、工学、历史学、教育学、管理学和艺术学等七个门类,现有博士后流动站1个、博士专业17个(实际招生)、硕士专业45个(实际招生)、本科专业27个。其中国家重点学科1个,北京市重点学科10个。学校目前设有三个学部、六个直属学院(教学部)和两个科研院所,分别为:汉语国际教育学部(含汉语学院、汉语进修学院、汉语速成学院、预科教育学院、华文学院)、外国语学部(含英语学院、高级翻译学院、应用外语学院、东方语言文化学院、西方语言文化学院、中东学院)、人文社会科学学部(含汉语教育学院、人文学院、政治学院、国际关系学院、新闻传播学院);信息科学学院、商学院、

2018年北京语言大学艺术类招生简章

北京语言大学2018 年艺术类本科招生简章 北京语言大学是教育部直属高校,是中国唯一一所以对来华留学生进行汉语和中华文化教育为主要任务的国际型大学,素有“小联合国”之称。艺术学院以传承、传播中华优秀传统艺术为宗旨,招收具有一定美术、书法和音乐基础的中国本科生。 一、招生计划 二、报名条件 1.符合教育部发布的普通高等学校年度招生工作文件中的报名条件。 2.色觉异常者(色盲、色弱)不得报考绘画和书法专业。 三、报名、缴费 1. 报名方式:登录北京语言大学本科招生网,进入“网上报名—艺术类”,按要求注册并如实填写报名信息。 2.报名时间:2018 年1 月19 日至2 月23 日。 3.网上缴费:考生提交报名申请后,须学校审核通过后方可缴费。根据北京市相

关规定,报考绘画、书法专业考生应缴纳美术类校考费用160 元/专业/人;报考音乐学(音乐国际教育与传播)专业考生应缴纳初试报名考试费100 元/人、复试考试费80 元/人、三试考试费80 元/人。 4.打印准考证:考生完成缴费后,可在规定时间内确认考试并打印《北京语言大学2018 年艺术类招生考试准考证》,使用A4 纸打印,黑白彩色均可。 5.绘画、书法可以兼报,音乐学(音乐国际教育与传播)不可兼报。如考生绘画、书法均校考合格,按照考生填报的志愿,顺序认定。 6.注意事项:①未按要求报名、缴费等影响考试和录取的,后果由考生本人承担; ②考生缴费后,无论考试与否,所交费用恕不退还;③所有专业考试均不接受现场报名。 四、专业考试 (一)考生须知 1.请考生务必按规定时间完成各阶段考试确认和缴费。考试结束后,考生可通过报名系统查询专业课成绩和校考合格名单。请关注报名系统信息,恕不另行通知。 2.考生须携带本人身份证原件及复印件、《北京语言大学2018 年艺术类招生考试准考证》,按指定的时间、地点参加专业考试。 3.考生不得携带与考试无关物品进入考场。报考绘画、书法专业的考生,考试所用纸张由学校统一提供,考生所用绘画、书法用具等由考生自备。报考音乐学(音乐国际教育与传播)的考生,所用服装、乐器等由考生自备。报考声乐类的考生可自带钢琴伴奏,也可自愿选择使用学校提供的钢琴伴奏。 (二)考试安排 1. 绘画

《高级语言程序设计》复习题及答案

一、选择题 1.以下叙述正确的是( ): A)在C程序中,main函数必须位于程序的最前面 B) C程序的每行只能写一条语句 C) C语言使用库函数实现输入输出操作 D)注释中的拼写错误会影响编译结果 2、以下说法中正确的是() A) C语言程序总是从第一个的函数开始执行 B) C语言程序总是从main()函数开始执行 C)在C语言程序中,要调用的函数必须在main()函数中定义 D)C语言程序中的main()函数必须放在程序的开始部分 3、下列选项种说法正确的是( ) A)函数由声明部分和执行部分两部分组成 B)语言中main函数一定在程序的开始部分 C)C语言程序总是从第一个定义的函数开始执行 D)C程序的每行中只能写一条语句 4、设有说明:int a;float b; char c; double d; 则表达式1.3*a+2*b*c+d*(int) 2.6 值的类型为( )。 A)doubleB) char C) floatD) int 5、C语言的标识符只能由字母、数字和下划线三种字符组成,且第一个字符( ) A)必须为字母 B)必须为下划线 C)必须为字母或下划线 D)可以是字母、数字和下划线中任一种字符 6、以下不正确的C语言标识符是( )。 A) ABC B) abc C)a_bc D) void 7、下列运算符中优先级最高的是( ) A)< B)+ C)&& D)!= 8、以下选项中属于C语言中合法关键字的是( ) A)Float B)abc C)int D)CASE 9、若x、i、j和k都是int型变量,计算下面表达式后,x的值为( ) x=(i=4,j=16,k=32) A)4 B)16 C)32 D)52 10、在C语言中,要求数据必须是整型的运算符是( ) A)/ B)+ + C)!=D) % 11、若整型变量x的值为8,则下列表达式中值为1的表达式是 A)x+=x-=x B) x%=x-1 C) x%=x%=3 D) x/=x+x 12、若w=1,x=2,y=3,z=4,则条件表达式“w > x? w : y< z ? y : z”的值是( ) A)4 B)3 C)2 D)1 13、有以下程序,程序运行后的输出结果是。 main() {inti=1,j=2,k=3; if(i++==1&&(++j==3||k++==3)) printf("%d %d %d\n",i,j,k); }

system verilog教程

SystemVerilog Tutorials 下面的手册会帮助你了解一些SystemVerilog中最重要的新特点。手册还提供了一些代码样本和例子使你可以对语言有更好"感觉"。这些辅导假设你们已经了解了一些Verilog语言。如果没有,你可以先去看看Verilog设计者指南(V erilog Designer’s Guide)。 * Data types * RTL design * Interfaces * Clocking * Assertion-based verification * Classes * Testbench automation and constraints * The Direct Programming Interface (DPI) SystemVerilog 的数据类型 这个手册将描述Systemverilog新引进的数据类型。他们大多数都是可以综合的,并且可以使RTL级描述更易于理解和书写。 整型和实型 SystemVerilog引进了几种新的数据类型。C语言程序员会熟悉其中的大多数。引进新的数据类型构思是这样的,如果C语言和SystemVerilog有相同的数据类型可以使C语言算法模型更容易的转化为SystemVerilog模型。 Verilog的变量类型有四态:既是0,1,X,Z。SystemVerilog引进了新的两态数据类型,每一位只可以是0或是1。当你不需要使用的X和Z值时,譬如在写Testbench和做为for语句的循环变量。使用两态变量的RTL级模型,可以使模拟器更有效率。并且使用得当的话将不会对综合结果产生影响。 二态整型 类型描述例子 Bit user-defined size bit [3:0] a_nibble; Byte 8 bits, unsigned byte a, b; Shortint 16 bits, signed shortint c, d; Int 32 bits, signed int i,j; Longint 64 bits, signed longint lword;

北语对外教学

北语对外教学 1.活动记录 08.10.17 地点:北京语言大学某多媒体教室 事件: hoho,对外教学果然很有趣哈。 骑车到了北语,唔,从北医去还是很近的。两个mm在校门口接我去了教室。这次对外教学是那边心理协会手语部的第一次手语班,一路都有他们的人做指引,所以还是有点紧张,毕竟他们还是很看重这次活动的,还好之前准备还算充分吧。 到了教室,唔,大概有四五十个人的样子。那边手语部长先发言,作介绍(他们海报上居然写了请到北京大学的手语老师= =),然后他们表演了自己的《隐形的翅膀》,hoho,看着还是很有感觉的。然后我就开始了。 完全是手语班的模式,前半部分教了字母,给每个字母做了词汇的扩展,看他们学的还是比较有趣的,然后打《字母歌》。一点都不奇怪的所有人都崩溃了,hoho。不过那边同学热情真的很高的,一再要求继续练习。后来又教了教材的第一课,因为他们不想只学字母,虽然我一再强调字母的重要性,hoho。 后半部分我教了《阳光总在风雨后》,可能稍有点难,不过效果还不错哈哈。 唔,大体就是这样子啦。最后,谢谢婷儿jj帮我之前准备^^。 人物:DittoLi 感想: 唔,对外教学就是很有趣的啦。而且北语这个项目很有发展的趋势,因为其实我们做的也是一项普及手语的事情嘛,可以好好发展一下嘿嘿。 另外,他们说要来明天的迎新晚会和后天的手语班。 p.s.: 附件里是我今天做得《阳光》的课件,因为找了半天没找到当时的。hoho。呼吁把这些课件整理整理,到时候就不用重新做了哈。 08.10.31 地点:北大->北医逸夫楼咖啡厅->北语图书馆五层影音教室 人物:DittoLi、任妍(某个团)、王文伟(小泡泡团)、秦思学(某个团)、蒋玉娇(某个团) 要大赞一下今天去的几个孩子,虽然里面还有比我大的师兄^^,呵呵。第一次参加对外教学就在满满一个教室的人前面教手语了,呵呵。虽然准备稍稍有点 匆忙,但感觉都很棒!hoho,一定要来发感想哈。呵呵。 以及,要继续加油哦!赶快把字母歌打熟练哈,呵呵。你们肯定都会很棒的哈哈!~ 唔,有热情就是最重要滴,hoho。 事件: 一、准备阶段

SystemVerilog语言简介(doc 26页)

SystemVerilog语言简介(doc 26页)

SystemVerilog语言简介 SystemVerilog是一种硬件描述和验证语言(HDVL),它基于IEEE 1364-2001 Verilog硬件描述语言(HDL),并对其进行了扩展,包括扩充了C语言数据类型、结构、压缩和非压缩数组、接口、断言等等,这些都使得SystemVerilog在一个更高的抽象层次上提高了设计建模的能力。SystemVerilog由Accellera 开发,它主要定位在芯片的实现和验证流程上,并为系统级的设计流程提供了强大的连接能力。下面我们从几个方面对SystemV erilog所作的增强进行简要的介绍,期望能够通过这个介绍使大家对SystemVerilog有一个概括性的了解。 1. 接口(Interface) Verilog模块之间的连接是通过模块端口进行的。为了给组成设计的各个模块定义端口,我们必须对期望的硬件设计有一个详细的认识。不幸的是,在设计的早期,我们很难把握设计的细节。而且,一旦模块的端口定义完成后,我们也很难改变端口的配置。另外,一个设计中的许多模块往往具有相同的端口定义,在Verilog中,我们必须在每个模块中进行相同的定义,这为我们增加了无谓的工作量。 SystemVerilog提供了一个新的、高层抽象的模块连接,这个连接被称为接口(Interface)。接口在关键字interface和e ndinterface之间定义,它独立于模块。接口在模块中就像一个

单一的端口一样使用。在最简单的形式下,一个接口可以认为是一组线网。例如,可以将PCI总线的所有信号绑定在一起组成一个接口。通过使用接口,我们在进行一个设计的时候可以不需要首先建立各个模块间的互连。随着设计的深入,各个设计细节也会变得越来越清晰,而接口内的信号也会很容易地表示出来。当接口发生变化时,这些变化也会在使用该接口的所有模块中反映出来,而无需更改每一个模块。下面是一个接口的使用实例:

北京语言大学各年度录取分数线

https://www.360docs.net/doc/6411535710.html,/schoolhtm/schoolAreaPoint/592/wen/schoolAreaPoint592_shand ong_wen.htm?furl=baiduald 北京语言大学在山东地区文科录取分数线 理科录取分数线 https://www.360docs.net/doc/6411535710.html,/lqsf_l.html 北京语言大学2012年招生计划(暂行)

注:2012年普招计划专业要求考生的外语语种应为英语。 2011年高招志愿填报常见问题 问:你校今年招生总体情况? 答:我校今年招生计划总数为1050人,比去年人数略微增加,所招生学生全部为全日制本科生。

问:你校招不招理科考生? 答:我校信息科学学院三个专业只招理科考生,汉语言文学专业只招文科考生,其余专业文理科考生兼收。 问:报考你校北京小语种的学生高考志愿中是否还需填报? 答:报考我校北京小语种的学生在高考志愿中无需填报我校。北京小语种为零批次录取,若想放弃北京小语种名额,请于6月15日至6月20日携带准考证、身份证来我校招办申请。 问:你校男女生比例有无限制? 答:除部分外语专业实施提前招生时有特殊规定外,北京语言大学统一录取时无男女比例限制。 问:你校对特长生有何优惠条件? 答:我校不单独招收特长生,如考生有特长,同等分数条件下优先录取。 问:你校在录取时是否有专业级差? 答:我校没有专业级差,在分专业录取时,根据各省(自治区、直辖市)的招生计划、专业志愿数、高考模式等具体情况按总分顺序录取,同时综合参考德智体状况,参考相关科目成绩。 问:你校是否预留二志愿名额? 答:我校不预留二志愿名额,在第一志愿生源不足的情况下,我校接收非第一志愿学生。 问:你校是否可修双学位? 答:我校暂不设置双学位,但我校设置对外汉语、英语、金融、计算机等专业的辅修,完成辅修课程并通过考试后颁发辅修证书。 问:你校大学生就业与深造情况怎样? 答:我校毕业生就业的部门主要集中在国家各部委、北京市属部门、机关和各种类型的企业,主要从事外交、外事、外贸、中外文化交流以及其它需要兼具汉语和外语能力的工作。近年来,毕业生考取研究生的比例为20%,出国继续深造的比例为5%左右。

《高级语言程序设计》答案

1. 输入两个整数,要求用两个函数求出其最大公约数和最小公倍数,最大公约数和最小公倍数都在主函数中输出。#include

Systemverilog的一个牛人总结

转一篇Systemverilog的一个牛人总结 (2012-12-12 16:47:06) 转载▼ 标签: 分类:Dreamywork systemverilog 验证 面向对象 杂谈 Systemverilog 数据类型 l 合并数组和非合并数组 1)合并数组: 存储方式是连续的,中间没有闲置空间。 例如,32bit的寄存器,可以看成是4个8bit的数据,或者也可以看成是1个32bit的数据。 表示方法: 数组大小和位,必须在变量名前指定,数组大小必须是【msb:lsb】 Bit[3:0] [7:0] bytes ; 2)二维数组和合并数组识别: 合并数组: bit [3:0] [7:0] arrys; 大小在变量名前面放得,且降序 二维数组: int arrays[0:7] [0:3] ; 大小在变量名后面放得,可降序可升序 位宽在变量名前面,用于识别合并和非合并数组,位宽在后面,用于识别数组中元素个数。 3)非合并数组 一般仿真器存放数组元素时使用32bit的字边界,byte、shortint、int都放在一个字中。 非合并数组:字的地位存放变量,高位不用。 表示方法: Bit [7:0] bytes; 4)合并数组和非合并数组的选择 (1)当需要以字节或字为单位对存储单元操作。 (2)当需要等待数组中变化的,则必须使用合并数组。例如测试平台需要通过存储器数据的变化来唤醒,需要用到@,@只能用于标量或者合并数组。

Bit[3:0] [7:0] barray[3] ; 表示合并数组,合并数组中有3个元素,每个元素时8bit,4个元素可以组成合并数组 可以使用barry[0]作敏感信号。 l 动态数组 随机事物不确定大小。 使用方法:数组在开始是空的,同时使用new[]来分配空间,在new[n]指定元素的个数。 Int dyn[]; Dyn = new[5]; //分配5个元素空间 Dyn.delete() ; //释放空间 l 队列 在队列中增加或删除元素比较方便。 l 关联数组 当你需要建立一个超大容量的数组。关联数组,存放稀疏矩阵中的值。 表示方法: 采用在方括号中放置数据类型的形式声明: Bit[63:0] assoc[bit[63:0]]; l 常量: 1)Verilog 推荐使用文本宏。 好处:全局作用范围,且可以用于位段或类型定义 缺点:当需要局部常量时,可能引起冲突。 2)Parameter 作用范围仅限于单个module 3)Systemverilog: 参数可以在多个模块里共同使用,可以用typedef 代替单调乏味的宏。 过程语句 l 可以在for循环中定义变量,作用范围仅在循环内部 for(int i=0;i<10;i++) array[i] =i; l 任务、函数及void函数 1)区别:

北京语言大学日语专业考研介绍2018

北鼎教育,专注北外考研及全国外语专业考研辅导! 北京语言大学日语专业考研介绍 一、专业简介 北京语言大学日语专业为教育部国家级特色专业建设点。本专业成立于1979年,现有13名教师,其中教授3名,副教授8名,讲师2名。2003年,北京语言大学专业首家开设中日同声传译方向硕士课程,在全国有着广泛的影响力。 二、招生情况、考试科目以及参考书目 注:北京语言大学日语语言文学专业初试不提供参考书目 日语语言文学专业复试: 综合考试所涉及的课程为:日语语言学、日语教学、日本文学、日本文化基础知识、日语基础。 三、报考条件 (1)国家承认学历的应届本科毕业生(录取当年9月1日前须取得国家承认的本科毕业证书。含普通高校、成人高校、普通高校举办的成人高等学历教育应届本科毕业生,及自学考试和网络教育届时可毕业本科生)。 (2)具有国家承认的大学本科毕业学历的人员。 (3)获得国家承认的高职高专毕业学历后满2年(从毕业后到录取当年9月1日)或2年以上,达到与大学本科毕业生同等学力,同时还需提供到普通高校进修本科课程10门以上的成绩单(教务处盖章有效),须在公开刊物上发表一篇以上(包括一篇)与所报考专业相关的学术论文(署名前2位);复试时加试两门所报专业大学本科主干课程。 (4)国家承认学历的本科结业生,按本科毕业生同等学力身份报考。 (5)已获硕士、博士学位的人员。 四、分数线 2017年的复试分数线为:53/80/345专业名称/代码 方向招生人数考试科目日语语言文学05020501 日语语言学02 日本文学03 日本文化04日本教育6 101思想政治理论241二外英语730基础日语832日本语言文化

system verilog 类的继承

类的继承 SystemVerilog支持单继承(类似Java,而不像C++). 有一个让SystemVerilog支持多重继承的提案[1], 但是短期内不会看到曙光。 目录 ? 1 什么是继承? ? 2 有什么好处 ? 3 开-关定律 ? 4 参考资料 什么是继承? 继承是面向对象编程范式的关键概念。类用来创建用户自定义类型. 继承使得用户可以用非常安全,非侵入的方式对类的行为进行增加或者修改。 使用继承可以定义子类型,在子类型中增加新的方法和数据。被继承的类一般称为基类(SystemVerilog中的超类),得到的新类一般称为引申类(或子类)。 为什么继承如此重要? 因为它使得复用得以实现。让我们通过实例来说明. 假设我们对一个图像模块进行建模. 对其中一部分,我们写了一个代表颜色的类: class Color; byte unsigned red; byte unsigned green; byte unsigned blue; function new(byte unsigned red_=255, byte unsigned green_=255, byte unsigned blue_=255); red=red_; green=green_; blue=blue_; endfunction:new function mix(Color other); function brighter(float percent); task draw_pixel(int x,int y);

Now现在它的下一个版本希望能够处理部分透明的图像。为此,我们给Color类增加了一个alpha成员,。alpha代表图像的透明度。alpha越大,图像的像素越结实(不透明)。'0'代表完全透明,使得图片的背景全部可见。因此,我们修改color类如下: class Color; byte unsigned red; byte unsigned green; byte unsigned blue; byte unsigned alpha; function new(byte unsigned red_=255, byte unsigned green_=255, byte unsigned blue_=255, byte unsigned alpha_=255); red=red_; green=green_; blue=blue_; alpha=alpha_; endfunction:new function mix(Color other);// new implementation -- would depend on // alpha values for both the colors function brighter(float percent);// original implementation good enough task draw_pixel(int x,int y);// new implementation // Other functions ... endclass:Color 注意,即使许多代码是由之前版本的Color类复制而来,我们还是需要单独维护两个版本的代码。这时继承就可以发挥作用,使用继承,我们可以简单的从原始的Color类继承出新类,来添加alpha成员。 class ColorWithAlpha extends Color; byte unsigned alpha; function new(byte unsigned red_=255, byte unsigned green_=255, byte unsigned blue_=255, byte unsigned alpha_=255);

2015北京语言大学语言习得与语言病理学考博分析

2015北京语言大学语言习得与语言病理学考博分 析 一、招考介绍 2014 语言学及应用语言学 二、联系导师 在初步定好考博学校之后,就要和所报考院校中意的老师取得联系,询问是否有招生名额,能否报考,这是我们考博成功的关键第一步。 大多数考生会在九月中下旬与导师取得联系。因为太早,学校里面直博名额什么的还没有确定,报考的导师也不清楚是否有名额;太晚的话,怕别的学生比你早联系就不好了。一般情况下,导师对一个学生很中意的话,后来联系的学生,导师一般也不会答应其报考了。在此说点题外话,联系导师的过程中,如果读研期间的导师有关系,可以尽量利用。如果没有,也没关系,凭着自己的本事也是可以和考博导师很好的沟通的,这就要看自己了。 通常跟导师初次联系,都是发邮件。导师回复邮件的情况一般有几种: (1)、欢迎报考。这种答复最笼统,说明不了问题。我们可以接着努力和老师多沟通,看看具体的进展,避免出现初试之后却没有名额的情况。 (2)、名额有限,可以报考,但有竞争。很多人说这样的回复不满意,认为希望很小一般会被刷。其实这样还是比较好的一种回答,最起码导师没有骗你而且给你机会去证明自己,考的好就可以上。 (3)、你的研究方向和我一样......各种一大堆他的研究方向和你相关,欢迎报考什么的话。不可否认,这是最好的情况,你可以放心的去考,一般不会出问题的。但不排除偶然,像出现直博和本学校的硕转博名额问题,可能会给我们的报考和录取产生影响。 总之考博凭的是实力和自身的本事,关系只是占一部分,自己努力了就行,不用过分纠结于导师回复有没有啥隐含意思的。 初次联系好导师后,一定要注意跟导师保持联系。每半个月或者一个月向导师汇报一下学习情况或者复习情况,交流一下科研方向,这很有必要。一方面让导师觉得你很想去跟他深造,另一方面显得你虔诚好学。10语言习得与语言病理学高立群①1011英语②2022语言学理论 ③3048儿童语言习得

system_verilog教程

基于断言的验证技术 SystemVerilog Tutorials 下面的手册会帮助你了解一些SystemVerilog中最重要的新特点。手册还提供了一些代码样本和例子使你可以对语言有更好"感觉"。这些辅导假设你们已经了解了一些Verilog语言。如果没有,你可以先去看看Verilog设计者指南(V erilog Designer’s Guide)。 * Data types * RTL design * Interfaces * Clocking * Assertion-based verification * Classes * Testbench automation and constraints * The Direct Programming Interface (DPI) SystemVerilog 的数据类型 这个手册将描述Systemverilog新引进的数据类型。他们大多数都是可以综合的,并且可以使RTL级描述更易于理解和书写。 整型和实型 SystemVerilog引进了几种新的数据类型。C语言程序员会熟悉其中的大多数。引进新的数据类型构思是这样的,如果C语言和SystemVerilog有相同的数据类型可以使C语言算法模型更容易的转化为SystemVerilog模型。 Verilog的变量类型有四态:既是0,1,X,Z。SystemVerilog引进了新的两态数据类型,每一位只可以是0或是1。当你不需要使用的X和Z值时,譬如在写Testbench和做为for语句的循环变量。使用两态变量的RTL级模型,可以使模拟器更有效率。并且使用得当的话将不会对综合结果产生影响。 二态整型 类型描述例子 Bit user-defined size bit [3:0] a_nibble;

北京语言大学翻译硕士各细分专业介绍

北京语言大学翻译硕士各细分专业介绍 翻译硕士专业学位研究生,即MTI(Master of Translation and Interpreting)是为了适应市场经济对应用型高层次专门人才的需求,国务院学位委员会于2007年1月批准设置的一种专业学位。2008年开始招生,2009年面向应届本科毕业生招生。 MTI教育重视实践环节,强调翻译实践能力的培养。翻译硕士专业学位的培养目标为具有专业口笔译能力的高级翻译人才。翻译硕士专业学位获得者应具有较强的语言运用能力、熟练地翻译技能和宽广的知识面,能够胜任不同专业领域所需的高级翻译工作。 全日制MTI招生对象为具有国民教育序列大学本科学历(或本科同等学力)人员,具有良好的双语基础。作为我国专业硕士之一,MTI不仅面向英语专业的考生,同时也鼓励非外语专业毕业生及有口笔译时间经验者报考,其中非外语专业的毕业生更受到报考院校的欢迎。 北语翻译硕士全日制学费总额为18000,学制为两年。 北语翻译硕士的培养目标是培养适应中国政治、经济、文化、体育、建筑等领域所需要的高层次、高素质、高技能的应用型口笔译人才。 专业方向 ①英语笔译、英语口译 考试科目为: 1.思想政治理论 2.翻译硕士英语 3.英语翻译基础 4.汉语写作与百科知识 ②日语笔译、日语口译 考试科目为: 1.思想政治理论 2.翻译硕士日语 3.日语翻译基础 4.汉语写作与百科知识 ③法语笔译、法语口译 考试科目为: 1.思想政治理论 2.翻译硕士法语 3.法语翻译基础 4.汉语写作与百科知识 ④朝鲜语笔译、朝鲜语口译 考试科目为: 1.思想政治理论 2.翻译硕士朝鲜语 3.朝鲜语翻译基础 4.汉语写作与百科知识

systemverilog面试

Qi1)What is callback (Qi2)What is factory pattern (Qi3)Explain the difference between data types logic and reg and wire . (Qi4)What is the need of clocking blocks (Qi5)What are the ways to avoid race condition between testbench and RTL using SystemVerilog (Qi6)Explain Event regions in SV. (Qi7)What are the types of coverages available in SV (Qi8)What is OOPS (Qi9)What is inheritance and polymorphism (Qi10)What is the need of virtual interfaces (Qi11)Explain about the virtual task and methods . (Qi12)What is the use of the abstract class (Qi13)What is the difference between mailbox and queue

(Qi14)What data structure you used to build scoreboard (Qi15)What are the advantages of linkedlist over the queue (Qi16)How parallel case and full cases problems are avoided in SV (Qi17)What is the difference between pure function and cordinary function (Qi18)What is the difference between $random and $urandom (Qi19)What is scope randomization (Qi20)List the predefined randomization methods. (Qi21)What is the dfference between always_combo and always@(*)c (Qi22)What is the use of packagess (Qi23)What is the use of $cast (Qi24)How to call the task which is defined in parent object into derived class (Qi25)What is the difference between rand and randc (Qi26)What is $root (Qi27)What is $unit

SystemVerilog 中的随机化激励

SystemVerilog中的随机化激励 神州龙芯集成电路设计公司 杨鑫 徐伟俊 陈先勇 夏宇闻 [摘要]:随着集成电路的验证工作日渐复杂,对验证的可靠性提出了越来越高的要求。传统的验证工作中也使用随机化激励以便减轻测试代码编写的工作量,以提升验证的可靠性。在SystemVerilog更强调了利用随机化激励函数以提高验证代码的效率和验证可靠性的重要性。本文以VMM库为例,阐述了如何在SystemVerilog中使用随机化函数来编写高效率的测试代码,重点介绍了可重用验证函数库的使用方法,以帮助读者理解如何使用SystemVerilog高效率地完成复杂的设计验证。 关键字:VMM SystemVerilog 激励随机化 1. 前言 随着电路工艺设计技术的不断发展,集成电路的逻辑设计变得越来越复杂,随之对验证工作提出了更高的要求。由于投片(tip-out)的费用较高,很有必要在投片前对芯片设计进行全面、可信的验证,以尽量减少“设计——测试——投片——调试——发现Bug修改设计”这一流程的迭代次数。因此在集成电路芯片的设计中,尤其是复杂逻辑设计中,对测试工作的效率和可靠性提出了更高的要求。 在传统的验证方法中,也有将激励随机化的方法,这样可以用较少的测试代码生成较多、较全面的测试激励。这些方法减少了人为因素的干扰,能有效地提高验证的工作效率和可靠性。 在SystemVerilog中,强调在验证中使用可重用的验证IP,包括如何生成随机化激励。对于如何尽可能地使用已有的验证IP,以及编写符合标准的可重用验证组件,SystemVerilog提供了一整套的工作机制,这使得符合规范的随机化激励组件能够很好地在多个设计间复用,这更进一步地提高了验证工作的效率和可靠性。 2. 在验证中使用随机化激励 在验证中,可以依照DUT(Design Under Test,被测设计,以下简称DUT)的验证要求来设计定向的激励,并对照DUT的预期响应,用人工的方法来判断设计是否正确。但也可以使用随机化激励来驱动DUT,并使用特定的机制来完成响应的自检测。 利用随机化来产生激励可以看作一种近似的自动化激励产生,因为随机化足够长的时间后,所生成的激励可以覆盖绝大部分的待验证特性。但是纯粹的随机化激励效率并不高,因为其中正确的,或是有意义的激励只占很少一部分。必须使用一定的约束条件限制随机化的范围,从而产生大量随机而有意义的激励。