intel8259a可编程中断控制器

intel8259a可编程中断控制器

●8086,8088兼容

●MCS-80,MCS-85兼容●8位优先级控制

●可扩展至64级

●可编辑中断模式●独立中断请求屏蔽功能●单电源+5v,无时钟

●28脚DIP或PLCC封装●高速-标准温度范围

-扩展温度范围

intel8259a可编程中断控制器可以为CPU处理8位优先级中断,而且,无须额外电路即可级联扩展至64位优先级中断处理。28脚DIP封装,使用NMOS技术,电路是静态的,无须时钟信号输入。

8259a被设计用来减少软件和实时处理的多级优先级中断。它有多种模式,满足系统的多种需要的最佳化。

8259a全面向上兼容intel8259。原先为8259所写的软件,可以使用8259a代替(MCS-80.85,无缓冲边沿触发)

。

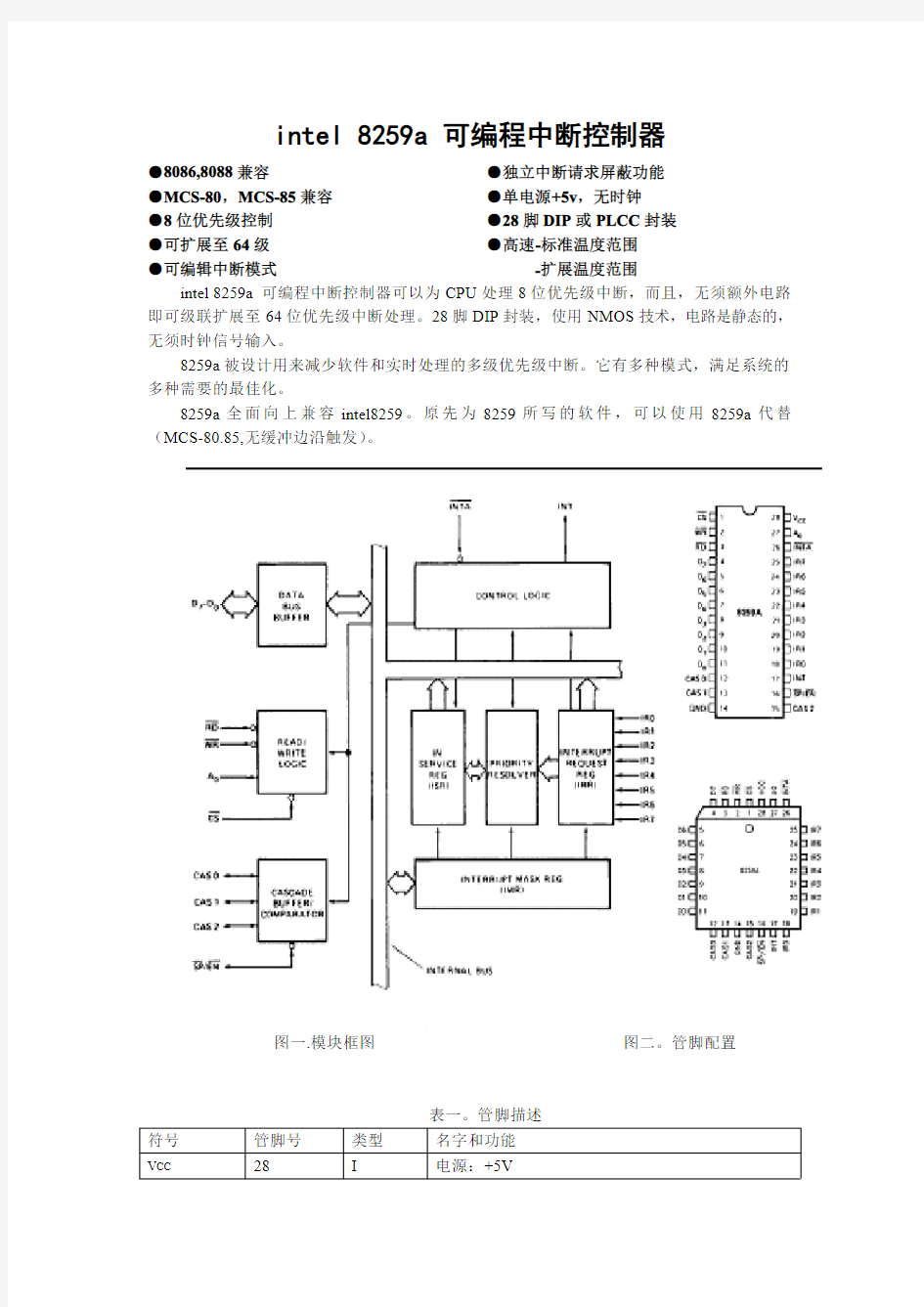

图一.模块框图图二。管脚配置

表一。管脚描述

符号管脚号类型名字和功能

V CC28I电源:+5V

GND14I地

CS1I芯片使能:低电压时,允许CPU与8259a之间/RD、

/WR的通信。但INTA功能与它独立

WR2I写:低电压且CS亦为低电压时,8259a接受来自

CPU的命令字

RD3I读:它与CS皆为低电压时,允许8259a将状态通

过数据总线发到CPU

D7-D04-11I/O双向数据总线:控制,状态和中断向量信息通过此

传输

CAS0-CAS212,13,15I/O级联线:CAS线组成8259a的私有总线以控制多

8259a架构。对主片为输出,对从片为输入

SP/EN16I/O从编程/缓冲器允许信号:这是一个双功能管脚。当

缓冲模式时,它可作为输出到缓冲接收器(EN)。

当非缓冲模式,作为输入以指定是否是主/从片

(SP=1时主片)

INT17O中断:当一个有效的中断请求判定出时,该管脚变

为高电平;用于给cpu中断

IR0-IR718-25I中断请求:异步输入。当如下情况时,被判定为中

断请求:出现上升沿电压且保持高电压直至被识别

(边沿触发模式),或者高电平触发。

INTA26I中断响应:用于允许8259a中断向量数据传输到数

据总线,由其定序。

A027I A0地址线:与/CS,/WR,/RD配合使用。用于解析来

自cpu的不同信息和cpu想要读出的状态。一般与

a0线相接(8086时A1)

功能说明书

微机系统上的中断

微机系统设计需要I/O设备,诸如键盘,显示器,传感器,和其他部件,并且以一种有效的方式接受I/O设备的服务,这样在整个过程中,微机才可以承担大量的系统任务而无所影响。

最常用的使用这些设备的方法是检测法。此即处理器必需以一定次序检测每一个设备,并且询问它需要服务的每一个设备。显而易见,主程序的很大一部分被这些持续的检测循环所占据,而且这种方法对系统有着严重的影响,限制了微机能够成带的任务,减少了使用这些设备的性价比。

一个更好的方法是,能够允许微处理器执行主程序并且只有当周边设备请求时才停下来去处理(周边设备的请求)。确实,这种方法将提供一个外部的异步输入,以通知处理器结束当前正被执行的指令,取得服务请求设备的子程序。一旦这个服务结束,处理器将重新继续放下的任务。

这种方法叫做中断。显然,系统效能大大增加,这样处理器可以承担更多的任务,进一步的提高其性价比。

可编程中断控制器(PIC)功能上是中断驱动系统环境下的总管家,决定那一个输入优先级最高,确定输入请求是否拥有比当前服务级别更高的优先级,并且将决定出的中断通知

cpu。

每一个周边设备或者架构通常都有一个与其特殊功能或工作要求相关联的程序,他被称为服务程序。PIC给CPU中断后,必须输入给CPU信息,以指出程序响应与请求设备相关的服务程序。这个指针是一个位表地址,并会被经常访问。

8259a

8259a是一个专门用在实时中断驱动的微机系统。它管理8级优先级或中断请求并可与其他8259a芯片级联(可达64级)。它被系统软件当做周边I/O设备来操作。编程者可以选择8259a的工作方式,以满足系统需要。优先级模式可以在主程序之间随时更改。这意味着整个中断结构可以根据系统需要而定义。

中断请求寄存器(IRR)和中断服务寄存器(ISR)

输入的中断由两个级联的寄存器IRR、ISR处理。IRR用来储存所有请求的中断,ISR 用来储存所有正在服务的中断请求。

优先权裁决器(PR)

该逻辑模块决定IRR各位的优先级。最高优先级的中断请求被选取并在/INTA脉冲期间映射到ISR的相应位。

中断屏蔽寄存器(IMR)

IMR储存需要屏蔽的位。IMR操作IRR。屏蔽高优先级输入并不影响低优先级

INT:它直接输出到CPU中断输入端。Voh完全兼容8080a,8085a和8086输入电平。/INTA(中断响应)

/INTA脉冲将引起8259a向数据总线释放位信息。数据格式取决于8259a的系统模式(uPM)

数据总线缓冲器这是一个三态双向8位缓冲器,是8259a与系统数据总线之间的接口。

控制字和状态信息通过它来传输。

读写控制逻辑

本模块的功能是接受CPU的输出命令。它包括初始化命令字(ICW)寄存器和操作命令字(OCW)寄存器,储存着多种设备操作的控制格式。该功能模块也可以允许将8259a 的状态传送到数据总线。

/CS

低电压有效。否则,不允许读写芯片操作。

/WR

低电压有效,允许向8259a写入ICWs AND OCWs

/RD

低电压有效,发送IRR ISR IMR或者中断号到数据总线。

A0

这个输入信号与/WR/RD信号关联,以写入命令给不同的命令寄存器、以及读取不同状态寄存器,可以直接与地址总线的某根相连。

级联缓冲器/比较器

该功能模块存储和比较系统中所有8259a的ID。相关的三根I/O管脚(CAS0-2),当8259a 是主片时,作为输出;当8259a是从片时,作为输入。作为主片时,8249a发送请求中断的从片ID到CAS0-2上。这样选中的从片,将在下一个或两个连续的/INTA脉冲中,发送预先编辑好的子程序的地址到数据总线上(详见“8259a的级联”部分)。

中断流程

在微机系统中,8259a最强大的的特征是可编程性和中断程序地址功能。后者允许直接或间接跳转到相应中断服务程序,而无须检测设备。中断事件的一般流程取决与所用CPU 的类型。

当为MCS-80/85系统时:

1.有一个或多个中断请求,IRR相应位置位

2.8259a处理这些请求,并向CPU发送中断请求INT。

3.CPU识别INT信号,并发出响应脉冲/INTA。

4.根据来自CPU的/INTA信号,置位最高优先级的ISR位,并将相应的IRR位复位。8259a也会通过D7-0向8位数据总线释放一个CALL指令代码(11001101)

5.这个CALL指令将会引起使cpu向8259发送另外两个/INTA脉冲。

6.这两个/INTA脉冲允许8259a释放它的预编辑程序地址到数据总线上。低八位地址在第一个/INTA脉冲发送,高八位地址在第二个/INTA脉冲发送。

7.这个由8259a释放3字节CALL指令完成。在自动中断结束模式(AEOI)时,在第三个/INTA脉冲的末尾,ISR位复位;否则,ISR位将保持“1”直到终端流程最后处理相应EOI命令。

在8086系统中,在第四步之前,终端流程是一样的。

4.根据来自CPU的/INTA信号,最高优先级的ISR位置位,并且相应的IRR位复位。在此脉冲期间内,8259a并不驱动数据总线。

5.8086发送第二个/INTA脉冲。在此期间,8259a向数据总线释放一个供CPU读取的八位指针。

6这样就结束了中断周期。AEOI模式时,在第二个/INTA脉冲结束时,ISR位复位。否则,ISR位将保持“1”直到在程序结尾相应的EOI命令被处理。

如果到第四步时没有中断请求(换言之,中断请求持续时间太短),8259a将处理中断级别7.向量字节和CAS线将看起来像是中断输入端7请求中断。

当8259a PIC接收到中断信号时,INT管脚激活并且开始响应周期。如果一个更高优先级的中断在这两个/INTA周期内发生,INT管脚在第二个/IINTA脉冲后立即失效(变为低电平)。再过一段不定时间后,INT管脚重新激活以识别等待服务的更高级别的中断请求。沉寂时间(inactive time)不是固定的,且在一个区间内变动。设计人员在使用8259a时,应当考虑这点。鉴于此,我们推荐设计相应的异步技术。

中断流程输出

MCS-80,MCS-85

该序列由三个/INTA脉冲定时。在第一个/INTA脉冲时,CALL代码被放到数据总线上。

表2.第一个中断向量内容

在第二个/INTA脉冲时,相应服务程序的低位地址放到数据总线上。当interval=4位时,A5-A7是可编辑的,A0-A4是由8259a自动插入。当interval=8,只有A6和A7可编辑,A0-A5自动插入。

表3.第二个中断向量内容

IR Interval=4Interval=8

D7D6D5D4D3D2D1D0D7D6D5D4D3D2D1D0 7A7A6A511100A7A6111000 6A7A6A511000A7A6110000 5A7A6A510100A7A6101000 4A7A6A510000A7A6100000 3A7A6A501100A7A6011000 2A7A6A501000A7A6010000 1A7A6A500100A7A6001000 0A7A6A500000A7A6000000

在/INTA脉冲期间,预先编辑好的子程序的高位地址,作为初始化次流程的字节2(A8-A15),被释放到总线上。中断向量的第三个字节内容如下表示:

D7D6D5D4D3D2D1D0

A15A14A13A12A11A10A9A8

8086,8088

8086模式与MCS-80模式相似,除了只有两个由处理器完成的中断响应周期,并且没有CALL操作码被送到处理器。第一个中断响应周期与mcs-80,85系统相似,都是在内部冻结中断状态以等待优先级处理。作为主片,8259处理在此脉冲结束时,处理级联线上的中断编码。在第一个周期,他不处理任何数据给处理器,且此时的数据总线缓冲器是禁用的。在8086模式下的第二个中断响应周期,主片(或设定的从片)将发送给处理器一个字节大小的中断号,它的编码如下图(注意ADI模式控制被忽略,8086模式下A5-A11不用)D7D6D5D4D3D2D1D0

IR7T7T6T5T4T3111

IR6T7T6T5T4T3110

IR5T7T6T5T4T3101

IR4T7T6T5T4T3100

IR3T7T6T5T4T3011

IR2T7T6T5T4T3010

IR1T7T6T5T4T3001

IR0T7T6T5T4T3000

8259A状态编辑

8259A接受来自CPU的两类命令字:

1.初始化命令字(ICW):在正常操作之前,系统使用的每一片8259a都必须初始化,通过2-4个字节的ICW,此由/WR脉冲控制。

2.操作命令字(OCW):这些命令字控制8259a工作于不同的中断模式。这些模式有:

a。全嵌套模式

b。循环优先模式

c。特殊屏蔽方式

d。程序查询模式

OCW命令字可以在初始化后的任何时间写入8259a

初始化命令字(ICW)

概述

无论何时,当A0=0且D4=1时,这个命令字将被认为是ICW1。ICW1开始初始化流程,以下步骤将自动发生:

a。边缘感应电路(the edge sense circuit)被复位,这意味着:中断输入(IR)必须为上升沿才能触发(即边缘触发模式)

b。中断屏蔽寄存器被清空(全置0)

c。IR7输入被置为优先级7(lowest)

d。从片模式地址被设为7

e。特殊屏蔽方式被清空,状态读取(Status Read)指向IRR

f。若IC4=0,那么ICW4全被置0(这意味着:非缓冲模式,非自动中断结束模式,mcs-80/85系统)

注意:ICW4中的主从模式仅用于缓冲模式。

ICW1,ICW2

A5-A15:服务程序页开始地址。在MCS80/85系统中,8个请求级别将产生Call指令对应8个等距分布在内存中的位置。可以编程设置内存间距是4或者8,这样8个程序将产生32/64字节的页。

地址格式长2字节(A0-A15)。当成需间隔为4时,A0-A4将被8259a自动分配,而A5-A15可被外部编辑;当interval=8时,A0-A5被8259a自动插入,而A6-A15可被外部编辑。

8字节interval将会与当前软件完美配合;4字节interval适合于紧凑跳转表。

在8086系统中,A15-A11被插入5个重要的位,8259a根据中断级别自动设置剩下的3位,A10-A5被忽略,ADI(地址间距)无效。

LTIM:如果LTIM=1,那么,8259a将工作于电平触发模式,边沿触发模块被禁用。

ADI:CALL指令地址间隔。1时4,0时8.

SNGL:信号,即是否为单片8259a。1时不处理ICW3。

IC4:1时读取ICW4.

ICW3

这个控制字只有在多片8259a级联时使用,此时SNGL=0。它将装载8位从寄存器,这

个寄存器多功能如下:

a。主片时(或者SP=1,或者在缓冲模式时ICW4的M/S=1),每一个从片都设为相应的“1”。主片然后发出一个字节大小的Call序列(MCS-80/85系统时),并且通过级联线(cascade line)使能相应从片发送第2、3个字节(8086时仅为第二个字节)。

b。从片(或者当SP=0,或者ICW4的BUF=1且M/S=0),位2-0为从片识别码(id)。从片标胶他的级联输入与这些位,如相等,Call序列的第2、3字节(8086仅第二个字节)将被发送到数据总线。

ICW4

SFNM:如果SFNM=1,将设为特殊全

嵌套模式

BUF:若BUF=1,将设为缓冲模式。在

缓冲模式时,SP/EN使能为输出并且主从片

由M/S决定

M/S:若为缓冲模式,M/S=1意味着

8259a被定为主片,反之为从片。若BUF=0,

则M/S无效。

AEOI:若AEOI=1,将设为自动结束中

断模式。

mPM:微处理器模式,若mPM=0则设

为MCS-80,85系统环境。若mPM=1,则设

为8086系统环境。

初始化命令字格式

ICW1

A0D7D6D6D4D3D2D1D0

0A7A6A51LTIM ADI SNGL IC4中断向量地址

A7-A5(仅用于

MCS-80/85)

1:电平触发

0:边沿触发

地址调用间隔

1:4间隔

0:8间隔

1:单片模式

0:级联模式

1:需要

ICW4

0不需要

ICW2

A0D7D6D6D4D3D2D1D0 1A15/T7A14/T6A13/T5A12/T4A11/T3A10A9A8

中断向量地址的A15-A8(MCS-80/85)

中断向量地址T7-T3

ICW3(主片)

A0D7D6D5D4D3D2D1D0 11:IR输入有从片

0:IR输入无从片

ICW3(从片)

A0D7D6D5D4D3D2D1D0 100000ID2ID1ID0

从片地址

ICW4

A0D7D6D5D4D3D2D1D0 1000SFNM BUF M/S AEOI mPM

1:特殊全嵌套模式0:全嵌套模式

0X:无缓冲模式

10:缓冲模式/从片

11:缓冲模式/主片

1:自动

EOI

0:一般

EOI

1:8086/8088

模式

0:MCS-80/85

模式

注意:从片ID等于相应主片上的IR输入。

操作命令字(OCWS)

初始化命令字被写入8259a后,芯片已经准备好接收中断请求。但是,在8259a工作期间,一个算法的选择(a select6ino of algorithms)可通过OCW命令8259a工作在多种模式。

操作命令字格式

OCW1

A0D7D6D5D4D3D2D1D0

1M7M6M5M4M3M2M1M0

1:中断屏蔽;0:屏蔽复位

OCW2

0R(rotate)SL EOI00L2L1L0

001一般中断结束方式中断结束

方式011特殊终端结束方式

101循环一般中断结束方式自动循环

方式100设置为循环自动中断结束方式

000清除循环自动中断结束方式(为

固定优先级)

111*循环特殊中断结束方式特殊循环

方式110*设置优先级命令

010无操作待操作的中断级别的二进制代码:

L2,L1,L0

注意:带*的表明试用

了L2-L0.

OCW3

00ESMM SMM01P RR RIS

10:一般屏蔽方式11:特殊屏蔽方式00:无操作

01:无操作1:程序查询方式

0:中断方式

10:在下一个RD脉冲读IRR

11:在下一个RD脉冲读ISR

00:无操作

01:无操作

OCW1

ocw1设定或清除中断屏蔽寄存器(IMR)的屏蔽位。M7-M0代表八个屏蔽位。若M=1则该输入端被屏蔽;若M=0则该输入端使能。

OCW2

R,SL,EOI-这三位控制着循环、结束中断模式以及两者结合模式。这三者的组合见上表。

L2,L1,L0-当SL为激活,这些位决定中断级别。

OCW3

ESMM-使能特殊中断屏蔽模式。若设为1,将使能SMM位设置或重设特殊中断屏蔽模式。若为0,SMM位忽略。

SMM-特殊中断屏蔽模式。若ESMM=1且SMM=1,8259a将进入特殊中断屏蔽模式,若ESMM=1且SM=0,8259a将回到普通中断屏蔽模式。当ESMM=0,SMM位无效。

全嵌套模式

初始化后若不另外设定模式,将自动进入此模式。中断请求按优先权从0到7排序(0最高)。当(CPU)中断响应时,裁决出(PR)最高优先级的中断请求,并将它的向量信息传到数据总线。另外,ISR(ISO-7)中的相应位被置位。此位保持为‘1’直到微处理器处理EOI命令(在从服务程序返回前),或者到最后一个INTA的后沿(trailing edge)(如果AEOI=1的话)。当IS位置位,以后所有同级别或低级别的中断将被禁止,而较高级别的中断将产生中断(只有当微处理器的内部中断使能端被软件设为使能时,才会响应)。

初始化之后,IR0优先级最高,IR7优先级最低。优先级可以被改变,这将在循环优先模式中说明。

中断结束(EOI)

在以下情况,IS(in service)将会被复位(置0):

1.在最后一个INTA脉冲的后沿(trailing edge)自动完成(ICW1的AEOI位置1)

2.中断服务程序结束前由8259a处理的命令字,EOI命令。

当级联模式时,必须有两个EOI命令,主从片各一次。

有两类EOI:特殊的和一般的。当工作在全嵌套系列模式时,8259a可以决定执行EOI 时,哪位IS位被复位。当为非特殊EOI命令时,8259A将自动复位ISR中已置位的最高优先级位,因为在全嵌套模式中,最高的IS级别一定是最近响应且服务的。一般中断结束方式可通过OCW2(EOI=1,SL=0,R=0)设置.

当非全嵌套模式时,8259a可能不能确定最近响应的中断级别。这种情况下,即需要--特殊中断结束命令,它包括要复位的IS级别。特殊EOI可通过OCW2(EOI=1,SL=1,R=0,且L0-L2是需要复位的二进制代码)设置。

这里需要注意,如果8259a工作在特殊屏蔽模式,由IMR位屏蔽的IS位将不会被非特殊EOI命令清除,。

自动中断结束模式(AEOI)

若ICW4的AEOI=1,那么,8259a将工作在AEOI模式直至由ICW4复位。此模式下,8259a在最后一个中断响应脉冲的后沿,将自动执行非特殊EOI命令(MCS-80/85时第三个,8086时第二个)。注意,从系统观点来看,此模式只适合于多片8259a嵌套中断架构。(Note that from

a system standpoint,this mode should be used only when a nested multilevel interrupt structure is not required within a single8259A)

AEOI模式只能用于主片。但1985年及以后的版本可以工作在AEOI模式,无论是主片还是从片。

Automatic Rotation优先级自动循环模式(等优先级设备)

在一些应用中,存在一些等优先级的设备,它们在被服务后,优先级降为最低,因此,在最糟的情况下,一个需要中断请求的设备等待直到其他七个设备至多服务一次。

有两种方法实现优先级自动循环模式,通过OCW2,有非特殊EOI命令(R=1,SL=0,EOI=1);和通过AEOI模式循环,由(R=1,SL=0.EOI=0)设置,由(R=0,SL=0,EOI=0)清除。

优先权特殊循环方式(Specific Rotation(Specific Priority))

编程者可以改变优先级通过编辑最低优先级,这样解决其它的优先级。例如,若IR5被设为最低优先级,那么IR6将是最高优先级。

设定优先级命令由OCW2处理:R=1,SL=1,EOI=0,L0-L2是最低优先级设备的二进制代码。

注意,此时的内部状态已被操作OCW2过程中又软件控制更新。但是,他独立与EOI 命令(同样由OCW2执行)。改变优先级通过EOI命令,通过使用循环或者特殊EOI命令in OCW2(R=1,SL=1,EOI=1,L0-L2=将要接受的最低优先级级别)。

中断屏蔽

每一个中断输入均可通过中断屏蔽寄存器(IMR)单独被屏蔽(操作OCW1).IMR的置1的每一位屏蔽响应中断输入。位0屏蔽IR0,位1屏蔽IR1,依此类推。屏蔽一位不影响其他。

特殊屏蔽模式

一些应用在软件操作过程中可能需要中断服务程序动态的改变中断优先结构。例如,程序可能有时希望禁用低优先级请求,有时又希望允许低优先级别请求。

这儿的困难是,若一个中断请求被响应而且EOI命令还未复位其IS位(换句话说,其正在被服务),8259A已经禁止了所有低优先级请求,如此就不容易让程序允许他们(指低优先级别请求)。

这就是为什么引进特殊屏蔽模式。在此模式中,当屏蔽位被OCW1置位,他禁用以后的同级别中断,但允许所有其他级别未被屏蔽的请求(低或者高均可)。

这样,通过IMR,任何请求均可被选择性允许.

特殊屏蔽模式由OCW3控制:SSMM=1,SMM=1,当SSMM=1,SMM=0是清除。

程序查询模式(poll mode)

在程序查询模式,INT输出功能不变,但微处理器可以忽略它。这可以这样完成:或者INT端不予微处理器连接,或者通过禁用微处理器中断功能。对设备的服务由查询命令完成。

查询命令由OCW3控制(P=1)。8259A把第二个RD信号(即RD=0,CS=0)作为中断响应,若有请求将相应IS位置位,读优先级。当由WR到RD时,中断冻结。

在读信号期间,以下字当被放到数据总线上:

D7D6D5D4D3D2D1D0

I-----W2W1W0

W2-W0:请求服务的最高优先级的二进制代码

若I=1,则说明有中断

当程序有多处相同时,该模式很有用(This mode is useful if there is a routine command common to several levels so that the INTA sequence is not needed(saves ROM space).)。另一个应用是扩展中断优先级当中断源多于64个时。

读8259a状态

一些内部寄存器的输入状态可以被读取以更新系统上的用户信息。

以下寄存器可被读取,通过OCW3(IRR和ISR,或OCW1[IMR]。

IRR:8位寄存器,包含待响应的中断请求级别。当中断被识别时,最高优先级将被复位。(不受IMR影响)

ISR:8位寄存器,包含正在被服务的优先级别。当EOI命令被处理时,ISR更新。

IMR:8位寄存器,包含被屏蔽的中断请求。

当OCW3的读寄存器命令处理时(RR=1,RIS=0)(RD脉冲之前),可以读取IRR。

当OCW3的读寄存器命令处理时(RR=1,RIS=1)(RD脉冲之前),可以读取ISR。

没有必要在每一个读状态操作前,都写一个OCW3命令,只要状态读取与前一次操作相关(操作同一寄存器),即,8259a记忆上一次IRR或ISR被OCW3选择。当程序查询模式时不成立。

初始化后,8259a指向IRR。

若读IMR,则不需要OCW3。输出信号将会包含IMR(当RD活跃且A0=1(OCW1))。

程序查询模式时状态读取无效,即OCW3的(P=1,RR=1)

边沿和电平触发模式

此模式由ICW1的位1设定。

若LTIM=0,中断请求将由IR输入上升沿决定,IR输入端可以保持高电平而不会产生另外的中断。

here is a figure of IRTriggering Timing Requirements。P18。

如果LTIM=1,中断请求将由IR输入端的高电平识别。而不需要边沿检测。中断请求必须在EOI命令处理前移去,或者,CPU中断允许阻止产生第二个中断。

优先级单元框图展示了一个8259a的概念性的电平感应和边沿感应电路。请一定注意:请求触发器(request latch)显然是一个D触发器。

不论在边沿还是电平触发模式,IR输入必须保持高电平直到第一个INTA的下降沿。若IR输入在此之前变为低电平,当CPU响应中断时,将默认为IR7。这是一个有用的保护措施,对于由IR输入端上的低频干扰噪声引起的响应。为了有效地实现这个功能,IR7(对应)服务程序是一个清除命令,简单的执行一个返回指令,以忽略中断干扰。如果IR7需做他用,默认的IR7仍然能够通过读取ISR检测到。正常的Ir7将会置位相应的ISR位,而默认的IR7不会。若在一个正常的IR7程序期间,一个默认的IR7发生,但ISR仍然保持置位。这种情况下,很有必要跟踪之前IR7程序是否执行过。如果另外的IR7发生,那么他是默认的。

特殊全嵌套模式

该模式用大型系统中,其中,8259a需要级联,且优先级保存在从片中。在此情况下,主片被设为特殊全嵌套模式(使用ICW4)。该模式与普通的嵌套模式有以下不同:a。当来自某一个从片的中断请求,该从片在主片的优先级模块中不会被锁住,来自该从片的更高级别的中断请求将会被主片识别,并给CPU中断。(在普通嵌套模式下,当从片的请求正被服务,从片被锁住,且更高级别的中断请求不会被响应。)

b。当存在中断服务程序,软件将会检测正被服务的中断,来自该从片只有一个。这将通过给从片发送一个非特殊中断结束(EOI)命令,然后读取它的ISR,检查是否为零。如果是空,则一个非特殊EOI被送到主片。如果不是,将不会送EOI给主片。

缓冲模式(BUFFERED MODE)

当8259a应用于大型系统,就需要使用总线驱动缓冲,需要使用级联模式。此处存在缓冲使能问题。

缓冲模式时,8259a通过SP/EN发送一个使能信号,以使能缓冲。在该模式下,无论何时8259a的数据总线输出使能,SP/EN输出激活。

这种改变迫使使用软件编辑以确定8259a是否是主片或从片。ICW4的位3设定缓冲模式,ICW4的位2决定主从片。

级联模式(CASCADE MODE)

8259A可以简单的互联成一个主片、八个从片的系统,可处理高达64级优先级。

主片通过3线级联总线控制从片。级联总线在从片的/INTA序列(sequence)中有使能作用。

在级联配置中,从片中断输出与主片中断输入相连。当从片请求时,然后被响应,在INTA期间,主片将使能相应从片发出程序地址字节2、3(8086/8088仅有字节2),。

级联总线通常是低电平,并将在第一个INTA脉冲的后沿到第三个脉冲的后沿期间,发送从片地址代码。系统中的每一片8259a必须单独初始化,并可被设定为不同的工作模式。EOI命令必须处理两次,一次主片,一次相应从片。需要一个地址译码器,以使能每一片8259a(通过CS端)。

主片的级联线只有当从片输入时才激活,没有从片输入时,级联线保持低电压。

《8259中断控制器实验》的实验报告

实验六8259中断控制器实验 6.1 实验目的 (1) 学习中断控制器8259的工作原理。 (2) 掌握可编程控制器8259的应用编程方法。 6.2 实验设备 PC微机一台、TD-PIT+实验系统一套。 6.3 实验内容 1. 单中断应用实验 (1)编写中断处理程序,利用PC机给实验系统分配的中断线,使用单次脉冲单元的KK1+按键模拟中断源,每次PC机响应中断请求,在显示器上显示一个字符。 (2)编写中断处理程序,利用PC机给实验系统分配的中断线,使用单次脉冲单元的KK1+按键模拟中断源,每次PC机响应中断请求,在显示器上显示“Hello”,中断5次后退出。 2.扩展多中断源实验 利用实验平台上8259控制器对扩展系统总线上的中断线INTR进行扩展。编写程序对8259控制器的IR0和IR1中断请求进行处理。 6.4 实验原理 1. 8259控制器的介绍 中断控制器8259A是Intel公司专为控制优先级中断而设计开发的芯片。它将中断源优先级排队、辨别中断源以及提供中断矢量的电路集于一片中,因此无需附加任何电路,只需对8259A进行编程,就可以管理8级中断,并选择优先模式和中断请求方式,即中断结构可以由用户编程来设定。同时,在不需增加其他电路的情况下,通过多片8259A的级连,能构成多达64级的矢量中断系统。它的管理功能包括:1)记录各级中断源请求,2)判别优先级,确定是否响应和响应哪一级中断,3)响应中断时,向CPU传送中断类型号。8259A的内部结构和引脚如图6-1所示。 8259A的命令共有7个,一类是初始化命令字,另一类是操作命令。8259A的编程就是根据应用需要将初始化命令字ICW1-ICW4和操作命令字OCW1-OCW3分别写入初始化命令寄存器组和操作命令寄存器组。ICW1-ICW4各命令字格式如图6-2所示,

微机接口实验报告-8259中断控制器应用实验

姓名 院专业班 年月日实验内容8259中断控制器实验指导老师 【实验目的】 (1)学习中断控制器8259的工作原理。 (2)掌握可编程控制器8259的应用编程方法。 【试验设备】 PC微机一台、TD-PIT+实验系统一套。 【实验内容】 (1) 编写中断处理程序,利用PC机给实验系统分配的中断线,使用单次脉冲单元的KK1+按键模拟中断源,每次PC机响应中断请求,在显示器上显示一个字符。 (2) 编写中断处理程序,利用PC机给实验系统分配的中断线,使用单次脉冲单元的KK1+按键模拟中断源,每次PC机响应中断请求,在显示器上显示“9”,中断显示6次后退出。 【实验原理】 1. 8259控制器的介绍 中断控制器8259A是Intel公司专为控制优先级中断而设计开发的芯片。它将中断源优先级排队、辨别中断源以及提供中断矢量的电路集于一片中,因此无需附加任何电路,只需对8259A进行编程,就可以管理8级中断,并选择优先模式和中断请求方式,即中断结构可以由用户编程来设定。同时,在不需增加其他电路的情况下,通过多片8259A的级连,能构成多达64级的矢量中断系统。它的管理功能包括:1)记录各级中断源请求,2)判别优先级,确定是否响应和响应哪一级中断,3)响应中断时,向CPU传送中断类型号。8259A的内部结构和引脚如图6-1所示。 8259A的命令共有7个,一类是初始化命令字,另一类是操作命令。8259A的编程就是根据应用需要将初始化命令字ICW1-ICW4和操作命令字OCW1- OCW3分别写入初始化命令寄存器组和操作命令寄存器组。ICW1-ICW4各命令字格式如图6-2所示,OCW1-OCW3各命令字格式如图6-3所示,其中OCW1用于设置中断屏蔽操作字,OCW2用于设置优先级循环方式和中断结束方式的操作命令字,OCW3用于设置和撤销特殊屏蔽方式、设置中断查询方式以及设置对8259内部寄存器的读出命令。 图6-1 8259内部结构和引脚图

实验六 8259中断控制(1)

实验六8259中断控制(1) 一.实验目的 1. 学习8086/8088 CPU中断系统的知识。 2. 学习8259中断控制器的使用。 二.实验要求 编写程序,使8255的A口控制双色灯。CPU执行主程序时四个绿灯亮。用+pulse作为8259的IR2的输入信号,向CPU请求中断。CPU在中断服务程序中熄灭绿灯,并使红灯亮。中断服务程序结束,又返回主程序,再使绿灯亮。 三.实验电路及连线

1.将8255的PA0~PA3接双色灯的DG1~DG4。 2.将8255的PA4~PA7接双色灯的DR1~DR4。 3.将单脉冲电路的+pulse接8259的IR2。 4.将8255的CS接200~207H。 5.将8259的CS接210~217H。 6.将K15插针连上。 四.编程提示 1. 8255初始化:A口方式0输出。 2. 8259初始化:边沿触发。 3. 设置中断矢量,将中断服务程序入口地址送入中断矢量表的相应单元,在本系统中,80000H~800FFH相当于00000H~000FFH,其中用户可用中断矢量表区域为80014H~800FFH。 4. 主程序控制8255 PA0~PA3输出点亮绿灯。 5. 编制中断服务程序,使PA4~PA7输出点亮红灯,关闭绿灯。 五.实验步骤 1. 编制程序。 2. 在PC机上编辑、汇编及连接。 3. 在实验板上按实验连线要求连接硬件线路(注意先关闭实验板电源)。 4. 连接实验板与PC机的串行通信线,开实验板电源。 5. 将程序从PC机送入实验板。 6. 运行程序,此时双色灯绿灯亮,表明在运行主程序。 7. 按一下+pulse按钮,应当红灯亮绿灯灭,表明在执行中断服务程序;过一会儿红灯熄灭了,绿灯又亮了起来,表明中断服务程序已返回了主程序。 六.实验报告 应包括画电路图、试验程序框图、编程(要有注释)、调试过程及心得体会等。

实验七-8259中断控制器实现

计算机科学与技术系 实验报告 专业名称计算机科学与技术 课程名称微机原理与接口技术 项目名称 8259A中断控制实验 班级 学号 姓名 同组人员无 实验日期 2016/06/28 一、实验目的与要求 1、了解8259的内部结构,工作原理;了解8259A与8088的接口逻辑;掌握对8259A 的初始化编程方法,了解8088是如何响应中断、退出中断的。

二、实验逻辑原理图与分析(汇编—流程图) 2.1 画实验逻辑原理图 2.2 逻辑原理图分析 实验原理与分析:由于实验中需拨动单脉冲开关,送给8259A的IR0,触发中断,8088计数中断次数,显示于G5区的数码管上。故8259中断控制实验需要8259A芯片,8282地址锁存器,用于8086CPU与8259A芯片地址线的连接,8286收发器用于8086CPU与8259A 芯片数据线的连接,通过地址译码器实现片选信号(CS)的选通。 三、程序分析 3.1程序代码分析 .MODEL TINY EXTRN Display8:NEAR ;装入外部程序块 IO8259_0 EQU 0F000H IO8259_1 EQU 0F001H .STACK 100 .DATA BUFFER DB 8 DUP(?) Counter DB ? ReDisplayFlag DB 0 .CODE START: MOV AX,@DATA

MOV DS,AX MOV ES,AX NOP CALL Init8259 CALL WriIntver MOV Counter,0 ;中断次数 MOV ReDisplayFlag,1 ;需要显示 STI ;开中断 START1: CMP ReDisplayFlag,0 JZ START1 CALL LedDisplay MOV ReDisplayFlag,0 JMP START1 Init8259 PROC NEAR MOV DX,IO8259_0 mov al,13h ;ICW1:0001 0011 上升沿触发,间隔为8,单片工作故没有ICW3,写ICW4 out dx,al mov dx,IO8259_1 mov al,08h ;ICW2:0000 1000 中断类型码为:00001,用的中断请求为IR0 out dx,al mov al,09h ;ICW4:0000 1001 000为ICW4的标识码,采用一般嵌套,缓冲方式,正常EOI,8086/8088系统 out dx,al mov al,0feh ;OCW1:1111 1110 屏蔽其他IR,允许IR0发送中断请求 out dx,al RET Init8259 ENDP WriIntver PROC NEAR PUSH ES MOV AX,0 MOV ES,AX MOV DI,20H ;20H~23H是IR0的矢量地址 LEA AX,INT_0 STOSW ;把INT_0的偏移地址写到ES:DI指向的内存单元中 MOV AX,CS STOSW ;把段基址存入ES:DI的内存单元中 POP ES RET WriIntver ENDP

8259A中断实验

实验8259单级中断控制器实验 一、实验目的 ⒈掌握8259中断控制器的接口方法。⒉ 掌握8259中断控制器的应用编程。 二、实验内容 利用8259实现对外部中断的响应和处理,要求程序对每次中断进行计数,并将计数结果送数码显示。 三、实验接线图 图6-6 四、编程指南 ⑴8259芯片介绍 中断控制器8259A是专为控制优先级中断而设计的芯片。它将中断源优先级排队、辨别中断源以及提供中断矢量的电路集于一片中。因此无需附加任何电路,只需对8259A进行编程,就可以管理8级中断,并选择优先模式和中断请求方式。即中断结构可以由用户编程来设定。同时,在不需要增加其它电路的情况下,通过多片8259A的级联,能构成多达64级的矢量中断系统。

⑵本实验中使用3号中断源IR3,“”插孔和IR3相连,中断方式 为边沿触发方式,每拨二次AN开关产生一次中断,满5次中断,显示“8259——good”。如果中断源电平信号不符合规定要求,则自动转到7号中断,显示“Err”。 五、实验程序框图 IR3中断服务程序: IR7中断服务程序: 六、实验步骤 1、按图6-6连好实验线路图。

⑴8259的INT连8088的INTR;⑵8259的INTA连8088的INTA;⑶“” 插孔和8259的3号中断IR3插孔相连,“”端初始为低电平;⑷8259的CS端接FF80H孔。 2、运行实验程序,在系统处于命令提示符“P.”状态下,按SCAL键,输入12D0,按EXEC键,系统显示8259-1。 3、拨动AN开关按钮,按满l0次显示good。 七、实验程序清单 CODE SEGMENT ;H8259.ASM ASSUME CS: CODE INTPORT1 EQU 0FF80H INTPORT2 EQU 0FF81H INTQ3 EQU INTREEUP3 INTQ7 EQU INTREEUP7 PA EQU 0FF20H ;字位口 PB EQU 0FF21H ;字形口 PC EQU 0FF22H ;键入口 ORG 12D0H START: JMP START0 BUF DB ?,?,?,?,?,? intcnt db ? data1: db0c0h,0f9h,0a4h,0b0h,99h,92h,82h,0f8h,80h,90h,88h,83h, 0c6h,0a1h db 86h,8eh,0ffh,0ch,89h,0deh,0c7h,8ch,0f3h,0bfh,8FH START0: CLD ;递加 CALL BUF1 ;写显示缓冲初值 CALL WRINTVER ;写中断向量 MOV AL,13H ;写ICW1 MOV DX,INTPORT1 OUT DX,AL MOV AL,08H ;写ICW2 MOV DX,INTPORT2 OUT DX,AL MOV AL,09H ;写ICW4 OUT DX,AL MOV AL,0F7H ;写OCW1 OUT DX,AL MOV intcnt,01H ;中断计数初值 STI ;开中断 WATING: CALL DISP ;DISP 8259-1

《8259中断控制器实验》的实验报告

实验六 8259中断控制器实验 6.1 实验目的 (1) 学习中断控制器8259的工作原理。 (2) 掌握可编程控制器8259的应用编程方法。 6.2 实验设备 PC微机一台、TD-PIT+实验系统一套。 6.3 实验容 1. 单中断应用实验 (1)编写中断处理程序,利用PC机给实验系统分配的中断线,使用单次脉冲单元的KK1+按键模拟中断源,每次PC机响应中断请求,在显示器上显示一个字符。 (2)编写中断处理程序,利用PC机给实验系统分配的中断线,使用单次脉冲单元的KK1+按键模拟中断源,每次PC机响应中断请求,在显示器上显示“Hello”,中断5次后退出。 2.扩展多中断源实验 利用实验平台上8259控制器对扩展系统总线上的中断线INTR进行扩展。编写程序对8259控制器的IR0和IR1中断请求进行处理。 6.4 实验原理 1. 8259控制器的介绍 中断控制器8259A是Intel公司专为控制优先级中断而设计开发的芯片。它将中断源优先级排队、辨别中断源以及提供中断矢量的电路集于一片中,因此无需附加任何电路,只需对8259A进行编程,就可以管理8级中断,并选择优先模式和中断请求方式,即中断结构可以由用户编程来设定。同时,在不需增加其他电路的情况下,通过多片8259A的级连,能构成多达64级的矢量中断系统。它的管理功能包括:1)记录各级中断源请求,2)判别优先级,确定是否响应和响应哪一级中断,3)响应中断时,向CPU传送中断类型号。8259A的部结构和引脚如图6-1所示。 8259A的命令共有7个,一类是初始化命令字,另一类是操作命令。8259A的编程就是根据应用需要将初始化命令字ICW1-ICW4和操作命令字OCW1-OCW3分别写入初始化命令寄存器组和操作命令寄存器组。ICW1-ICW4各命令字格式如图6-2所示,OCW1-OCW3各命令字格式如图6-3所示,其中OCW1用于设置中断屏蔽操作字,OCW2用于设置优先级循环

实验二:8259 中断控制器实验

实验二 8259A中断控制器实验 1、编制程序:拨动单脉冲开关,“”送给8259A的IR0,触发中断, 8088计数中断次数,显示于G5区的数码管上 2、运行程序 3、上下拨动单脉冲开关,拨动二次,产生一个“”,观察结果, 数码管上显示的次数与拨动开关次数是否对应。 .MODEL TINY EXTRN DISPLAY8:NEAR IO8259_0 EQU 0F000H IO8259_1 EQU 0F001H .STACK 100 .DATA BUFFER DB 8 DUP(?) COUNTER DB ? REDISPLAYFLAG DB 0 .CODE START: MOV AX,@DATA MOV DS,AX MOV ES,AX NOP CALL INIT8259 CALL WRIINTVER MOV COUNTER,0 MOV REDISPLAYFLAG,1 STI ;?a?D?? START1: CMP REDISPLAYFLAG,0 JZ START1 CALL LEDDISPLAY MOV REDISPLAYFLAG,0 JMP S TART1 INIT8259 PROC NEAR MOV DX,IO8259_0 MOV AL,13H OUT DX,AL MOV DX,IO8259_1 MOV AL,08H OUT DX,AL MOV AL,09H OUT DX,AL MOV AL,0FEH OUT DX,AL

RET INIT8259 ENDP WRIINTVER PROC NEAR PUSH ES MOV AX,0 MOV ES,AX MOV DI,20H LEA AX,INT_0 STOSW MOV AX,CS STOSW POP E S RET WRIINTVER ENDP LEDDISPLAY PROC NEAR MOV AL,COUNTER MOV AH,AL AND AL,0FH MOV BUFFER,AL AND AH,0F0H ROR A H,4 MOV BUFFER + 1,AH MOV BUFFER + 2,10H ;??áù??2?Dèòa??ê? MOV BUFFER + 3,10H MOV BUFFER + 4,10H MOV BUFFER + 5,10H MOV BUFFER + 6,10H MOV BUFFER + 7,10H LEA SI,BUFFER CALL DISPLAY8 RET LEDDISPLAY ENDP INT_0: PUSH DX PUSH AX MOV AL,COUNTER ADD AL,1 DAA MOV COUNTER,AL MOV REDISPLAYFLAG,1 MOV DX,IO8259_0 MOV AL,20H

8259中断实验

XX学院 实验报告 实验名称 姓名 学号 班级 教师 日期

一、实验内容与要求 1.1 实验内容 本次实验分为如下3个子实验: (1)单中断请求实验:利用系统总线上中断请求信号MIR7,设计一个单一中断请求实验; (2)双中断优先级实验:利用系统总线上中断请求信号MIR6和MIR7,设计一个双中断优 先级应用实验,观察8253对中断优先级的控制; (3)级联中断实验:利用系统总线上中断请求信号MIR7和SIR1,设计一个级联中断应用 实验。 1.2 实验要求 本次实验中三个子实验的实验要求如下: (1)单中断请求实验:单脉冲KK1+与主片8259的IR7相连。每按KK1+,进入一次中断, 输出7; (2)双中断优先级实验:单脉冲KK1+连主片8259的IR7,KK2+连其IR6。每当KK1+按 下时显示“7”,每当KK2+按下显示“6”; (3)级联中断实验:单脉冲KK1+连主片8259的IR7,KK2+连从片的IR1。每当KK1+按 下时显示“M7”,每当KK2+按下显示“S1”。 二、实验原理与硬件连线 2.1 实验原理 (1)中断控制器8259简介 在Intel 386EX芯片中集成有中断控制单元(ICU),该单元包含有两个级联中断控制器,一个为主控制器,一个为从控制器。该中断控制单元就功能而言与工业上标准的82C59A是一致的,操作方法也相同。从片的INT连接到主片的IR2信号上构成两片8259的级联。 在TD-PITE实验系统中,将主控制器的IR6、IR7以及从控制器的IR1开放出来供实验使用,主片8259的IR4供系统串口使用。8259的内部连接及外部管脚引出如图1-1:

计算机组成原理与接口技术笔记 15 中断8259中断控制器

8259有4个初始化控制字,3个操作控制字。 三个重要的寄存器:中断服务寄存器、中断屏蔽寄存器、中断请求寄存器 中断请求寄存器:发出中断请求的设备 中断屏蔽寄存器:被屏蔽中断的设备 中断服务寄存器:正在被响应中断的设备 8086处理器芯片有INTR和NMI引脚,用来接收中断请求,会通过INTA引脚来发回中断响应。 INTR是可以屏蔽的中断,NMI是不可屏蔽的中断。都是输入高电平时有效。 INT 02H是已经分配的NMI中断。 INTR接收的中断的处理程序没有在中断向量中初始化,需要我们自己初始化。 INT 00:除法出错 INT 01:单步执行 也可以把TF标志位设置为1,标志寄存器不能直接进行赋值,所以要通过堆栈来赋值。 INT 03:断点中断 遇到INT 03则中断程序执行 INT 04:有符号数溢出中断 指令:INTO,如果OF为1,则执行INT 04中断 如何编写自己的中断服务程序 AH = 35H,INT 21H,可以获取中断向量表中,中断号为AL的中断服务程序的入口地址。 返回值在ES和BX中。 AH = 25H,INT 21H,可以设置中断向量表,可以把我们写的中断服务程序的入口地址写入到中断向量表中。 入口地址通过DS:DX传递进去。 中断服务程序的返回是IRET 中断的优先级 一般情况下会给不同的IO设备分配不同的优先级,如果同时有中断请求,则先处理优先级高的中断请求。 优先级低的中断请求在执行的时候,优先级高的中断请求可以把优先级低的中断请求打断。 中断屏蔽位:对于不同优先级的中断请求 假设有4个中断设备,则设置4个位表示这4个设备发出的请求是否能被响应,如果该位是1,则不能响应,如果是0则能够响应。 8259芯片:可编程中断控制器 8086处理器只有一个INTR来接收中断请求信号,如果直接接收则只能接收一个外设的中断请求。用8259芯片来扩展。 8259可以接收8路中断请求信号,IR0最低,IR7最高 8259是处理器的一个外设,也需要分配端口地址。

8259A中断控制器和8253计数器

8259A中断控制器和8253计数器·定时器实验 浏览次数:1129次悬赏分:50|解决时间:2008-12-2 12:17 |提问者:liushang8811 程序1 参考流程图 1:开始 2:关中断 3:初始化8253(设定定时器0和1的工作方式及技术初值) 4:使用INT 21H的35H号功能获取0AH号中断向量并保存。 5:使用INT 21H的25H号功能设置0AH号中断的新中断向量。 6:设置IMR寄读器及允许IRQ2中断。 7:开中断 8:循环等待中断。 程序2 参考流程图:编写中断服务程序。要求主机每响应一次IRQ2的中断时,就执行一次终端服务子程序。中断服务子程序的核心就是显示字符串“THIS IS A 8259A INTERRUPT” 1:开始 2:显示字符串 3:技术结束?终端结束并返回 4:关中断 5: 使用INT 21H的25H号功能恢复原OAH号中断的中断向量 6: 恢复IMR寄存器的原值 7: 开中断 8: 结束,返回DOS 用汇编,急用,跪谢 1. MOV AX,FLAGS AND AX,1111110111111111B ;关中断 MOV FLAGS,AX

MOV AL,00110110B ;假设定时器0设为方式3 OUT 43H,AL MOV AL,XXH ; OUT 40H,AL MOV AL,XXH OUT 40H,AL ;定时器0初值 MOV AL,01110110B ;假设定时器1设为方式3 OUT 43H,AL MOV AL,XXH ; OUT 41H,AL MOV AL,XXH OUT 41H,AL ;定时器1初值 MOV AH,35H MOV AL,0AH INT 21H PUSH ES ;保存原向量 PUSH BX PUSH DS ;借用DS和DX作中断入口,暂时保存原值PUSH DX MOV DS,XXH ;新中断向量段地址 MOV DX,XXH ;新中断向量偏移量 MOV AH,25H MOV AL,0AH INT 21H

8259a中断控制器——利用IRQ2显示中断过程

8259a中断控制器:利用8259A的IRQ2显示中断过程 目录 8259a中断控制器:利用8259A的IRQ2显示中断过程 (1) 设计题目: (1) 要求: (1) 设计思路: (1) 实验代码: (2) 实验心得体会: (10) 设计题目: 利用8259A IRQ2显示中断过程 要求: 1.主是在7段数码管上循环显示‘8’从右到左显示 2.中断服务中在7段数码管上依次显示全1234567 89要去显示2秒左右时间可采用软件Software延迟(时间可通过调试大致2秒左右)总计中断9次结束返回DOS 3.每次由手动产生IRQ2中断请求信号引起中断 设计思路: 软件Software方面有两个主要部分:主和中断服务子 主首先要完成是些和处理工作例如查找设备设置TPC卡中9054芯片IO口,保存原来0AH号中断中断向量设置新中断向量设置中断掩码显示提示信息然后打开中断进入主循环在主循环中不断在LED上从右向左显示8直到被IRQ2中断信号打断此外在主中还对中断执行进行计数当计数满9次后自动跳出为了使主上8循环可以看出来故将显示8延迟设计比较长当完成9次中断主还要完成些后续处理工作:恢复中断掩码;恢复中断向量;设置TPC卡中9054芯片IO口,关闭中断返回DOS 中断子完成在6位数码管上“同时”显示个数功能这个数为1—9中某个可以用循环次数作为参数这里同时显示实质上是利用视觉上暂停效果即只要每秒能在同个数码管上显示信息超过24次看起来就是同时了而这点在现在计算机速度条件下很容易实现为了不发生混乱在中断子执行过程中不允许再次中断 另外中还有两个子:findtpc和dispword这些是为了完成查找设备等预处理 硬件方面实验时把总线上IRQ2引脚和拨键开关相连以手动产生中断信号另外再把LED片选信号CS和210-217相连(注:LED显示是通过向LED数据端口送入数据再向LED位选端口送入

中断控制器8259A及中断服务

实验内容:中断控制器8259A及中断服务 1、实验连线原理见图1所示: 8259A连线: (1)单脉冲与时钟单元“”插孔和8259的3号中断IR3插孔相连作为中断源; (2)8259的INT连8088的INTR(Xl5); (3)8259的INTA连8088的INTA(Xl2); (4)8259的CS端接EX1(8259A端口地址是60H,61H); (5)A0→A0。 (6)IOWR→IOWR; (7)IORD→IORD; (8)连通CPU和8259A的数据总线,JX4→JX17。 8255连线: (1)将8255的A端口的PA7到PA0连接到灯L1~L8上。 图1:实验连线图 2、实验原理:按动按键AN0后,单脉冲与时钟单元部件会产生“”信号,该信号的上升沿作为中断请求送8259A的IR3引脚,如果8259A没有屏蔽该级中断并且其优先级最高,8259A向CPU的INTR引脚送中断,CPU如果允许响应中断,则进入中断处理子程序,中断处理子程序向8255A的A端口送数据,将灯L1~L8点亮1秒。 3、实验要求:单片8259A以缓冲方式连接数据总线,以上升沿作为中断请求信号,中断源通过IR3引入,优先级采用一般全嵌套方式,非自动中断结束方式,引脚IR0~IR7的中断类型号为08F~0FH,编写一个汇编程序,主程序完成8255和8259A的初始化,循环等待中断请求;中断处理子程序将灯点亮1秒后熄灭。 4、端口地址: 5、系统内存分配:

5、程序结构: CODE SEGMENT ASSUME CS:CODE MAIN PROC START: ;主过程 ;初始化8259 ;初始化8255 ;调用3号中断 MAIN ENDP INT3 PRCO ……;中断处理子程序 INT3 ENDP DELAY PROC …… ;延时子过程 DELAY ENDP CODE ENDS END 6、程序流程图 主程序

实验六 8259中断控制(1)

星期二1-2节序号:1 实验六8259中断控制(1) 12120771 易远明 一、电路图 二、程序框图

三、实验程序及注释 ASSUME CS:CODE INTPORT1 EQU 0060H INTPORT2 EQU 0061H INTQ3 EQU INTREEUP3 INTCNT DB ? ORG 1200H START: CLD MOV DX,0FF2BH MOV AL,80H ;设置8255方式字:A口出 OUT DX,AL CALL WRINTVER ;WRITE INTRRUPT MOV AL,13H ;ICW1=00010011B,边沿触发、单8259、需ICW4 MOV DX,INTPORT1 OUT DX,AL MOV AL,08H MOV DX,INTPORT2 OUT DX,AL MOV AL,09H ;ICW4=00001001B,非特殊全嵌套方式、缓冲/从、正常EOI OUT DX,AL MOV AL,0F7H ;OCW1=11110111B OUT DX,AL MOV INTCNT,01H ;延时 STI WATING: MOV DX,0FF28H ;主程序绿灯亮(低四位为0则绿灯亮,高四位为1故红灯灭)MOV AL,0F0H OUT DX,AL JMP WA TING WRINTVER: MOV AX,0H

MOV ES,AX MOV DI,002CH ;中断向量地址2CH=0BH*4 LEA AX,INTQ3 STOSW ;送偏移地址 MOV AX,0000h STOSW ;送段地址 RET INTREEUP3:CLI ;中断服务子程序开始 MOV DX,0FF28H ;中断服务子程序执行红灯亮 MOV AL,0FH ;低四位为1则绿灯灭,高四位为0故红灯亮 OUT DX,AL CALL DELAY1S MOV AL,20H ;OCW2=001 00 000B非特殊EOI命令,结束命令,用于完全嵌套方式的中断结束 MOV DX,INTPORT1 OUT DX,AL STI ;开系统中断 IRET DELAY1S: MOV CX,0FFFFH MOV BX,5 L:DEC CX JNZ L DEC BX JNZ L RET CODE ENDS END START

8259A中断控制器实现

一、实验目的与要求 1、了解8259的内部结构,工作原理;了解8259A 与8088的接口逻辑; 掌握对8259A 的初始化编程方法,了解8088是如何响应中断、退出中断的。 二、实验逻辑原理图与分析 2.1 画实验逻辑原理图 AD0~AD15 ALE WR# INTR INTA 数据锁存器 地址锁存器 地址译码器D0~D7 CS#A0 WR#INT INTA# IR0 A0 2.2 逻辑原理图分析 8282地址锁存器,用于8086CPU 与8259A 芯片地址线的连接用于总线周期T1状态 下发出的地址信号。经锁存后的地址信号可以在整个周期内保持稳定不变,8286收发器用于8086CPU 与8259A 芯片数据线的连接,通过地址译码器实现片选信号(CS )的选通。 (1)、8086是Intel 系列的16为微处理器,芯片上有4万个晶体管,采用NMOS 工艺制造,用单一的+5V 电源,时钟频率为4.77MHZ~10MHZ.8086有16根数据线和20根地址线,它既能处理16位数据,也能处理8位数据,可寻址的内存空间为1MB 。 (2)、8282锁存器:用来锁存8086访问存储器或I/O 端口时,于总线周期T1状态下发出的地址信号。经锁存后的地址信号可以在整个周期内保持稳定不变 (3)、8286收发器:可以进行双向数据锁存 (4)、8259A 可编程中断控制器主要功能: 1)、 1片8259A 能管理8级中断,通过级联用9片8259A 可以构成64 级主从 式中断系统 2)、每一级中断可以屏蔽或允许 3)、在中断响应周期,8259A 可提供相应的中断类型号。 4)、 可编程使8259A 工作在多种不同的方式。 (5)、8259A 的内部结构:

实验一 8259单级中断控制器实验

实验一8259单级中断控制器实验 一、实验目的 ⒈掌握8259中断控制器的接口方法。 ⒉掌握8259中断控制器的应用编程。 二、实验内容 利用8259实现对外部中断的响应和处理,要求程序对每次中断进行计数,并将计数结果送数码显示。 三、实验接线图 图6-6 四、编程指南 ⑴8259芯片介绍 中断控制器8259A是专为控制优先级中断而设计的芯片。它将中断源优先级排队、辨别中断源以及提供中断矢量的电路集于一片中。因此无需附加任何电路,只需对8259A进行编程,就可以管理8级中断,并选择优先模式和中断请求方式。即中断结构可以由用户编程来设定。同时,在不需要增加其它电路的情况下,通过多片8259A的级联,能构成多达64级的矢量中断系统。

⑵本实验中使用3号中断源IR3,“”插孔和IR3相连,中断方式为边沿触发方式,每拨二次AN开关产生一次中断,满5次中断,显示“8259——good”。如果中断源电平信号不符合规定要求,则自动转到7号中断,显示“Err”。 五、实验程序框图 IR3中断服务程序: IR7中断服务程序:

六、实验步骤 1、按图6-6连好实验线路图。 ⑴ 8259的INT连8088的INTR; ⑵ 8259的INTA连8088的INTA; ⑶“”插孔和8259的3号中断IR3插孔相连,“”端初始为低电平; ⑷ 8259的CS端接FF80H孔; ⑸连JX4→JX17。 2、DJ-8086k软件启动和联机 ⑴启动和联机。双击桌面上‘DJ-8086k’快捷图标,即可运行DJ-8086k软件; ⑵新建文件:单击菜单栏“文件”或工具栏“新建”图标,即会建立一个新的源程序 编辑窗口,此时可在此窗口编辑、输入源程序(注:新建文件扩展名为 .ASM)。 或打开文件F3:单击菜单栏“文件”或工具栏“打开”图标,弹出“打开文件”的对话框,然后选择要装入的源文件,单击“确定”即可装入源文件。; 3、调试程序 ⑴编译装载F9: 打开源文件,依次单击:调试”\“编译装载F9”或工具栏上的编译装载图标,状 态栏会提示正在编译、编译成功、正在装载数据、装载数据结束,几秒钟后便会弹出‘源文件调试窗口’,如编译出错,会提示错误信息,待修改源文件正确后,重新编译装载即可; ⑵连续运行; 单击菜单栏“调试”下的“连续运行”或单击工具栏的连续运行图标,即全速连续运行程序,系统显示8259-1。 ⑶在系统处于命令提示符“P.”状态下,输入12D0,按EXEC键,系统显示8259-1。 ⑷拨动AN开关按钮,按满6次显示good。 七、实验程序清单 CODE SEGMENT ;H8259.ASM ASSUME CS: CODE INTPORT1 EQU 0FF80H INTPORT2 EQU 0FF81H INTQ3 EQU INTREEUP3 INTQ7 EQU INTREEUP7 PA EQU 0FF20H ;字位口 PB EQU 0FF21H ;字形口 PC EQU 0FF22H ;键入口 ORG 12D0H START: JMP START0 BUF DB ?,?,?,?,?,?

实验二中断控制电路实验

实验二中断控制电路实验 一. 实验目的 1.学习单片机的中断控制原理。 2.编程中断控制器。 二. 实验环境 硬件环境:奔 3 以上处理器,512MB 以上内存空间 软件环境: windowsXP 以上操作系统,emu8086 编译环境, Proteus7.5sp3。 三. 实验内容与完成情况 1.实验电路图 2.实验原理 8259 中断控制器是专为控制优先级中断设计的芯片。它将中断源优先级排队,辩别中 断源以及提供中断矢量的电路集于一片中。因此无需附加任何电路,只需对8259 进行编程,就可以管理8 级中断,并选择优行模式和中断请求方式,即中断结构可以由用户编程来设定。 同时,在不需要增加其它电路的情况下,通过多片8259 的级联,能构成多达64 级的矢量中断系统。 (1) 写初始化命令字 * 写初始化命令字ICW1(A0=0) ,以确定中断请求信号类型,清除中断屏蔽寄存器,中断优 先级排队和确定系统用单片还是多片。

* 写初始化命令字ICW2 ,以定义中断向量的高五位类型码。 * 写初始化命令字ICW3 ,以定义主片8259A 中断请求线上IR0~IR7 有无级联的8259A 从片。 第 i 位=0,表明IRi 引脚上无从片 第 i 位=1,表明IRi 引脚上有从片 * 写初始化命令ICW4 ,用来定义8259A 工作时用8085 模式,还是8088 模式,以及中断服务寄存器复位方式等。

(2) 写控制命令字 * 写操作命令字0CW1,用来设置或清除对中断源的屏蔽。 第 i 位=0,对应的中断请求IRi 开放 第 i 位=1,对应的中断请求IRi 屏蔽 注:OCW1 如不写,则在初始化命令写入后,OCW1 为全开放状态。 * 操作命令字OCW2 ,设置优先级是否进行循环、循环方式及中断结束方式。注:8259A 复位时自动设置IR0 优先权最高,IR7 优先权最低。

13281036_刘大力_8259中断控制器作业

接口作业3: 8259-1:利用8255触发8259A的中断点亮 LED 一、目的 掌握8259A矢量中断方式的硬件连接和软件编程的方法,同时掌握中断和其它接口芯片配合来完成某一特定任务的方法。 二、内容 8255的PC6作为8259A的中断源,8255每向8259A发出中断请求,都让LED指示灯交替点亮和熄灭。 三、实验接线图 图1-4 实验连线图 四、编程提示 1、中断服务程序的主要功能是交替点亮和熄灭LED指示灯(即第1次进中断点亮LED, 第2次进中断则熄灭LED)。当然8255A能使用前需要在主程序中初始化。 2、主程序可以采样死等待的方式,如果要结束程序,可以按动实验平台的Reset键。 也可以采用计数的方法,即进中断5次后结束程序。 3、8255的PC6作为中断源,应采用上升沿触发方式(由低到高的变化),为了能够进 行下次中断,PC6必须变为低点平。 4、为了能使LED的闪烁可见,在中断各申请之间加入延迟程序。

.MODEL SMALL .386 CODE SEGMENT ASSUME CS:CODE START: MOV DX,203H MOV AL,10000000B ;设置8255控制字 OUT DX,AL MOV CL,0 CLI ;关386CPU中端 IN AL,21H;写入中断屏蔽字OCW1时,采用读取-修改-写入的顺序 AND AL,11011111B OUT 21H,AL;将中断入口地址写入中断向量表 PUSH DS MOV BX,0 MOV DS,BX LEA AX,CS:INT_PROC ;将中断程序的入口地址给AX MOV BX,5 ;N=IRX 中端IR5 MOV SI,30H ;BASE=30H 基址 ADD SI,BX ;W基址+IR5=中断类型号35H SAL SI,2 ;中断类型号为35H*4=中断向量存在SI MOV DS:[SI],AX ;将入口地址AX送到中断向量表中 PUSH CS POP AX MOV DS;[SI+2],AX POP DS

使用8259A的单级中断控制实验

实验五使用8259A的单级中断控制实验 一、实验目的 1、掌握中断控制器8259A与微机接口的原理和方法。 2、掌握中断控制器8259A的应用编程。 二、预备知识 1、8259A的内部结构 8259A是专为控制优先级中断而设计的芯片。它将中断源按优先级排队、辨认中断源、提供中断向量的电路集成于一体,只要用软件对它进行编程,就可以管理8 级中断。 如图5-19所示,它由中断请求寄存器(IRR)、优先级分析器、中断服务寄存器(ISR)、中断屏蔽寄存器(IMR)、数据总线缓冲器、读写控制电路和级联缓冲器、比较器组成。 图5-19 中断请求寄存器:寄存所有要求服务的请求IR0~IR7。 中断服务寄存器:寄存正在被服务的中断请求。 中断屏蔽寄存器:存放被屏蔽的中断请求,该寄存器的每一位表示一个中断号,该位为1,屏蔽该号中断,否则开放该号中断。 数据总线缓冲器:是双向三态的,用以连接系统总线和8259A内部总线,通过它可以由CPU对8259A写入状态字和控制字。 读写控制电路:用来接受I/O命令,对初始化命令和操作命令字寄存器进行写入,以确定8259A的工作方式和控制方式。 级联缓冲器/比较器:用于多片8259A的连接,能构成多达64级的矢量中断系统。 2、8259A编程及初始化 (1) 写初始化命令字

优先级排队和确定系统用单片还是多片。 * 写初始化命令字ICW2,以定义中断向量的高五位类型码。 * 写初始化命令字ICW3,以定义主片8259A中断请求线上IR0~IR7有无级联的8259A从片。 第i位=0,表明IRi引脚上无从片 第i位=1,表明IRi引脚上有从片 * 写初始化命令ICW4,用来定义8259A工作时用8085模式,还是8088模式,以及中断

8259中断控制实验报告

8259中断控制实验 一.实验目的 1. 掌握8259 中断控制器的工作原理。 2. 掌握系统总线上IR1,IR2 中断请求的应用编程方法。 二.实验设备 IA-32 架构的微机系统及应用教学平台一套。 三.实验原理 3.1 中断控制器8259简介 中断控制器8259 是Intel公司专为控制优先级中断而设计开发的芯片。它将中断源优先级排队、辨别中断源以及提供中断矢量的电路集于一片中,因此无需附加任何电路,只需对8259 进行编程,就可以管理8 级中断,并选择优先模式和中断请求方式,即中断结构可以由用户编程来设定。同时,在不需增加其他电路的情况下,通过多片8259 的级连,能构成多达64 级的矢量中断系统。它的管理功能包括:1)记录各级中断源请求,2)判别优先级,确定是否响应和响应哪一级中断,3)响应中断时,向CPU 传送中断类型号。8259 的内部结构和引脚如图1 所示。 图 1 8259 内部结构和引脚图 8259 的命令共有7 个,一类是初始化命令字,另一类是操作命令。8259 的编程就是根据应用需要

将初始化命令字ICW1-ICW4 和操作命令字OCW1- OCW3 分别写入初始化命令寄存器组和操作命令寄存器组。ICW1-ICW4 各命令字格式如图2所示,OCW1-OCW3各命令字格式如图3 所示,其中OCW1 用于设置中断屏蔽操作字,OCW2 用于设置优先级循环方式和中断结束方式的操作命令字,OCW3 用于设置和撤销特殊屏蔽方式、设置中断查询方式以及设置对8259 内部寄存器的读出命令。 图 2(a) ICW1格式 图 2(b) ICW2格式 图 2(c) ICW3格式 图 2(d) ICW4格式

实验五 8259A中断控制器实验

南昌大学实验报告 学生姓名:林海金学号:6100210178 专业班级:卓越通信101班 实验类型:验证□综合□设计□创新实验日期:2012-5-22 实验成绩: 一、实验项目名称 实验五8259A中断控制器实验 二、实验目的 (1)了解8259A中断控制器的工作原理。 (2)了解PC机中断的原理和过程。 (3)学会中断程序的编写。 三、实验要求 编写中断程序,在请求8259A1时,能够响应8259A的硬件中断,并在数码管上显示“IRQ0…”字样,中断结束时,显示“E…IRQ”。 四、实验仪器及连线方式 1)实验仪器:AEDK-T598D实验系统。 2)连线方式:INT0连接至+PULSE;8259A的片选接至试验箱的200H;8279的片选接至210H~217H。 五、实验说明 以中断0为例,先加载主中断程序,然后再加载中断程序IRQ0程序,然后打开对话窗口,输入“SW 0:0020,<回车>0000,””8200<回车>”,在执行“G8100:0<回车>Y”即可。

六、实验参考程序 INT00 EQU 200H INT01 EQU 201H Z8279 EQU 239H D8279 EQU 238H LEDMODE EQU 00H SCANFRQ EQU 38H DATA SEGMENT DATA ENDS STACK SEGMENT STA DW 50 DUP(?) TOP EQU LENGTH STA STACK ENDS CODE SEGMENT ASSUME CS:CODE,DS:DATA,SS:STACK START: CLI MOV AL,13H MOV DX,INT00 OUT DX,AL NOP NOP MOV AL,8 MOV DX,INT01 OUT DX,AL MOV CX,0FFFH L00: LOOP L00 MOV AL,3 MOV DX,INT01 OUT DX,AL MOV CX,0FFFH MOV CX,0FFFH L01: LOOP L01 NOP NOP MOV DX,Z8279 MOV AL,LEDMODE OUT DX,AL MOV AL,SCANFRQ OUT DX,AL MOV DX,INT01 MOV AL,00H OUT DX,AL MOV CX,0FFFH L02: LOOP L02 MOV DX,INT00 MOV AL,20H OUT DX,AL MOV CX,0FFFH L03: LOOP L03 MOV DX,Z8279 MOV AL,90H OUT DX,AL MOV AL,0D0H OUT DX,AL MOV CX,0FFFFH L2: LOOP L2