波特率发生器

串口RS232通信程序(Verilog)

串口有9个管脚,其中只有三个是最重要的,分别是

pin 2: RxD (receive data)接收数据

pin 3: TxD (transmit data)发送数据

pin 5: GND(ground)地

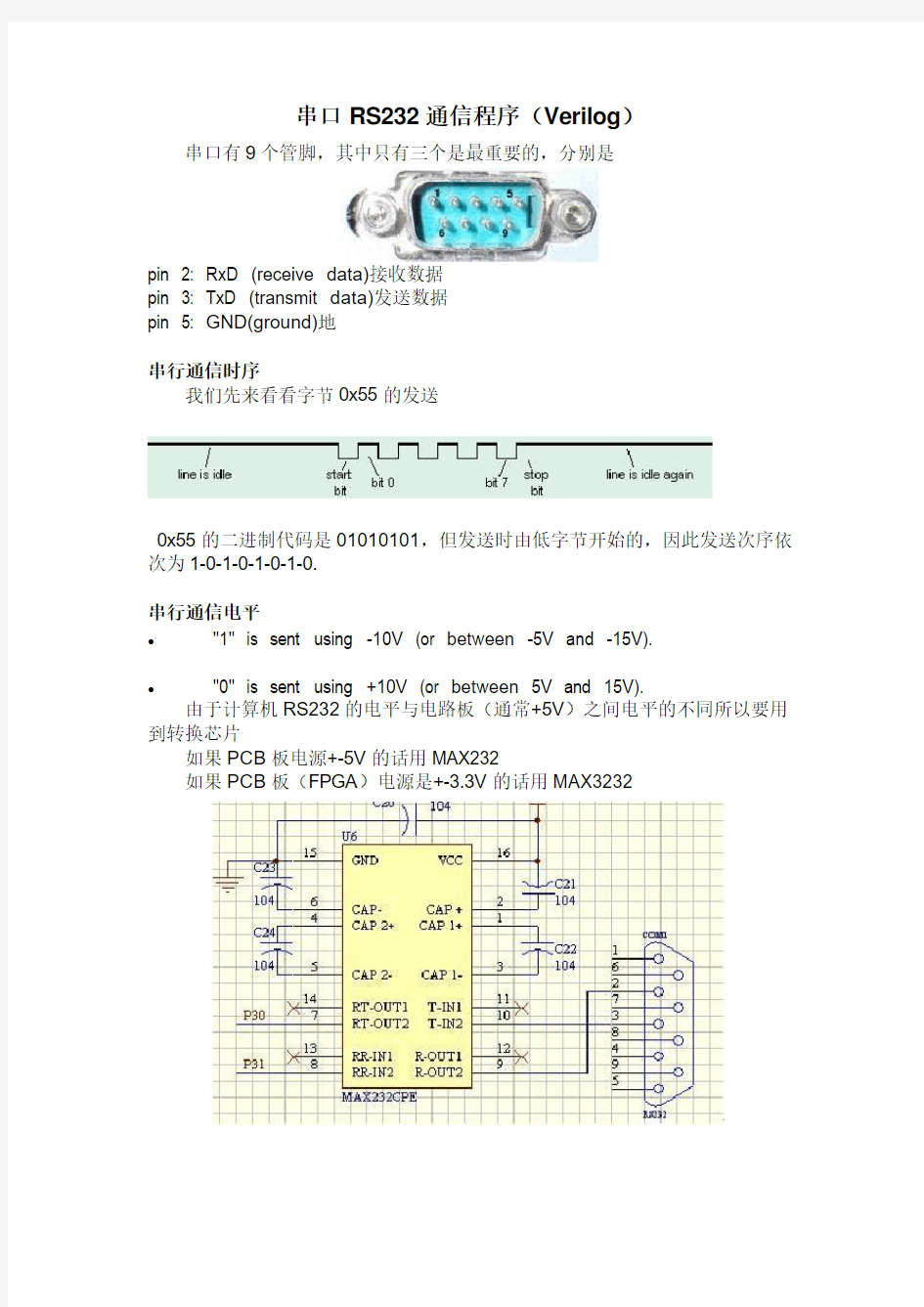

串行通信时序

我们先来看看字节0x55的发送

0x55的二进制代码是01010101,但发送时由低字节开始的,因此发送次序依次为1-0-1-0-1-0-1-0.

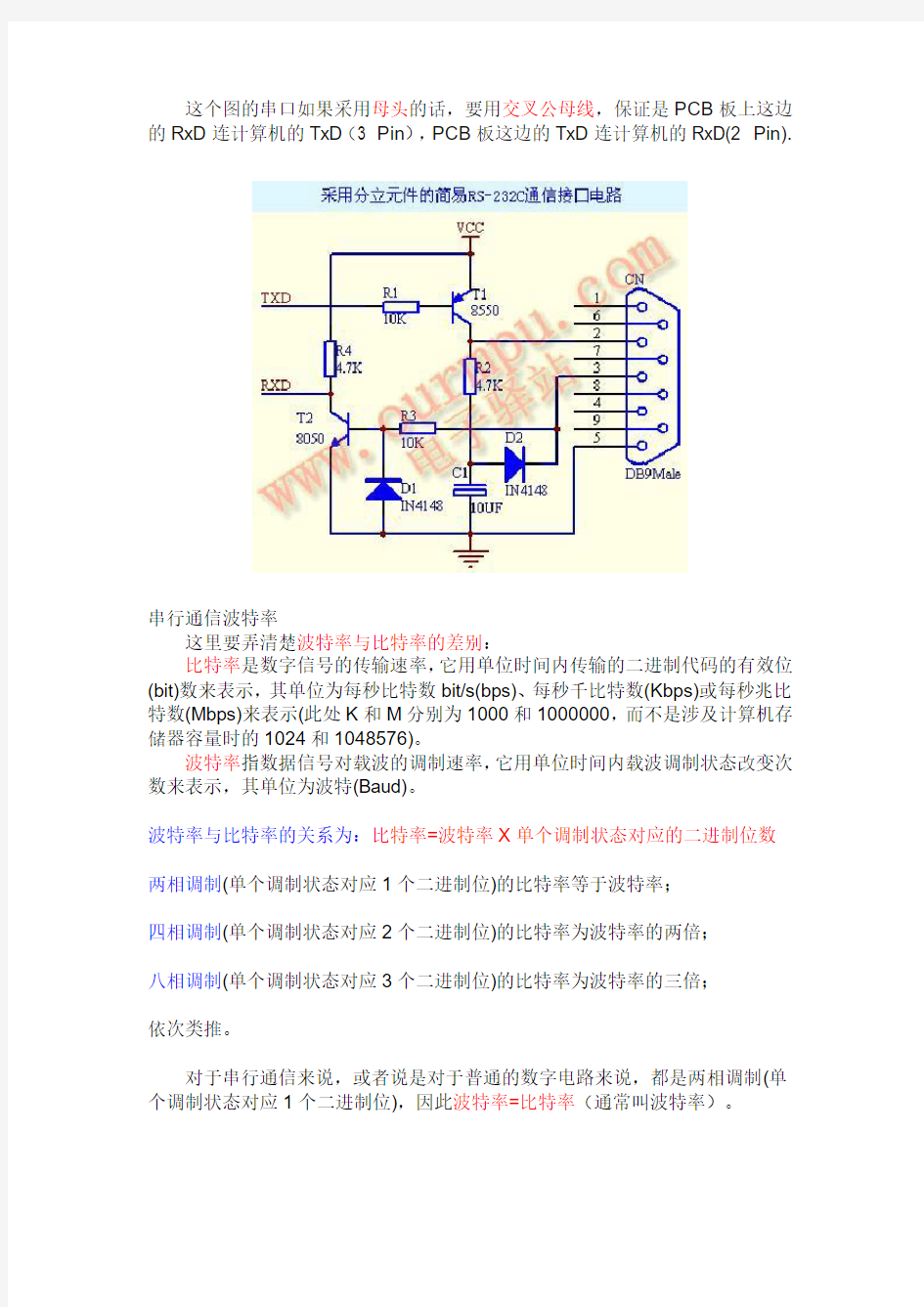

串行通信电平

?"1" is sent using -10V (or between -5V and -15V).

?"0" is sent using +10V (or between 5V and 15V).

由于计算机RS232的电平与电路板(通常+5V)之间电平的不同所以要用到转换芯片

如果PCB板电源+-5V的话用MAX232

如果PCB板(FPGA)电源是+-3.3V的话用MAX3232

这个图的串口如果采用母头的话,要用交叉公母线,保证是PCB板上这边的RxD连计算机的TxD(3 Pin),PCB板这边的TxD连计算机的RxD(2 Pin).

串行通信波特率

这里要弄清楚波特率与比特率的差别:

比特率是数字信号的传输速率,它用单位时间内传输的二进制代码的有效位(bit)数来表示,其单位为每秒比特数bit/s(bps)、每秒千比特数(Kbps)或每秒兆比特数(Mbps)来表示(此处K和M分别为1000和1000000,而不是涉及计算机存储器容量时的1024和1048576)。

波特率指数据信号对载波的调制速率,它用单位时间内载波调制状态改变次数来表示,其单位为波特(Baud)。

波特率与比特率的关系为:比特率=波特率X单个调制状态对应的二进制位数

两相调制(单个调制状态对应1个二进制位)的比特率等于波特率;

四相调制(单个调制状态对应2个二进制位)的比特率为波特率的两倍;

八相调制(单个调制状态对应3个二进制位)的比特率为波特率的三倍;

依次类推。

对于串行通信来说,或者说是对于普通的数字电路来说,都是两相调制(单个调制状态对应1个二进制位),因此波特率=比特率(通常叫波特率)。

PS:可以看看下面图就知道什么是四相调制。

如果系统时钟是1.8432MHz ,那16分频就得到115200Hz

reg [3:0] BaudDivCnt;

always @(posedge clk) BaudDivCnt<= BaudDivCnt + 1;

wire BaudTick = (BaudDivCnt==15);

但通常系统的时钟不是刚刚好是波特率的整数倍,如果不采用DCM对系统进行倍频的话,可以采用下面程序进行处理,设系统时钟为2MHz=2000000Hz 2000000/115200=17.36111

1024/59= 17.356

2000000/115200≈1024/59

两个频率很接近,可以采用下面程序产生我们要的波特率。

// 10 bits for the accumulator ([9:0]), and one extra bit for the accumulator carry-out ([10])

reg [10:0] acc; // 11 bits total!

always @(posedge clk)

acc<= acc[9:0] + 59;

// use only 10 bits from the previous result, but save the full 11 bits

wire BaudTick = acc[10]; // so that the 11th bit is the carry-out

当系统时钟为2MHz的时候,计算得到的波特率的值为115234,与115200只有0.03%的误差。

我们怎么得到“59”呢,可以看下面的推导

其中Baud< 参照上面的程序与公式推导可以把程序修改如下: parameter ClkFrequency = 25000000; // 25MHz parameter Baud = 115200; parameter BaudGeneratorAccWidth = 16; parameter BaudGeneratorInc = (Baud< reg [BaudGeneratorAccWidth:0] BaudGeneratorAcc; always @(posedge clk) BaudGeneratorAcc<= BaudGeneratorAcc[BaudGeneratorAccWidth-1:0] + BaudGeneratorInc; wire BaudTick = BaudGeneratorAcc[BaudGeneratorAccWidth]; 当要注意的是,上面程序中BaudGeneratorInc的计算公式出错,因为在Verilo g语言中中间结果只能32位,而这个公式计算的结果超过了32位。所以要把这行改为 parameter BaudGeneratorInc = ((Baud<<(BaudGeneratorAccWidth-4))+(ClkFrequency>>5))/(ClkFrequency>> 4); 程序改变,得到的波特率不变。 常用的RTL语法结构如下: ☆模块声明:module……endmodule ☆端口声明:input,output,inout(inout的用法比较特殊,需要注意) ☆信号类型:wire,reg,tri等,integer常用语for语句中(reg,wire时最常用的,一般tri和integer 不用) ☆参数定义:parameter ☆运算操作符:各种逻辑操作符、移位操作符、算术操作符大多时可综合的(注:===与!==是不可综合的) ☆比较判断:if……else,case(casex,casez)……default endcase ☆连续赋值:assign,问号表达式(?:) ☆always模块:(敏感表可以为电平、沿信号posedge/negedge;通常和@连用) ☆begin……end(通俗的说,它就是C语言里的“{ }”) ☆任务定义:task……endtask ☆循环语句:for(用的也比较少,但是在一些特定的设计中使用它会起到事半功倍的效果) ☆赋值符号:= 和<= (阻塞和非阻塞赋值,在具体设计中时很有讲究的) 可综合的语法时verilog可用语法里很小的一个子集,用最精简的语句描述最复杂的硬件,这也正是硬件描述语言的本质。对于做RTL级设计来说,掌握好上面这些基本语法是很重要。 相信大家在看了这么多了verilog语法书籍以后一定有点烦了,那么现在我告诉大家一个好消息,对于一个RTL级的设计来说,掌握了上面的语法就已经足够了,无论多么牛逼的工程师,在他的代码 里无非也就是上面一些语法而已。当然了,对于一个能够进行很好的仿真验证的代码,一般还需要在RTL级的设计代码中添加一些延时之类的语句,比如大家一定知道#10的作用,就是延时10个单位时间,这个语句虽然在仿真的时候是实实在在的延时,但是这个语句在综合后是会被忽略的,也就是说在我们综合并且布局布线最后烧进FPGA里,这个#10的延时是不会在硬件上实现的。所以说,上面给出的这些语法才是可以最后在硬件上实现的,其它的语法大多会在综合后被忽略。这么一来大家就要问了,为什么语法书里又要给出这么多的语法呢?呵呵,它们大都是为仿真验证是写testbench 准备的,先点到为止,下集继续! 对于模型(module)的建立,要保证可综合性应该注意: (1)不使用initial。(被忽略) (2)不使用#10。(被忽略) (3)不使用循环次数不确定的循环语句,如forever、while等。 (4)不使用用户自定义原语(UDP元件)。 (5)尽量使用同步方式设计电路。 (6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 (7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。 (8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。(10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。 (11)如果不打算把变量推导成锁存器,那么必须在if语句或case语句的所有条件分支中都对变量明确地赋值。 (12)避免混合使用上升沿和下降沿触发的触发器。 投影机串口码大全 3M ................................................................... 错误!未定义书签。ASK .................................................................. 错误!未定义书签。BARCO ................................................................ 错误!未定义书签。BOXLIGHT ............................................................. 错误!未定义书签。CHRISTIE ............................................................. 错误!未定义书签。DIGITEL .............................................................. 错误!未定义书签。EIKI ................................................................. 错误!未定义书签。INFOCUS .............................................................. 错误!未定义书签。LENOVO ............................................................... 错误!未定义书签。LUMENS ............................................................... 错误!未定义书签。NEC .................................................................. 错误!未定义书签。OPTOMA ............................................................... 错误!未定义书签。PLUS ................................................................. 错误!未定义书签。POLAROID ............................................................. 错误!未定义书签。PROJECTIONDESIGN ..................................................... 错误!未定义书签。PROXIMA .............................................................. 错误!未定义书签。VIEWSONIC ............................................................ 错误!未定义书签。爱普生............................................................... 错误!未定义书签。奥视................................................................. 错误!未定义书签。东芝................................................................. 错误!未定义书签。飞利浦............................................................... 错误!未定义书签。富士通............................................................... 错误!未定义书签。惠普................................................................. 错误!未定义书签。佳能................................................................. 错误!未定义书签。明基................................................................. 错误!未定义书签。三洋................................................................. 错误!未定义书签。 基于Verilog HDL语言的可综合性设计 1 引言 逻辑综合带来了数字设计行业的革命,有效地提高了生产率,减少了设计周期时间。在手动转换设计的年代,设计过程受到诸多限制,结更容易带来人为的错误。而一个小小的错误就导致整个模块需进行重新设计,设计转换工作占去了整个设计周期的大部分时间,验证工作进行困难,设计技术无法重用等等。而自动逻辑综合工具的出现,突破了上述种种限制,使得设计者从繁琐的转换工作中解脱出来,将更多的时间用于验证和优化,不仅保证了功能的实现,而且有利于提高性能。可见,综合在逻辑设计中具有举足轻重的作用。 2 综合的概念及其过程 2.1 逻辑综合概述 综合就是在给定标准元件库和一定的设计约束条件下,把用语言描述的电路模型转换成门级网表的过程。要完成一次综合过程,必须包含三要素:RTL级描述、约束条件和工艺库。 2.2 RTL级描述 RTL级描述是以规定设计中采用各种寄存器形式为特征,然后在寄存器之间插入组合逻辑,其可以用如图1所示的“寄存器和云图”方式来表示。 图1 RTL级描述 2.3 约束条件 为了控制优化输出和映射工艺要用约束,它为优化和映射试图满足的工艺约束提供了目标,并且它们控制设计的结构实现方式。目前综合工具中可用的约束包括面积、速度、功耗和可测性约束,未来我们或许会看到对封装的约束和对布图的约束等,但是,目前的最普遍的约束是按面积和按时间的约束。 时钟限制条件规定时钟的工作频率,面积限制条件规定该设计将花的最大面积。综合工具将试图用各种可能的规则和算法尽可能地满足这些条件。 2.4 工艺库 按照所希望的逻辑行为功能和有关的约束建立设计的网表时,工艺库持有综合工具必须的全部信息。工艺库含有允许综合进程为建立设计做正确选择的全部信息,工艺库不仅含有ASIC单元的逻辑功能,而且还有该单元的面积、单元输入到输出的定时关系、有关单元扇出的某种限制和对单元所需的定时检查。 51单片机串口通信及波特率设置 MCS-51单片机具有一个全双工的串行通信接口,能同时进行发送和接收。它可以作为UART(通用异步接收和发送器)使用,也可以作为同步的移位寄存器使用。 1. 数据缓冲寄存器SBUF SBUF是可以直接寻址的专用寄存器。物理上,它对应着两个寄存器,即一个发送寄存器一个接收寄存器,CPU写SBUF就是修改发送寄存器;读SBUF就是读接收寄存器。接收器是双缓冲的,以避免在接收下一帧数据之前,CPU未能及时的响应接收器的中断,没有把上一帧的数据读走而产生两帧数据重叠的问题。对于发送器,为了保持最大的传输速率,一般不需要双缓冲,因为发送时CPU是主动的,不会产生重叠问题。 2. 状态控制寄存器SCON SCON是一个逐位定义的8位寄存器,用于控制串行通信的方式选择、接收和发送,指示串口的状态,SCON即可以字节寻址也可以位寻址,字节地址98H,地址位为98H~9FH。它的各个位定义如下: MSB LSB SM0 SM1 SM2 REN TB8 RB8 TI RI SM0和SM1是串口的工作方式选择位,2个选择位对应4种工作方式,如下表,其中Fosc是振荡器的频率。 SM0 SM1 工作方式功能波特率 0 0 0 8位同步移位寄存器Fosc/12 0 1 1 10位UART 可变 1 0 2 11位UART Fosc/64或Fosc/32 1 1 3 11位UART 可变 SM2在工作方式2和3中是多机通信的使能位。在工作方式0中,SM2必须为0。在工作方式1中,若SM2=1且没有接收到有效的停止位,则接收中断标志位RI不会被激活。在工作方式2和3中若SM2=1且接收到的第9位数据(RB8)为0,则接收中断标志RB8不会被激活,若接收到的第9位数据(RB8)为1,则RI置位。此功能可用于多处理机通信。 REN为允许串行接收位,由软件置位或清除。置位时允许串行接收,清除时禁止串行接收。 TB8是工作方式2和3要发送的第9位数据。在许多通信协议中该位是奇偶位,可以按需要由软件置位或清除。在多处理机通信中,该位用于表示是地址帧还是数据帧。 RB8是工作方式2和3中接收到的第9位数据(例如是奇偶位或者地址/数据标识位),在工作方式1中若SM2=0,则RB8是已接收的停止位。在工作方式0中RB8不使用。 TI 为发送中断标志位,由硬件置位,软件清除。工作方式0中在发送第8位末尾由硬件置位;在其他工作方式时,在发送停止位开始时由硬件置位。TI=1时,申请中断。CPU 响应中断后,发送下一帧数据。在任何工作方式中都必须由软件清除TI。 RI为接收中断标志位,由硬件置位,软件清除。工作方式0中在接收第8位末尾由硬件置位;在其他工作方式时,在接收停止位的中间由硬件置位。RI=1时,申请中断,要求CPU取走数据。但在工作方式1中,SM2=1且未接收到有效的停止位时,不会对RI置位。在任何工作方式中都必须由软件清除RI。 系统复位时,SCON的所有位都被清除。 控制寄存器PCON也是一个逐位定义的8位寄存器,目前仅仅有几位有定义,如下所示:MSB LSB STM32单片机的串口通信波特率计算方法 1. 什么是波特率 不管是什么单片机,在使用串口通信的时候,有一个非常重要的参数:波特率。什么是波特率:波特率就是每秒传送的字节数。双方在传输数据的过程中,波特率一致,这是通讯成功的基本保障。下面以STM32单片机为例,讲解一下串口波特率的计算方法。 2. STM32波特率相关的寄存器 STM32单片机设置波特率的寄存器只有一个:USART_BRR寄存器,如下图所示。 该寄存器的有效位数为16位,前4位用于存放小数部分,后12位用于存放整数部分。将波特率算出来后,数值填入这个波特率就可以了。下面介绍如何计算。 3. 波特率计算方法 STM32的数据手册给出了计算方法,有一个公式,如下图所示: 在这个公式上,共有三个变量,其中两个我们是知道的,Fck和Tx/Rx波特率这两个是已知的,USARTDIV是未知的。通过该公式的描述可以看出如果使用USART1的话,那Fck 就是PCLK2=72MHz,否则就是PCLK1=36MHz,Tx/Rx波特率这个参数是已知的。只需要计算出USARTDIV的值赋值给USART_BRR寄存器就可以了。以115200为例,将公式变形后得到:USARTDIV = 72×1000000/(16×115200) = 39.0625。即将39.0625写入USART_BRR即可。 前文说过,USART_BRR的前4位存放小数部分,后12位存放整数部分。 那小数部分DIV_Fraction = 0.0625×16 = 1 = 0x01;那整数部分DIV_Mantissa = 39 = 0x27;那USART_BRR = 0X271; 数据手册给我们提供了一张数据表: 在这张数据表上,已经算出了常用的波特率值,我们可以拿来直接用。但是如果我们想把 波特率选择 在串行通讯中,收发双方的数据传送率(波特率)要有一定的约定。在8051串行口的四种工作方式中,方式0和2的波特率是固定的,而方式1和3的波特率是可变的,由定时器T1的溢出率控制。 方式0 方式0的波特率固定为主振频率的1/12。 方式2 方式2的波特率由PCON 中的选择位SMOD 来决定,可由下式表示: 波特率=2的SMOD 次方除以64再乘一个fosc,也就是当SMOD=1时,波特率为1/32fosc,当SMOD=0时,波特率为1/64fosc 3.方式1和方式3 定时器T1作为波特率发生器,其公式如下: 波特率=定时器T1溢出率 产生溢出所需的周期数/计数率T 132 2=溢出率T 1mod ?s 式中T1计数率取决于它工作在定时器状态还是计数器状态。当工作于定时器状态时,T1计数率为fosc/12;当工作于计数器状态时,T1计数率为外部输入频率,此频率应小于fosc/24。产生溢出所需周期与定时器T1的工作方式、T1的预置值有关。 定时器T1工作于方式0:溢出所需周期数=8192-x 定时器T1工作于方式1:溢出所需周期数=65536-x 定时器T1工作于方式2:溢出所需周期数=256-x 因为方式2为自动重装入初值的8位定时器/计数器模式,所以用它来做波特率发生器最恰当。 当时钟频率选用11.0592MHZ 时,取易获得标准的波特率,所以很多单片机系统选用这个看起来“怪”的晶振就是这个道理。 下表列出了定时器T1工作于方式2常用波特率及初值。 常用波特率 Fosc(MHZ) SMOD TH1初值 19200 11.0592 1 FDH 9600 11.0592 0 FDH 4800 11.0592 0 FAH 2400 11.0592 0 F4h 1200 11.0592 0 E8h 例如9600 11.0592 0 FDH 溢出率T 1定时时32 2 =波特率mod ?s T1溢出率= T1计数率/产生溢出所需的周期数 产生溢出所需的周期数=256-FD(253)=3 SMOD=0 11059200/12*3 *1/32=9600 RS-232接口引脚信号的定义 9针25针信号方向功能 3 2 TXD O 发送数据 2 3 RXD I 接收数据 7 4 RTS O 请求传送 8 5 CTS I 清除传送 6 6 DSR I 数据通信装置(DCE)准备就绪 5 7 SG 信号公共参考地 1 8 DCD I 数据载波检测 4 20 DTR O 数据终端设备(DTE)准备就绪 9 22 RI I 振铃指示 由于25针与9针连接器并无本质区别,因而容易实现相互转换,所以市场上25针到9针串行转接器都是无源的。 RS-232标准的电气特性参数 项目参数指标 带3~7千欧负载时驱动器的输出电平逻辑0为+3~+25V,逻辑1为-3~-25V 不带负载时驱动器的输出电平-25~+25V 驱动器通断时的输出阻抗>300欧 输出短路电流<0.5A 驱动器转换速率<30V/us 接收器输入阻抗3~7千欧 接收器输入电压-25~+25V 输入开路时接收器的输出逻辑 1 输入经300欧接地时接收器的输出逻辑 1 +3V输入时接收器的输出逻辑0 -3V输入时接收器的输出逻辑 1 最大负载电容2500pF 不能识别的过渡区-3V~+3V 单片机串行端口的工作方式 (1)方式0:8位移位寄存器输入/输出方式,多用于外接移位寄存器以扩展I/O端口,波特 率固定为fosc/12。(因此好像不需要进行串行口初始化,因为初始化的任务是设定波特率和数据传送方式,在这里已经都固定了)。 在方式0中,串行口作为输出时,只要向串行缓冲器SBUF写入一字节的数据后,串行端口就把此8位数据以fosc/12的波特率,从RXD引脚逐位输出(从低位到高位),(注意:只有在该情况下数据是由RXD输出!)TXD输出频率为fosc/12的同步移位脉冲,数据发送前,尽管不使用中断,中断标志TI还是必须置清0,8位数据发送完后,TI 自动置1,若要再发送,必须用软件将TI清0。 串行端口作为输入时,RXD为数据输入端,TXD仍为同步信号输出端,输出频率为fosc/12同步移位脉冲,使外部数据逐位移入RXD,当接收到8位数据后,中断标志RI 自动置1,若要再接收,必须用软件将RI清0。 (2)方式1(该方式应用最为广泛):10位异步通信方式,包括1个起始位(0电位)+8个数据位(从低位到高位)+1个停止位(1电位)。波特率由定时器T1的溢出率和SMOD 综合:不可综合的运算符:= = = ,!= =,/(除法),%(取余数)。 1、不使用初始化语句。 2、不使用带有延时的描述。 3、不使用循环次数不确定的循环语句,如:forever、while等。 4、尽量采用同步方式设计电路。 5、除非是关键路径的设计,一般不调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 6、用always过程块描述组合逻辑,应在信号敏感列表中列出所有的输入信号。 7、所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 8、在verilog模块中,任务(task)通常被综合成组合逻辑的形式,每个函数(function)在调用时通常也被综合为一个独立的组合电路模块。 9、用户自定义原语(UDP)是不可综合的,它只能用来建立门级元件的仿真模型。 一般综合工具支持的V erilog HDL结构 移位运算符:V erilog HDL提供向右(>>)及向左(<<)两种运算符,运算符高位或地位一旦移出即予丢弃,其空缺的位则予以补零。 连续赋值语句(assign)、case语句、if…else语句都是可以综合的 initial 语句内若包含有多个语句时,必须以begin end 作聚合;单一的初值赋值,因此并不需以begin end做聚合。 循环(Loops)并不能单独地在程序中存在,而必须在initial和always块中才能使用。initial过程块中的语句仅执行一次,而always块中的语句是不断重复执行的。 编写顶层模块的注意事项 每个端口除了要声明是输入、输出还是双向外,还要声明其数据类型,是连线型(wire)还是寄存器型(reg),如果没有声明则综合器默认为wire型。 1、输入和双向端口不能声明为寄存器型。 2、在测试模块中不需要定义端口。 编写testbentch所归纳的心得 CAN总线能够在一定的范围内容忍总线上CAN节点的通信波特率的偏差,这种机能使得CAN总线有很强的容错性,同时也降低了对每个节点的振荡器精度。 实际上,CAN总线的波特率是一个范围。假设定义的波特率是250KB/S,但是实际上根据对寄存器的设置,实际的波特率可能为200~300KB/S(具体值取决于寄存器的设置)。 在CAN的底层协议里将CAN数据的每一位时间(TBit)分为许多的时间段(Tscl),这些时间段包括: A.位同步时间(Tsync) B.时间段1(Tseg1) C.时间段2(Tseg2) 其中位同步时间占用1个Tscl;时间段2占用(Tseg1+1)个Tscl;时间段2占用(Tseg2+1)个Tscl,所以CAN控制器的位时间(TBit)就是: TBit=Tseg1+Tseg2+Tsync=(TSEG1+TSEG2+3)*Tscl CAN的波特率(CANbps)就是1/TBit。Tsync=1Tscl 但是这样计算出的值是一个理论值。在实际的网络通信中由于存在传输的延时、不同节点的晶体的误差等因素,使得网络CAN的波特率的计算变得复杂起来。CAN在技术上便引入了重同步的概念,以更好的解决这些问题。 这样重同步带来的结果就是要么时间段1(Tseg1)增加TSJW(同步跳转宽度SJW+1),要么时间段减少TSJW,因此CAN的波特率实际上有一个范围: 1/(Tbit+Tsjw) ≤CANbps≤1/(Tbit-Tsjw) CAN有波特率的值四以下几个元素决定: A.最小时间段Tscl; B.时间段1 TSEG1; C.时间段2 TSEG2; D.同步跳转宽度SJW SJW(重同步跳转宽度)决定了一次重同步期间一个位时间被延长或缩短的时间量子Tscl是通过总线时序寄存器设置计算的。 Tscl=(BRP+1)/FVBP。FVBP为微处理器的外设时钟。 而TSEG1与TSEG2又是怎么划分的呢?TSEG1与TSEG2的长度决定了CAN数据的采样点,这种方式允许宽范围的数据传输延迟和晶体的误差。其中TSEG1用来调整数据传输延迟时间造成的误差,而TSEG2则用来调整不同点节点晶体频率的误差。 TSEG1与TSEG2的是分大体遵循以下规则: Tseg1≥Tseg2≥2TSJW;Tseg2≥2Tscl 总的来说,对于CAN的波特率计算问题,把握一个大的方向就行了,其计算公式可了规结为: BitRate = Fpclk/( (BRP+1) * ((Tseg1+1)+(Tseg2+1)+1)) 《计算机网络名词解释》 1.计算机网络 计算机网络就是指,将分布在不同地理位置、具有独立功能的多台计算机及其外部设备,用通信设备和通信线路连接起来,在网络操作系统和通信协议及网络管理软件的管理协调下,实现资源共享、信息传递的系统。 2.通信链路 通信链路是指两个网络节点之间传输信息和数据的线路。 3.资源子网 资源子网提供访问网络和处理数据的能力,有主机系统、终端控制器和终端组成。 4.通信子网 通信子网是计算机网络中负责数据通信的部分,主要完成数据的传输、交换以及通信控制。它由网络节点、通信链路组成。 5.网络通信协议 网络通信协议就是实现网络协议规则和功能的软件,它运行在网络计算机和设备中,计算机通过使用通信协议访问网络。 6.数据通信的基本概念 数据通信是两个实体间的数据传输和交换,是通过各种不同的工作方式和传输介质,把处在不同地理位置的终端和计算机,或计算机与计算机连接起来,从而完成数据传输、信息交换和通信处理等任务。 7.信息 信息是对客观事物的反应,可以对物质形态、大小、结构、性能等全部或部分特性的描,也可以表示物质与外界的联系。 8.数据 信息可以用数字的形式表示,数字化的信息称为数据。数据是信息的载体,信息则是数据的在含义和解释。取连续值得数据称为模拟数据,取离散值得数据称为数字数据。 9.信道 信道是传送信号的一条通道,可以分为物理信道和逻辑信道。 10.物理信道 物理信道是指用来传送信号或数据的物理通路,有传输介质及其附属设备组成。 11.逻辑信道 逻辑信道也是指传输信息的一条通路,但在信号的收、发节点之间并不一定存在与之相对应的物理传输介质,而是在物理信道基础上,由节点设备部的来实现。 12.信道容量 信道容量是指信道传输信息的最大能力,通常用信息速率来表示。单位时间传送的比特数越多,则信息的传输能力就越大,表示信道容量越大。 13.比特率 比特率是一种数字信号的传输速率,它表示单位时间所传送的二进制代码的有效位数,单位用比特每秒(bps)或千比特每秒(kbps)表示。 14.波特率 波特率是一种调制速率,也称波形速率。在数据传输过程中,线路上每秒钟传送的波形个数 . . 1)所有综合工具都支持的结构: always,assign,begin,end,case,wire,tri,supply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 2)所有综合工具都不支持的结构: time,defparam,$finish,fork,join,initial,delays,UDP,wait。 3)有些工具支持有些工具不支持的结构: casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点: 1)不使用initial。 2)不使用#10。 3)不使用循环次数不确定的循环语句,如forever、while等。 4)不使用用户自定义原语(UDP元件)。 5)尽量使用同步方式设计电路。 6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对 51单片机波特率计算的公式和方法 51单片机芯片的串口可以工作在几个不同的工作模式下,其工作模式的设置就是使用SCON寄存器。它的各个位的具体定义如下: SM0SM1SM2REN TB8RB8TI RI SM0、SM1为串行口工作模式设置位,这样两位可以对应进行四种模式的设置。串行口工作模式设置。 波特率在使用串口做通讯时,一个很重要的参数就是波特率,只有上下位机的波特率一样时才可以进行正常通讯。波特率是指串行端口每秒内可以传输的波特位数。这里所指的波特率,如标准9600不是每秒种可以传送9600个字节,而是指每秒可以传送9600个二进位,而一个字节要8个二进位,如用串口模式1来传输那么加上起始位和停止位,每个数据字节就要占用10个二进位,9600波特率用模式1传输时,每秒传输的字节数是9600÷10=960字节。 51芯片的串口工作模式0的波特率是固定的,为fosc/12,以一个12M的晶振来计算,那么它的波特率可以达到1M。模式2的波特率是固定在fosc/64或fosc/32,具体用那一种就取决于PCON寄存器中的SMOD位,如SMOD为0,波特率为focs/64,SMOD为1,波特率为focs/32。 模式1和模式3的波特率是可变的,取决于定时器1或2(52芯片)的溢出速率,就是说定时器1每溢出一次,串口发送一次数据。那么我们怎么去计算这两个模式的波特率设置时相关的寄存器的值呢?可以用以下的公式去计算。 上式中如设置了PCON寄存器中的SMOD位为1时就可以把波特率提升2倍。通常会使用定时器1工作在定时器工作模式2下,这时定时值中的TL1做为计数,TH1做为自动重装值,这个定时模式下,定时器溢出后,TH1的值会自动装载到TL1,再次开始计数,这样可以不用软件去干预,使得定时更准确。在这个定时模式2下定时器1溢出速率的计算公式如下: 溢出速率=(计数速率)/(256-TH1初值) 溢出速率=fosc/[12*(256-TH1初值)] 上式中的“计数速率”与所使用的晶体振荡器频率有关,在51芯片中定时器启动后会在每一个机器周期使定时寄存器TH的值增加一,一个机器周期等于十二个振荡周期,所以可以得知51芯片的计数速率为晶体振荡器频率的1/12,一个12M的晶振用在51芯片上,那么51的计数速率就为1M。通常用11.0592M 晶体是为了得到标准的无误差的波特率,那么为何呢?计算一下就知道了。如我们要得到9600的波特率,晶振为11.0592M和12M,定时器1为模式2,SMOD 设为1,分别看看那所要求的TH1为何值。代入公式: 11.0592M 9600=(2÷32)×((11.0592M/12)/(256-TH1)) TH1=250 DVD导航仪端口和波特率大全,说不定能帮到你。 也是从网上下载下来的,借花献佛,希望对大家有所帮助。 不知道怎么上传附件,就全部拷贝复制上来吧。 也没怎么排版了,大家将就看吧。 DVD导航端口速率 导读:常见导航端口和速率表:附上一些800*480高清DVD导航一体机端口、波特率,供大家参考。1. 富威:COM2/4800 2. 索菱、索莱特:COM3/9600 3. 凯振:COM2/9600 4. 路特仕、图音:COM2/9600 5. 卡仕达、科骏达。 常见导航端口和速率表: 附上一些800*480高清DVD导航一体机端口、波特率,供大家参考。 1. 富威:COM2/4800 2. 索菱、索莱特:COM3/9600 3. 凯振:COM2/9600 4. 路特仕、图音:COM2/9600 5. 卡仕达、科骏达:COM6/4800或COM1/9600 6. 欧华:COM2/9600 7. 视宏:COM2/4800 8. 超音:COM2/9600 9. 凌盛:COM2/4800 10.佳艺田:COM2/9600 11.路畅:COM1/9600 12.飞韵:COM7/38400 13.科维:COM2/4800 14.飞歌:COM6/4800 15.道道全: COM2/4800 16.新星光:COM1/9600 17百事通;COM2/9600 本人收集了好久的,只是作为一个参考 常见品牌GPS导航端口速率汇总 车专用DVD品牌分辨率卡号端口号波特率 卡仕达320*240 CF_Storage COM6 4800 480*234 MMC_Storage COM6 4800 科骏达320*240 CF_Storage COM6 4800 480*234 MMC_Storage COM6 4800 华阳(派迅)416*234 存储卡COM2 9600 天派SDMMC COM1 4800 欧华320*240 StorageCard COM2 4800 科维320*240 StorageCard COM2 4800 城际通天籁专用420*240 CF_Storage COM6 4800 新奥迪A6L专用480*234 StorageCard COM2 4800 黑匣子导航盒320*240 StorageCard COM2 4800 Verilog的综合与不可综合 综合说明编的代码可以对应出具体的电路,不可综合说明没有对应的电路结构。不可综合的代码编译通过,只能看到输出,不能实现电路,就是不能用来制作具体的芯片。 一、基本 Verilog中的变量有线网类型和寄存器类型。线网型变量综合成wire,而寄存器可能综合成WIRE,锁存器和触发器。 二:verilog语句结构到门级的映射 1、连续性赋值:assign 连续性赋值语句逻辑结构上就是将等式右边的驱动左边的结点。因些连续性赋值的目标结点总是综合成由组合逻辑驱动的结点。Assign语句中的延时综合时都将忽视。 2、过程性赋值: 过程性赋值只出现在always语句中。 阻塞赋值和非阻塞赋值就该赋值本身是没有区别的,只是对后面的语句有不同的影响。 建议设计组合逻辑电路时用阻塞赋值,设计时序电路时用非阻塞赋值。 过程性赋值的赋值对象有可能综合成wire,latch,和flip-flop,取决于具体状况。如,时钟控制下的非阻塞赋值综合成flip-flop。 过程性赋值语句中的任何延时在综合时都将忽略。 建议同一个变量单一地使用阻塞或者非阻塞赋值。 3、逻辑操作符: 逻辑操作符对应于硬件中已有的逻辑门 4、算术操作符: Verilog中将reg视为无符号数,而integer视为有符号数。因此,进行有符号操作时使用integer,使用无符号操作时使用reg。 5、进位: 通常会将进行运算操作的结果比原操作数扩展一位,用来存放进位或者借位。如: Wire [3:0] A,B; Wire [4:0] C; Assign C=A+B; C的最高位用来存放进位。 6、关系运算符: 关系运算符:<,>,<=,>= 和算术操作符一样,可以进行有符号和无符号运算,取决于数据类型是reg,net还是integer。 串行通信波特率的一种自动检测方法 (哈尔滨工业大学控制工程系150001) 任贵勇屈彦成王常虹 摘要:给出了一种利用接收到的字符信息检测串行终端通信波特率的方法。此方法简单、可靠、易行,并给出了实现这种检测方法的伪代码。 关键词:自动检测;波特率 串行通信是终端和主机之间的主要通信方式,通信波特率一般选择1800、4800、9600和 19200等。终端的类型有很多种,其通信速率也有很多种选择。主机怎样确定终端的通信速率呢?本文给出了一种简单、易行的方法:设定主机的接收波特率(以9600波特为例),终端发送一个特定的字符(以回车符为例),主机根据接收到的字符信息就可以确定终端的通信波特率。本文对这种方法予以详述。 1 基本方法 回车符的ASCII值为0x0D。串行通信时附加一个起始位和终止位,位的传输顺序一般是先传低位再传高位。此时回车符的二进制表示方式为: 图1 回车符的位序列 串行通信中一个二进制位的传输时间(记为T)取决于通信的波特率,9600波特时一个二进制位的传输时间是19200波特时一个二进制位传输时间的两倍,即:2*T19200=T 9600。因此,9600波特时一个位的传输时间,19200波特时可以传输两个位。同样地,9600波特传输两个位的时间在4800波特时只能传送一个位。主机设定接收波特率为9600,终端只有也以9600波特发送的字符,主机才能正确地接收。发送波特率高于或低于9600都会使主机接收到的字符发生错误。接收波特率为9600,终端以不同的波特率发送回车符时,主机接收到的二进制序列如表1所示。 从表1中可以看出,除了19200和1800波特时两种特例情况,其他情形的二进制序列都是 9600波特时二进制序列的变换。取前十个二进制位与9600波特时的二进制位相对应。忽略缺少停止位‘1’引发的数据帧错误,把接收到的字符表示成字节方式(如表1的最右列所示)。例如:在发送速率为1200波特,接收速率为9600波特时,主机得到的字节是0x80,而不是正确的回车符0x0D。因为在不同的发送速率下(9600,4800,2400,1200)得到的字节不同,所以通过接收字符的判定就可以确定发送波特率。 发送波特率为19200时,其发送速度正好是接收速度(9600波特)的两倍,因此发送端的两个二进制位会被接收端看作一个。取决于不同的串行接口硬件,‘01’和‘10’这两种二进制位组合可能被认为是‘1’或者‘0’。幸运的是,只有0~4位存在这样的歧义问题,后面的位因为都是停止位,所以都是‘1’。因此,发送速率为19200波特时接收到的字符其高半个字节为0xF。低半个字节可能是多个值中的一个,但不会是0x0,因为0x0D中有相邻的两个‘1’,这就会至少在低半个字节中产生一个‘1’。因此,整个字节的形式为0xF?,且低半个字节不为0。 表1 不同波特率下的二进制序列 1)所有综合工具都支持的结构:always,assign,begin,end,case,wire,tri,aupply0,supply1,reg,integer,default,for,function,and,nand,or,nor,xor,xnor,buf,not,bufif0,bufif1,notif0,notif1,if,inout,input,instantitation,module,negedge,posedge,operators,output,parameter。 (2)所有综合工具都不支持的结构:time,defparam,$finish,fork,join,initial,delays,UDP,wait。 (3)有些工具支持有些工具不支持的结构:casex,casez,wand,triand,wor,trior,real,disable,forever,arrays,memories,repeat,task,while。 建立可综合模型的原则 要保证Verilog HDL赋值语句的可综合性,在建模时应注意以下要点:(1)不使用initial。 (2)不使用#10。 (3)不使用循环次数不确定的循环语句,如forever、while等。 (4)不使用用户自定义原语(UDP元件)。 (5)尽量使用同步方式设计电路。 (6)除非是关键路径的设计,一般不采用调用门级元件来描述设计的方法,建议采用行为语句来完成设计。 (7)用always过程块描述组合逻辑,应在敏感信号列表中列出所有的输入信号。 (8)所有的内部寄存器都应该能够被复位,在使用FPGA实现设计时,应尽量使用器件的全局复位端作为系统总的复位。 (9)对时序逻辑描述和建模,应尽量使用非阻塞赋值方式。对组合逻辑描述和建模,既可以用阻塞赋值,也可以用非阻塞赋值。但在同一个过程块中,最好不要同时用阻塞赋值和非阻塞赋值。 (10)不能在一个以上的always过程块中对同一个变量赋值。而对同一个赋值对象不能既使用阻塞式赋值,又使用非阻塞式赋值。 CAN波特率设置时的参数计算 CAN(Controller Area Network)总线最早由德国 BOSCH公司提出,主要用于汽车内部测量与控制中心之间的数据通信。由于其良好的性能,在世界范围内广泛应用于其他领域当中,如工业自动化、汽车电子、楼宇建筑、电梯网络、电力通讯和安防消防等诸多领域,并取逐渐成为这些行业的主要通讯手段。 Can 控制器器只需要进行少量的设置就可以进行通信,其中较难设置的部分就是通信波特率的计算。CAN总线能够在一定的范围内容忍总线上CAN节点的通信波特率的偏差,这种机能使得CAN总线有很强的容错性,同时也降低了对每个节点的振荡器精度。实际上,CAN总线的波特率是一个范围。假设定义的波特率是250KB/S,但是实际上根据对寄存器的设置,实际的波特率可能为200~300KB/S(具体值取决于寄存器的设置)。 CAN波特率设置时需要计算几个参数,这些参数共同决定波特率大小,由于计算比较复杂,希望有一个简易步骤,本人经过研究,找到一个简易办法,现贴出来分享,不对的地方请留言指正。需要说明的是,本人使用的can控制器是AT89C51CC03单片机中的can 首先,确定一下各项参数的取值范围: 参数范围编程值说明 BRP [1..64] 0-63 定义时间量子(时间份额)的长度tq Sync_Seg 1 tq 固定长度,总线输入与系统时钟同步 Prog_Seg [1..8]tq 0-7 补偿物理延时时间 Phase_Seg1 [1..8]tq 0-7 可通过同步暂时延长 Phase_Seg2 [1..8]tq 0-7 可通过同步暂时缩短 TSJW [1..4]tq 0-3 不能比任何一相位缓冲段长 以上是参数的取值范围,编程值是实际往寄存器里写的值,为实际取值减1。下面说一下步骤: 1、首先计算CAN时钟和波特率的比值; 2、根据比值确定预分频器的分频值BRP,计算时间量子的数目,这个数值范围是8-25; 3、将时间量子数减1(去掉Sync_Seg)后在Prog_Seg Phase_Seg1 Phase_Seg2三个参数中分配; 常见导航仪默认端口和波特率大全常见导航仪默认端口和波特率 1. 富威:COM2/4800 2. 索菱、索莱特:COM3/9600 3. 凯振:COM2/9600 4. 路特仕、图音:COM2/9600 5. 卡仕达、科骏达:COM1/9600或COM6/4800 6. 欧华:COM2/9600! 7.视宏:COM2/4800 8.超音:COM2/9600 9.凌盛:COM2/4800 10.佳艺田:COM2/9600 11.路畅:COM1/9600 常见品牌GPS导航端口速率汇总 常见品牌GPS导航端口速率汇总 车专用DVD品牌分辨率卡号端口号波特率 卡仕达 320*240 CF_Storage COM6 4800 480*234 MMC_Storage COM6 4800 科骏达320*240 CF_Storage COM6 4800 480*234 MMC_Storage COM6 4800 华阳(派迅) 416*234 存储卡COM2 9600 天派 SDMMC COM1 4800 欧华 320*240 Storage COM2 4800 科维320*240 Storage COM2 4800 城际通天籁专用420*240 CF_Storage COM6 4800 一线通新奥迪A6L480*234 Storage COM2 4800 黑匣子导航盒320*240 Storage COM2 4800 路特仕 800*480 Storage com1 9600 佳亿田320*240 Storage COM2 4800 途美A831、途美A837:com1 , 4800 途美A851、途美A852、途美A856:com2 , 4800 任E行Z10、Z20+、乐驾4300:com2 , 4800 依路行4302、4305、4306 :com2 , 4800 路驰com1 4800 HD500 com7 38400 奥可视T400、T410、T420等:com1 ,4800 神达C系列、乐游系列:com2 ,57600 神行者898、858、818:com2 ,4800 欧华com2 4800 新科com1 38400 纽曼com2 4800可综合的Verilog语法子集总汇

投影机串口控制码大全

基于VerilogHDL语言的可综合性设计

51单片机串口通信及波特率设置

STM32单片机的串口通信波特率计算方法

波特率计算

RS-232串行通讯大全

verilog综合心得

CAN波特率设置及寄存器设置

计算机网络技术 名词大全

verilog语句可综合vs不可综合

单片机波特率的计算方法

DVD导航仪端口和波特率集合

verilog语言的综合与不可综合

串口波特率自动检测

Verilog可综合与不可综合语句汇总

CAN波特率设置时的参数计算

常见导航仪默认端口和波特率大全