常用数字集成电路集锦

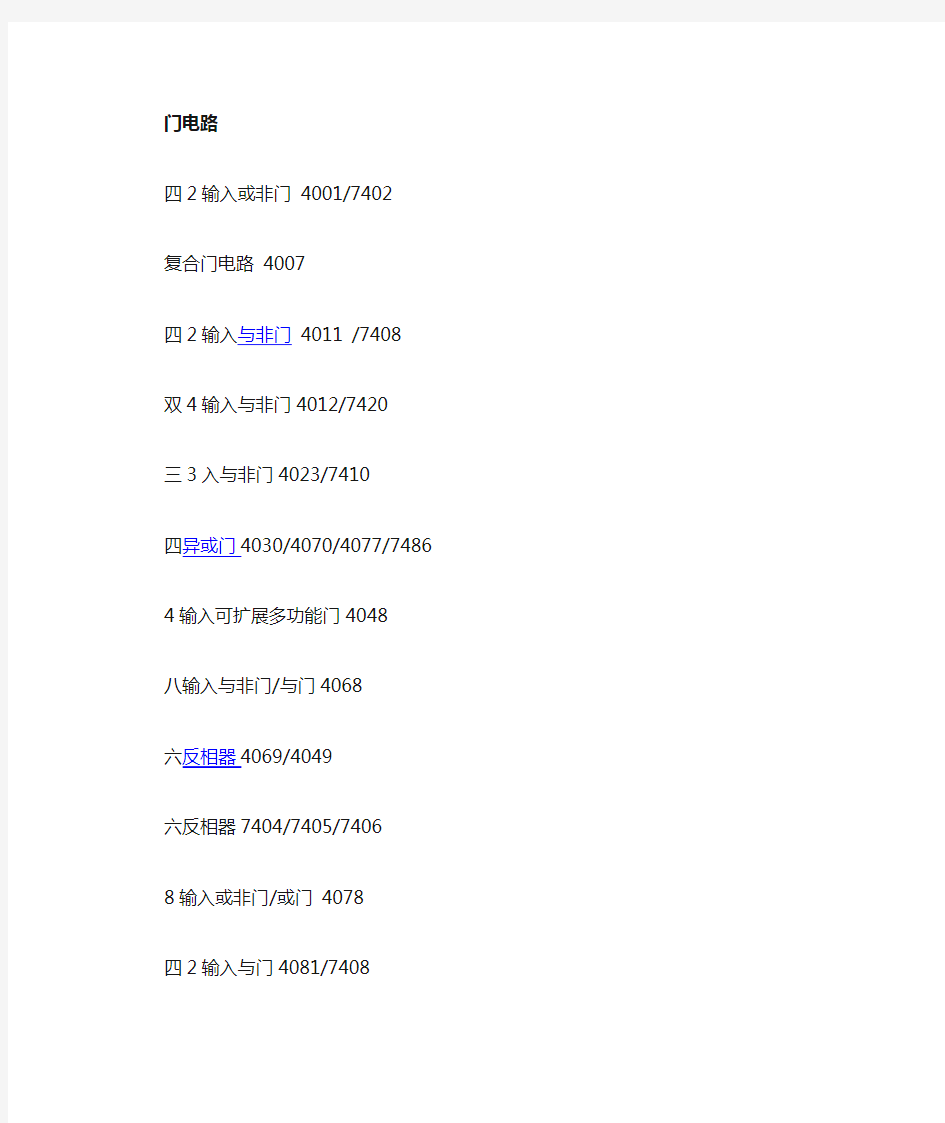

门电路

四2输入或非门 4001/7402

复合门电路 4007

四2输入与非门 4011 /7408

双4输入与非门4012/7420

三3入与非门4023/7410

四异或门4030/4070/4077/7486

4输入可扩展多功能门4048

八输入与非门/与门4068

六反相器4069/4049

六反相器7404/7405/7406

8输入或非门/或门 4078

四2输入与门4081/7408

双4输入与门4082/7421

其它 4085/4086/4530等

触发器

双主-从D型触发器4013/7474

双J-K触发器4027/74111~74114

四锁存D型触发器4042

4三态R-S锁存触发器4043

四2输入施密特触发器4093/40106

3输入端J-K触发器4095/4096

8位可寻址锁存器4099/4599

六锁存D型触发器40174/40175

双4位锁存D型触发器 4508

六锁存D型触发器74174/74175

8D锁存器74273/74373

时基延时分频电路

通用定时电路555

无稳态/单稳态多谐振荡器4047

“N”分频计数器4059

二进制比例乘法器 4089

24级分频器4521

BCD比例乘法器4527

单稳态多谐振荡器74121~74123

单稳态多谐振荡器74221

其它 MM5369/MN6041/MC14451

计数器

脉冲分配器/计数器 4017、4022

二进制串行计数器 4020、4024、4040、4060;74161、74162、74163;

可预置4位二进制/BCD加减计数器 4029

可预置4位BCD/二进制计数器40161、40162、40163;

可预置4位可逆计数器40192、40193;74190-74193

可预置4位可逆计数器4510、4516

双4 位BCD/二进制同步加计数器4518、4520

可预置同步1/N计数器 4522、4526

BCD计数器7490、74196

译码器

BCD-十进制译码器4028

BCD-7段译码/液晶驱动器4055/4056

BCD- 7段译码驱动器4511/4547

4线-16线译码器4514/4515/74154

BCD-七段锁存译码,驱动器4543/4544/4558

双二进制四选一译码器/分离器4555/4556

三位BCD计数器译码器4553

BCD-七段锁存译码,驱动器7447~7449

双二-四线译码器74139

BCD- 7段译码驱动器74141/74142

模拟开关数据选择器

四与或选择器4019

八选一模拟开关4051

双4选1模拟开关4052

三组二路模拟开关4053

四传输门4016/4066

16选1模拟开关4067

双路八选一模拟开关4097

八路数据选择器 4512

双四路/单八路模拟开关4529

寄存器

18位串入/串出移位寄存器4006

8位串入/并入-串出移位寄存器4014

双4位串入/并出移位寄存器4015

4位并入/串入-并出/串出移位寄存4035

4位并入/串入-并出/串出移位寄存40194/40195/74194/74195

4位移位寄存7494

运算电路

通用运算放大器LM324

4电压比较器LM393

4位超前进位全加器4008

4位数值比较器4585/4063

编码电路编译码配对电路

音调解码器LM567

8位优先编码器4532/74348

10-4线编码器40147/74147

8-8线优先编码器74147/74149

编译码配对电路MC145026/45027/45028/45030

编译码配对电路PT2262/2272

编译码配对电路PT2248/2249/2250

编译码配对电路VD5012/5013/5014

编译码配对电路VD5102/5103/5104

编译码配对电路VD5026/5027/5028

遥控电路

遥控配对电路BA5104/5204

遥控配对电路MC14457/14458

遥控配对电路TC9148/9149/9150

频率合成电路

锁相环频率合成4046

锁相环频率合成MC145152/45156

锁相环频率合成MC145146

点线显示驱动器LM3914/3915

大功率反相驱动器ULN2003

9011 NPN 30V 30mA 400mW 150MHz 放大倍数20-80 9012 PNP 50V 500mA 600mW 低频管放大倍数

30-90

9013 NPN 20V 625mA 500mW 低频管放大倍数

40-110

9014 NPN 45V 100mA 450mW 150MHz 放大倍数20-90

8050 NPN 25V 700mA 200mW 150MHz 放大倍数

30-100

8550 PNP 40V 1500mA 1000mW 200MHz 放大倍数40-140

详情如下:

90系列三极管参数

90系列三极管大多是以90字为开头的,但也有以ST90、C或A90、S90、SS90、UTC90开头的,它们的特性及管脚排列都是一样的。

9011 结构:NPN

集电极-发射极电压 30V

集电极-基电压 50V

射极-基极电压 5V

集电极电流 0.03A

耗散功率 0.4W

结温 150℃

特怔频率平均 370MHZ

放大倍数:D28-45 E39-60 F54-80 G72-108 H97-146 I132-198

9012 结构:PNP

集电极-发射极电压 -30V

集电极-基电压 -40V

射极-基极电压 -5V

集电极电流 0.5A

耗散功率 0.625W

结温 150℃

特怔频率最小 150MHZ

放大倍数:D64-91 E78-112 F96-135 G122-166 H144-220 I190-300

9013 结构:NPN

集电极-发射极电压 25V

集电极-基电压 45V

射极-基极电压 5V

集电极电流 0.5A

耗散功率 0.625W

结温 150℃

特怔频率最小 150MHZ

放大倍数:D64-91 E78-112 F96-135 G122-166 H144-220 I190-300

9014 结构:NPN

集电极-发射极电压 45V

集电极-基电压 50V

射极-基极电压 5V

集电极电流 0.1A

耗散功率 0.4W

结温 150℃

特怔频率最小 150MHZ

放大倍数:A60-150 B100-300 C200-600 D400-1000 9015 结构:PNP

集电极-发射极电压 -45V

集电极-基电压 -50V

射极-基极电压 -5V

集电极电流 0.1A

耗散功率 0.45W

结温 150℃

特怔频率平均 300MHZ

放大倍数:A60-150 B100-300 C200-600 D400-1000 9016 结构:NPN

集电极-发射极电压 20V

集电极-基电压 30V

射极-基极电压 5V

集电极电流 0.025A

耗散功率 0.4W

结温 150℃

特怔频率平均 620MHZ

放大倍数:D28-45 E39-60 F54-80 G72-108 H97-146 I132-198

9018 结构:NPN

集电极-发射极电压 15V

集电极-基电压 30V

射极-基极电压 5V

集电极电流 0.05A

耗散功率 0.4W

结温 150℃

特怔频率平均 620MHZ

放大倍数:D28-45 E39-60 F54-80 G72-108 H97-146 I132-198

三极管8550

8550是一种常用的普通三极管。

它是一种低电压,大电流,小信号的PNP型硅三极管

集电极-基极电压Vcbo:-40V

工作温度:-55℃ to +150℃

和8050(NPN)相对

主要用途:开关应用,射频放大

三极管8050

8050是常用的NPN小功率三级管,下面是的8050引脚图参数资料。

<8050管脚图>

8050三级管参数:类型:开关型; 极性:NPN; 材料:硅; 最大集存器电流(A):0.5 A; 直流电增益:10 to 60; 功耗:625 mW; 最大集存器发射电(VCEO):25; 频率:150 KHz

PE8050 硅 NPN 30V 1.5A 1.1W

3DG8050 硅 NPN 25V 1.5A FT=190 *K

2SC8050 硅 NPN 25V 1.5A FT=190 *K MC8050 硅 NPN 25V 700mA 200mW 150MHz CS8050 硅 NPN 25V 1.5A FT=190 *K

数字电路芯片大全资料

芯片大全 -- 74系列芯片资料(还算可以)! 74系列芯片资料 反相器驱动器 LS04 LS05 LS06 LS07 LS125 LS240 LS244 LS245 与门与非门 LS00 LS08 LS10 LS11 LS20 LS21 LS27 LS30 LS38 或门或非门与或非门 LS02 LS32 LS51 LS64 LS65 异或门比较器 LS86 译码器 LS138 LS139 寄存器 LS74 LS175 LS373 反相器: Vcc 6A 6Y 5A 5Y 4A 4Y 六非门74LS04 ┌┴─┴─┴─┴─┴─┴─┴┐六非门(OC门) 74LS05 _ │1413 12 11 10 9 8│六非门(OC高压输出) 74LS06 Y = A )│ │ 1 2 3 4 5 6 7│ └┬─┬─┬─┬─┬─┬─┬┘ 1A 1Y 2A 2Y 3A 3Y GND 驱动器: Vcc 6A 6Y 5A 5Y 4A 4Y ┌┴─┴─┴─┴─┴─┴─┴┐ │1413 12 11 10 9 8│ Y = A )│六驱动器(OC高压输出) 74LS07 │ 1 2 3 4 5 6 7│ └┬─┬─┬─┬─┬─┬─┬┘ 1A 1Y 2A 2Y 3A 3Y GND Vcc -4C 4A 4Y -3C 3A 3Y ┌┴─┴─┴─┴─┴─┴─┴┐ _ │1413 12 11 10 9 8│

Y =A+C )│四总线三态门 74LS125 │ 1 2 3 4 5 6 7│ └┬─┬─┬─┬─┬─┬─┬┘ -1C 1A 1Y -2C 2A 2Y GND Vcc -G B1 B2 B3 B4 B8 B6 B7 B8 ┌┴─┴─┴─┴─┴─┴─┴─┴─┴─┴┐8位总线驱动器 74LS245 │20 19 18 17 16 15 14 13 12 11│ )│DIR =1 A=>B │ 1 2 3 4 5 6 7 8 9 10│DIR=0 B=>A └┬─┬─┬─┬─┬─┬─┬─┬─┬─┬┘ DIR A1 A2 A3 A4 A5 A6 A7 A8 GND 页首非门,驱动器与门,与非门或门,或非门异或门,比较器译码器寄存器 正逻辑与门,与非门: Vcc 4B 4A 4Y 3B 3A 3Y ┌┴─┴─┴─┴─┴─┴─┴┐ │1413 12 11 10 9 8│ Y = AB )│2输入四正与门 74LS08 │ 1 2 3 4 5 6 7│ └┬─┬─┬─┬─┬─┬─┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 4B 4A 4Y 3B 3A 3Y ┌┴─┴─┴─┴─┴─┴─┴┐ __ │1413 12 11 10 9 8│ Y = AB )│2输入四正与非门 74LS00 │ 1 2 3 4 5 6 7│ └┬─┬─┬─┬─┬─┬─┬┘ 1A 1B 1Y 2A 2B 2Y GND Vcc 1C 1Y 3C 3B 3A 3Y ┌┴─┴─┴─┴─┴─┴─┴┐ ___ │1413 12 11 10 9 8│ Y = ABC )│3输入三正与非门 74LS10 │ 1 2 3 4 5 6 7│ └┬─┬─┬─┬─┬─┬─┬┘ 1A 1B 2A 2B 2C 2Y GND Vcc H G Y

常用数字芯片型号解读

常用数字芯片型号解读 逻辑电平有:TTL、CMOS、LVTTL、LVCMOS、ECL、PECL、LVDS、GTL、BTL、ETL、GTLP;RS232、RS422、RS485等。 图1-1:常用逻辑系列器件 TTL:Transistor-Transistor Logic CMOS:Complementary Metal Oxide Semicondutor LVTTL:Low Voltage TTL LVCMOS:Low Voltage CMOS ECL:Emitter Coupled Logic, PECL:Pseudo/Positive Emitter Coupled Logic LVDS:Low Voltage Differential Signaling GTL:Gunning Transceiver Logic BTL:Backplane Transceiver Logic ETL:enhanced transceiver logic GTLP:Gunning Transceiver Logic Plus TI的逻辑器件系列有:74、74HC、74AC、74LVC、74LVT等 S - Schottky Logic LS - Low-Power Schottky Logic CD4000 - CMOS Logic 4000 AS - Advanced Schottky Logic 74F - Fast Logic ALS - Advanced Low-Power Schottky Logic HC/HCT - High-Speed CMOS Logic BCT - BiCMOS Technology AC/ACT - Advanced CMOS Logic FCT - Fast CMOS Technology ABT - Advanced BiCMOS Technology LVT - Low-Voltage BiCMOS Technology LVC - Low Voltage CMOS Technology LV - Low-Voltage CBT - Crossbar Technology ALVC - Advanced Low-Voltage CMOS Technology AHC/AHCT - Advanced High-Speed CMOS CBTLV - Low-Voltage Crossbar Technology ALVT - Advanced Low-Voltage BiCMOS Technology AVC - Advanced Very-Low-Voltage CMOS Logic TTL器件和CMOS器件的逻辑电平 :逻辑电平的一些概念 要了解逻辑电平的内容,首先要知道以下几个概念的含义: 1:输入高电平(Vih):保证逻辑门的输入为高电平时所允许的最小输入高电平,当输入电平高于Vih时,则认为输入电平为高电平。 2:输入低电平(Vil):保证逻辑门的输入为低电平时所允许的最大输入低电平,当输入电平低于Vil时,则认为输入电平为低电平。 3:输出高电平(Voh):保证逻辑门的输出为高电平时的输出电平的最小值,逻辑门的输出为高电平时的

电子设计常用芯片

741 运算放大器 2063A JRC杜比降噪 20730 双功放 24C01AIPB21 存储器 27256 256K-EPROM 27512 512K-EPROM 2SK212 显示屏照明 3132V 32V三端稳压 3415D 双运放 3782M 音频功放 4013 双D触发器 4017 十进制计数器/脉冲分配器4021 游戏机手柄 4046 锁相环电路 4067 16通道模拟多路开关 4069 游戏机手柄 4093 四2输入施密特触发器 4098 41256 动态存储器 52432-01 可编程延时电路 56A245 开关电源 5G0401 声控IC 5G673 八位触摸互锁开关 5G673 触摸调光 5G673 电子开关 6116 静态RAM 6164 静态RAM 65840 单片数码卡拉OK变调处理器7107 数字万用表A/D转换器74123 单稳多谐振荡器 74164 移位寄存器 7474 双D触发器 7493 16分频计数器 74HC04 六反相器 74HC157 微机接口 74HC4053 74HCU04 六反相器 74LS00 与门 74LS00 4*2与非门 74LS00 四2与非门 74LS00 与门 74LS04 6*1非门 74LS08 4*2与门 74LS11 三与门 74LS123 双单稳多谐振荡器 74LS123 双单稳多谐振荡器 74LS138 三~八译码器 74LS142 十进制计数器/脉冲分配器74LS154 4-16线译码器 74LS157 四与或门74LS161 四2计数器 74LS161 十六进制同步计数器 74LS161 四~二计数器 74LS164 数码管驱动 74LS18 射频调制器 74LS193 加/减计数器 74LS193 四2进制计数器 74LS194 双向移位寄存器 74LS27 4*2或非门 74LS32 四或门 74LS32 4*2或门 74LS374 八位D触发器 74LS374 三态同相八D触发器 74LS377 74LS48 7位LED驱动 74LS73 双J-K触发器 74LS74 双D触发器 74LS85 四位比较器 74LS90 计数器 75140 线路接收器 75141 线路接收器 75142A 线路接收器 75143A 线路接收器 7555 时钟发生器 79MG 四端负稳压器 8051 空调单片机 8338 六反相器 A1011 降噪 ACVP2205-26 梳状滤波视频处理 AD536 专用运放 AD558 双极型8位D-A(含基准电压)变换器AD558 双极型8位D-A(含基准电压)变换器AD574A 12比特A/D变换器 AD650 AD670 8比特A/D变换器(单电源)1995s-2、15 AD7523 D-A变换器1994x-125 AD7524 D-A变换器1994x-126 AD7533 模数转换器1994x-141 AD7533 模数转换器1995s-184 ADC0804 8比特A/D变换器1995s-2、20 ADC0809 8CH8比特A/D 1995s-2、23 ADC0833 A/D变换4路转换器1995s-2 ADC80 12比特A/D变换器1995s-2、8 ADC84/85 高速12比特A/D变换器1995s-2 AG101 手掌游戏机1993x-155 AM6081 双极型8位D-A变换器1994x-127 AMP1200 音频功放皇后1993s-104 AN115 立体声解码1991-135 AN2510S 摄象机寻象器1994x-109 AN2661NK 影碟机视频1995s-45

数字集成电路总结

数字集成电路基础学习总结

第一章数字电子技术概念 1.1 数字电子技术和模拟电子技术的区别 模拟信号:在时间上和数值上均作连续变化的电路信号。 数字信号:表示数字量的信号,一般来说数字信号是在两个稳定状态之间作阶跃式变化的信号,它有电位型和脉冲型两种表达形式:用高低不同的电位信号表示数字“1”和“0”是电位型表示法;拥有无脉冲表示数字“1”和“0”是脉冲型表示法。 数字电路包括:脉冲电路、数字逻辑电路。数字电路的特点:1)小、轻、功耗低2)抗干扰力强3)精度高 按电路组成的结构可分立元件电路 集成电路 数数字电路分类 小规模 按集成度的大小来分中规模 大规模 超大规模 双极型电路 按构成电路的半导体器件来分 单极型电路 组合逻辑电路 按电路有记忆功能来分 1.2 1.3 三极管:是一种三极(发射极E、基极B(发射结、集电结)半导体器件,他有NPN和PNP两种,可工作在截止、放大、饱和三种工作状态。 电流公式:I(E)=I(B)+I(C) 放大状态:I(C)=βI(B) 饱和状态:I(C)< βI(B) 1.4 数制,两要素基数 权 二进制,十进制,十六进制之间的转换: 二进制转换成十进制:二进制可按权相加法转化成十进制。 十进制转换成二进制:任何十进制数正数的整数部分均可用除2取余法转换成二进制数。 二进制转化成八进制:三位一组分组转换。 二进制转换成十六进制:四位一组分组转换。 八进制转换成十六进制:以二进制为桥梁进行转换。 1.5 码制 十进制数的代码表示法常用以下几种:8421BCD码、5421BCD码、余3BCD码。 8421BCD码+0011=5421BCD码 第二章逻辑代数基础及基本逻辑门电路

数字电路常用芯片应用设计

74ls138 摘要: 74LS138 为3 -8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其中LS是指采用低功耗肖特基电路. 引脚图: 工作原理: 当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。 内部电路结构:

功能表真值表: 简单应用:

74ls139: 74LS139功能: 54/74LS139为2 线-4 线译码器,也可作数据分配器。其主要电特性的典型值如下:型号54LS139/74LS139 传递延迟时间22ns 功耗34mW 当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一个对应的输出端以低电平译出。若将选通端(G1)作为数据输入端时,139 还可作数据分配器。 74ls139引脚图:

引出端符号: A、B:译码地址输入端 G1、G2 :选通端(低电平有效) Y0~Y3:译码输出端(低电平有效74LS139内部逻辑图:

74LS139真值表: 74ls164: 164 为8 位移位寄存器,其主要电特性的典型值如下:54/74164 185mW 54/74LS164 80mW当清除端(CLEAR)为低电平时,输出端(QA -QH)均为低电平。串行数据输入端(A,B)可控制数据。当A、B任意一个为低电平,则禁止新数据输入,在时钟端(CLOCK)脉冲上升沿作用下Q0 为低电平。当A、B 有一个为高电平,则另一个就允许输入数据,并在CLOCK 上升沿作用下决定Q0 的状态。 引脚功能: CLOCK :时钟输入端CLEAR:同步清除输入端(低电平有效)A,B :串行数据输入端QA-QH:输出端 (图1 74LS164封装图)

数字集成电路复习资料

第一章 数字集成电路介绍 第一个晶体管,Bell 实验室,1947 第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。(随时间呈指数增长) 抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。这一模型含有用来在下一层次上处理这一模块所需要的所有信息。 固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。 可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。 一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。 一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。 理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。 传播延时、上升和下降时间的定义 传播延时tp 定义了它对输入端信号变化的响应有多快。它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。 上升和下降时间定义为在波形的10%和90%之间。 对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。功耗-延时积(PDP)----门的每次开关事件所消耗的能量。 一个理想的门应当快速且几乎不消耗能量,所以最后的质量评价为。能量-延时积(EDP) = 功耗-延时积2 。 第三章、第四章CMOS 器件 手工分析模型 ()0 12' 2 min min ≥???? ??=GT DS GT D V V V V V L W K I 若+-λ ()DSAT DS GT V V V V ,,m in min = 寄生简化:当导线很短,导线的截面很大时或当所采用的互连材料电阻率很低时,电感的影响可 以忽略:如果导线的电阻很大(例如截面很小的长 铝导线的情形);外加信号的上升和下降时间很 慢。 当导线很短,导线的截面很大时或当所采用的互 连材料电阻率很低时,采用只含电容的模型。 当相邻导线间的间距很大时或当导线只在一段很 短的距离上靠近在一起时:导线相互间的电容可 以被忽略,并且所有的寄生电容都可以模拟成接 地电容。 平行板电容:导线的宽度明显大于绝缘材料的厚度。 边缘场电容:这一模型把导线电容分成两部分:一个平板电容以及一个边缘电容,后者模拟成一条圆柱形导线,其直径等于该导线的厚度。 多层互连结构:每条导线并不只是与接地的衬底耦合(接地电容),而且也与处在同一层及处在相 邻层上的邻近导线耦合(连线间电容)。总之,再 多层互连结构中导线间的电容已成为主要因素。这一效应对于在较高互连层中的导线尤为显著, 因为这些导线离衬底更远。 例4.5与4.8表格 电压范围 集总RC 网络 分布RC 网络 0 → 50%(t p ) 0.69 RC 0.38 RC 0 → 63%(τ) RC 0.5 RC 10% → 90%(t r ) 2.2 RC 0.9 RC 0 → 90% 2.3 RC 1.0 RC 例4.1 金属导线电容 考虑一条布置在第一层铝上的10cm 长,1μm 宽的铝线,计算总的电容值。 平面(平行板)电容: ( 0.1×106 μm2 )×30aF/μm2 = 3pF 边缘电容: 2×( 0.1×106 μm )×40aF/μm = 8pF 总电容: 11pF 现假设第二条导线布置在第一条旁边,它们之间只相隔最小允许的距离,计算其耦合电 容。 耦合电容: C inter = ( 0.1×106 μm )×95 aF/μm2 = 9.5pF 材料选择:对于长互连线,铝是优先考虑的材料;多晶应当只用于局部互连;避免采用扩散导线;先进的工艺也提供硅化的多晶和扩散层 接触电阻:布线层之间的转接将给导线带来额外的电阻。 布线策略:尽可能地使信号线保持在同一层上并避免过多的接触或通孔;使接触孔较大可以降低接触电阻(电流集聚在实际中将限制接触孔的最大尺寸)。 采电流集聚限制R C , (最小尺寸):金属或多晶至n+、p+以及金属至多晶为 5 ~ 20 Ω ;通孔(金属至金属接触)为1 ~ 5 Ω 。 例4.2 金属线的电阻 考虑一条布置在第一层铝上的10cm 长,1μm 宽的铝线。假设铝层的薄层电阻为0.075Ω/□,计算导线的总电阻: R wire =0.075Ω/□′(0.1′106 μm)/(1μm)=7.5k Ω 例4.5 导线的集总电容模型 假设电源内阻为10k Ω的一个驱动器,用来驱动一条10cm 长,1μm 宽的Al1导线。 电压范围 集总RC 网络 分布RC 网络 0 → 50%(t p ) 0.69 RC 0.38 RC 0 → 63%(τ) RC 0.5 RC 10% → 90%(t r ) 2.2 RC 0.9 RC 0 → 90% 2.3 RC 1.0 RC 使用集总电容模型,源电阻R Driver =10 k Ω,总的集总电容C lumped =11 pF t 50% = 0.69 ′ 10 k Ω ′ 11pF = 76 ns t 90% = 2.2 ′ 10 k Ω ′ 11pF = 242 ns 例4.6 树结构网络的RC 延时 节点i 的Elmore 延时: τDi = R 1C 1 + R 1C 2 + (R 1+R 3) C 3 + (R 1+R 3) C 4 + (R 1+R 3+R i ) C i 例4.7 电阻-电容导线的时间常数 总长为L 的导线被分隔成完全相同的N 段,每段的长度为L/N 。因此每段的电阻和电容分别为rL/N 和cL/N R (= rL) 和C (= cL) 是这条导线总的集总电阻 和电容()()()N N RC N N N rcL Nrc rc rc N L DN 2121 (2222) +=+=+++??? ??=τ 结论:当N 值很大时,该模型趋于分布式rc 线;一条导线的延时是它长度L 的二次函数;分布rc 线的延时是按集总RC 模型预测的延时的一半. 2 rcL 22=RC DN =τ 例4.8 铝线的RC 延时.考虑长10cm 宽、1μm 的 Al1导线,使用分布RC 模型,c = 110 aF/μm 和r = 0.075 Ω/μm t p = 0.38′RC = 0.38 ′ (0.075 Ω/μm) ′ (110 aF/μm) ′ (105 μm)2 = 31.4 ns Poly :t p = 0.38 ′ (150 Ω/μm) ′ (88+2′54 aF/μm) ′ (105 μm)2 = 112 μs Al5: t p = 0.38 ′ (0.0375 Ω/μm) ′ (5.2+2′12 aF/μm) ′ (105 μm)2 = 4.2 ns 例4.9 RC 与集总C 假设驱动门被模拟成一个电压源,它具有一定大小的电源内阻R s 。 应用Elmore 公式,总传播延时: τD = R s C w + (R w C w )/2 = R s C w + 0.5r w c w L 2 及 t p = 0.69 R s C w + 0.38 R w C w 其中,R w = r w L ,C w = c w L 假设一个电源内阻为1k Ω的驱动器驱动一条1μm 宽的Al1导线,此时L crit 为 2.67cm 第五章CMOS 反相器 静态CMOS 的重要特性:电压摆幅等于电源电压 à 高噪声容限。逻辑电平与器件的相对尺寸无关 à 晶体管可以采用最小尺寸 à 无比逻辑。稳态时在输出和V dd 或GND 之间总存在一条具有有限电阻的通路 à 低输出阻抗 (k Ω) 。输入阻抗较高 (MOS 管的栅实际上是一个完全的绝缘体) à 稳态输入电流几乎为0。在稳态工作情况下电源线和地线之间没有直接的通路(即此时输入和输出保持不变) à 没有静态功率。传播延时是晶体管负载电容和电阻的函数。 门的响应时间是由通过电阻R p 充电电容C L (电阻R n 放电电容C L )所需要的时间决定的 。 开关阈值V M 定义为V in = V out 的点(在此区域由于V DS = V GS ,PMOS 和NMOS 总是饱和的) r 是什么:开关阈值取决于比值r ,它是PMOS 和NMOS 管相对驱动强度的比 DSATn n DSATp p DD M V k V k V V = ,r r 1r +≈ 一般希望V M = V DD /2 (可以使高低噪声容限具有相近的值),为此要求 r ≈ 1 例5.1 CMOS 反相器的开关阈值 通用0.25μm CMOS 工艺实现的一个CMOS 反相器的开关阈值处于电源电压的中点处。 所用工艺参数见表3.2。假设V DD = 2.5V ,最小尺寸器件的宽长比(W/L)n 为1.5 ()()()() ()()()() V V L W V V V V k V V V V k L W L W M p DSATp Tp M DSATp p DSATn Tn M DSATn n n p 25.125.55.15.35 .320.14.025.1263.043.025.10.163.01030101152266 ==?==----?-???----=---= 分析: V M 对于器件比值的变化相对来说是不敏感的。将比值设为3、2.5和2,产生的V M 分别为1.22V 、1.18V 和 1.13V ,因此使PMOS 管的宽度小于完全对称所要求的值是可以接受的。 增加PMOS 或NMOS 宽度使V M 移向V DD 或GND 。不对称的传输特性实际上在某些设计中是所希望的。 噪声容限:根据定义,V IH 和V IL 是dV out /dV in = -1(= 增益)时反相器的工作点 逐段线性近似V IH = V M - V M /g V IL = V M + (V DD - V M )/g 过渡区可以近似为一段直线,其增益等于在开关阈值V M 处的增益g 。它与V OH 及V OL 线的交点用来定义V IH 和V IL 。点。

常用数字集成电路管脚排列及逻辑符号

常用数字集成电路管脚排列及逻辑符号

图 D-1 74LS00 四 2 输入与非门

图 D-2 74LS01 四 2 输入与非门(OC)

图 D-3 74LS02 四 2 输入或非门

图 D-4 74LS04 六反相器

图 D-5 74LS08 四 2 输入与门

图 D-6 74LS10 三 3 输入与非门

图 D-7 74LS20 双 4 输入与非门

图 D-8

R

74LS32 四 2 输入或门

S

Q

S R Q

R Q S

R

S

Q

图 D-9 74LS54 4 路 2-2-2-2 输入与或非门

图 D-10 74LS74 双上升沿 D 型触发器

图 D-11 74LS86 四 2 输入异或门

图 D-12

74LS112 双下降沿 J-K 触发器

图 D-13 74LS126 四总线缓冲器

图 D-14

74LS138 3 线-8 线译码器

图 D-15 74LS148 8 线-3 线优先编码器

图 D-16 74LS151 8 选 1 数据选择器

图 D-17 74LS153 双 4 选 1 数据选择器

图 D-18 74LS161 4 位二进制同步计数器

图 D-19 74LS194 4 位双向移位寄存器

图 D-20 74LS196 二-五-十进制计数器

图 D-21 74LS283 4 位二进制超前进位全加器

图 D-22

74LS290 二-五-十进制计数器

图 D-23

CD4011B 四 2 输入与非门

图 D-24 CD4081 四 2 输入与门

数字电路知识点汇总(精华版)

数字电路知识点汇总(东南大学)第1章数字逻辑概论 一、进位计数制 1.十进制与二进制数的转换 c.分配律:) A? ?=+ B (C A? A C ?B A+ B + +) ? = C )() ) (C A B A 3)逻辑函数的特殊规律 a.同一律:A+A+A b.摩根定律:B A+ B ? A = A B A? = +,B

b.关于否定的性质A=A 二、逻辑函数的基本规则 代入规则 在任何一个逻辑等式中,如果将等式两边同时出现某一变量A的地方,都用一个函数L表示,则等式仍然成立,这个规则称为代入规则 B⊕ C A 解:先用摩根定理展开:AB=B A+再用吸收法 L=E AB+ + B A =E A+ + B + B D A =) A A+ D + + ( ) (E B B =) A A+ + D + ) 1( 1(E B B

=B A + 3)消去法 利用B A B A A +=+ 消去多余的因子 例如,化简函数L=ABC B A B A A +++ 解: L=ABC E B A B A B A +++ B A B A B A =)()()(BC A C B A C B A C B C B A B A +++?++? =)()1()1(B B C A A C B C B A +++++? =C A C B B A ++? 2.应用举例 将下列函数化简成最简的与-或表达式

1)L=A D DCE BD B A +++ 2) L=AC C B B A ++ 3) L=ABCD C B C A AB +++ 解:1)L=A D DCE BD B A +++ =DCE A B D B A +++)( A B B =)()(C B A C A ABCD C AB AB ++++ =)1()1(B C A CD C AB ++++ =C A AB + 四、逻辑函数的化简—卡诺图化简法: 卡诺图是由真值表转换而来的,在变量卡诺图中,变量的取值顺序是按循环码

常用基本数字集成电路应用设计

课程设计题目:常用基本数字集成电路应用设计 学生姓名: 学号: 院系: 专业班级: 指导教师姓名及职称: 起止时间: 课程设计评分: 常用基本数字集成电路应用设计 1.多谐振荡器概述 多谐振荡器是一种自激振荡器,它不需要输入触发信号,接通电源后就可自动输出矩形脉冲。由于矩形脉冲含有丰富的谐波分量,因此,常将矩形脉冲产生电路称为多谐振荡器。 1.1非门电路构成的多谐振荡器设计

1.1.1基本原理 门电路构成多谐振荡器 非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。电路的基本工作 原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。 (1)不对称多谐振荡器 非对称型多谐振荡器的输出波形是不对称的,当用TTL与非门组成时,输出脉冲宽度 tw1=RC, tw2=1.2RC, T=2.2RC 调节 R和C值,可改变输出信号的振荡频率,通常用改变C实现输出频率的粗调,改 变电位器R实现输出频率的细调。 图1为不对称多谐振荡器,为了使电路产生振荡,要求U1A和U1B两个反向器都工作在电压传输特性的转折区,即工作在放大区。 (2)对称型多谐振荡器 电路完全对称,电容器的充放电时间常数相同, 故输出为对称的方波。改变R和C的值, 可以改变输出振荡频率。非门3用于输出波形整形。 一般取R≤1KΩ?,当R1=R2=1KΩ,C1=C2=100pf~100μf时,f可在几Hz~MHz 变化。

脉冲宽度tw1=tw2=0.7RC,T=1.4RC. 图2中,U1A和U1B两个反向器之间经电容C1和C2耦合形成正反馈回路。 (3) 石英晶体稳频的多谐振荡器 当要求多谐振荡器的工作频率稳定性很高时,上述几种多谐振荡器的精度已不能满足要 求。为此常用石英晶体作为信号频率的基准。用石英晶体与门电路构成的多谐振荡器常用来 为微型计算机等提供时钟信号。 图3所示为常用的晶体稳频多谐振荡器。(a)、 (b)为TTL器件组成的晶体振荡电路;(c)、 (d)为CMOS器件组成的晶体振荡电路,一般用于电子表中,其中晶体的f0=32768Hz。 图3(c)中,门1用于振荡,门2用于缓冲整形。Rf是反馈电阻,通常在几十兆欧之 间选取,一般选22MΩ。R起稳定振荡作用,通常取十至几百千欧。C1是频率微调电容器, C2用于温度特性校正。

数字集成电路的分类

数字集成电路的分类 数字集成电路有多种分类方法,以下是几种常用的分类方法。 1.按结构工艺分 按结构工艺分类,数字集成电路可以分为厚膜集成电路、薄膜集成电路、混合集成电路、半导体集成电路四大类。图如下所示。 世界上生产最多、使用最多的为半导体集成电路。半导体数字集成电路(以下简称数字集成电路)主要分为TTL、CMOS、ECL三大类。 ECL、TTL为双极型集成电路,构成的基本元器件为双极型半导体器件,其主要特点是速度快、负载能力强,但功耗较大、集成度较低。双极型集成电路主要有TTL(Transistor-Transistor Logic)电路、ECL(Emitter Coupled Logic)电路和I2L(Integrated Injection Logic)电路等类型。其中TTL电路的性能价格比最佳,故应用最广泛。

ECL,即发射极耦合逻辑电路,也称电流开关型逻辑电路。它是利用运放原理通过晶体管射极耦合实现的门电路。在所有数字电路中,它工作速度最高,其平均延迟时间tpd可小至1ns。这种门电路输出阻抗低,负载能力强。它的主要缺点是抗干扰能力差,电路功耗大。 MOS电路为单极型集成电路,又称为MOS集成电路,它采用金属-氧化物半导体场效应管(Metal Oxide Semi-conductor Field Effect Transistor,缩写为MOSFET)制造,其主要特点是结构简单、制造方便、集成度高、功耗低,但速度较慢。MOS集成电路又分为PMOS(P-channel Metal Oxide Semiconductor,P沟道金属氧化物半导体)、NMOS(N-channel Metal Oxide Semiconductor,N沟道金属氧化物半导体)和CMOS(Complement Metal Oxide Semiconductor,复合互补金属氧化物半导体)等类型。 MOS电路中应用最广泛的为CMOS电路,CMOS数字电路中,应用最广泛的为4000、4500系列,它不但适用于通用逻辑电路的设计,而且综合性能也很好,它与TTL电路一起成为数字集成电路中两大主流产品。CMOS数字集成电路电路主要分为4000(4500系列)系列、54HC/74HC系列、54HCT/74HCT系列等,实际上这三大系列之间的引脚功能、排列顺序是相同的,只是某些参数不同而已。例如,74HC4017与CD4017为功能相同、引脚排列相同的电路,前者的工作速度高,工作电源电压低。4000系列中目前最常用的是B 系列,它采用了硅栅工艺和双缓冲输出结构。 Bi-CMOS是双极型CMOS(Bipolar-CMOS)电路的简称,这种门电路的特点是逻辑部分采用CMOS结构,输出级采用双极型三极管,因此兼有CMOS电路的低功耗和双极型电路输出阻抗低的优点。 (1)TTL类型 这类集成电路是以双极型晶体管(即通常所说的晶体管)为开关元件,输入级采用多发射极晶体管形式,开关放大电路也都是由晶体管构成,所以称为晶体管-晶体管-逻辑,即Transistor-Transistor-Logic,缩写为TTL。TTL电路在速度和功耗方面,都处于现代数字集成电路的中等水平。它的品种丰富、互换性强,一般均以74(民用)或54(军用)为型号前缀。 ①74LS系列(简称LS,LSTTL等)。这是现代TTL类型的主要应用产品系列,也是逻辑集成电路的重要产品之一。其主要特点是功耗低、品种多、价格便宜。 ②74S系列(简称S,STTL等)。这是TTL的高速型,也是目前应用较多的产品之一。

数字集成电路

数字集成电路专题研究 摘要:现在的电路可以分为两个方向,一个是数字,还有一个是模拟,在此更加偏重对数字方面的研究!全文一共可以分为两部分,一部分是基本的数字电路,还有一部分为较大型的集成电路。前一部分(基本数字电路)从认识数字电路开始,其间涉及到数字电路的分析方法---函数分析方法;在数字电路中分TTL 和COMS两种电路,在此报告中提到了这两种电路的电平比较关系。因COMS电路功耗低、工作电压范围宽、扇出能力强和售价低等优点,所以着重介绍一下CMOS 电路的常用特性,以及由它构成的一些常见的数字电路!而在后半部方介绍的是集成电路,从集成电路的分类到如何做好集成电路的设计;集成电路的设计分为前端和后端设计前端是指逻辑部分,后端是指物理层的设计.前端是设计内部的逻辑.后端是指假设逻辑设计已经完成,如何做出最后的芯片,涉及到芯片内部如何分区,如何布线,模拟部分,寄生效应等等.而由于专业方向这里又着重去讨论前端设计:系统集成芯片(SoC)的IC设计。同时收集了一些集成电路的设计工具。 关键字:数字电路函数表示 COMS集成电路常

见的数字电路集成电路分类 IC前端设计工具系统集成芯片SOC IC设计软件 VHDL/ Veriolg HDL 正文: 一.数字电路简介: 在电子设备中,通常把电路分为模拟电路和数字电路两类,前者涉及模拟信号,即连续变化的物理量,例如在24小时内某室内温度的变化量;后者涉及数字信号,即断续变化的物理量,开关K 快速通、断时,在电阻R 上就产生一连串的脉冲(电压),这就是数字信号。人们把用来传输、控制或变换数字信号的电子电路称为数字电路。数字电路工作时通常只有两种状态:高电位(又称高电平)或低电位(又称低电平)。通常把高电位用代码“1 ”表示,称为逻辑“1 ”;低电位用代码“0 ”表示,称为逻辑“0 ”(按正逻辑定义的)。注意:有关产品手册中常用“H ”代表“1 ”、“L ”代表“0 ”。实际的数字电路中,到底要求多高或多低的电位才能表示“1 ”或“0 ”,这要由具体的数字电路来定。例如一些TTL 数字电路的输出电压等于或小于0.2V,均可认为是逻辑“0 ”,等于或者大于3V,均可认为是逻辑“1 ”(即电路技术指标)。CMOS数字电路的逻辑“0 ”或“1 ”的电位值是与工作电压有关的。讨论数字电路

常用数字电路单元的结构

第3章常用数字单元电路结构 3.1 引言 本章介绍CMOS数字电路中常用单元电路的结构。本章暂不考虑电路性能问题,因此可将MOS管看成受电压控制的开关。 3.2 互补静态CMOS逻辑 互补静态逻辑是CMOS电路中最重要的逻辑系列,目前多数CMOS逻辑电路采用这种方法设计,其一般结构如图3-1。 互补静态逻辑的任何单元电路都是由一个连接VDD的pMOS上拉网络和一个连接GND的nMOS下拉网络构成。所谓互补关系指这样一种对应关系,在上拉网络中的PMOS管个数与下拉网络中NMOS管个数相等,且在nMOS网络中串联的晶体管,必须对应pMOS网络中的并联晶体管,nMOS网络中的并联晶体管必须对应pMOS网络中的串联晶体管。满足这种关系时,对于任何输入组合,必有一个网络导通,而另一个网络截止。这种CMOS逻辑门在输入稳定时,不会有从VDD到GND的电流,因此,其静态功耗很低,这是CMOS电路的主要优点。静态CMOS逻辑门的另一个重要优点是,在任何输入组合下,输出端或者通过pMOS网络上拉到VDD,或者通过nMOS网络下拉到GND,输出逻辑状态比较稳定,有较强的抗干扰能力。 3.1.1互补静态逻辑基本CMOS逻辑门

图3-2是一些基本的CMOS 逻辑门,可以看出,这些基本CMOS 门都符合互补关系。 互补静态CMOS 逻辑门的pMOS 网络和nMOS 网络的导通逻辑恰好相反,如果用F N 表示nMOS 网络的导通逻辑,F P 表示pMOS 网络的导通逻辑,则必须有 P N F F = (3-1) 例如,在与非门中, AB F N = AB B A F P =+= 整个门的逻辑关系与pMOS 网络的导通逻辑相同,但观察nMOS 网络的导通条件更容易些。这种关系也可以推广到更复杂的电路。 CMOS 逻辑门总是含有反相关系,nMOS 下拉网络总是在部分或全部输入为“1”时导通,从而使输出为“0”。对于任何互补CMOS 逻辑门,判断逻辑关系的方法是:根据nMOS 网络的导通逻辑,再加上“非”逻辑,就可以得到整个门的逻辑关系。 在互补静态CMOS 逻辑门中,只有反相器、与非门和或非门是最基本的逻辑门,而与门和或门要利用上述基本逻辑门实现,也就是说,一个与门的晶体管数相当于相同输入的与非门的晶体管数加2。

常用数字集成电路资料.

CD4000 双3输入端或非门+单非门TI CD4001 四2输入端或非门 HIT/NSC/TI/GOL CD4002 双4输入端或非门NSC CD4006 18位串入/串出移位寄存 器NSC CD4007 双互补对加反相器NSC CD4008 4位超前进位全加器NSC CD4009 六反相缓冲/变换器NSC CD4010 六同相缓冲/变换器NSC CD4011 四2输入端与非 门HIT/TI CD4012双4输入端与非门NSC CD4013双主-从D型触发器 FSC/NSC/TOS CD4014 8位串入/并入-串出移位寄存器NSC CD4015 双4位串入/并 出移位寄存器TI CD4016 四传输门FSC/TI CD4017 十进制计数/分配器 FSC/TI/MOT CD4018可预希9 1/N计数器NSC/MOT CD4019四与或选择器PHI CD4020 1 4级串行二进制计数/分频器FSC CD4021 08位串入/并入-串出移位寄存器 PHI/NSC CD4022 八进9计数/分配器NSC/MOT 型号器件名称厂牌备注CD4023 三3输入端与非门NSC/MOT/TI CD4024 7级二进制串行计数/分频器NSC/MOT/TI CD4025 三3输入端或非门NSC/MOT/TI CD4026 十进9计数/7段译码器 NSC/MOT/TI CD4027 双J-K 触发器NSC/MOT/TI CD4028 BCD 码十进制译码器 NSC/MOT/TI CD4029 可预置可逆计数器NSC/MOT/TI CD4030 四异或门 NSC/MOT/TI/GOL CD4031 64 位串入/串出移位存储器NSC/MOT/TI CD4032 三串行加法器NSC/TI CD4033 十进制计数/7段译码器NSC/TI CD4034 8位通用总线寄 存器NSC/MOT/TI CD4035 4 位并入/串入-并出/串出移位寄存NSC/MOT/TI CD4038 三串行加法器NSC/TI CD4040 12级二进制串行计数/分频器NSC/MOT/TI CD4041 四同相/反相缓冲器NSC/MOT/TI CD4042四锁存D型触发器NSC/MOT/TI CD4043 4三态R-S锁存触发器("1"触发NSC/MOT/TI CD4044四三态R-S锁存触发器("0"触 发NSC/MOT/TI CD4046 锁相环NSC/MOT/TI/PHI CD4047 无稳态/单稳态多谐振荡器NSC/MOT/TI 型号器件名称厂牌备注CD4048 4输入端可扩展多功能门 NSC/HIT/TI CD4049 六反相缓冲/变换器NSC/HIT/TI CD4050 六同相缓冲/变换器 NSC/MOT/TI CD4051 八选一模拟开关NSC/MOT/TI CD4052 双4选1模拟开关 NSC/MOT/TI CD4053 三组二路模拟开关NSC/MOT/TI CD4054 液晶显示驱动器 NSC/HIT/TI CD4055 BCD-7 段译码/液晶驱动器NSC/HIT/TI CD4056 液晶显示驱动器NSC/HIT/TI CD4059 “N分频计数器NSC/TI CD4060 14级二进制串行计数/分频 器NSC/TI/MOT CD4063 四位数字比较器NSC/HIT/TI CD4066 四传输门 NSC/TI/MOT CD4067 16 选1模拟开关NSC/TI CD4068 八输入端与非门/与门

常用数字集成电路管脚图

实验室提供的常用TTL 器件如下: 附录:常用数字集成电路管脚排列及逻辑符号 1A 1B 1Y 2A 2B 2Y 4A 4B 4Y 3A 3B 3Y GND V 图D-1 74LS00四2输入与非门 图D-2 74LS01四2输入与非门(OC ) 8 9 10 11 1 2 12 13 3 14 4 5 6 7 4Y GND 4A 5Y 6A 6Y 5A V CC 1A 1Y 2A 2Y 3A 3Y 。 1。 1 。 1 。 1 。 1 。 1 图D-3 74LS02四2输入或非门 图D-4 74LS04六反相器 8 910 11 121213 314 4567GND & & & & 1A 1B 1Y 2A 2B 2Y 4A 4B 4Y 3A 3B 3Y V CC 8 9 10 11 1212 13 314 4567 1C 1Y 3C 3B 3A 3Y 1A 1B 2A 2B 2C 2Y GND Vcc 。&&&。。 图D-5 74LS08四2输入与门 图D-6 74LS10三3输入与非门 8 9 10 11 1111 2 2 3 3 4 4 5 6 7 Vcc 2D 2C 2B 2A 2Y 1A 1B 1C 1D 1Y GND 。 &。 & N N 1A 1B 2Y 2A 2B 3Y 3A 3B 4Y 4A 4B GND V CC 8 9 10 11 1111 2 2 3 3 4 4 5 6 7 1Y 1 1 1 1 ≥≥≥≥ 图D-7 74LS20双4输入与非门 图D-8 74LS32四2输入或门

8 9 10 11 1212 13 314 45 6 7 ≥1 。 A C D E F N GND N N B H G Y V CC D R S D Q 2D R 1 1D 1CP 1 1Q 1 S D Q GND D Q CP 8 9 10 11 1111 2 2 3 3 4 4567 Q O O D Q CP Q O O D R D S D D R S Vcc 2 2D 2CP 2 2Q 图D-9 74LS54 4路2-2-2-2输入与或非门 图D-10 74LS74双上升沿D 型触发器 1A 1B 2Y 2A 2B 3Y 3A 3B 4Y 4A 4B GND V CC 8 9 10 11 1111 2 2 3 3 4 4 5 6 7 1Y =1 =1 =1 =1 9 10 11 1111 2 2 3 3 4 45678 115 6 Vcc D 2R D 22K 21J 22Q 1R CP CP 1K 1J S D 11Q 1Q 2Q GND K J CP D D Q Q R S S D 。 。 。。。 。 K CP J D R D S Q Q 图D-11 74LS86四2输入异或门 图D-12 74LS112双下降沿J-K 触发器 8 9 10 11 1 2 12 13 3 14 4 5 6 7 GND 1E 1A 1Y 2E 2A 2Y 4E 4A 4Y 3E 3A 3Y V CC EN 1EN 1 EN 1 EN 1 9 10 11 111122 3 3 4 4 5 6 7 8 115 6 Y 0 Vcc Y Y Y Y Y Y 1 2 3 4 5 6 S S Y GND 3 2 1 S A A A 012 7Y 0 Y Y Y Y Y 1 2 3 45 S S Y S A A 12 71 3 2 A 0 Y 6。 。 。 。 。 。 。 。 。 。 图D-13 74LS126四总线缓冲器 图D-14 74LS138 3线-8线译码器 9 10 11 1212 13 314 4567815 16 I 4。I 0 GND V CC I 5I 6I 7I 0 I 1 I 2 I 3 Y 0 Y 1Y 2Y S Y EX S I 1 I 2 I 3 I 4 I 5 I 6 I 7 Y 0 Y 1 Y 2 Y S Y EX S(E)。。。。。。 。。。。。。。 9 10 11 111122 3 3 4 4 5 6 7 8 115 6D 4V C C D D D A A A 56 7 1 2 GND D D D 321D 4D D D A A 56701D W D D 2 1 D 3A 2S ( E ) W S (E )D 0W W 。 。 图D-15 74LS148 8线-3线优先编码器 图D-16 74LS151 8选1数据选择器 9 10 11 1 2 12 13 314 45678 15 16 1D 3GND V CC 1D 21D 11D 0A 0 A 11W 2S 2D 3 2D 2 2D 1 2D 0 2W . . 。 。 A 0 2S 2D 32D 2 2D 1 2D 02W 1D 3 1D 2 1D 1 1D 0 A 11W A 0A 1 1S 9 10 11 12 13 123 14 45678 16 15 GND CR LD CP ENT O O Q CC Q 0Q 1Q 2 Q 3 D 0D 1 D 2D 3ENP D 0D 1D 2D 3ENP V CC Q CC Q 0 Q 1 Q 2 Q 3 ENT LD CP CR 图D-17 74LS153双4选1数据选择器 图D-18 74LS161 4位二进制同步计数器 9 10 11 1212 13 314 45678 15 16 CR GND V CC D SR M 1 CP Q 4 Q 3 M 0 D L D 4Q 1 Q 2 D 3D 2D 1CR Q Q Q Q CP 1 2 3 4 S 1 S 0 D SR D D D D D L 。 1 2 3 4 8 9 10 11 111122 3 34 45 6 7 CT/LD Qc C A QA V CC Q D D B Q B Cr QD Q B QB Qc C A QA CPB GND C r CP A CP B CT /LD CP A 。 。 。 图D-19 74LS194 4位双向移位寄存器 图D-20 74LS196二-五-十进制计数器