米勒效应分析

Mos 管米勒效应分析‐dengdexing

1、元器件参数 IRFBL3703

VDSS RDS(on) max ID 30V 0.0025? 260A

ID @ TC = 25°C,Continuous Drain Current, VGS @ 10V 260A ID @ TC = 100°C Continuous Drain Current, VGS @ 10V 180 dv/dt Peak Diode Recovery, 5.0 V/ns Ciss Input Capacitance ––– 8250pf Coss Output Capacitance ––– 3000pf

Crss Reverse Transfer Capacitance 10360pf Coss Output Capacitance 3060pf

其他参数请见IR 官网IRFBL3703datasheet 。

2、mos 门极灌电流(驱动源电压幅值)对驱动波形的影响

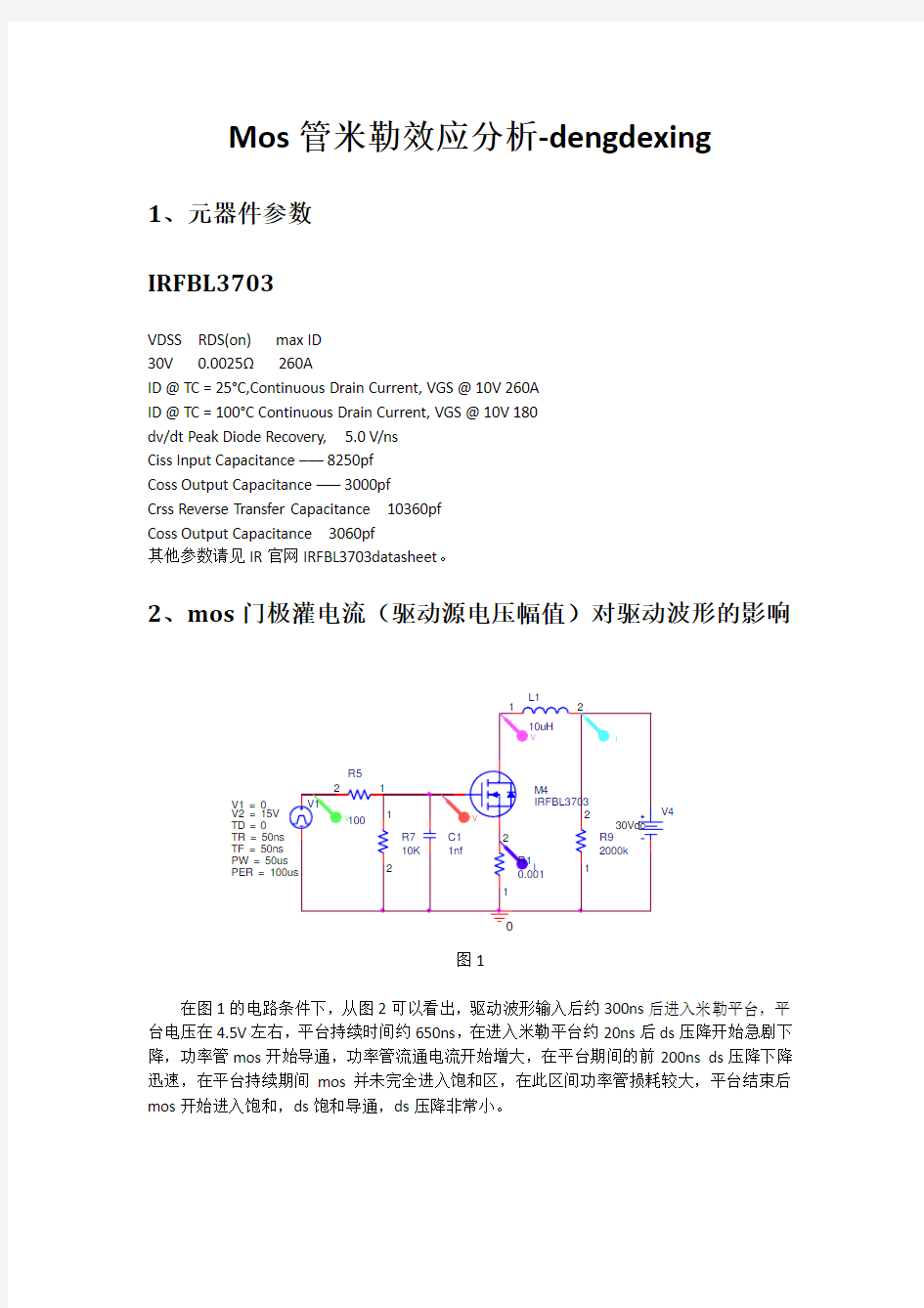

图1

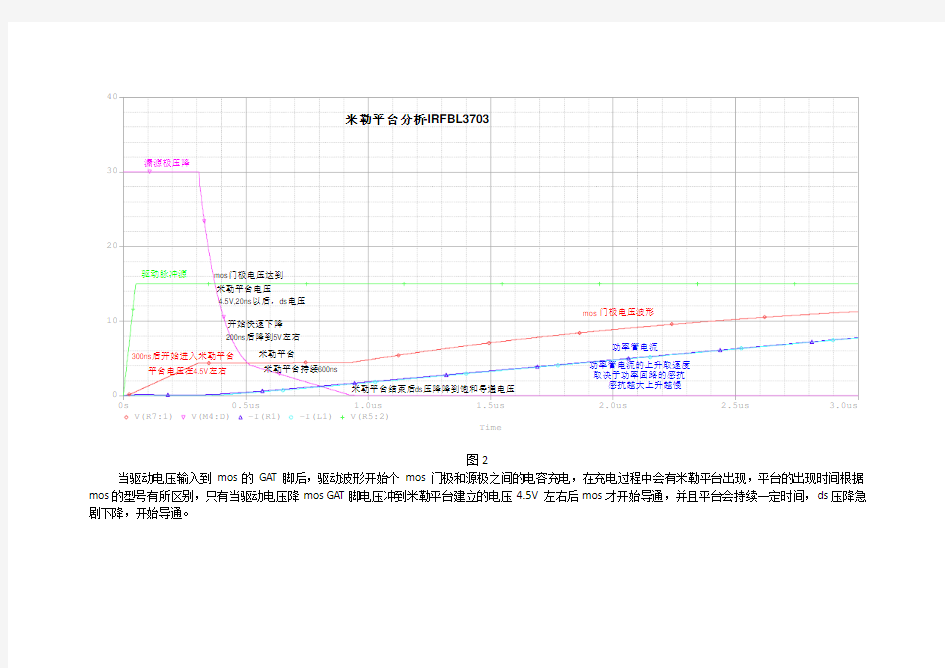

在图1的电路条件下,从图2可以看出,驱动波形输入后约300ns 后进入米勒平台,平台电压在4.5V 左右,平台持续时间约650ns ,在进入米勒平台约20ns 后ds 压降开始急剧下降,功率管mos 开始导通,功率管流通电流开始增大,在平台期间的前200ns ds 压降下降迅速,在平台持续期间mos 并未完全进入饱和区,在此区间功率管损耗较大,平台结束后mos 开始进入饱和,ds 饱和导通,ds 压降非常小。

TD = 0TF = 50ns PW = 50us V1 = 0TR = 50ns V2 = 15V L1

图2

当驱动电压输入到mos 的GAT 脚后,驱动波形开始个mos 门极和源极之间的电容充电,在充电过程中会有米勒平台出现,平台的出现时间根据mos 的型号有所区别,只有当驱动电压降mos GAT 脚电压冲到米勒平台建立的电压4.5V 左右后mos 才开始导通,并且平台会持续一定时间,ds 压降急剧下降,开始导通。

Time

0s

0.5us

1.0us 1.5us

2.0us 2.5us

3.0us

V(R7:1)

V(M4:D)

-I(R1)

-I(L1)

V(R5:2)

010

20

30

40

平台电压在4.5V 左右

300ns 后开始进入米勒平台

感抗越大上升越慢

取决于功率回路的感抗

功率管电流的上升取速度200ns 后降到5V 左右

米勒平台结束后ds 压降降到饱和导通电压

米勒平台持续600ns

开始快速下降

4.5V,20ns 以后,ds 电压

米勒平台电压

mos 门极电压达到

驱动脉冲源

米勒平台

功率管电流mos 门极电压波形

漏源极压降

米勒平台分析-IRFBL3703

图3

驱动PWM 波形幅值变为7V

图3较图1,驱动源幅值由15V 变为7V,mos 的充电电流也相应减少,从图4可以看出,300ns 后mos 门极开始进入米勒平台,ds 压降在进入米勒平台的20ns 左右急剧下降,功率管流过电流相应上升,平台持续时间约2600ns ,在进入平台的前800ns 的时间断ds 压降下降迅速,剩余平台时间段ds 电压下降较前一段较慢,米勒平台结束后ds 压降到达饱和压降电压。

TD = 0TF = 50ns PW = 50us V1 = 0TR = 50ns V2 = 7V L1

图4 米勒效应分析‐ GATE=7V

在此可以得到结论,充电电流的大小(驱动电压的幅值,当然驱动电阻的作用也是等效的,驱动电阻越小,驱动源灌入GATE 门极的电流越大)影响

到mos 管GATE 门极的上升速度,决定了ds 压降下降的速度,以及mos 管ds 电压应力的伏秒数。

Time

0s

1us

2us 3us

4us 5us 6us 7us 8us 9us 10us

V(M4:G)

V(M4:D)

-I(R1)

V(V1:+)

010

20

30

40

GATE=7V

IRFBL3703米勒效应分析2

驱动源,7V

3100ns 后到达饱和压降

电流波形

到达米勒平台

300ns 左右

平台持续时间600ns

米勒平台

门极驱动波形

ds 压降波形

图5 驱动电阻R5=10 ohm

上面有提到,在门极驱动源电压幅值不超过mos 的门极电压范围、驱动源供电能力充足的前提下,增加驱动源幅值同减小驱动电阻的作用类似,都可以增加单位时间灌入mos 门极电容的电流,从而减小mos 门极充电时间,缩短导通过程中ds 压降到饱和压降的时间,这样有利于降低在卡通过程中的损耗。图4中驱动电阻变为R5=10 ohm ,图6所示,在驱动信号到达的60ns 后就开始米勒效应,米勒平台宽度变为70ns ,米勒平台结束后,ds 压降下降到饱和导通电压附近。

TD = 0TF = 50ns PW = 50us V1 = 0TR = 50ns V2 = 15V L1

图6 mos 门极GATE=15V,R5=10 ohm

门极驱动电阻R5=10 ohm ,电流上升时间缩短,mos 米勒平台缩短,ds 压降下降更为迅速,功率管在驱动信号到来后迅速打开;同时功率管ds 电压应

力增加,参数设计尤其是需要软开关设计的场合时需要重点关注。

Time

0s

0.5us

1.0us

1.5us

2.0us

2.5us

3.0us

V(M4:G)

V(M4:D)

-I(R1)

V(V1:+)

010

20

30

40

电流波形

mos 门极

ds 漏源极电压

mos IRFBL3703米勒效应分析

驱动源15V,驱动电阻R5=10ohm

米勒平台

驱动源信号15V

Mos 管的开通过程实际上是电容的充电过程,充电的快慢由驱动和充电电容共同决定,时间参数τ=R*C ,尤其是包括mos 自身的Ciss 电容以及门极并联电容的充电,前边分析了驱动电阻对米勒平台以及mos 门极信号的影响。可以预见,充电电容的大小同样影响mos 驱动门极上升波形。如图7,C1=42nf 、图8为驱动波形.

图7 C1=42nf

TD = 0TF = 50ns PW = 50us V1 = 0TR = 50ns V2 = 15V L1

图8 C1=45nf 时驱动信号和ds 电压波形

Time

0s

0.5us

1.0us

1.5us

2.0us

2.5us

3.0us

V(M5:G)

V(M5:D)

-I(R1)

V(V1:+)

010

20

30

40

mos 驱动门极信号波形

电流波形

米勒平台

驱动源信号

ds 漏源极电压

3、总结

米勒效应或者米勒平台是mos本身固有的特性,mos管从外部电特性看,存在几个极间电容,门极和源极之间的Ciss电容,也叫输入电容,漏极和源极之间的Coss也叫输出电容,漏极与门极之间存在Crss电容习惯脚反馈电容。这几个等效电容的存在对mos驱动性能、开关速度,功率等级、开关损耗、效率分析直接相关,甚至关系到整个系统的性能。输入电容Ciss的存在以及习惯上在门极GATE和源极之间并联的外部输入电容,直接关系到开关速度,决定门极驱动信号的上升波形,由于两个输入电容的存在,当外部驱动源信号输入到mos的GATE极上时,mos管漏极和源极不会立即导通,所以此时ds压差很大,当输入电容被充电到特定程度后,驱动波形上出现一定时间的平台电压专业术语称之为米勒平台或米勒效应,常见的mos管米勒平台电压在4‐6V左右,在米勒平台未结束期间mos并未完全打开,只是部分打开,所以ds之间的电压只是在迅速下降,直到米勒效应结束,ds之间的导通阻抗降低到标称值的Rdson,ds压降下降到饱和压降值,功率管完全打开。米勒平台以及驱动波形上升的时间的长短还与外部驱动电路相关,同时mos自身的Ciss更是起决定作用,通常功率级别越大Rdson越小,Ciss越大,米勒平台和上升时间就越长,反之依然。

由于τ=R*C的原因,外部输入电阻通常叫做驱动电阻也影响米勒平台和驱动上升波形的快慢。

在米勒效应未结束期间,mos未完全打开,这里的特性同三极管的放大区域类似,功率损耗非常大,属于开关损耗的一部分,作为功率开关的mos,这当然是要尽量避免的。在允许的前提下,从前面的分析可知,可以减小驱动电阻或者提高驱动波形幅值,加快ds压差降低的速度,减小驱动波形在上升过程的损耗。另外方面,ds压差下降速度加快必然导致ds电压应力剧增,这将给mos选型以及EMC特性带来不利影响。

从驱动波形尤其是米勒效应的分析可知,在mos斩波设计参考中如BLDC驱动设计,全桥电源、逆变等功率电路设计中,驱动波形直接的决定了死区参数等,避开mos的损耗或误导通区间;此外米勒平台波形还决定了mos导通电流的时序关系,在大功率电路中流行的ZCS、ZVS软开关技术的实现也是必然要考虑到的。

MOS管的米勒效应-讲的很详细

米勒效应的影响: MOSFET的栅极驱动过程,可以简单的理解为驱动源对MOSFET的输入电容(主要是栅源极电容Cgs)的充放电过程;当Cgs达到门槛电压之后, MOSFET就会进入开通状态;当MOSFET开通后,Vds开始下降,Id开始上升,此时MOSFET进入饱和区;但由于米勒效应,Vgs会持续一段时间不再上升,此时Id已经达到最大,而Vds还在继续下降,直到米勒电容充满电,Vgs又上升到驱动电压的值,此时MOSFET进入电阻区,此时Vds彻底降下来,开通结束。 由于米勒电容阻止了Vgs的上升,从而也就阻止了Vds的下降,这样就会使损耗的时间加长。(Vgs上升,则导通电阻下降,从而Vds下降) 米勒效应在MOS驱动中臭名昭著,他是由MOS管的米勒电容引发的米勒效应,在MOS管开通过程中,GS电压上升到某一电压值后GS电压有一段稳定值,过后GS 电压又开始上升直至完全导通。为什么会有稳定值这段呢?因为,在MOS开通前,D极电压大于G极电压,MOS寄生电容Cgd储存的电量需要在其导通时注入G极与其中的电荷中和,因MOS完全导通后G极电压大于D极电压。米勒效应会严重增加MOS的开通损耗。(MOS管不能很快得进入开关状态) 所以就出现了所谓的图腾驱动!!选择MOS时,Cgd越小开通损耗就越小。米勒效应不可能完全消失。 MOSFET中的米勒平台实际上就是MOSFET处于“放大区”的典型标志 用用示波器测量GS电压,可以看到在电压上升过程中有一个平台或凹坑,这就是米勒平台。 米勒效应指在MOS管开通过程会产生米勒平台,原理如下。 理论上驱动电路在G级和S级之间加足够大的电容可以消除米勒效应。但此时开关时间会拖的很长。一般推荐值加0.1Ciess的电容值是有好处的。 下图中粗黑线中那个平缓部分就是米勒平台。

MOS管的米勒效应-讲的很详细讲解学习

M O S管的米勒效应-讲 的很详细

米勒效应的影响: MOSFET的栅极驱动过程,可以简单的理解为驱动源对MOSFET的输入电容(主要是栅源极电容Cgs)的充放电过程;当Cgs达到门槛电压之后, MOSFET就会进入开通状态;当MOSFET开通后,Vds开始下降,Id开始上升,此时MOSFET 进入饱和区;但由于米勒效应,Vgs会持续一段时间不再上升,此时Id已经达到最大,而Vds还在继续下降,直到米勒电容充满电,Vgs又上升到驱动电压的值,此时MOSFET进入电阻区,此时Vds彻底降下来,开通结束。 由于米勒电容阻止了Vgs的上升,从而也就阻止了Vds的下降,这样就会使损耗的时间加长。(Vgs上升,则导通电阻下降,从而Vds下降) 米勒效应在MOS驱动中臭名昭著,他是由MOS管的米勒电容引发的米勒效应,在MOS管开通过程中,GS电压上升到某一电压值后GS电压有一段稳定值,过后GS电压又开始上升直至完全导通。为什么会有稳定值这段呢?因为,在MOS 开通前,D极电压大于G极电压,MOS寄生电容Cgd储存的电量需要在其导通时注入G极与其中的电荷中和,因MOS完全导通后G极电压大于D极电压。米勒效应会严重增加MOS的开通损耗。(MOS管不能很快得进入开关状态)

所以就出现了所谓的图腾驱动!!选择MOS时,Cgd越小开通损耗就越小。米勒效应不可能完全消失。 MOSFET中的米勒平台实际上就是MOSFET处于“放大区”的典型标志 用用示波器测量GS电压,可以看到在电压上升过程中有一个平台或凹坑,这就是米勒平台。 米勒效应指在MOS管开通过程会产生米勒平台,原理如下。 理论上驱动电路在G级和S级之间加足够大的电容可以消除米勒效应。但此时开关时间会拖的很长。一般推荐值加0.1Ciess的电容值是有好处的。 下图中粗黑线中那个平缓部分就是米勒平台。

配合力的计算

配合力的计算 Griffing提出的双列杂交共有4种方法,其中以方法4最常用。 有5个亲本,即p=5,不包括自交和反交,共有组合数10个[a=p(p-1)/2],完全随机区组设计,3次重复(b=3)。 第一步,离差平方和的计算。 校正值: C=X2../ab =30= 总的 St=∑X2ijk-C =重复 Sb=∑X2..k/a –C =++/= 一般配合力 Sg=∑X2i../b(p-2)-4X2.../bp(p-2) =+1672+++992)/45 =特殊配合力 Ss=∑∑X2ij./b-∑./b(p-2)+ 2X2…/b(p-1)(p-2) =++++432++402+++/3-+1672++1222+992)/9+18= 机误 Se=St-Sb-Sg-Ss = 父本母本 ⒈⒉345 Xi..ⅠⅡⅢⅠⅡⅢⅠⅡⅢⅠⅡⅢⅠⅡⅢ

1101191110 21314161917151312167 3436 45357 54099和 第二步,方差分析 自由度平方和均方 重复b-1=2Mb= 一般配合 p-1Mg= 力 特殊配合 p(p-3)/2=5Ms= 力 试验误差(a-1)(b-1)=18Me= 第三步,遗传参数估算 σ2g =(Mg-Ms)/b(p-2)= σ2s =(Ms-Me)/b= 两种配合力的相对重要性比较如下: 一般配合力 σ2g /σ2g+σ2s =+=% 特殊配合力 σ2s /σ2g+σ2s =+= 一般配合力效应值计算如下:

g?=(pX i.– 2X..)/p(p-2) g1 =(5*/15= g2 =(5*/15= g3 =(5*/15= g4 =(5*/15= g5 =(5*33-196)/15= 特殊配合力效应值计算如下:S?=X ij–(X i.+/(p-2)+2X../(p-1)(p-2) S1*2 = +/3+98/6= S1*3 = +/3+98/6= S1*4 = +/3+98/6= S1*5 = 8-+33)/3+98/6= S2*3 = +/3+98/6= S2*4 = +/3+98/6= S2*5 = +33)/3+98/6= S3*4 = +/3+98/6= S3*5 = +33)/3+98/6= S4*5 = +33)/3+98/6=

MOS管的米勒效应

MOSFE的栅极驱动过程,可以简单的理解为驱动源对MOSFE的输入电容(主要是栅源极电容Cgs)的充放电过程;当Cgs达到门槛电压之后,MOSFET就会进入开通状态;当MOSFE开通后,Vds开始下降,Id开始上升,此时MOSFE进入饱和区;但由于米勒效应,Vgs会持续一段时间不再上升,此时Id已经达到最大,而Vds还在继续下降,直到米勒电容充满电,Vgs又上升到驱动电压的值,此时MOSFE进入电阻区,此时Vds 彻底降下来,开通结束。 由于米勒电容阻止了Vgs的上升,从而也就阻止了Vds的下降,这样就会使损耗的时间加长。(Vgs上升,则导通电阻下降,从而Vds下降) 米勒效应在MOS区动中臭名昭著,他是由MOST的米勒电容引发的米勒效应,在MOS?开通过程中,GS电压上升到某一电压值后GS电压有一段稳定值,过后GS 电压又开始上升直至完全导通。为什么会有稳定值这段呢?因为,在MOST通前,D极电压大于G极电压,MOS寄生电容Cgd储存的电量需要在其导通时注入G极与其中的电荷中和,因MOS完全导通后G极电压大于D极电压。米勒效应会严重增加MOS勺开通损耗。(MOST 不能很快得进入开关状态) 所以就出现了所谓的图腾驱动!!选择MOS时,Cgd越小开通损耗就越小。米勒效应不可能完全消失。 MOSFE中的米勒平台实际上就是MOSFE处于“放大区”的典型标志 用用示波器测量GS电压,可以看到在电压上升过程中有一个平台或凹坑,这就是米勒平台。 米勒效应指在MOST开通过程会产生米勒平台,原理如下。 理论上驱动电路在G级和S级之间加足够大的电容可以消除米勒效应。但此时开关时间会拖的很长。一般推荐值加的电容值是有好处的。 下图中粗黑线中那个平缓部分就是米勒平台。 删荷系数的这张图在第一个转折点处:Vds开始导通。Vds的变化通过Cgd和驱动源的

功率MOS管烧毁的原因(米勒效应)

mos在控制器电路中的工作状态:开通过程(由截止到导通的过渡过程)、导通状态、关断过程(由导通到截止的过渡过程)、截止状态。 Mos主要损耗也对应这几个状态,开关损耗(开通过程和关断过程),导通损耗,截止损耗(漏电流引起的,这个忽略不计),还有雪崩能量损耗。只要把这些损耗控制在mos承受规格之内,mos即会正常工作,超出承受范围,即发生损坏。而开关损耗往往大于导通状态损耗(不同mos这个差距可能很大。 Mos损坏主要原因: 过流----------持续大电流或瞬间超大电流引起的结温过高而烧毁; 过压----------源漏过压击穿、源栅极过压击穿; 静电----------静电击穿。CMOS电路都怕静电; Mos开关原理(简要)。Mos是电压驱动型器件,只要栅极和源级间给一个适当电压,源级和漏级间通路就形成。这个电流通路的电阻被成为mos内阻,就是导通电阻

配合力在作物育种上的应用

配合力在作物育种上的应用 摘要配合力是指因交配组合不同表现了子代的差异,进而表明不同亲本间有不同的组合能力。它分为一般配合力和特殊配合力。配合力重要的意义在于配制杂交组合时对亲本的选配,应在亲本性状的一般配合力高的基础上,选用有较大的特殊配合力方差的亲本。特殊配合力的轮回选择对群体改良有效。配合力也受到环境的影响。 关键词配合力;亲本选配;轮回选择;环境 作物育种的目的是获得优良目标性状的基因型,在现代育种中,获得较大的遗传变异和较准确地识别优良基因型是达到这一目的的两大主要环节。杂交是培育良种的主要手段,而杂交育种成败的重要因素之一是亲本品种的选择。多年来的杂交试验表明,亲本本身的表现与其后代的表现并不一致,有些亲本本身表现很好,但所产生的杂交后代并不理想;而有些亲本本身并不优越,但能从它们杂交后代分离出很优良的个体或组合。因此,优良品种并不一定是优良的亲本。这样因亲本交配组合不同表现了子代的差异,进而表明不同亲本间有不同的组合能力,这种能力被称为配合力,它是杂交组合中亲本各性状配合能力的一个指标。1942年,Sprague 和Tatum根据对玉米数量性状的研究和杂交育种的实践,提出了一般配合力的概念,发展到现在,配合力的应用早已不仅仅局限在玉米上,而是推广到其他任何一种授粉方式的作物上和各种性状上,应用配合力选配亲本组合不仅能在较早世代就能初步鉴定出组合和亲本的优劣,而且还可以大大缩小我们处理材料的范围和时间,从而大大提高育种效率。 1 应用配合力分析、判断能否利用杂种优势育种 对配合力进行差异显著性测验,可以预测该作物是否可采用杂交优势育种。这种判断一般只应用在刚开展或尚未开展杂优育种的作物上(已大量开展杂优育种的作物上该项早已获得证明),以萝卜为例,在生产上大多采用品种,近年来,为了提高它的育种效率,增加组合选配的预见性,对其亲本系及轮配组合的维生素C、还原糖、淀粉酶等生化指标进行了测定,结果表明亲本系的维生素C、淀粉酶的一般配合力差异极显著,组合间维生素C、淀粉酶、还原糖含量的特殊配合差异极显著,上述3个指标的正反交效应差异并不显著。因此认为,在萝卜优质育种上,采取杂种优势育种是可行的,目前已有很多高产优质的萝卜杂交种产生。 2 配合力应用于优势组合的选配 关于配合力分析进行优势组合的选择,近年来进展较大,几乎所有作物上都

MOS管的米勒效应 讲的很详细

米勒效应的影响:(主要的输入电容可以简单的理解为驱动源对MOSFETMOSFET 的栅极驱动过程,就会进达到门槛电压之后, MOSFET是栅源极电容Cgs)的充放电过程;当Cgs进开始上升,此时MOSFET开通后,Vds开始下降,Id入开通状态;当MOSFET已经达到会持续一段时间不再上升,此时Id入饱和区;但由于米勒效应,Vgs又上升到驱动电压的值,直到米勒电容充满电,Vgs而Vds还在继续下降,最大,Vds彻底降下来,开通结束。此时MOSFET进入电阻区,此时的下降,这样就会使损Vds由于米勒电容阻止了Vgs的上升,从而也就阻止了下降)Vgs上升,则导通电阻下降,从而Vds耗的时间加长。 ( 在管的米勒电容引发的米勒效应,他是由MOS米勒效应在MOS驱动中臭名昭著,GS电压有一段稳定值,过后电压上升到某一电压值后GSMOS管开通过程中,GS 开通前,在为什么会有稳定值这段呢?因为,MOS电压又开始上升直至完全导通。极储存的电量需要在其导通时注入G极电压,MOS寄生电容CgdD极电压大于G。米勒效应会严极电压G完全导通后极电压大于D与其中的电荷中和,因MOS管 不能很快得进入开关状态)的开通损耗。(MOS重增加MOS越小开通损耗就越小。米勒CgdMOS时,所以就出现了所谓的图腾驱动!!选择效应不可能完全消失。MOSFET处于“放大区”的典型标志MOSFET中的米勒平台实际上就是电压,可以看到在电压上升过程中有一个平台或凹坑,这就GS用用示波器测量是米勒平台。管开通过程会产生米勒平台,原理如下。MOS米勒效应指在但此时开级之间加 足够大的电容可以消除米勒效应。G级和S理论上驱动电路在的电容值是有好 处的。关时间会拖的很长。一般推荐值加0.1Ciess 下图中粗黑线中那个平缓部分就是米勒平 台。.

MOS管的米勒效应-讲的很详细

创作编号:BG7531400019813488897SX 创作者:别如克* 米勒效应的影响: MOSFET的栅极驱动过程,可以简单的理解为驱动源对MOSFET的输入电容(主要是栅源极电容Cgs)的充放电过程;当Cgs达到门槛电压之后,MOSFET就会进入开通状态;当MOSFET开通后,Vds开始下降,Id开始上升,此时MOSFET进入饱和区;但由于米勒效应,Vgs会持续一段时间不再上升,此时Id已经达到最大,而Vds还在继续下降,直到米勒电容充满电,Vgs又上升到驱动电压的值,此时MOSFET进入电阻区,此时Vds彻底降下来,开通结束。 由于米勒电容阻止了Vgs的上升,从而也就阻止了Vds的下降,这样就会使损耗的时间加长。(Vgs上升,则导通电阻下降,从而Vds下降) 米勒效应在MOS驱动中臭名昭著,他是由MOS管的米勒电容引发的米勒效应,在MOS管开通过程中,GS电压上升到某一电压值后GS电压有一段稳定值,过后GS电压又开始上升直至完全导通。为什么会有稳定值这段呢?因为,在MOS开通前,D极电压大于G极电压,MOS寄生电容Cgd储存的电量需要在其导通时注入G极与其中的电荷中和,因MOS完全导通后G极电压大于D极电压。米勒效应会严重增加MOS的开通损耗。(MOS管不能很快得进入开关状态) 所以就出现了所谓的图腾驱动!!选择MOS时,Cgd越小开通损耗就越小。米勒效应不可能完全消失。 MOSFET中的米勒平台实际上就是MOSFET处于“放大区”的典型标志 用用示波器测量GS电压,可以看到在电压上升过程中有一个平台或凹坑,

这就是米勒平台。 米勒效应指在MOS管开通过程会产生米勒平台,原理如下。 理论上驱动电路在G级和S级之间加足够大的电容可以消除米勒效应。但此时开关时间会拖的很长。一般推荐值加0.1Ciess的电容值是有好处的。下图中粗黑线中那个平缓部分就是米勒平台。 删荷系数的这张图在第一个转折点处:Vds开始导通。Vds的变化通过Cgd 和驱动源的内阻形成一个微分。因为Vds近似线性下降,线性的微分是个常数,从而在Vgs处产生一个平台。 米勒平台是由于mos 的g d 两端的电容引起的,即mos datasheet里的Crss 。 这个过程是给Cgd充电,所以Vgs变化很小,当Cgd充到Vgs水平的时候,Vgs才开始继续上升。 Cgd在mos刚开通的时候,通过mos快速放电,然后被驱动电压反向充电,分担了驱动电流,使得Cgs上的电压上升变缓,出现平台

米勒效应会对MOSFET管造成怎样的影响

米勒效应会对MOSFET管造成怎样的影响 米勒平台形成的基本原理 MOSFET的栅极驱动过程,可以简单的理解为驱动源对MOSFET的输入电容(主要是栅源极电容Cgs)的充放电过程;当Cgs达到门槛电压之后,MOSFET就会进入开通状态;当MOSFET开通后,Vds开始下降,Id开始上升,此时MOSFET进入饱和区;但由于米勒效应,Vgs会持续一段时间不再上升,此时Id已经达到最大,而Vds还在继续下降,直到米勒电容充满电,Vgs又上升到驱动电压的值,此时MOSFET进入电阻区,此时Vds 彻底降下来,开通结束。 由于米勒电容阻止了Vgs的上升,从而也就阻止了Vds的下降,这样就会使损耗的时间加长。(Vgs上升,则导通电阻下降,从而Vds下降) 米勒效应在MOS驱动中臭名昭著,他是由MOS管的米勒电容引发的米勒效应,在MOS 管开通过程中,GS电压上升到某一电压值后GS电压有一段稳定值,过后GS电压又开始上升直至完全导通。为什么会有稳定值这段呢?因为,在MOS开通前,D极电压大于G 极电压,MOS寄生电容Cgd储存的电量需要在其导通时注入G极与其中的电荷中和,因MOS完全导通后G极电压大于D极电压。米勒效应会严重增加MOS的开通损耗。(MOS 管不能很快得进入开关状态) 所以就出现了所谓的图腾驱动!!选择MOS时,Cgd越小开通损耗就越小。米勒效应不可能完全消失。 MOSFET中的米勒平台实际上就是MOSFET处于“放大区”的典型标志。 用用示波器测量GS电压,可以看到在电压上升过程中有一个平台或凹坑,这就是米勒平台。 米勒平台形成的详细过程 米勒效应指在MOS管开通过程会产生米勒平台,原理如下。 理论上驱动电路在G级和S级之间加足够大的电容可以消除米勒效应。但此时开关时间

如何减轻米勒电容所引起的寄生导通效应

如何减轻米勒电容所引起的寄生导通效应 当IGBT在开关时普遍会遇到的一个问题即寄生米勒电容开通期间的米勒平台。米勒效应在单电源门极驱动的应用中影响是很明显的。基于门极G与集电极C之间的耦合,在IGBT关断期间会产生一个很高的瞬态dv/dt,这样会引发门极VGE间电压升高而导通,这是一个潜在的风险(如图1)。 图1:下管IGBT因为寄生米勒电容而引起导通 寄生米勒电容引起的导通 在半桥拓扑中,当上管IGBT(S1)正在导通, 产生变化的电压dV/dt加在下管IGBT(S1)C-E间。电流流经S2的寄生米勒电容CCG 、门极驱动电阻RG 、内部集成门极驱动电阻RDRIVER ,如图1所示。电流大小大致可以如下公式进行估算: 这个电流产生使门极电阻两端产生电压差,这个电压如果超过IGBT的门极驱动门限阈值,将导致寄生导通。设计工程师应该意识到IGBT节温上升会导致IGBT门极驱动阈值会有所下降,通常就是mv/℃级的。 当下管IGBT(S2)导通时,寄生米勒电容引起的导通同样会发生在S1上。 减缓米勒效应的解决方法 通常有三种传统的方法来解决以上问题:第一种方法是改变门极电阻(如图2);第二种方法是在在门极G和射极E 之间增加电容(如图3);第三种方法是采用负压驱动(如图4)。除此之外,还有一种简单而有效的解决方案即有源钳位技术(如图5)。 独立的门极开通和关断电阻 门极导通电阻RGON影响IGBT导通期间的门极充电电压和电流;增大这个电阻将减小门极充电的电压和电流,但会增加开通损耗。 寄生米勒电容引起的导通通过减小关断电阻RGOFF可以有效抑制。越小的RGOFF同样也能减少IGBT的关断损耗,然而需要付出的代价是在关断期间由于杂散电感会产生很高的过压尖峰和门极震荡。

采用零电压开关消除米勒效应

采用零电压开关消除米勒效应 设计电源时,工程师常常会关注与MOSFET导通损耗有关的效率下降问题。在出现较大RMS电流的情况下, 比如转换器在非连续导电模式(DCM)下工作时,若选择Rds(on)较小的MOSFET,芯片尺寸就会较大,从而输入电容也较大。也就是说,导通损耗的减小将会造成较大的输入电容和控制器较大的功耗。当开关频率提高时,问题将变得更为棘手。 MOSFET导通和关断时的典型栅电流如图1所示。在导通期间,流经控制器Vcc引脚的峰值电流对Vcc充电;在关断期间,存储的电流流向芯片的接地端。如果在相应的面积上积分,即进行篿gate(t)dt,则可得到驱动晶体管的栅电荷Qg 。将其乘以开关频率Fsw,就可得到由控制器Vcc提供的平均电流。因此,控制器上的总开关功率(击穿损耗不计)为: Pdrv = Fsw×Qg×Vcc (1) 如果使用开关速度为100kHz 的12V控制器驱动栅电荷为100nC的MOSFET,驱动器的功耗即为100nC×100kHz×12V=10mA×12V=120mW。 图1 MOSFET导通和关断时的典型栅电流 MOSFET的物理结构中有多种寄生单元,其中电容的作用十分关键,如图2所示。产品数据表中的三个参数采取如下定义:当源-漏极短路时,令Ciss = Cgs + Cgd;当栅-源极短路时,令Coss = Cds + Cgd;Crss = Cgd。 驱动器实际为栅-源极连接。当斜率为dt 的电压V施加到电容C上时(如驱动器的输出电压),将会增大电容内的电流:

I=C×dV/dt (2) 因此,向MOSFET施加电压时,将产生输入电流Igate = I1 + I2,如图2所示。在右侧电压节点上利用式(2),可得到: I1=Cgd×d(Vgs-Vds)/dt=Cgd×(dVgs/dt-dVds/dt) (3) I2=Cgs×d(Vgs/dt) (4) 如果在MOSFET上施加栅-源电压Vgs,其漏-源电压Vds 就会下降(即使是呈非线性下降)。因此,可以将连接这两个电压的负增益定义为: Vgs δVds/δAv=- (5) 将式(5)代入式(3)和式(4)中,并分解dVgs/dt,可得: Vgs)=Cgd×dVgs/dt×(1-Av) δVds/δI1=Cgd×dVgs/dt×(1- (6) 在转换(导通或关断)过程中,栅-源极的总等效电容Ceq为: Igate=(Cgd×(1-Av)+Cgs)×dVgs/dt=Ceq×dVgs/dt (7) 式中(1-Av)这一项被称作米勒效应,它描述了电子器件中输出和输入之间的电容反馈。当栅-漏电压接近于零时,将会产生米勒效应。典型功率MOSFET的栅电荷如图3所示,该图通过用恒定电流对栅极充电并对栅-源电压进行观察而得。根据式(6),当Ciss突然增大时,电流持续流过。但由于电容急剧增加,而相应的电压升高dVgs却严重受限,因此电压斜率几乎为零,如图3中的平坦区域所示。 图3也显示出降低在转换期间Vds(t)开始下降时的点的位置,有助于减少平坦区域效应。Vds=100V时的平坦区域宽度要比Vds=400V时窄,曲线下方的面积也随之减小。因此,如果能在Vds等于零时将MOSFET导通,即利用ZVS技术,就不会产生米勒效应。 在准谐振模式(QR)中采用反激转换器是消除米勒效应较经济的方法, 它无需在下一个时钟周期内使开关处于导通状态,只要等漏极上的自然振荡将电压逐渐降至接近于零。与此同时,通过专用引脚可以检测到控制器再次启动了晶体管。通过在开关打开处反射的足够的反激电压(N×[V out+Vf]),即可实现ZVS操作,这通常需要800V(通用范围)的高压MOSFET。基于安森美的NCP1207的QR转换器如图4所示,它可以直接使用高压电源供电。该转换器在ZVS下工作时的栅-源电压和漏极波形如图5所示。 总之,如果需要Qg较大的MOSFET,最好使反激转换器在ZVS下工作,这样可

密勒电容与密勒效应

1、密勒电容与密勒效应 简单说来: 对电子管,屏极与栅极之间的电容; 对晶体管,集电极与基极之间的电容; 对场效应管,漏极与栅极之间的电容。 这些管子作共阴极(共发射极、共源极)放大器时,输出端与输入端电压反相,使得该电容的充电放电电流增大,从输入端看进去,好像该电容增大了k倍,k是放大倍数。这种现象叫密勒效应。 也可以这样解释,在反相放大器中,输入极与输出极间的等效电容会扩大到1-Av倍反射到输入极的效应。 比如,考虑共源(或共射)的单管放大器,设C为GD (BC)电容,则有, i = (vi-vo) * jwC = vi * (1-Av) * jwC = vi * jw[(1-Av)*C] 这里[(1-Av)*C]即可看作在GS(BE)处的等效电容。 详见维基百科() 2、密勒效应 密勒效应(Miller effect)是在中,反相放大电路中,输入与输出之间的分布或寄生电容由于的放大作用,其等效到输入端的电容值会扩大1+K倍,其中K是该级放大电路电压放大倍数。虽然一般密勒效

应指的是电容的放大,但是任何输入与其它高放大节之间的阻抗也能够通过密勒效应改变放大器的输入阻抗。 输入电容的增长值为 A v是放大器的放大,C是反馈电容。 密勒效应是米勒定理的一个特殊情况。 历史 米勒效应是以命名的。1919年或1920年密勒在研究三极管时发现了这个效应,但是这个效应也适用于现代的半导体。 引导 假设一个放大率为A v的理想电压,其输入和输出点之间的阻抗为Z。其输出电压因此为V o = A v V i,输入电流则为 这个电流流过阻抗Z,上面的方程显示由于放大器的放大率实际上一个更大的电流流过Z,实际上Z就好像它小得多一样。电路的输入阻抗为 假如Z是电容的话,则

消除米勒效应

设计电源时,工程师常常会关注与MOSFET导通损耗有关的效率下降问题。在出现较大RMS电流的情况下, 比如转换器在非连续导电模式(DCM)下工作时,若选择Rds(on)较小的MOSFET,芯片尺寸就会较大,从而输入电容也较大。也就是说,导通损耗的减小将会造成较大的输入电容和控制器较大的功耗。当开关频率提高时,问题将变得更为棘手。 图1 MOSFET导通和关断时的典型栅电流 图2 MOSFET中的寄生电容

图3 典型MOSFET的栅电荷 图4 基于专用控制器的简单QR转换器 图5 ZVS技术消除米勒效应 MOSFET导通和关断时的典型栅电流如图1所示。在导通期间,流经控制器Vcc 引脚的峰值电流对Vcc充电;在关断期间,存储的电流流向芯片的接地端。如果

在相应的面积上积分,即进行篿gate(t)dt,则可得到驱动晶体管的栅电荷Qg 。将其乘以开关频率Fsw,就可得到由控制器Vcc提供的平均电流。因此,控制器上的总开关功率(击穿损耗不计)为: Pdrv = Fsw×Qg×Vcc (1) 如果使用开关速度为100kHz 的12V控制器驱动栅电荷为100nC的MOSFET,驱动器的功耗即为100nC×100kHz×12V=10mA×12V=120mW。 MOSFET的物理结构中有多种寄生单元,其中电容的作用十分关键,如图2所示。产品数据表中的三个参数采取如下定义:当源-漏极短路时,令Ciss = Cgs + C gd;当栅-源极短路时,令Coss = Cds + Cgd;Crss = Cgd。 驱动器实际为栅-源极连接。当斜率为dt 的电压V施加到电容C上时(如驱动器的输出电压),将会增大电容内的电流: I=C×dV/d t (2) 因此,向MOSFET施加电压时,将产生输入电流Igate = I1 + I2,如图2所示。在右侧电压节点上利用式(2),可得到: I1=Cgd×d(Vgs-Vds)/dt=Cgd×(dVgs/dt-dVds/d t) (3) I2=Cgs×d(Vgs/dt) (4) 如果在MOSFET上施加栅-源电压Vgs,其漏-源电压Vds 就会下降(即使是呈非线性下降)。因此,可以将连接这两个电压的负增益定义为: Vgs δV ds/δAv=- (5) 将式(5)代入式(3)和式(4)中,并分解 dVgs/dt,可得: Vgs)=Cgd×dVgs/dt×(1-A v) δVds/δI1=Cgd×dVgs/dt×(1- (6) 在转换(导通或关断)过程中,栅-源极的总等效电容Ceq为: Igate=(Cgd×(1-Av)+Cgs)×dVgs/dt=Ceq×dVgs/d t (7) 式中(1-Av)这一项被称作米勒效应,它描述了电子器件中输出和输入之间的电容反馈。当栅-漏电压接近于零时,将会产生米勒效应。典型功率MOSFET的栅电荷如图3所示,该图通过用恒定电流对栅极充电并对栅-源电压进行观察而得。根据式(6),当Ciss突然增大时,电流持续流过。但由于电容急剧增加,而相应的电压升高dVgs却严重受限,因此电压斜率几乎为零,如图3中的平坦区域所示。图3也显示出降低在转换期间Vds(t)开始下降时的点的位置,有助于减少平坦区域效应。Vds=100V时的平坦区域宽度要比Vds=400V时窄,曲线下方的面积也随之减小。因此,如果能在Vds等于零时将MOSFET导通,即利用ZVS技术,就不会产生米勒效应。 在准谐振模式(QR)中采用反激转换器是消除米勒效应较经济的方法, 它无需在 下一个时钟周期内使开关处于导通状态,只要等漏极上的自然振荡将电压逐渐降

MOS管的米勒效应-讲的很详细

米勒效应的影响: MOSFET栅极驱动过程,可以简单的理解为驱动源对MOSFET输入电容(主要是栅源极电容Cgs)的充放电过程;当Cgs达到门槛电压之后,MOSFETC会进入开通状态;当MOSFE升通后,Vds开始下降,Id开始上升,此时MOSFET 入饱和区;但由丁米勒效应,Vgs会持续一段时间不再上升,此时Id已经达到最大,而Vds还在继续下降,直到米勒电容充满电,Vgs乂上升到驱动电压的值,此时MOSFET入电阻区,此时Vds彻底降下来,开通结束。 由丁米勒电容阻止了Vgs的上升,从而也就阻止了Vds的下降,这样就会使损耗的时间加长。(Vgs上升,贝U导通电阻下降,从而Vds下降) 米勒效应在MO&区动中臭名昭著,他是由MO筝的米勒电容引发的米勒效应,在MO筝开通过程中,GS电压上升到某一电压值后GS电压有一段稳定值,过后GS 电压乂开始上升直至完全导通。为什么会有稳定值这段呢?因为,在MOST通前,D 极电压大丁G极电压,MO南生电容Cgd储存的电量需要在其导通时注入G极与其中的电荷中和,因MO织全导通后G极电压大丁D极电压。米勒效应会严重增加MOS勺开通损耗。(MOST不能很快得进入开关状态) 所以就出现了所谓的图腾驱动!!选择MOS寸,Cgd越小开通损耗就越小。米勒 效应不可能完全消失。 MOSFET的米勒平台实际上就是MOSFE处丁“放大区”的典型标志 用用示波器测量GS电压,可以看到在电压上升过程中有一个平台或凹坑,这就是米勒平台。 米勒效应指在MO争开通过程会产生米勒平台,原理如下。 理论上驱动电路在G级和S级之间加足够大的电容可以消除米勒效应。但此时开关时间会拖的很长。一般推荐值加O.ICiess的电容值是有好处的。 下图中粗黑线中那个平缓部分就是米勒平台

米勒效应分析

Mos 管米勒效应分析‐dengdexing 1、元器件参数 IRFBL3703 VDSS RDS(on) max ID 30V 0.0025? 260A ID @ TC = 25°C,Continuous Drain Current, VGS @ 10V 260A ID @ TC = 100°C Continuous Drain Current, VGS @ 10V 180 dv/dt Peak Diode Recovery, 5.0 V/ns Ciss Input Capacitance ––– 8250pf Coss Output Capacitance ––– 3000pf Crss Reverse Transfer Capacitance 10360pf Coss Output Capacitance 3060pf 其他参数请见IR 官网IRFBL3703datasheet 。 2、mos 门极灌电流(驱动源电压幅值)对驱动波形的影响 图1 在图1的电路条件下,从图2可以看出,驱动波形输入后约300ns 后进入米勒平台,平台电压在4.5V 左右,平台持续时间约650ns ,在进入米勒平台约20ns 后ds 压降开始急剧下降,功率管mos 开始导通,功率管流通电流开始增大,在平台期间的前200ns ds 压降下降迅速,在平台持续期间mos 并未完全进入饱和区,在此区间功率管损耗较大,平台结束后mos 开始进入饱和,ds 饱和导通,ds 压降非常小。 TD = 0TF = 50ns PW = 50us V1 = 0TR = 50ns V2 = 15V L1

米勒效应的解决方法

Mitigation Methods for Parasitic Turn-on effect due to Miller Capacitor White Paper Introduction One of the common problems faced when switching an IGBT is parasitic turn-on due to Miller capacitor. This effect is noticeable in single supply gate driver (0 to +15V). Due to this gate-collector coupling, a high dV/dt transient created during IGBT turn-off can induce parasitic turn-on (Gate voltage, VGE) which is potentially dangerous (Figure 1). GE DRIVER G CG Gate Voltage Spike High dV/dt Figure 1. Bottom IGBT Parasitic Turn-On due to Miller Capacitor Parasitic Turn-on due to Miller Capacitor When turning on the upper IGBT, S1 in a half-bridge, a voltage change dV CE /dt occurs across the lower IGBT, S2. A current flows through the parasitic Miller capacitor C CG of S2, the gate resistor R G and internal driver gate resistor, R DRIVER . Figure 1 shows the current flow through the capacitor. This current value can be approximated by the following formula: dt dV C I CE CG CG (1)This current creates a voltage drop across the gate resistor. If this voltage exceeds the IGBT gate threshold voltage, a parasitic turn-on occurs. Designers should be aware that rising IGBT chip temperature would lead to a slight reduction of gate threshold voltage, usually in the range of mV/°C. This parasitic turn-on can also be seen on S1 when S2 is turned on. Parasitic Turn-on Mitigation Solutions There are three classical solutions to the above problem; the first being to vary the gate resistor (Figure 2), second to add a capacitor between gate and emitter (Figure 3) and third to use negative gate drive (Figure 4). A fourth simple and effective solution is the Active Clamp technique (Figure 5). Separate gate resistor for turn-on and turn-off The on-gate resistor, R GON influences the voltage and current change during IGBT turn-on. Increasing this resistor reduces the voltage and current changes but increases switching losses. Parasitic turn-on can be prevented by reducing the off-gate resistor, R GOFF . The smaller R GOFF will also reduce switching loss during IGBT turn-off. However, the trade off is higher over-shoot Vce and oscillation during turn-off due to stray inductances. Due to the above, some design optimization of both gate resistors would be required (Figure 2). Figure 2. Separate On and Off Gate resistor

可消除米勒效应并提升PFC性能的折叠共源共栅结构.doc

可消除米勒效应并提升PFC性能的折叠共源共栅结构 离线式电源的功率因数校正器(PFC)前端很容易受到工作频率限制 的影响,而这种限制是相关的功率MOSFET 具有共源(MOSFET)或共发射极(双极晶体管)结构的所有晶体管都会产生米勒效应。 大多数PFC都采用具有共源MOSFET或共发射极功率双极晶体管结构的升压转换器。图1是一个采用共源功率MOSFET(Q)的传统升压PFC内核。这个内核本质上是一个高增益放大器,可以通过在电感器L上存储和释放能量来控制功率。当MOSFET处于导通和断开状态时,它的漏极电压(V DS)在接近0V和PFC输出电压之间摆动,PFC 输出一般在200V~400V之间。该电压以一定周期对MOSFET的漏/源极电容(C DS)和漏/栅电容(C DG)进行再充电,并且影响栅/源极(C GS)电容(图2)。 相对于V GS和E IN驱动电压,V DS和漏/栅极电压(V DG)是反相的,记住这一点至关重要。这意味着存在来自漏/栅极的负反馈,这就是米勒效应。米勒效应可加大MOSFET或双极晶体管的视在输入电容值。为了解米勒效应的影响,本文将分析米勒效应是如何影响升压晶体管的输入电流的,并同时忽略时序方法。MOSFET的内部栅极电阻(R G)(图2)可忽略不计,不在本次分析范围内。

图1:这个简化的PFC电路采用UC3854A和单电源MOSFET。 假定MOSFET为负反馈放大器,如果对其施加一个较小的步进输入(E IN),则式1成立: dV DG=dV GS-dV DS (1) 其中,V DG=漏/栅极电压,V GS=栅/源极电压,V DS=漏/源极电压。 它们的值都很小,因此将用这些值的微分形式进行分析,但是: dV DS=- dI D×Z L (2) 其中,dI D=MOSFET漏极电流的变化,Z L=负载阻抗。

2021年MOS管的米勒效应-讲的很详细之令狐采学创编

米勒效应的影响: 欧阳光明(2021.03.07) MOSFET的栅极驱动过程,可以简单的理解为驱动源对MOSFET 的输入电容(主要是栅源极电容Cgs)的充放电过程;当Cgs达到门槛电压之后,MOSFET就会进入开通状态;当MOSFET开通后,Vds开始下降,Id开始上升,此时MOSFET进入饱和区;但由于米勒效应,Vgs会持续一段时间不再上升,此时Id已经达到最大,而Vds还在继续下降,直到米勒电容充满电,Vgs又上升到驱动电压的值,此时MOSFET进入电阻区,此时Vds彻底降下来,开通结束。 由于米勒电容阻止了Vgs的上升,从而也就阻止了Vds的下降,这样就会使损耗的时间加长。(Vgs上升,则导通电阻下降,从而Vds下降) 米勒效应在MOS驱动中臭名昭著,他是由MOS管的米勒电容引发的米勒效应,在MOS管开通过程中,GS电压上升到某一电压值后GS电压有一段稳定值,过后GS电压又开始上升直至完全导通。为什么会有稳定值这段呢?因为,在MOS开通前,D极电压大于G 极电压,MOS寄生电容Cgd储存的电量需要在其导通时注入G极与其中的电荷中和,因MOS完全导通后G极电压大于D极电压。米勒效应会严重增加MOS的开通损耗。(MOS管不能很快得进入开关状态) 所以就出现了所谓的图腾驱动!!选择MOS时,Cgd越小开通损

耗就越小。米勒效应不可能完全消失。 MOSFET中的米勒平台实际上就是MOSFET处于“放大区”的典型标志 用用示波器测量GS电压,可以看到在电压上升过程中有一个平台或凹坑,这就是米勒平台。 米勒效应指在MOS管开通过程会产生米勒平台,原理如下。 理论上驱动电路在G级和S级之间加足够大的电容可以消除米勒效应。但此时开关时间会拖的很长。一般推荐值加0.1Ciess的电容值是有好处的。 下图中粗黑线中那个平缓部分就是米勒平台。 删荷系数的这张图在第一个转折点处:Vds开始导通。Vds的变化通过Cgd和驱动源的内阻形成一个微分。因为Vds近似线性下降,线性的微分是个常数,从而在Vgs处产生一个平台。 米勒平台是由于mos 的g d 两端的电容引起的,即mos datasheet里的Crss 。 这个过程是给Cgd充电,所以Vgs变化很小,当Cgd充到Vgs水平的时候,Vgs才开始继续上升。 Cgd在mos刚开通的时候,通过mos快速放电,然后被驱动电压反向充电,分担了驱动电流,使得Cgs上的电压上升变缓,出现平台to~t1: Vgs from 0 to Vth.Mosfet没通.电流由寄生二极管Df. t1~t2: Vgs from Vth to Va. Id t2~t3: Vds下降.引起电流继续通过Cgd. Vdd越高越需要的时间越长. Ig 为驱动电流.