定时器工作原理及应用引脚图

555定时器

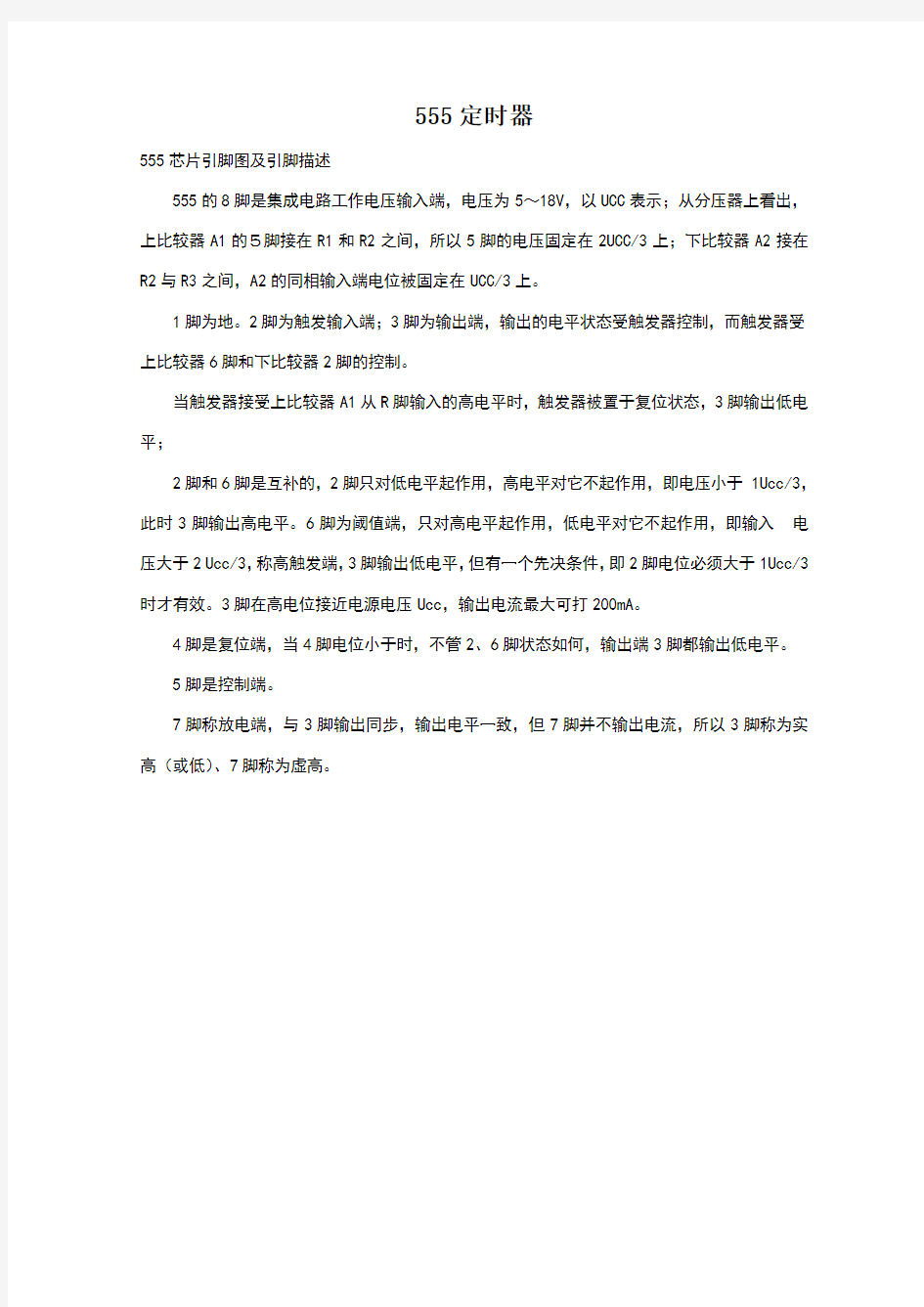

555芯片引脚图及引脚描述

555的8脚是集成电路工作电压输入端,电压为5~18V,以UCC表示;从分压器上看出,上比较器A1的5脚接在R1和R2之间,所以5脚的电压固定在2UCC/3上;下比较器A2接在R2与R3之间,A2的同相输入端电位被固定在UCC/3上。

1脚为地。2脚为触发输入端;3脚为输出端,输出的电平状态受触发器控制,而触发器受上比较器6脚和下比较器2脚的控制。

当触发器接受上比较器A1从R脚输入的高电平时,触发器被置于复位状态,3脚输出低电平;

2脚和6脚是互补的,2脚只对低电平起作用,高电平对它不起作用,即电压小于1Ucc/3,此时3脚输出高电平。6脚为阈值端,只对高电平起作用,低电平对它不起作用,即输入电压大于2 Ucc/3,称高触发端,3脚输出低电平,但有一个先决条件,即2脚电位必须大于1Ucc/3时才有效。3脚在高电位接近电源电压Ucc,输出电流最大可打200mA。

4脚是复位端,当4脚电位小于时,不管2、6脚状态如何,输出端3脚都输出低电平。

5脚是控制端。

7脚称放电端,与3脚输出同步,输出电平一致,但7脚并不输出电流,所以3脚称为实高(或低)、7脚称为虚高。

1概述

555定时器的简介

555定时器是一种多用途的数字——模拟混合集成电路,利用它能极方便地构成施密特触发器、单稳态触发器和多谐振荡器。由于使用灵活、方便,所以555定时器在波形的产生与交换、测量与控制、家用电器、电子玩具等许多领域中都得到了广泛应用。自从signetics公司于1972年推出这种产品以后,国际上个主要的电子器件公司也都相继的生产了各自的555定时器产品。尽管产品型号繁多,但是所有双极型产品型号最后的3位数码都是555,所有CMOS产品型号最后的4位数码都是7555.而且,它们的功能和外部引脚排列完全相同。

555定时器的应用

(1)构成施密特触发器,用于TTL系统的接口,整形电路或脉冲鉴幅等;(2)构成多谐振荡器,组成信号产生电路;

(3)构成单稳态触发器,用于定时延时整形及一些定时开关中。

555应用电路采用这3种方式中的1种或多种组合起来可以组成各种实用的电子电路,如定时器、分频器、元件参数和电路检测电路、玩具游戏机电路、音响告警电路、电源交换电路、频率变换电路、自动控制电路等。

2 555定时器的电路结构与工作原理

图 1

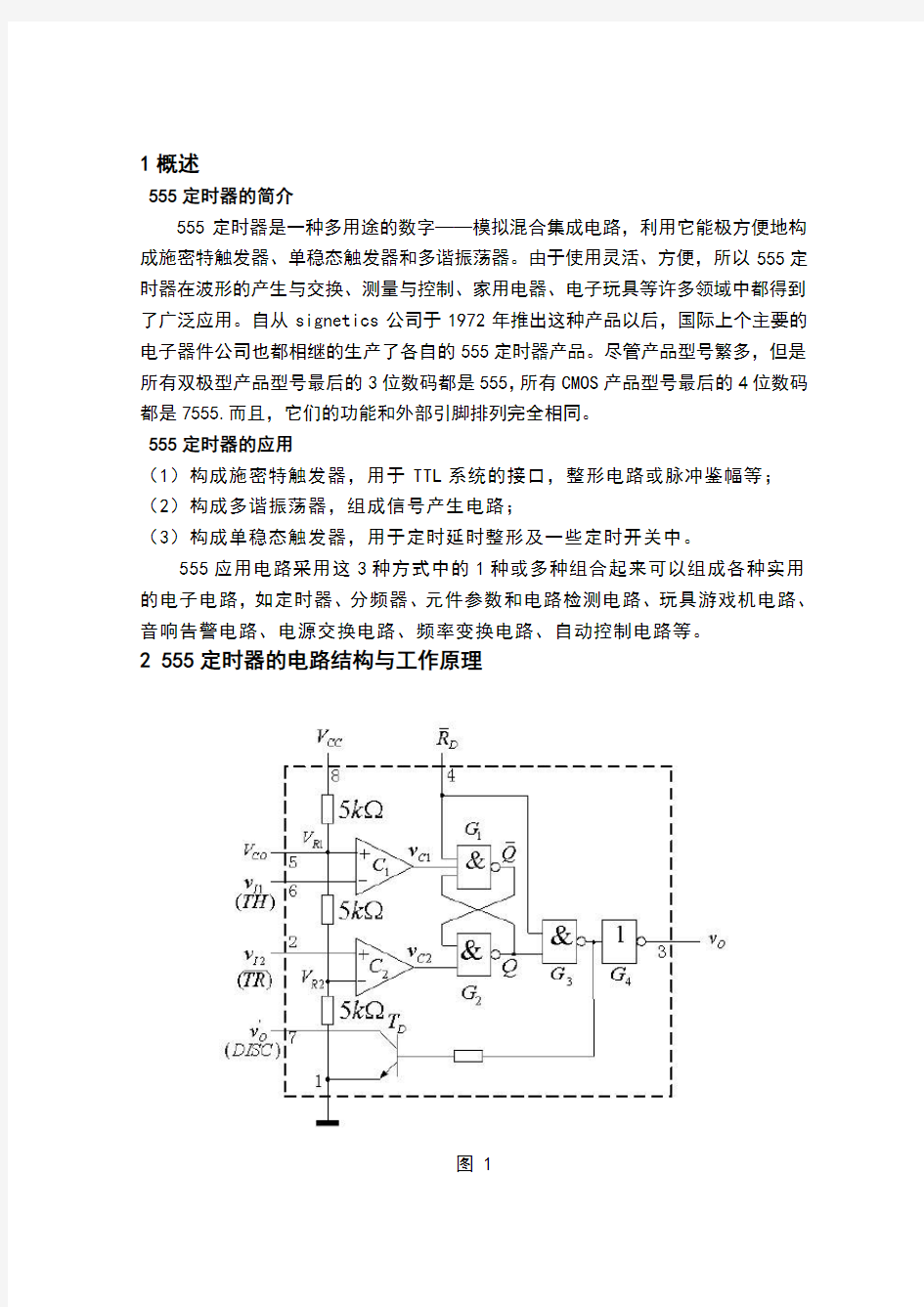

3、555定时器与触发器的联系、555定时器构成单稳态触发器

图 2

上图为由555定时器和外接定时元件R、C构成的单稳态触发器。D为钳位二极管,稳态时555电路输入端处于电源电平,内部放电开关管T导通,输出端Vo输出低电平,当有一个外部负脉冲触发信号加到Vi端。并使2端电位瞬时低于1/3VCC,低电平比较器动作,单稳态电路即开始一个稳态过程,电容C开始充电,Vc按指数规律增长。当Vc充电到2/3VCC时,高电平比较器动作,比较器A1翻转,输出Vo从高电平返回低电平,放电开关管T重新导通,电容C上的电荷很快经放电开关管放电,暂态结束,恢复稳定,为下个触发脉冲的来到作好准备。波形图见图3。

图3 单稳态触发器波形图

暂稳态的持续时间Tw(即为延时时间)决定于外接元件R、C的大小。Tw=

通过改变R、C的大小,可使延时时间在几个微秒和几十分钟之间变化。当这种单稳态电路作为计时器时,可直接驱动小型继电器,并可采用复位端接地的方法来终止暂态,重新计时。此外需用一个续流二极管与继电器线圈并接,以防继电器线圈反电势损坏内部功率管。

555定时器接成多谐振荡器

多谐振荡器又称为无稳态触发器,它没有稳定的输出状态,只有两个暂稳态。在电路处于某一暂稳态后,经过一段时间可以自行触发翻转到另一暂稳态。两个暂稳态自行相互转换而输出一系列矩形波。多谐振荡器可用作方波发生器。

图 4 多谐振荡器和工作波形

接通电源后,假定是高电平,则T截止,电容C充电。充电回路是VCC—R1—R2— C—地,按指数规律上升,当上升到时(TH、端电平大于),输出翻转为低电平。是低电平,T导通,C放电,放电回路为C—R2—T—地,按指数规律下降,当下降到时(TH、端电平小于),输出翻转为高电平,放电管T截止,电容再次充电,如此周而复始,产生振荡,经分析可得输出高电平时间 T=(R1+R2)Cln2

输出低电平时间T=R2Cln2

振荡周期 T=(R1+2R2)Cln2

555电路要求R1 与R2 均应大于或等于1KΩ,但R1+R2应小于或等于Ω。

外部元件的稳定性决定了多谐振荡器的稳定性,555定时器配以少量的元件即可获得较高精度的振荡频率和具有较强的功率输出能力。因此这种形式的多谐振荡器应用很广。

555定时器组成占空比可调的多谐振荡器

电路增加了一个电位器和两个导引二极管。D1、D2 用来决定电容充、放电电流流经电阻的途径(充电时D1 导通,D2截止;放电时D2导通,D1 截止)。

占空比 P=tw1/(tw1+tw2)

=RA/(RA+RB)×100%

可见,若取RA=RB 电路即可输出占空比为50%的方波信号。

555定时器组成施密特触发器

op07放大器电路图设计

op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。 特点: 超低偏移:150μV最大。 低输入偏置电流:1.8nA 。 低失调电压漂移:0.5μV/℃。 超稳定,时间:2μV/month最大 高电源电压范围:±3V至±22V 图1 OP07外型图片 图2 OP07 管脚图 OP07芯片引脚功能说明: 1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚6为输出,7接电源+ 图3 OP07内部

电路图 ABSOLUTE MAXIMUM RATINGS 最大额定值 Sy mb ol 符号Parameter参数 Value 数值 Unit 单位 VC C Supply Voltage 电源电压±22 V Vid Differential Input Voltage差分输入电 压 ±30 V Vi Input Voltage 输入电压±22 V Top er Operating Temperature 工作温度 -40 to +105 ℃ Tst g Storage T emperature 贮藏温度 -65 to +150 ℃ 电气特性 虚拟通道连接= ± 15V ,Tamb = 25 ℃(除非另有说明) Sy mb Parameter 参数及测试条件最小典最 Uni t

AT89C51单片机的概述

AT89C51单片机的概述 (1)AT89C51单片机的结构 AT89C51单片机是美国Atmel公司生产低电压,高性能CMOS 8位单片机,片内含4k bytes 的可反复擦写的只读程序存储器(EPROM)和128 bytes的随机存取数据存储器(RAM),器件采用Atmel公司的高密度、非易失性存取技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器(CPU)和Flash 存储单元,功能强大[3]。AT89C51单片机可提供许多高性价比的应用场合,可灵活应用于各种控制领域。 上图为AT89C51单片机的基本组成功能方块图。由图可见,在这一块芯片上,集成了一台微型计算机的主要组成部分,其中包括CPU、存储器、可编程I/O口、定时器/计数器、串行口等,各部分通过内部总线相连。下面介绍几个主要部分。 外中断控制并行口串行通信 AT89C51 功能方块图 (2)AT89C51的管脚说明 ATMEL公司的AT89C51是一种高效微控制器。采用40引脚双列直插封装形式。AT89C51单片机是高性能单片机,因为受引脚数目的限制,所以有不少引脚具有第二功能。 VCC:供电电压。 GND:接地。 P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P1口的管

脚第一次写1时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。在FLASH编程时,P0 口作为原码输入口,当FLASH进行校验时,P0输出原码,此时P0外部必须被拉高。 P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL 门电流。P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为第八位地址接收。 P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL 门电流,当P2口被写1时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址1时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。 P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。当P3口写入1后,它们被内部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,P3口将输出电流。 P3口也可作为AT89C51的一些特殊功能口,如下表所示: P3口管脚备选功能 P3.0 RXD(串行输入口) P3.1 TXD(串行输出口) P3.2 INT0(外部中断0) P3.3 INT1(外部中断1) P3.4 T0(记时器0外部输入) P3.5 T1(记时器1外部输入) P3.6 WR(外部数据存储器写选通) P3.7 RD(外部数据存储器读选通) P3口同时为闪烁编程和编程校验接收一些控制信号。 RST:复位输入。当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。 ALE/PROG:当访问外部存储器时,地址锁存允许端的输出电平用于锁存地址的地址字节。在FLASH编程期间,此引脚用于输入编程脉冲。在平时,ALE端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。因此它可用作对外部输出的脉冲或用于定时目的。然而要注意的是:每当用作外部数据存储器时,将跳过一个ALE脉冲。如想禁止ALE 的输出可在SFR8EH地址上置0。此时, ALE只有在执行MOVX,MOVC指令时ALE才起作用。 PSEN:外部程序存储器的选通信号端。在由外部程序存储器取指期间,每个机器周期两次PSEN有效。但在访问外部数据存储器时,这两次有效的/PSEN信号将不出现。

555定时器产生三种波形发生器

目录 摘要 (2) 第一章方案提出 (3) 第二章电路的基本组成及工作原理 (4) 第一节系统组成框图 (4) 第二节方波的产生 (5) 第三节由方波输出为三角波(利用积分器来实现) (7) 第四节由三角波输出正弦波 (9) 第三章 555定时器的介绍 (10) 第一节电路组成 (11) 第二节引脚的作用 (12) 第三节基本功能 (13) 第四章元件清单 (15) 第五章总结 (16) 附录及参考文献 (17) 第一节附录 (17) 一多谐振荡器——产生矩形脉冲波的自激振荡器 (17) 二电路原理图 (19) 第二节参考文献 (20)

摘要 各种电器设备要正常工作,常常需要各种波形信号的支持。电器设备中常用的信号有正弦波、矩形波、三角波和锯齿波等。在电器设备中,这些信号是由波形产生和变换电路来提供的。波形产生电路是一种不需外加激励信号就能将直流能源转化成具有一定频率、一定幅度和一定波形的交流能量输出电路,又称为振荡器或波形发生器。 在生产实践和科技领域中有着广泛的应用。各种波形曲线均可以用三角函数方程式来表示。能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。 波形发生器通过与波形变换电路相结合,它能产生正弦波、矩形波、三角波和阶梯波等各种波形,能满足现代测量、通信、自动控制和热加工、音视频设备及数字系统等对各种信号源的需求。例如在通信、广播、电视系统中,都需要射频(高频)发射,这里的射频波就是载波,把音频(低频)、视频信号或脉冲信号运载出去,就需要能够产生高频的振荡器。在工业、农业、生物医学等领域内,如高频感应加热、熔炼、淬火、超声诊断、核磁共振成像等,都需要功率或大或小、频率或高或低的振荡器等。 关键字:方案确定、参数计算、信号、发生器等。

AT89C51单片机温度控制系统

毕业设计(论文) 论文题目:AT89C51单片机温度控制系统 所属系部:电子工程系 指导老师:职称: 学生姓名:班级、学号: 专业:应用电子技术 2012 年05 月15 日

毕业设计(论文)任务书 题目:AT89C51单片机温度控制系统 任务与要求:设计并制作一个能够控制1KW电炉的温度控制系统,控制温度恒定在37--38度之间。 时间:年月日至年月日 所属系部:电子工程系 学生姓名:学号: 专业:应用电子技术 指导单位或教研室:测控技术教研室 指导教师:职称: 年月日

摘要 本设计是以一个1KW电炉为控制对象,以AT89C51为控制系统核心,通过单片机系统设计实现对保电炉温度的显示和控制功能。本温度控制系统是一个闭环反馈调节系统,由温度传感器DS18B20对保炉内温度进行检测,经过调理电路得到合适的电压信号。经A/D转换芯片得到相应的温度值,将所得的温度值与设定温度值相比较得到偏差。通过对偏差信号的处理获得控制信号,去调节加热器的通断,从而实现对保温箱温度的显示和控制。本文主要介绍了电炉温度控制系统的工作原理和设计方法,论文主要由三部分构成。①系统整体方案设计。②硬件设计,主要包括温度检测电路、A/D转换电路、显示电路、键盘设计和控制电路。③系统软件设计,软件的设计采用模块化设计,主要包括A/D转换模块、显示模块等。 关键词:单片机传感器温度控制

目录 绪论 (1) 第一章温度控制系统设计和思路 (2) 1.1温度控制系统设计思路 (2) 1.2 系统框图 (2) 第二章 AT89C51单片机 (3) 2.1 AT89C51单片机的简介 (3) 2.2 AT89C51单片机的主要特性 (3) 2.3 AT89C51单片机管脚说明 (4) 第三章温度控制的硬件设备 (6) 3.1温度传感器简介 (6) 3.2 DS18B20工作原理 (7) 3.3 DS18B20使用中注意事项 (8) 第四章系统硬件设计 (9) 4.1温度采集电路 (9) 4.2 数码管温度显示电路 (9) 4.2.1 数码管的分类 (9) 4.2.2 数码管的驱动方式 (10) 4.2.3 恒流驱动与非恒流驱动对数码管的影响 (11) 4.3 单片机接口电路 (12) 4.3.1 P0口的上拉电阻原理 (12) 4.3.2 上拉电阻的选择 (14) 4.4 单片机电源及下载线电路 (14) 4.5 温度控制电路 (15) 第五章温度控制的软件设计 (17) 5.1 数码管动态显示 (17) 5.2 DS18B20初始化 (17) 5.3 系统流程图 (19) 谢辞 (20) 参考文献 (21) 附录 (22)

555引脚图

NE555引脚图及ne555的作用介绍 ne555是一种应用特别广泛作用很大的的集成电路,属于小规模集成电路,在很多电子产品中都有应用。ne555的作用是用内部的定时器来构成时基电路,给其他的电路提供时序脉冲。ne555时基电路有两种封装形式有,一是dip双列直插8脚封装,另一种是sop-8小型(smd)封装形式。其他ha17555、lm555、ca555分属不同的公司生产的产品。内部结构和工作原理都相同。 ne555的内部结构可等效成23个晶体三极管.17个电阻.两个二极管.组成了比较器.RS触发器.等多组单元电路.特别是由三只精度较高5k电阻构成了一个电阻分压器.为上.下比较器提供基准电压.所以称之为555. ne555属于cmos工艺制造. NE555引脚图介绍如下 1地GND 2触发 3输出 4复位 5控制电压 6门限(阈值) 7放电 8电源电压Vcc 应用十分广泛. 下面是一个简单的ne555电路应用

NE555绍 NE555 (Timer IC)大约在1971年由Signetics Corporation发布,在当时是唯一非常快速且商业化的Timer IC,在往后的30年來非常普遍被使用,且延伸出许多的应用电路,尽管近年來CMOS技术版本的Timer IC如MOTOROLA的MC1455已被大量的使用,但原规格的NE555依然正常的在市场上供应,尽管新版IC在功能上有部份的改善,但其脚位劲能并没变化,所以到目前都可直接的代用。 NE555是属于555系列的计时IC的其中的一种型号,555系列IC的接脚功能及运用都是相容的,只是型号不同的因其价格不同其稳定度、省电、可产生的振荡频率也不大相同;而555是一个用途很广且相当普遍的计时IC,只需少数的电阻和电容,便可产生数位电路所需的各种不同频率之脉冲信号。 a. NE555的特点有: 1.只需简单的电阻器、电容器,即可完成特定的振荡延时作用。其延

c引脚图及功能中文资料

89c51引脚图及功能 89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。89C2051是一种带2K字节闪烁可编程可擦除只读存储器的单片机。单片机的可擦除只读存储器可以反复擦除100次。该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL的89C51是一种高效微控制器,89C2051是它的一种精简版本。89C单片机为很多嵌入式控制系统提供了一种 灵活性高且价廉的方案。 1.主要特性: ·与MCS-51 兼容 ·4K字节可编程闪烁存储器 寿命:1000写/擦循环 数据保留时间:10年 ·全静态工作:0Hz-24Hz ·三级程序存储器锁定 ·128*8位内部RAM ·32可编程I/O线 ·两个16位定时器/计数器 ·5个中断源 ·可编程串行通道 ·低功耗的闲置和掉电模式 ·片内振荡器和时钟电路

2.管脚说明: VCC:供电电压。 GND:接地。 P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P1口的管脚第一次写1时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。 P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为 第八位地址接收。 P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控 制信号。

NE555定时器构成多谐振荡器

NE555定时器构成的多谐振荡器 一、原理 1、555定时器内部结构 555定时器是一种模拟电路和数字电路相结合的中规模集成电路,其内部结构如图(A ) 及管脚排列如图(B )所示。 它由分压器、比较器、基本R--S 触发器和放电三极管等部分组成。分压器由三个5K 的等值电阻串联而成。分压器为比较器1A 、2A 提供参考电压,比较器1A 的参考电压为 2 3 cc V ,加在同相输入端,比较器2A 的参考电压为13cc V ,加在反相输入端。比较器由两个 结构相同的集成运放1A 、2A 组成。高电平触发信号加在1A 的反相输入端,与同相输入端的参考电压比较后,其结果作为基本R--S 触发器_ D R 端的输入信号;低电平触发信号加在 2A 的同相输入端,与反相输入端的参考电压比较后,其结果作为基本R —S 触发器_ D S 端 的输入信号。基本R--S 触发器的输出状态受比较器1A 、2A 的输出端控制。 2、 多谐振荡器工作原理 由555定时器组成的多谐振荡器如图(C)所示,其中R 1、R 2和电容C 为外接元件。其 工作波如图(D)所示。

设电容的初始电压c U =0,t =0时接通电源,由于电容电压不能突变,所以高、低触 发端TH V =TL V =0<1 3 VCC,比较器A1输出为高电平,A2输出为低电平,即_ 1D R =, _ 0D S =(1表示高电位,0表示低电位),R S -触发器置1,定时器输出01u =此时 _ 0Q =,定时器内部放电三极管截止,电源cc V 经1R ,2R 向电容C充电,c u 逐渐升高。当 c u 上升到1 3 cc V 时,2A 输出由0翻转为1,这时__ 1D D R S ==,R S -触发顺保持状态不 变。所以0 —VCC:供电电压。 —GND:接地。 —P0口:P0口为 一个8位漏级开路双 向I/O口,每个管脚可 吸收8TTL门电流。当P1口的管脚写“1”时,被定义为高阻输入。P0能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。在FLASH编程时,P0口作为原码输入口,当FLASH进行校验时,P0输出原码,此时P0外部电位必须被拉高。 —P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入“1”后,电位被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH 编程和校验时,P1口作为第八位地址接收。 —P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚电位被内部上拉电阻拉高,且作为输入。作为输入时,P2口的管脚电位被外部拉低,将输出电流,这是由于内部上拉的缘故。P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址“1”时,它利用内部上拉的优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。 —P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL 门电流。当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。作为输入时,由于外部下拉为低电平,P3口将输出电流(ILL),也是由于上拉的缘故。 P3口也可作为AT89C51的一些特殊功能口,如下所示: P3.0 RXD(串行输入口) P3.1 TXD(串行输出口) P3.2 0 INT(外部中断0) P3.3 1 INT(外部中断1) P3.4 T0(记时器0外部输入) P3.5 T1(记时器1外部输入) P3.6 W R(外部数据存储器写选通) P3.7 RD(外部数据存储器读选通) P3口同时为闪烁编程和编程校验接收一些控制信号。 —RST:复位输入。当振荡器复位器件时,要保持RST脚两个机器周期的高电平时间。 ALE/:当访问外部存储器时,地址锁存允许的输出电平用于锁存—PROG 地址的地位字节。在FLASH编程期间,此引脚用于输入编程脉冲。在平时,ALE 端以不变的频率周期输出正脉冲信号,此频率为振荡器频率的1/6。因此它可用作对外部输出的脉冲或用于定时目的。然而要注意的是:每当用作外部数据存储器时,将跳过一个ALE脉冲。如想禁止ALE的输出可在SFR8EH地址上置0。此时, ALE 只有在执行MOVX,MOVC指令时ALE才起作用。另外,该引脚被略微拉高。如果微处理器在外部执行状态ALE禁止,置位无效。 —PSEN:外部程序存储器的选通信号。在由外部程序存储器取址期间,每个机器周期PSEN两次有效。但在访问外部数据存储器时,这两次有效的PSEN 信号将不出现。 EA/:当EA保持低电平时,访问外部ROM;注意加密方式1时,EA将—VPP 内部锁定为RESET;当EA端保持高电平时,访问内部ROM。在FLASH编程期间,此 NE555 (Timer IC)大约在1971年由Signetics Corporation发布,在当时是唯一非常快速且商业化的Timer IC,在往后的30年来非常普遍被使用,且延伸出许多的应用电路,尽管近年來CMOS技术版本的Timer IC如MOTOROLA的MC1455已被大量的使用,但原规格的NE555依然正常的在市场上供应,尽管新版IC在功能上有部份的改善,但其脚位劲能并没变化,所以到目前都可直接的代用。 NE555是属于555系列的计时IC的其中的一种型号,555系列IC的接脚功能及运用都是相容的,只是型号不同的因其价格不同其稳定度、省电、可产生的振荡频率也不大相同;而555是一个用途很广且相当普遍的计时IC,只需少数的电阻和电容,便可产生数位电路所需的各种不同频率的脉波讯号。 a. NE555的特点有: 1.只需简单的电阻器、电容器,即可完成特定的振荡延时作用。其延时范围极广,可由几微秒至几小时之久。 2.它的操作电源范围极大,可与TTL,CMOS等逻辑闸配合,也就是它的输出准位及输入触发准位,均能与这些逻辑系列的高、低态组合。 3.其输出端的供给电流大,可直接推动多种自动控制的负载。 4.它的计时精确度高、温度稳定度佳,且价格便宜。 b. NE555引脚位配置说明下: NE555接脚图 ne555的结构图 Pin 1 (接地) -地线(或共同接地) ,通常被连接到电路共同接地。 Pin 2 (触发点) -这个脚位是触发NE555使其启动它的时间周期。触发信号上缘电压须大于2/3 VCC,下缘须低于1/3 VCC 。 Pin 3 (输出) -当时间周期开始555的输出输出脚位,移至比电源电压少1.7伏的高电位。周期的结束输出回到O伏左右的低电位。于高电位时的最大输出电流大约200 mA 。 —VCC:供电电压。 :接地。—GND 口为P0P0口:—位漏级开路双8一个每个管脚可口,向I/O门电流。当8TTL 吸收时,1”“P1口的管脚写被定义为高阻输入。能够用于外部程序P0数据存储 器,它可以地址被定义为数据/FLASH的第八位。在外部输出原码,此时P0口作 为原码输入口,当FLASH进行校验时,P0编程时,P0 电位必须被拉高。口缓冲 器能接收P1I/O8位双向口,—P1口:P1口是一个内部提供上拉电阻的”后, 电位被内部上拉为高,可用作输入,1门电流。P1口管脚写入“输出4TTLFLASH 口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在P1 口 作为第八位地址接收。编程和校验时,P1输口缓冲器可接收,口,P2P2口为一 个内部上拉电阻的8位双向I/O—P2口:”时,其管脚电位被内部上拉电阻拉高, 且作口被写“1个4TTL门电流,当P2出口的管脚电位被外部拉低,将输出电流, 这是由于内部为输入。作为输入时,P2位地址外部数据存储器进行存取口当用 于外部程序存储器或16上拉的缘故。P2”时,它利用内部上拉的优势,当1P2 时,口输出地址的高八位。在给出地址“P2口输出其特殊功能寄存器的内容。 对外部八位地址数据存储器进行读写时,P2 编程和校验时接收高八位地址信号 和控制信号。口在FLASHTTL4个8个带内部上拉电阻的双向I/O口,可接收输出 P3 —P3口:口管脚是”后,它们被内部上拉为高电平,并用作输入。作为输1 门电流。当P3口写入“ (ILL),也是由于上拉的缘故。口将输出电流入时,由 于外部下拉为低电平, P3 . . . . NE555在线计算器555集成电路参数应用计算 NE555绍 NE555 (Timer IC)大约在1971年由Signetics Corporation发布,在当时是唯一非常快速且商业化的Timer IC,在往后的30年來非常普遍被使用,且延伸出许多的应用电路,尽管近年來CMOS技术版本的Timer IC如MOTOROLA的MC1455已被大量的使用,但原规格的NE555依然正常的在市场上供应,尽管新版IC在功能上有部份的改善,但其脚位劲能并没变化,所以到目前都可直接的代用。 NE555是属于555系列的计时IC的其中的一种型号,555系列IC的接脚功能及运用都是相容的,只是型号不同的因其价格不同其稳定度、省电、可产生的振荡频率也不大相同;而555是一个用途很广且相当普遍的计时IC,只需少数的电阻和电容,便可产生数位电路所需的各种不同频率之脉冲信号。 a.NE555的特点有: 1.只需简单的电阻器、电容器,即可完成特定的振荡延时作用。其延时范围极广,可由几微秒至几小时之久。 2.它的操作电源电压范围极大,可与TTL,CMOS等逻辑电路配合, 也就是它的输出准位及输入触发准位,均能与这些逻辑系列的高、低态组合。 3.其输出端的供给电流大,可直接推动多种自动控制的负载。 4.它的计时精确度高、温度稳定度佳,且价格便宜。 5.静态电流最大值VCC = 5 V, RL = ∞ =6mA VCC =15 V, RL = ∞ =15mA b. NE555引脚图功能配置说明下: 图1-2 NE555各脚功能-管脚图Pin 1 (接地) -地线(或共同接地) ,通常被连接到电路共同 AT89C51引脚图及功能 电子元件知识2010-03-04 23:12:41 阅读1759 评论1 字号:大中小订阅 89C51外部引脚图:(可以直接拷入ASM程序文件中,作注释使用,十分方便); ┏━┓┏━┓ ; P1.0 ┫1 ┗┛40┣Vcc ; P1.1 ┫2 39┣P0.0 ; P1.2 ┫3 38┣P0.1 ; P1.3 ┫4 37┣P0.2 ; P1.4 ┫5 36┣P0.3 ; P1.5 ┫6 35┣P0.4 ; P1.6 ┫7 34┣P0.5 ; P1.7 ┫8 33┣P0.6 ; RST/Vpd ┫9 32┣P0.7 ; RXD P3.0 ┫10 31┣-EA/Vpp(内1/外0 程序地址选择) ; TXD P3.1 ┫11 30┣ALE/-P (地址锁存输出) ; -INT0 P3.2 ┫12 29┣-PSEN (外部程序读选通输出) ; -INT1 P3.3 ┫13 28┣P2.7 ; T0 P3.4 ┫14 27┣P2.6 ; T1 P3.5 ┫15 26┣P2.5 ; -WR P3.6 ┫16 25┣P2.4 ; -RD P3.7 ┫17 24┣P2.3 ; X2 ┫18 23┣P2.2 ; X1 ┫19 22┣P2.1 ; GND ┫20 21┣P2.0 ; ┗━━━━┛ 引脚说明: ①电源引脚 Vcc(40脚):典型值+5V。 Vss(20脚):接低电平。 ②外部晶振 X1、X2分别与晶体两端相连接。当采用外部时钟信号时,X2接振荡信号,X1接地。 ③输入输出口引脚: P0口:I/O双向口。作输入口时,应先软件置“ 1”。 P1口:I/O双向口。作输入口时,应先软件置“ 1”。 P2口:I/O双向口。作输入口时,应先软件置“ 1”。 P3口:I/O双向口。作输入口时,应先软件置“ 1”。 ④控制引脚: RST/Vpd、ALE/-PROG、-PSEN、-EA/Vpp组成了MSC-51的控制总线。 RST/Vpd(9脚):复位信号输入端(高电平有效)。 NE555引脚功能 Pin 1 (接地) -地线(或共同接地) ,通常被连接到电路共同接地。 Pin 2 (触发点) -这个脚位是触发NE555使其启动它的时间周期。触发信号上缘电压须大于2/3 VCC,下缘须低于1/3 VCC 。 Pin 3 (输出) -当时间周期开始555的输出输出脚位,移至比电源电压少1.7伏的高电位。周期的结束输出回到O伏左右的低电位。于高电位时的最大输出电流大约200 mA。 Pin 4 (重置) -一个低逻辑电位送至这个脚位时会重置定时器和使输出回到一个低电位。它通常被接到正电源或忽略不用。 Pin 5 (控制) -这个接脚准许由外部电压改变触发和闸限电压。当计时器经营在稳定或振荡的运作方式下,这输入能用来改变或调整输出频率。 Pin 6 (重置锁定) - Pin 6重置锁定并使输出呈低态。当这个接脚的电压从1/3 VCC电压以下移至2/3 VCC以上时启动这个动作。 Pin 7 (放电) -这个接脚和主要的输出接脚有相同的电流输出能力,当输出为ON时为LOW,对地为低阻抗,当输出为OFF时为HIGH,对地为高阻抗。 Pin 8 (V +) -这是555个计时器IC的正电源电压端。供应电压的范围是+4.5伏特(最小值)至+16伏特(最大值)。 参数功能特性: ?供应电压4.5-18V ?供应电流3-6 mA ?输出电流225mA (max) ?上升/下降时间100 ns .NE555的相关应用: NE555的作用范围很广,但一般多应用于单稳态多谐振荡器(Monostable Mutlivibrator)及无稳态多谐振荡器(Astable Multivibrator)。 图1是NE555的外形图,图2是它的内部功能原理框图,图3是它的内部等效电路。NE555的内部中心电路是三极管Q15和Q17加正反馈组成的RS触发器。输入控制端有直接复位Reset端,通过比较器A1,复位控制端的TH、比较器A2置位控制的T。输出端为F,另外还有集电极开路的放电管DIS。它们控制的优先权是R、T、TH。、 55的极限参数 电源电压允许功耗工作温度储藏温度最高结温 +18V 600mW -10—+70℃ 军用-55—+125℃-65—+150℃ 300℃ at89c51引脚图及功能 AT89C51是美国ATMEL公司生产的低电压,高性能CMOS8位单片机,片内含4k bytes的可反复擦写的只读程序存储器(PEROM)和128 bytes的随机存取数据存储器(RAM),器件采用ATMEL公司的高密度、非易失性存储技术生产,兼容标准MCS-51指令系统,片内置通用8位中央处理器(CPU)和Flash存储单元,功能强大AT89C51单片机可为您提供许多高性价比的应用场合,可灵活应用于各种控制领域。 主要性能参数: ·与MCS-51产品指令系统完全兼容·4k字节可重擦写Flash闪速存储器·1000次擦写周期 ·全静态操作:0Hz-24MHz ·三级加密程序存储器·128×8字节内部RAM ·32个可编程I/O口线·2个16位定时/计数器·6个中断源 ·可编程串行UART通道·低功耗空闲和掉电模式 功能特性概述: AT89C51提供以下标准功能:4k字节Flash闪速存储器,128字节内部RAM,32个I/O口线,两个16位定时/计数器,一个5向量两级中断结构,一个全双工串行通信口,片内振荡器及时钟电路。同时,AT89C51可降至0Hz的静态逻辑操作,并支持两种软件可选的节电工作模式。空闲方式停止CPU的工作,但允许RAM,定时/计数器,串行通信口及中断系统继续工作。掉电方式保存RAM中的内容,但振荡器停止工作并禁止其它所有部件工作直到下一个硬件复位。 ·P0口:P0口是一组8位漏极开路型双向I/O口,也即地址/数据总线复用口。作为输出口用时,每位能吸收电流的方式驱动8个TTL逻辑门电路,对端口写“1”可作为高阻抗输入端用。 在访问外部数据存储器或程序存储器时,这组口线分时转换地址(低8位)和数据总线复用,在访问期间激活内部上拉电阻。 在FIash编程时,P0口接收指令字节,而在程序校验时,输出指令字节,校验时,要求外接上拉电阻。 ·P1口:P1是一个带内部上拉电阻的8位双向I/O口,P1的输出缓冲级可驱 NE555管脚功能原理应用电路图与pdf资料 一.ne555管脚图及内部原理图 NE555内部电路方框图: 内部含有两个电压比较器,一个分压器,一个RS触发器,一个放电晶体管和一个功率输出级。 电路内部方框图 电路引脚图 参考【电子制作https://www.360docs.net/doc/9019094364.html,】 二.应用电路图 触摸延时灯 集成电路IC1是一片555定时电路,在这里接成单稳态电路。平时由于触摸片P端无感应电压,电容C1通过555第7脚放电完毕,第3脚输出为低电平,继电器KS释放,电灯不亮。 当需要开灯时,用手触碰一下金属片P,人体感应的杂波信号电压由C2加至555的触发端,使555的输出由低变成高电平,继电器KS吸合,电灯点亮。同时,555第7脚内部截止,电源便通过R1给C1充电,这就是定时的开始。 当电容C1上电压上升至电源电压的2/3时,555第7脚道通使C1放电,使第3脚输出由高电平变回到低电平,继电器释放,电灯熄灭,定时结束。 定时长短由R1、C1决定:T1=1.1R1*C1。按图中所标数值,定时时间约为4分钟。D1可选用1N4148或1N4001。 相片曝光定时器 附图电路是用555单稳电路制成的相片曝光定时器。用人工启动式单稳电路。 工作原理:电源接通后,定时器进入稳态。此时定时电容CT的电压为:VCT=VC C=6V。对555这个等效触发器来讲,两个输入都是高电平,即VS=0。继电器KA不吸合,常开点是打开的,曝光照明灯HL不亮。 按一下按钮开关SB之后,定时电容CT立即放到电压为零。于是此时555电路等效触发的输入成为:R=0、S=0,它的输出就成高电平:V0=1。继电器KA吸动,常开接点闭合,曝光照明灯点亮。按钮开关按一下后立即放开,于是电源电压就通过RT向电容C T充电,暂稳态开始。当电容CT上的电压升到2/3VCC既4伏时,定时时间已到,555等效电路触发器的输入为:R=1、S=1,于是输出又翻转成低电平:V0=0。继电器KA释放,曝光灯HL熄灭。暂稳态结束,有恢复到稳态。 曝光时间计算公式为:T=1.1RT*CT。本电路提供参数的延时时间约为1秒~2分钟,可由电位器RP调整和设置。 电路中的继电器必需选用吸合电流不应大于30mA的产品,并应根据负载(HL)的容量大小选择继电器触点容量。 单电源变双电源电路 附图电路中,时基电路555接成无稳态电路,3脚输出频率为20KHz、占空比为1:1的方波。3脚为高电平时,C4被充电;低电平时,C3被充电。由于VD1、VD2的存在,C3、C4在电路中只充电不放电,充电最大值为EC,将B端接地,在A、C两端就得到+ /-EC的双电源。本电路输出电流超过50mA。 简易催眠器 《基础强化训练》报告 题目:OP07功率放大器 专业班级:电子科学与技术0703班学生姓名:田鑫 指导教师:钟毅 武汉理工大学信息工程学院 2009年07月17日 基础强化训练任务书 学生姓名:田鑫专业班级:电子科学与技术0703班指导教师:钟毅工作单位:武汉理工大学 题目:protel应用实践—OP07功率放大器 ·初始条件:计算机;Microsoft Office Word软件;PROTEL软件 ·要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求) 1、绘制具有一定规模、一定复杂程度的电路原理图*.sch(自选)。可以涉及模拟、数字、高频、单片机、或者一个具有完备功能的电路系统。 2、绘制相应电路原理图的双面印刷版图*.pcb 3、对电路原理图进行仿真,给出仿真结果(如波形*.sdf、数据)并说明是否达到设计意图。 ·时间安排: 1、2009年7月13日集中,作基础强化训练具体实施计划与报告格式的要求说明;学生查阅相关资料,学习电路的工作原理。 2、2009年7月14日,电路设计与分析。 3、2009年7月15日至2009年7月16日,相关电路原理图和PCB版图的绘制。 4、2009年7月17日,上交基础强化训练成果及报告,进行答辩。 答疑地点:鉴主13楼电子科学与技术实验室。 指导教师签名: 年月日系主任(或责任教师)签名: 年月日 摘要 (1) ABSTRACT (2) 1绪论 (3) 1.1Protel99SE简介 (3) 1.2PROTEL99SE系统组成 (3) 1.3PROTEL99SE功能特性 (4) 2设计内容及要求 (4) 2软件的选择 (4) 2.1设计目的及主要任务 (4) 2.1.1设计目的 (4) 2.1.2设计任务及主要技术指标 (5) 2.2设计要求 (5) 3OP07介绍 (5) 4OP07功放电路图 (7) 5OP07功放PCB板绘制 (10) 6OP07电路仿真 (13) 7心得与体会 (15) 8主要参考文献 (16) N E555详细介绍和引 脚图 NE555 (Timer IC)大约在1971年由Signetics Corporation发布,在当时是唯一非常快速且商业化的Timer IC,在往后的30年来非常普遍被使用,且延伸出许多的应用电路,尽管近年來CMOS技术版本的Timer IC如MOTOROLA的MC1455已被大量的使用,但原规格的NE555依然正常的在市场上供应,尽管新版IC在功能上有部份的改善,但其脚位劲能并没变化,所以到目前都可直接的代用。 NE555是属于555系列的计时IC的其中的一种型号,555系列IC的接脚功能及运用都是相容的,只是型号不同的因其价格不同其稳定度、省电、可产生的振荡频率也不大相同;而555是一个用途很广且相当普遍的计时IC,只需少数的电阻和电容,便可产生数位电路所需的各种不同频率的脉波讯号。 a. NE555的特点有: 1.只需简单的电阻器、电容器,即可完成特定的振荡延时作用。其延时范围极广,可由几微秒至几小时之久。 2.它的操作电源范围极大,可与TTL,CMOS等逻辑闸配合,也就是它的输出准位及输入触发准位,均能与这些逻辑系列的高、低态组合。 3.其输出端的供给电流大,可直接推动多种自动控制的负载。 4.它的计时精确度高、温度稳定度佳,且价格便宜。 b. NE555引脚位配置说明下: NE555接脚图 ne555的结构图 Pin 1 (接地) -地线(或共同接地) ,通常被连接到电路共同接地。 Pin 2 (触发点) -这个脚位是触发NE555使其启动它的时间周期。触发信号上缘电压须大于2/3 VCC,下缘须低于1/3 VCC 。 Pin 3 (输出) -当时间周期开始555的输出输出脚位,移至比电源电压少1.7伏的高电位。周期的结束输出回到O伏左右的低电位。于高电位时的最大输出电流大约200 mA 。 Pin 4 (重置) -一个低逻辑电位送至这个脚位时会重置定时器和使输出回到一个低电位。它通常被接到正电源或忽略不用。 Pin 5 (控制) -这个接脚准许由外部电压改变触发和闸限电压。当计时器经营在稳定或振荡的运作方式下,这输入能用来改变或调整输出频率。 Pin 6 (重置锁定) - Pin 6重置锁定并使输出呈低态。当这个接脚的电压从1/3 VCC电压以下移至2/3 VCC以上时启动这个动作。 Pin 7 (放电) -这个接脚和主要的输出接脚有相同的电流输出能力,当输出为ON时为LOW,对地为低阻抗,当输出为OFF时为HIGH,对地为高阻抗。 莈螃莃莈虿肁膆op07的功能介绍:Op07芯片是一种低噪声,非斩波稳零的双极性运算放大器集成电路。由于OP07具有非常低的输入失调电压(对于OP07A最大为25μV),所以OP07在很多应用场合不需要额外的调零措施。OP07同时具有输入偏置电流低(OP07A为±2nA)和开环增益高(对于OP07A为300V/mV)的特点,这种低失调、高开环增益的特性使得OP07特别适用于高增益的测量设备和放大传感器的微弱信号等方面。 袃膅薈蒁膁螄蒈特点: 蚃蚈罿莀薆蚈膀超低偏移:150μV最大。 低输入偏置电流:1.8nA 。 低失调电压漂移:0.5μV/℃。 超稳定,时间:2μV/month最大 高电源电压范围:±3V至±22V 袈螀薀肃螈螇肂图1 OP07外型图片 芈蚀袅羈蕿节蒄图2 OP07 管脚图 膄蒃膇莁蒂芆肇OP07芯片引脚功能说明: 1和8为偏置平衡(调零端),2为反向输入端,3为正向输入端,4接地,5空脚6为输出,7接电源+ 芅芇衿薂袄膇肀图3 OP07内部电路图 蒇蚀螁蚆莇蚈莄ABSOLUTE MAXIMUM RATINGS 最大额定值 芈羁膃薇 葿蒃螂 Sy mb ol 符号肁羅螆芁蚃薄蚇Parameter参数 薃袆蝿袃莆螆肀 Value 数值 Unit 单位 VC C Supply Voltage 电源电压±22 V Vid Differential Input Voltage差分输入电 压 ±30 V Vi Input Voltage 输入电压±22 V Top er Operating Temperature 工作温度 -40 to +105 ℃ Tst g Storage T emperature 贮藏温度 -65 to +150 ℃ 电气特性 AT89C51单片机简介 AT89C51是一种带4K字节闪烁可编程可擦除只读存储器(FPEROM—Falsh Programmable and Erasable Read Only Memory)的低电压,高性能CMOS8位微处理器,俗称单片机。AT89C2051是一种带2K字节闪烁可编程可擦除只读存储器的单片机。单片机的可擦除只读存储器可以反复擦除100次。该器件采用ATMEL高密度非易失存储器制造技术制造,与工业标准的MCS-51指令集和输出管脚相兼容。由于将多功能8位CPU和闪烁存储器组合在单个芯片中,ATMEL 的AT89C51是一种高效微控制器,AT89C2051是它的一种精简版本。AT89C单片机为很多嵌入式控制系统提供了一种灵活性高且价廉的方案。 1.主要特性: ·与MCS-51 兼容 ·4K字节可编程闪烁存储器 寿命:1000写/擦循环 数据保留时间:10年 ·全静态工作:0Hz-24Hz ·三级程序存储器锁定 ·128*8位内部RAM ·32可编程I/O线 ·两个16位定时器/计数器 ·5个中断源 ·可编程串行通道 ·低功耗的闲置和掉电模式 ·片内振荡器和时钟电路 2.管脚说明: VCC:供电电压。 GND:接地。 P0口:P0口为一个8位漏级开路双向I/O口,每脚可吸收8TTL门电流。当P1口的管脚第一次写1时,被定义为高阻输入。P0 能够用于外部程序数据存储器,它可以被定义为数据/地址的第八位。在FIASH编程时,P0 口作为原码输入口,当FIASH进行校验时,P0输出原码,此时P0外部必须被拉高。 P1口:P1口是一个内部提供上拉电阻的8位双向I/O口,P1口缓冲器能接收输出4TTL门电流。P1口管脚写入1后,被内部上拉为高,可用作输入,P1口被外部下拉为低电平时,将输出电流,这是由于内部上拉的缘故。在FLASH编程和校验时,P1口作为第八位地址接收。 P2口:P2口为一个内部上拉电阻的8位双向I/O口,P2口缓冲器可接收,输出4个TTL门电流,当P2口被写“1”时,其管脚被内部上拉电阻拉高,且作为输入。并因此作为输入时,P2口的管脚被外部拉低,将输出电流。这是由于内部上拉的缘故。P2口当用于外部程序存储器或16位地址外部数据存储器进行存取时,P2口输出地址的高八位。在给出地址“1”时,它利用内部上拉优势,当对外部八位地址数据存储器进行读写时,P2口输出其特殊功能寄存器的内容。P2口在FLASH编程和校验时接收高八位地址信号和控制信号。 P3口:P3口管脚是8个带内部上拉电阻的双向I/O口,可接收输出4个TTL门电流。当P3口写入“1”后,它们被内部上拉为高电平,并用作输入。作为输入,由于外部下拉为低电平,P3口将输出电流(ILL)这是由于上拉的缘故。AT89C51的引脚功能

NE555详细介绍和引脚图

AT89C51的引脚功能

NE555管脚解说及内部结构图

AT89C51引脚图及功能

NE555引脚功能

at89c51引脚图及功能

ne555管脚功能原理应用电路图与pdf资料

OP07功率放大器的应用实践

NE555详细介绍和引脚图讲课教案

op07放大器电路图设计

AT89C51引脚全部和功能