直接数字频率合成芯片AD9832原理及其典型应用设计

《测控技术》2004年第23卷第12期·68·

文章编号:1000–8829(2004)12–0068–03

直接数字频率合成芯片AD9832原理及其典型应用设计DDS AD9832 and It’s Typical Application

(同济大学交通信息工程系,上海 200331)沈拓,董德存

摘要:直接数字式频率合成技术可以提供快速的信号建立时间,纯净的信号频谱,方便地产生各种波形,实现各种调制方式,在通信与电子系统中广泛应用。笔者介绍了直接数字频率合成芯片AD9832的组成结构、转换原理和典型应用电路,分析了与80C51的接口时序,并给出了C驱动源代码。

关键词:直接数字频率合成;AD9832;开关电容滤波器;

80C51

中图分类号:TN74

文献标识码:B

Abstract:Direct digital synthesis can offer high converting speed,pure singal spectrum,and generate many types of wave-form,realize some modulations. It is widely used in communica-tion and electronic systems because of these special advantages. The composition,operational principle and typical application circuit of AD9832 are introduced. AD9832 to 80C51 interface,timing and C driver source code are discussed.

Key words:direct digital synthesis ; AD9832 ; switched capacitor filter ; 80C51

直接数字式频率合成(DDS,direct digital synthesis)是近年出现的新一代频率合成方法,采用全数字化VLSI技术设计,与传统的直接频率合成及PLL锁相环频率合成相比,信号建立时间快,一般在几ns到几μs;频率分辨率高;频率转换时相位保持连续;容易实现QAM、FSK、PSK和GMSK等各种调制方式[1]。AD9832是一款完备的DDS芯片,只需要1个外部参考时钟、2个电阻和几个退耦电容就可以产生高达12.5 MHz的正弦波,并且采用串行接口设计,使用方便,已经越来越多地应用到各种通信与电子系统中。

1 DDS基本转换原理

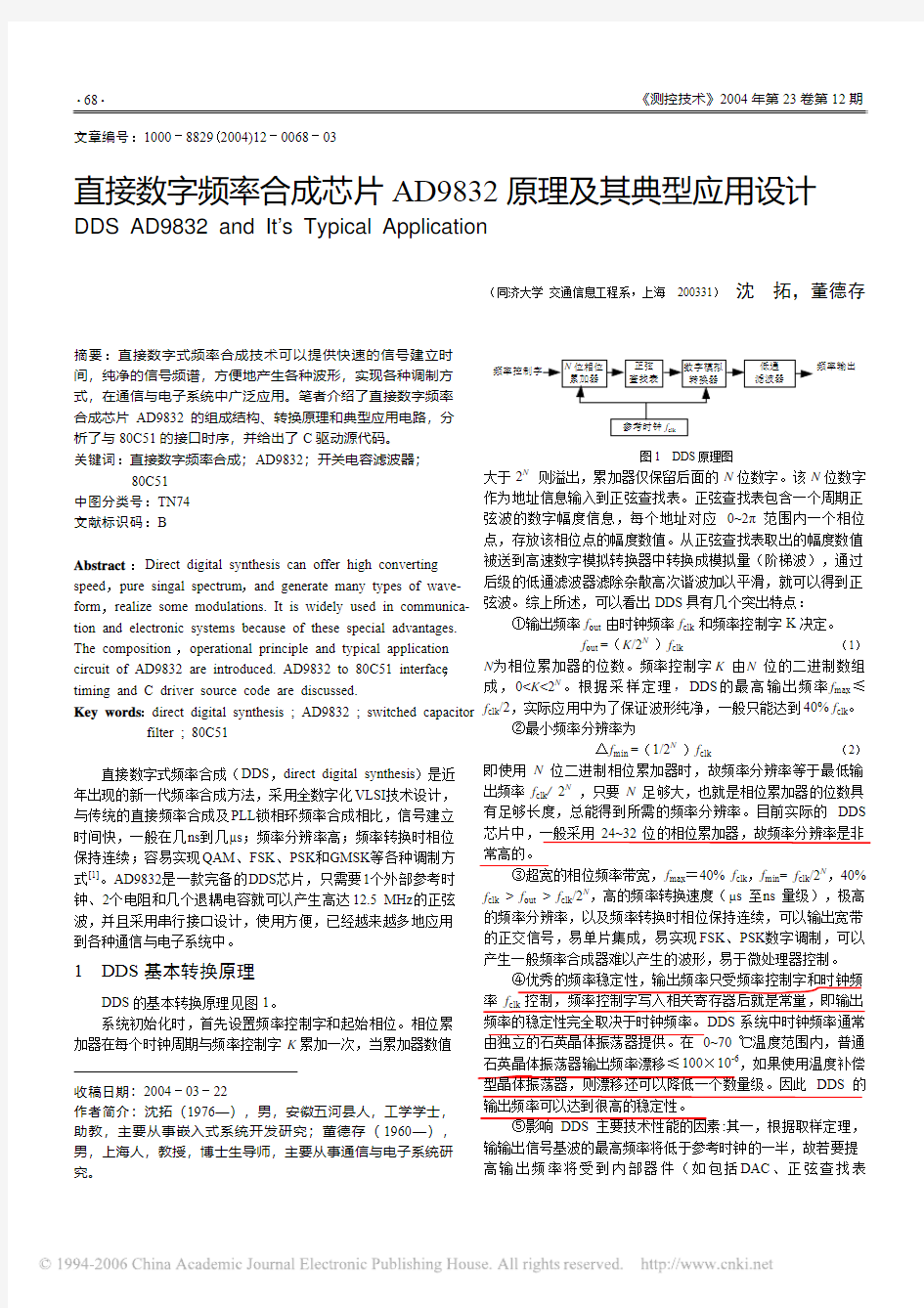

DDS的基本转换原理见图1。

系统初始化时,首先设置频率控制字和起始相位。相位累加器在每个时钟周期与频率控制字K累加一次,当累加器数值

收稿日期:2004–03–22

作者简介:沈拓(1976—),男,安徽五河县人,工学学士,助教,主要从事嵌入式系统开发研究;董德存(1960—),男,上海人,教授,博士生导师,主要从事通信与电子系统研究。

图1 DDS原理图

大于2N 则溢出,累加器仅保留后面的N位数字。该N位数字作为地址信息输入到正弦查找表。正弦查找表包含一个周期正弦波的数字幅度信息,每个地址对应0~2π范围内一个相位点,存放该相位点的幅度数值。从正弦查找表取出的幅度数值被送到高速数字模拟转换器中转换成模拟量(阶梯波),通过后级的低通滤波器滤除杂散高次谐波加以平滑,就可以得到正弦波。综上所述,可以看出DDS具有几个突出特点:

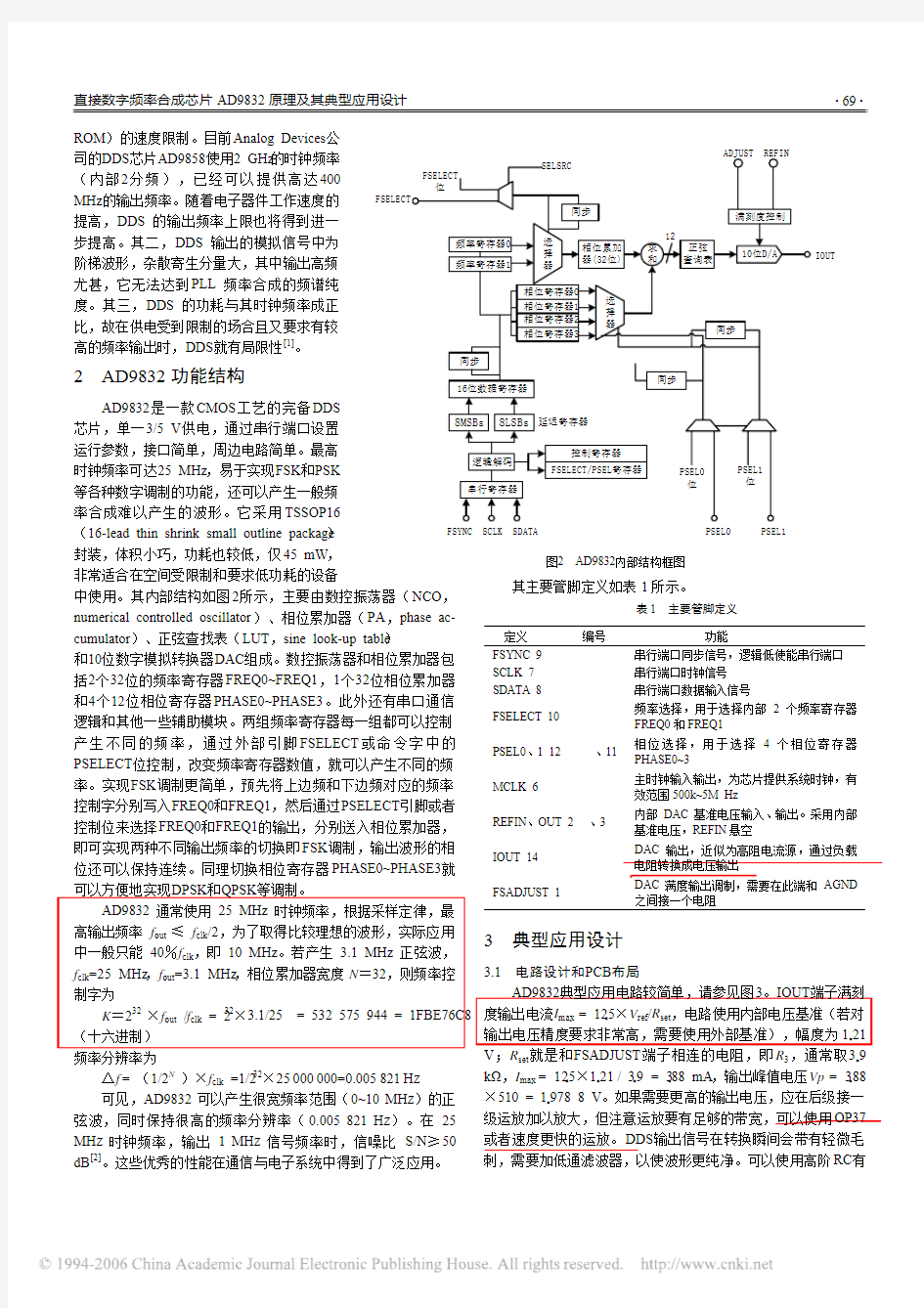

①输出频率f out 由时钟频率f clk 和频率控制字K决定。

f out =(K/2N)f clk(1)N为相位累加器的位数。频率控制字K 由N 位的二进制数组成,0 f clk/2,实际应用中为了保证波形纯净,一般只能达到40% f clk。 ②最小频率分辨率为 Δf min =(1/2N)f clk (2)即使用N 位二进制相位累加器时,故频率分辨率等于最低输出频率f clk/ 2N,只要N 足够大,也就是相位累加器的位数具有足够长度,总能得到所需的频率分辨率。目前实际的DDS 芯片中,一般采用24~32位的相位累加器,故频率分辨率是非常高的。 ③超宽的相位频率带宽,f max=40%f clk,f min= f clk/2N,40% f clk > f out > f clk/2N,高的频率转换速度(μs 至ns 量级),极高的频率分辨率,以及频率转换时相位保持连续,可以输出宽带的正交信号,易单片集成,易实现FSK、PSK数字调制,可以产生一般频率合成器难以产生的波形,易于微处理器控制。 ④优秀的频率稳定性,输出频率只受频率控制字和时钟频率f clk 频率的稳定性完全取决于时钟频率。DDS系统中时钟频率通常由独立的石英晶体振荡器提供。在0~70 ℃温度范围内,普通石英晶体振荡器输出频率漂移≤100×10-6,如果使用温度补偿型晶体振荡器,则漂移还可以降低一个数量级。因此DDS的输出频率可以达到很高的稳定性。 ⑤影响DDS主要技术性能的因素:其一,根据取样定理,输输出信号基波的最高频率将低于参考时钟的一半,故若要提高输出频率将受到内部器件(如包括DAC、正弦查找表 直接数字频率合成芯片AD9832原理及其典型应用设计 ·69· ROM )的速度限制。目前Analog Devices 公司的DDS 芯片AD9858使用2 GHz 的时钟频率(内部2分频),已经可以提供高达400 MHz 的输出频率。随着电子器件工作速度的提高,DDS 的输出频率上限也将得到进一步提高。其二,DDS 输出的模拟信号中为阶梯波形,杂散寄生分量大,其中输出高频尤甚,它无法达到PLL 频率合成的频谱纯度。其三,DDS 的功耗与其时钟频率成正比,故在供电受到限制的场合且又要求有较高的频率输出时,DDS 就有局限性[1]。 2 AD9832功能结构 AD9832是一款CMOS 工艺的完备DDS 芯片,单一3/5 V 供电,通过串行端口设置运行参数,接口简单,周边电路简单。最高时钟频率可达25 MHz ,易于实现FSK 和PSK 等各种数字调制的功能,还可以产生一般频 率合成难以产生的波形。它采用TSSOP16 (16-lead thin shrink small outline package )封装,体积小巧,功耗也较低,仅45 mW ,非常适合在空间受限制和要求低功耗的设备 中使用。其内部结构如图2所示,主要由数控振荡器(NCO , numerical controlled oscillator )、相位累加器(PA ,phase ac-cumulator )、正弦查找表(LUT ,sine look-up table ) 和10位数字模拟转换器DAC 组成。数控振荡器和相位累加器包 括2个32位的频率寄存器FREQ0~FREQ1,1个32位相位累加器 和4个12位相位寄存器PHASE0~PHASE3。此外还有串口通信逻辑和其他一些辅助模块。两组频率寄存器每一组都可以控制产生不同的频率,通过外部引脚FSELECT 或命令字中的PSELECT 位控制,改变频率寄存器数值,就可以产生不同的频 率。实现FSK 调制更简单,预先将上边频和下边频对应的频率控制字分别写入FREQ0和FREQ1,然后通过PSELECT 引脚或者 控制位来选择FREQ0和FREQ1的输出,分别送入相位累加器,即可实现两种不同输出频率的切换即FSK 调制,输出波形的相位还可以保持连续。同理切换相位寄存器PHASE0~PHASE3就 可以方便地实现DPSK 和QPSK 等调制。 AD9832通常使用25 MHz 时钟频率,根据采样定律,最高输出频率f out ≤ f clk /2,为了取得比较理想的波形,实际应用中一般只能40%f clk ,即10 MHz 。若产生3.1 MHz 正弦波,f clk =25 MHz ,f out =3.1 MHz ,相位累加器宽度N =32,则频率控制字为 K =232 ×f out / f clk = 232×3.1/25 = 532 575 944 = 1FBE76C8 (十六进制) 频率分辨率为 Δf = (1/2N )×f clk =1/232×25 000 000=0.005 821 H Z 可见,AD9832可以产生很宽频率范围(0~10 MH Z )的正弦波,同时保持很高的频率分辨率(0.005 821 H Z )。在25 MH Z 时钟频率,输出1 MH Z 信号频率时,信噪比S/N ≥50 dB [2]。这些优秀的性能在通信与电子系统中得到了广泛应用。 其主要管脚定义如表1所示。 表1 主要管脚定义 定义 编号 功能 FSYNC 9 串行端口同步信号,逻辑低使能串行端口 SCLK 7 串行端口时钟信号 SDATA 8 串行端口数据输入信号 FSELECT 10 频率选择,用于选择内部2个频率寄存器 FREQ0和FREQ1 PSEL0、1 12、11 相位选择,用于选择4个相位寄存器 PHASE0~3 MCLK 6 主时钟输入输出,为芯片提供系统时钟,有 效范围500k~5M Hz REFIN 、OUT 2、3 内部DAC 基准电压输入、输出。采用内部 基准电压,REFIN 悬空 IOUT 14 DAC 输出,近似为高阻电流源,通过负载 电阻转换成电压输出 FSADJUST 1 DAC 满度输出调制,需要在此端和AGND 之间接一个电阻 3 典型应用设计 3.1 电路设计和PCB 布局 AD9832典型应用电路较简单,请参见图3。IOUT 端子满刻度输出电流I max = 12.5×V ref /R set ,电路使用内部电压基准(若对输出电压精度要求非常高,需要使用外部基准),幅度为1.21 V ;R set 就是和FSADJUST 端子相连的电阻,即R 3,通常取3.9 k ?,I max = 12.5×1.21 / 3.9 = 3.88 mA ,输出峰值电压Vp = 3.88×510 = 1.978 8 V 。如果需要更高的输出电压,应在后级接一级运放加以放大,但注意运放要有足够的带宽,可以使用OP37或者速度更快的运放。DDS 输出信号在转换瞬间会带有轻微毛刺,需要加低通滤波器,以使波形更纯净。可以使用高阶RC 有 IOUT FSYNC SCLK SDATA PSEL0 PSEL1 图2 AD9832内部结构框图 《测控技术》2004年第23卷第12期 ·70· 源滤波器,推荐使用开关电容滤波器,如八阶椭圆滤波器 MAX293,使用更方便,便于调整,当然滤波性也能更好[3]。 为了降低输出噪声,模拟电源A VDD 和数字电源DVDD 是分开的,都加有退耦电容;模拟地AGND 和数字地GGND 也是分开的,PCB 布局时要注意两者分别走线,只在一点相连,保证数字回流不干扰模拟输出的稳定。串口信号线如SCLK 、SDATA 等应该避免从芯片下面通过,以减少这些高速跳变的数字信号携带的高次谐波影响模拟输出。电压基准REFOUT 和补偿COMP 端也加了0.01 μF 退耦电容。这些退耦电容都应该尽量减小环路面积,并尽量靠近芯片,最大程度地降低输出噪声。 3.2 软件设计 AD9832可以和常见的DSP 如ADSP21XX 系列,以及MCU 如68HC11、80C51系列接口[2],本例由80C51 MCU 控制。驱动程序可以选择汇编或者C 语言,考虑到C 的移植性好,可读性强,采用C51编写[4]。头文件中声明:SCLK 为AD9832时钟管脚;SDATA 为数据输入;FSYNC 为同步。串口写时序如图4所示。FSYNC 由高电平变为低电平,表示串口传输开始,在SCLK 的下降沿时SDATA 数据有效,即AD9832在SCLK 的下降沿读入SDATA 电平状态。主控器件应首先将SDATA 置为所需状态,然后再将SCLK 拉低,发送一位数据。串口通信时,高位数据首先移入,低位数据后移入。具体函数如下: void byte_shift (unsigned int data_16) //向AD9832写入16bit 数据 { unsigned int temp; FSYNC = 0; SCLK = 1; for (temp=0x8000; temp; temp>>=1, SCLK=1; ){ SDATA=data_16&temp; //先发送最 高位数据 SCLK=0; } FSYNC = 1; } void Freq_Process (unsigned char FREQ0_LSBs_L , unsigned char FREQ0_LSBs_H , unsigned char FREQ0_MSBs_L , unsigned char FREQ0_MSBs_H ) //计算频率寄存器参数 { byte_shift (0xf800); byte_shift (0x3400+FREQ0_LSBs_L ); byte_shift (0x2500+FREQ0_LSBs_H ); byte_shift (0x3600+FREQ0_MSBs_L ); byte_shift (0x2700+FREQ0_MSBs_H ); byte_shift (0xc000); } void Freq_Adjust (float value_Freq ) //产生指定频率的正弦波 { unsigned long Freq_reg; unsigned char L_L , L_H , H_L , H_H; Freq_reg=value_Freq*0x106; L_L=Freq_reg&0x000000ff; L_H=(Freq_reg>>8)&0x000000ff; H_L=(Freq_reg>>16)&0x000000ff; H_H=(Freq_reg>>24)&0x000000ff; Freq_Process (L_L ,L_H ,H_L ,H_H ); } 4 结束语 AD9832具有高稳定性、高精度、高分辨率、高速建立信号等突出优点,容易实现多种调制方式,产生多种复杂信号,在通信、测量和其他电子系统中都有广泛的用途。若辅以PLL 技术,还可以实现更加灵活的频率合成。 参考文献: [1] 高泽溪,高成.直接频率合成器(DDS )及其性能分析[J].北京:北京航 空航天大学学报,1998,24(1). [2] Analog Devices ,Inc.. AD9832 data sheet[Z].1999. [3] Maxim Integrated Products ,Inc..MAX293/294/297 data sheet[Z].1992. [4] 徐爱钧,彭秀华.单片机高级语言C51 Windows 环 境编程与应用[M].北京:电子工业出版社,2001. □ R 3 R 4 C 6 C 7 C 14 C 4 C 15 C 5 图3 AD9832典型应用电路 t 7 t 9 t 6 t 5 t 10 t 4 t 8 D15 D14 D1 D0 D14 D15 图4 写时序 SCLK FSYNC SDATA D2 第三章、器件 一、超深亚微米工艺条件下MOS 管主要二阶效应: 1、速度饱和效应:主要出现在短沟道NMOS 管,PMOS 速度饱和效应不显著。主要原因是 TH G S V V -太大。在沟道电场强度不高时载流子速度正比于电场强度(μξν=) ,即载流子迁移率是常数。但在电场强度很高时载流子的速度将由于散射效应而趋于饱和,不再随电场 强度的增加而线性增加。此时近似表达式为:μξυ=(c ξξ<),c s a t μξυυ==(c ξξ≥) ,出现饱和速度时的漏源电压D SAT V 是一个常数。线性区的电流公式不变,但一旦达到DSAT V ,电流即可饱和,此时DS I 与GS V 成线性关系(不再是低压时的平方关系)。 2、Latch-up 效应:由于单阱工艺的NPNP 结构,可能会出现VDD 到VSS 的短路大电流。 正反馈机制:PNP 微正向导通,射集电流反馈入NPN 的基极,电流放大后又反馈到PNP 的基极,再次放大加剧导通。 克服的方法:1、减少阱/衬底的寄生电阻,从而减少馈入基极的电流,于是削弱了正反馈。 2、保护环。 3、短沟道效应:在沟道较长时,沟道耗尽区主要来自MOS 场效应,而当沟道较短时,漏衬结(反偏)、源衬结的耗尽区将不可忽略,即栅下的一部分区域已被耗尽,只需要一个较小的阈值电压就足以引起强反型。所以短沟时VT 随L 的减小而减小。 此外,提高漏源电压可以得到类似的效应,短沟时VT 随VDS 增加而减小,因为这增加了反偏漏衬结耗尽区的宽度。这一效应被称为漏端感应源端势垒降低。 4、漏端感应源端势垒降低(DIBL): VDS增加会使源端势垒下降,沟道长度缩短会使源端势垒下降。VDS很大时反偏漏衬结击穿,漏源穿通,将不受栅压控制。 5、亚阈值效应(弱反型导通):当电压低于阈值电压时MOS管已部分导通。不存在导电沟道时源(n+)体(p)漏(n+)三端实际上形成了一个寄生的双极性晶体管。一般希望该效应越小越好,尤其在依靠电荷在电容上存储的动态电路,因为其工作会受亚阈值漏电的严重影响。 绝缘体上硅(SOI) 6、沟长调制:长沟器件:沟道夹断饱和;短沟器件:载流子速度饱和。 7、热载流子效应:由于器件发展过程中,电压降低的幅度不及器件尺寸,导致电场强度提高,使得电子速度增加。漏端强电场一方面引起高能热电子与晶格碰撞产生电子空穴对,从而形成衬底电流,另一方面使电子隧穿到栅氧中,形成栅电流并改变阈值电压。 影响:1、使器件参数变差,引起长期的可靠性问题,可能导致器件失效。2、衬底电流会引入噪声、Latch-up、和动态节点漏电。 解决:LDD(轻掺杂漏):在漏源区和沟道间加一段电阻率较高的轻掺杂n-区。缺点是使器件跨导和IDS减小。 8、体效应:衬底偏置体效应、衬底电流感应体效应(衬底电流在衬底电阻上的压降造成衬偏电压)。 二、MOSFET器件模型 1、目的、意义:减少设计时间和制造成本。 2、要求:精确;有物理基础;可扩展性,能预测不同尺寸器件性能;高效率性,减少迭代次数和模拟时间 3、结构电阻:沟道等效电阻、寄生电阻 4、结构电容: 三、特征尺寸缩小 目的:1、尺寸更小;2、速度更快;3、功耗更低;4、成本更低、 方式: 1、恒场律(全比例缩小),理想模型,尺寸和电压按统一比例缩小。 优点:提高了集成密度 未改善:功率密度。 问题:1、电流密度增加;2、VTH小使得抗干扰能力差;3、电源电压标准改变带来不便;4、漏源耗尽层宽度不按比例缩小。 2、恒压律,目前最普遍,仅尺寸缩小,电压保持不变。 优点:1、电源电压不变;2、提高了集成密度 问题:1、电流密度、功率密度极大增加;2、功耗增加;3、沟道电场增加,将产生热载流子效应、速度饱和效应等负面效应;4、衬底浓度的增加使PN结寄生电容增加,速度下降。 3、一般化缩小,对今天最实用,尺寸和电压按不同比例缩小。 限制因素:长期使用的可靠性、载流子的极限速度、功耗。 中国最具潜力的20家芯片设计企业 专题特写:《国际电子商情》创刊二十周年系列报道 春华秋实:中国IC设计业走向可持续发展之路 ? 《国际电子商情》伴随着中国电子产业飞速发展已经走过了整整二十个不平凡的春秋,我们热切的目光也一路见证了中国IC设计业从孕育到成长,从星星之火到阵容壮大。今天,我们聚集在创刊20周年庆的舞台上,与20家中国最具代表性的IC设计公司一道,细数回顾饱含酸甜苦辣的发展历程,展现他们创立以来的丰硕成果和未来发展规划,分享业界志士们对产业环境变化的衷心感言。 诚然,中国IC产业在过去十几年取得了巨大的成就,IC设计企业已接近500家,2004年销售收入过亿元人民币的企业达到了16家之多。但是IC企业仍然有很长的路要走,一方面产品市场范围过窄,主要集中于电源管理、信号处理、视频编解码、玩具控制等几个方面,在相当一段时间里仍将提供替代性产品为主;另一方面,企业知识产权的建立与保护机制有待健全和加强。所幸的是,本土IC设计企业已然清醒认识到这些问题,正在向具有自主知识产权、自我良性循环成长的可持续发展之路迈进。 安凯开曼公司 这是一家创办于硅谷、根植于中国的芯片设计公司。成立4年多来,员工总数与设计人员大幅增长,推出多媒体应用处理器(AK3210M、AK3220M)、多媒体协处理器(A2、A6)两条产品主线,并提供多媒体手机、个人媒体播放器、无线监控、车载电话等完整解决方案。目前,安凯公司正与重庆重邮信科股份有限公司紧密合作,联合开发具有中国自主知识产权的TD-SCDMA基带处理器芯片。 安凯认为,现在中国IC设计产业的竞争如火如荼,对于本土的IC设计公司而言,想要在这样的竞争中生存和壮大,必须要在国际强手留下的生存空间中拿出有知识产权的特色产品,即注重芯片差异化特征的修炼。安凯的目标是成为全球一流的移动手持设备多媒体应用处理器的主要提供商。 设计目的: 1.掌握CMOS反相器和两级CMOS运算放大器的电路图基本原理。 2.熟练掌握并运用tanner作图软件。 3. 基本能根据仿真图对电路进行基本分析 一.CMOS反相器 1.工作原理 1).基本电路结构 2).开启电压|UTP|=UTN,且小于VDD。当uI= UIL=0V时,VTN截止,VTP导通, uO = UOH≈VDD当uI =UIH = VDD ,VTN导 通,VTP截止,uO =UOL≈0V 3.)工作特点 VTP和VTN总是一管导通而另一管截止,流过 VTP和VTN的静态电流极小(纳安数量级),因而 CMOS反相器的静态功耗极小。这是CMOS电路最 突出的优点之一。 2.用Tanner仿真 1)cmos反相器电路图 2)反相器 瞬时分析 生成t-spice文件如下: 进行仿真: 仿真状态窗口: 仿真结果报告文件: 3)反 相器 瞬时 分析 在 W-Ed it中 观看 仿真 结果 4)反相 器直流 分析在 W-Edit 中观看 仿真结 果 3.用Tanner画CMOS反相器版图 二.两级CMOS运算放大器设计 设计原理分析: 单级有源负载差动放大器的增益一般可达几十到几百倍左右。但作为运算放大器,这个增益是不够的,因此还需要多级级联。下面我们来分析两级CMOS运算放大器。 两级CMOS运算放大器的基本电路图如下: V 9 V 3U r I D3 I D1 V 1 V 4U i I D4I D2V 2 V 5 U DD ?à??213¥C c A U o I SS V 8 V 7 V 6 U SS 图一 电路图 下面我们根据题设指标,tanner 下进行仿真,并进行分析: 已知: K N=μn C ox=25 μA /V2, K P=μpCox=12.5 μA /V2, Cc=5 pF ,功耗Pm ≤10 mW ,U DD=9 V , λN=0.01 V-1,λP=0.015 V-2,U TH=1V 。 要求:Aud>5000,单位增益带宽GB=3MHz ,压摆率SR=2V/us 。 1. 根据总功率Pm=10mW ,Udd=9V ,可求出允许总电流I=Pm/Udd=1100uA 2. 根据压摆率SR=2V/us,算出第一级偏置电流Iss. SR=Io1(max)/Cc ,Io1=Id4-Id2=Id1-Id2,Id1最大值为Iss,Id2最小值为0,故Io1(max)=Iss 。Iss=SR*Cc=10uA 。 区Iss=100uA,Id1q=Id2=50uA. 741 运算放大器 2063A JRC杜比降噪 20730 双功放 24C01AIPB21 存储器 27256 256K-EPROM 27512 512K-EPROM 2SK212 显示屏照明 3132V 32V三端稳压 3415D 双运放 3782M 音频功放 4013 双D触发器 4017 十进制计数器/脉冲分配器4021 游戏机手柄 4046 锁相环电路 4067 16通道模拟多路开关 4069 游戏机手柄 4093 四2输入施密特触发器 4098 41256 动态存储器 52432-01 可编程延时电路 56A245 开关电源 5G0401 声控IC 5G673 八位触摸互锁开关 5G673 触摸调光 5G673 电子开关 6116 静态RAM 6164 静态RAM 65840 单片数码卡拉OK变调处理器7107 数字万用表A/D转换器74123 单稳多谐振荡器 74164 移位寄存器 7474 双D触发器 7493 16分频计数器 74HC04 六反相器 74HC157 微机接口 74HC4053 74HCU04 六反相器 74LS00 与门 74LS00 4*2与非门 74LS00 四2与非门 74LS00 与门 74LS04 6*1非门 74LS08 4*2与门 74LS11 三与门 74LS123 双单稳多谐振荡器 74LS123 双单稳多谐振荡器 74LS138 三~八译码器 74LS142 十进制计数器/脉冲分配器74LS154 4-16线译码器 74LS157 四与或门74LS161 四2计数器 74LS161 十六进制同步计数器 74LS161 四~二计数器 74LS164 数码管驱动 74LS18 射频调制器 74LS193 加/减计数器 74LS193 四2进制计数器 74LS194 双向移位寄存器 74LS27 4*2或非门 74LS32 四或门 74LS32 4*2或门 74LS374 八位D触发器 74LS374 三态同相八D触发器 74LS377 74LS48 7位LED驱动 74LS73 双J-K触发器 74LS74 双D触发器 74LS85 四位比较器 74LS90 计数器 75140 线路接收器 75141 线路接收器 75142A 线路接收器 75143A 线路接收器 7555 时钟发生器 79MG 四端负稳压器 8051 空调单片机 8338 六反相器 A1011 降噪 ACVP2205-26 梳状滤波视频处理 AD536 专用运放 AD558 双极型8位D-A(含基准电压)变换器AD558 双极型8位D-A(含基准电压)变换器AD574A 12比特A/D变换器 AD650 AD670 8比特A/D变换器(单电源)1995s-2、15 AD7523 D-A变换器1994x-125 AD7524 D-A变换器1994x-126 AD7533 模数转换器1994x-141 AD7533 模数转换器1995s-184 ADC0804 8比特A/D变换器1995s-2、20 ADC0809 8CH8比特A/D 1995s-2、23 ADC0833 A/D变换4路转换器1995s-2 ADC80 12比特A/D变换器1995s-2、8 ADC84/85 高速12比特A/D变换器1995s-2 AG101 手掌游戏机1993x-155 AM6081 双极型8位D-A变换器1994x-127 AMP1200 音频功放皇后1993s-104 AN115 立体声解码1991-135 AN2510S 摄象机寻象器1994x-109 AN2661NK 影碟机视频1995s-45 福州大学至诚学院 数字集成电路课程设计报告 设计题目:51型MCU数字芯片的设计与验证 班级:2班 专业:微电子 姓名:柳青 学号: 211014338 指导老师: 王仁平 教师评分: 日期: 目录 第1部分课程设计要求 ............................................... 错误!未定义书签。第2部分51型MCU数字芯片的设计过程............................... 错误!未定义书签。 2.1设计和时序约束设置..............................................错误!未定义书签。 2.2平面规划7? 2.3布局设计18? 2.4时钟树综合与后布局优化....................................... 错误!未定义书签。22.5布线...........................................................错误!未定义书签。6 2.6 DFM-可制造性设计. (30) 第3部分 Astro-Rail分析FFt芯片的功耗和电源完整性?错误!未定义书签。 3.1 Astro-Rail分析芯片的功耗流程3?5 3.2Astro-Rail分析芯片的电压降和电迁移流程37? 第4部分设计心得 ........................................................................................................................................... 41参考文献 . (42) 74ls138 摘要: 74LS138 为3 -8 线译码器,共有54/74S138和54/74LS138 两种线路结构型式,其中LS是指采用低功耗肖特基电路. 引脚图: 工作原理: 当一个选通端(G1)为高电平,另两个选通端(/(G2A)和/(G2B))为低电平时,可将地址端(A、B、C)的二进制编码在一个对应的输出端以低电平译出。利用G1、/(G2A)和/(G2B)可级联扩展成24 线译码器;若外接一个反相器还可级联扩展成32 线译码器。若将选通端中的一个作为数据输入端时,74LS138还可作数据分配器。 内部电路结构: 功能表真值表: 简单应用: 74ls139: 74LS139功能: 54/74LS139为2 线-4 线译码器,也可作数据分配器。其主要电特性的典型值如下:型号54LS139/74LS139 传递延迟时间22ns 功耗34mW 当选通端(G1)为高电平,可将地址端(A、B)的二进制编码在一个对应的输出端以低电平译出。若将选通端(G1)作为数据输入端时,139 还可作数据分配器。 74ls139引脚图: 引出端符号: A、B:译码地址输入端 G1、G2 :选通端(低电平有效) Y0~Y3:译码输出端(低电平有效74LS139内部逻辑图: 74LS139真值表: 74ls164: 164 为8 位移位寄存器,其主要电特性的典型值如下:54/74164 185mW 54/74LS164 80mW当清除端(CLEAR)为低电平时,输出端(QA -QH)均为低电平。串行数据输入端(A,B)可控制数据。当A、B任意一个为低电平,则禁止新数据输入,在时钟端(CLOCK)脉冲上升沿作用下Q0 为低电平。当A、B 有一个为高电平,则另一个就允许输入数据,并在CLOCK 上升沿作用下决定Q0 的状态。 引脚功能: CLOCK :时钟输入端CLEAR:同步清除输入端(低电平有效)A,B :串行数据输入端QA-QH:输出端 (图1 74LS164封装图) 1:什么是同步逻辑和异步逻辑? 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入x 有无变化,状态表中的每个状态都是稳定的。 异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起。 2:同步电路和异步电路的区别: 同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。 异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。 3:时序设计的实质: 时序设计的实质就是满足每一个触发器的建立/保持时间的要求。 4:建立时间与保持时间的概念? 建立时间:触发器在时钟上升沿到来之前,其数据输入端的数据从不稳定到稳定的最小时间。保持时间:触发器在时钟上升沿到来之后,其数据输入端的数据必须保持不变的最小时间。5:为什么触发器要满足建立时间和保持时间? 因为触发器内部数据的形成是需要一定的时间的,如果不满足建立和保持时间,触发器将进入亚稳态,进入亚稳态后触发器的输出将不稳定,在0和1之间变化,这时需要经过一个恢复时间,其输出才能稳定,但稳定后的值并不一定是你的输入值。这就是为什么要用两级触发器来同步异步输入信号。这样做可以防止由于异步输入信号对于本级时钟可能不满足建立保持时间而使本级触发器产生的亚稳态传播到后面逻辑中,导致亚稳态的传播。 6:什么是亚稳态?为什么两级触发器可以防止亚稳态传播? 这也是一个异步电路同步化的问题。亚稳态是指触发器无法在某个规定的时间段内到达一个可以确认的状态。使用两级触发器来使异步电路同步化的电路其实叫做“一位同步器”,他只能用来对一位异步信号进行同步。两级触发器可防止亚稳态传播的原理:假设第一级触发器的输入不满足其建立保持时间,它在第一个脉冲沿到来后输出的数据就为亚稳态,那么在下一个脉冲沿到来之前,其输出的亚稳态数据在一段恢复时间后必须稳定下来,而且稳定的数据必须满足第二级触发器的建立时间,如果都满足了,在下一个脉冲沿到来时,第二级触发器将不会出现亚稳态,因为其输入端的数据满足其建立保持时间。同步器有效的条件:第一级触发器进入亚稳态后的恢复时间+第二级触发器的建立时间< =时钟周期。 更确切地说,输入脉冲宽度必须大于同步时钟周期与第一级触发器所需的保持时间之和。最保险的脉冲宽度是两倍同步时钟周期。所以,这样的同步电路对于从较慢的时钟域来的异步信号进入较快的时钟域比较有效,对于进入一个较慢的时钟域,则没有作用。 7:系统最高速度计算(最快时钟频率)和流水线设计思想: 同步电路的速度是指同步系统时钟的速度,同步时钟愈快,电路处理数据的时间间隔越短,电路在单位时间内处理的数据量就愈大。假设Tco是触发器的输入数据被时钟打入到触发器到数据到达触发器输出端的延时时间(Tco=Tsetpup+Thold);Tdelay是组合逻辑的延时; 问答: Point out design objects in the figure such as :design, cell, reference, port, pin, net, then write a command to set 5 to net A Design: top Reference: ADD DFF Cell: U1 U2 Port: A B clk sum Pin: A B D Q Net: A B SIN Set_load 5 [get_nets A] why do we not choose to operate all our digital circuits at these low supply voltages? 答:1)不加区分地降低电源电压虽然对减少能耗能正面影响,但它绝对会使门的延时加大 2)一旦电源电压和本征电压(阈值电压)变得可比拟,DC特性对器件参数(如晶体管 阈值)的变化就变得越来越敏感 3)降低电源电压意味着减少信号摆幅。虽然这通常可以帮助减少系统的内部噪声(如串扰引起的噪声),但它也使设计对并不减少的外部噪声源更加敏感) 问道题: 1.CMOS静态电路中,上拉网络为什么用PMOS,下拉网络为什么用NMOS管 2.什么是亚阈值电流,当减少VT时,V GS =0时的亚阈值电流是增加还是减少? 3.什么是速度饱和效应 4.CMOS电压越低,功耗就越少?是不是数字电路电源电压越低越好,为什么? 5.如何减少门的传输延迟? P203 6.CMOS电路中有哪些类型的功耗? 7.什么是衬垫偏置效应。 8.gate-to-channel capacitance C GC,包括哪些部分 VirSim有哪几类窗口 3-6. Given the data in Table 0.1 for a short channel NMOS transistor with V DSAT = 0.6 V and k′=100 μA/V2, calculate V T0, γ, λ, 2|φf|, and W / L: 课程设计题目:常用基本数字集成电路应用设计 学生姓名: 学号: 院系: 专业班级: 指导教师姓名及职称: 起止时间: 课程设计评分: 常用基本数字集成电路应用设计 1.多谐振荡器概述 多谐振荡器是一种自激振荡器,它不需要输入触发信号,接通电源后就可自动输出矩形脉冲。由于矩形脉冲含有丰富的谐波分量,因此,常将矩形脉冲产生电路称为多谐振荡器。 1.1非门电路构成的多谐振荡器设计 1.1.1基本原理 门电路构成多谐振荡器 非门作为一个开关倒相器件,可用以构成各种脉冲波形的产生电路。电路的基本工作 原理是利用电容器的充放电,当输入电压达到与非门的阈值电压VT 时,门的输出状态即发生变化。因此,电路输出的脉冲波形参数直接取决于电路中阻容元件的数值。 (1)不对称多谐振荡器 非对称型多谐振荡器的输出波形是不对称的,当用TTL与非门组成时,输出脉冲宽度 tw1=RC, tw2=1.2RC, T=2.2RC 调节 R和C值,可改变输出信号的振荡频率,通常用改变C实现输出频率的粗调,改 变电位器R实现输出频率的细调。 图1为不对称多谐振荡器,为了使电路产生振荡,要求U1A和U1B两个反向器都工作在电压传输特性的转折区,即工作在放大区。 (2)对称型多谐振荡器 电路完全对称,电容器的充放电时间常数相同, 故输出为对称的方波。改变R和C的值, 可以改变输出振荡频率。非门3用于输出波形整形。 一般取R≤1KΩ?,当R1=R2=1KΩ,C1=C2=100pf~100μf时,f可在几Hz~MHz 变化。 脉冲宽度tw1=tw2=0.7RC,T=1.4RC. 图2中,U1A和U1B两个反向器之间经电容C1和C2耦合形成正反馈回路。 (3) 石英晶体稳频的多谐振荡器 当要求多谐振荡器的工作频率稳定性很高时,上述几种多谐振荡器的精度已不能满足要 求。为此常用石英晶体作为信号频率的基准。用石英晶体与门电路构成的多谐振荡器常用来 为微型计算机等提供时钟信号。 图3所示为常用的晶体稳频多谐振荡器。(a)、 (b)为TTL器件组成的晶体振荡电路;(c)、 (d)为CMOS器件组成的晶体振荡电路,一般用于电子表中,其中晶体的f0=32768Hz。 图3(c)中,门1用于振荡,门2用于缓冲整形。Rf是反馈电阻,通常在几十兆欧之 间选取,一般选22MΩ。R起稳定振荡作用,通常取十至几百千欧。C1是频率微调电容器, C2用于温度特性校正。 课程设计报告 课程名称:数字日历电路的设计 专业/班级:通信工程 姓名:王平 学号:0930******** 指导教师:栾华东 目的与要求 (1)设计基准脉冲电路产生的信号; (2)能进行年、月、日的计时以及独立的时间显示电路; (3)能进行星期的显示; (4)快速校时; (5)充分结合和利用所学的内容来完成; (6)选作内容 ○1可以进行某年某月某日的备忘预设置,到达备忘日期后,该日期可以以4Hz的频率闪动; ○2可以进行某年某月某日的备忘预设置,到达备忘日期后,报警灯闪动。 原理及方案 (1)多谐振荡器电路:这里利用了555定时器和RC组成的多谐振荡器,产生1kHz的信号。 (2)分频器电路:利用三片74LS90集成芯片构成分频器将1kHz信号分频得到1Hz的秒脉冲信号,同时再利用一片74LS90芯片得到2Hz的校时信号。 (3)校时电路:利用一个开关和或门逻辑元器件组合而成。可以分别对时间和年、月、日等进行校时。 (4)译码显示器:采用了共阴极的七段数字显示器,和译码器74LS48集成芯片组合成。 (5)时、分、秒计数电路:分别用两片74LS90集成芯片组成24进制、60进制、60进制作为时间的计数,均从0开始计数。 (6)星期计数电路:由74LS161构成的,从1开始计数到6,然后跳到8(星期日),完成一个星期的计数。 (7)年、月、日计数电路:年份的计数用4片74LS90构成104进制计数,月份由两片74LS90构成12进制并从1开始计数,而日也用74ls90构成经过数据选择器74LS151根据月份进行大月31进制、小月30进制、二月29进制的计数。 (8)备忘录预设置电路:由计数器、译码器和显示器构成可以对某日某月的设置。 (9)报警灯闪动系统:通过比较器74LS85对预设置和当前日期比较,相等时输出信号使灯闪动。 原理方框图如下: 一、CPLD CPLD是一种用户根据各自需要而自行构造逻辑功能的数字集成电路。其基本设计方法是借助集成开发软件平台,用原理图、硬件描述语言等方法,生成相应的目标文件,通过下载电缆(“在系统”编程)将代码传送到目标芯片中,实现设计的数字系统。 这里以抢答器为例讲一下它的设计(装修)过程,即芯片的设计流程。CPLD的工作大部分是在电脑上完成的。打开集成开发软件(Altera公司Max+pluxII)→画原理图、写硬件描述语言(VHDL,Verilog)→编译→给出逻辑电路的输入激励信号,进行仿真,查看逻辑输出结果是否正确→进行管脚输入、输出锁定(7128的64个输入、输出管脚可根据需要设定)→生成代码→通过下载电缆将代码传送并存储在CPLD芯片中。7128这块芯片各管脚已引出,将数码管、抢答开关、指示灯、蜂鸣器通过导线分别接到芯片板上,通电测试,当抢答开关按下,对应位的指示灯应当亮,答对以后,裁判给加分后,看此时数码显示加分结果是否正确,如发现有问题,可重新修改原理图或硬件描述语言,完善设计。设计好后,如批量生产,可直接复制其他CPLD芯片,即写入代码即可。如果要对芯片进行其它设计,比如进行交通灯设计,要重新画原理图、或写硬件描述语言,重复以上工作过程,完成设计。这种修改设计相当于将房屋进行了重新装修,这种装修对CPLD来说可进行上万次。 家庭成员:经过几十年的发展,许多公司都开发出了CPLD可编程逻辑器件。比较典型的就是Altera、Lattice、Xilinx世界三大权威公司的产品,这里给出常用芯片:Altera EPM7128S(PLCC84) Lattice LC4128V(TQFP100) Xilinx XC95108 (PLCC84) 可编程逻辑器件的两种主要类型是现场可编程门阵列(FPGA)和复杂可编程逻辑器件(CPLD)。在这两类可编程逻辑器件中,FPGA提供了最高的逻辑密度、最丰富的特性和最高的性能。现在最新的FPGA器件,如Xilinx Virtex?系列中的部分器件,可提供八百万"系统门"(相对逻辑密度)。这些先进的器件还提供诸如内建的硬连线处理器(如IBM Power PC)、大容量存储器、时钟管理系统等特性,并支持多种最新的超快速器件至器件(device-to-device)信号技术。FPGA被应用于范围广泛的应用中,从数据处理和存储,以及到仪器仪表、电信和数字信号处理等。 与此相比,CPLD提供的逻辑资源少得多 - 最高约1万门。但是,CPLD提供了非常好的可预测性,因此对于关键的控制应用非常理想。而且如Xilinx CoolRunner?系列CPLD器件需要的功耗极低,并且价格低廉,从而使其对于成本敏感的、电池供电的便携式应用(如移动电话和数字手持助理)非常理想。 在线检测指的是在不影响设备运行的条件下,对设备状况连续或定时进行的监测,通常是自动进行的。 二、时钟芯片DS12887 1 《模拟集成电路设计原理》期末考试 一.填空题(每空1分,共14分) 1、与其它类型的晶体管相比,MOS器件的尺寸很容易按____比例____缩小,CMOS电路被证明具有_较低__的制造成本。 2、放大应用时,通常使MOS管工作在_ 饱和_区,电流受栅源过驱动电压控制,我们定义_跨导_来表示电压转换电流的能力。 3、λ为沟长调制效应系数,对于较长的沟道,λ值____较小___(较大、较小)。 4、源跟随器主要应用是起到___电压缓冲器___的作用。 5、共源共栅放大器结构的一个重要特性就是_输出阻抗_很高,因此可以做成___恒定电流源_。 6、 6、由于_尾电流源输出阻抗为有限值_或_电路不完全对称_等因素,共模输入电平的变化会引起差动输出的改变。 7、理想情况下,_电流镜_结构可以精确地复制电流而不受工艺和温度的影响,实际应用中,为了抑制沟长调制效应带来的误差,可以进一步将其改进为__共源共栅电流镜__结构。 8、为方便求解,在一定条件下可用___极点—结点关联_法估算系统的极点频率。 9、与差动对结合使用的有源电流镜结构如下图所示,电路的输入电容Cin为__ CF(1-A) __。 10、λ为沟长调制效应系数,λ值与沟道长度成___反比__(正比、反比)。 二.名词解释(每题3分,共15分) 11、1、阱 解:在CMOS工艺中,PMOS管与NMOS管必须做在同一衬底上,其中某一类器件要做在一个“局部衬底”上,这块与衬底掺杂类型相反的“局部衬底”叫做阱。 2、亚阈值导电效应 解:实际上,VGS=VTH时,一个“弱”的反型层仍然存在,并有一些源漏电流,甚至当VGS 哈尔滨理工大学数字集成电路设计实验报告 学院:应用科学学院 专业班级:电科12 - 1班 学号:32 姓名:周龙 指导教师:刘倩 2015年5月20日 实验一、反相器版图设计 1.实验目的 1)、熟悉mos晶体管版图结构及绘制步骤; 2)、熟悉反相器版图结构及版图仿真; 2. 实验内容 1)绘制PMOS布局图; 2)绘制NMOS布局图; 3)绘制反相器布局图并仿真; 3. 实验步骤 1、绘制PMOS布局图: (1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层; (4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层; (7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察; 2、绘制NMOS布局图: (1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览; 3、绘制反相器布局图: (1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice 模拟; 4. 实验结果 nmos版图 电科《集成电路原理》期末考试试卷 一、填空题 1.(1分) 年,第一次观测到了具有放大作用的晶体管。 2 . ( 2 分 ) 摩 尔 定 律 是 指 。 3. 集 成 电 路 按 工 作 原 理 来 分 可 分 为 、 、 。 4.(4分)光刻的工艺过程有底膜处理、涂胶、前烘、 、 、 、 和去胶。 5. ( 4 分 ) MOSFET 可 以 分 为 、 、 、 四种基本类型。 6.(3分)影响MOSFET 阈值电压的因素有: 、 以及 。 7.(2分)在CMOS 反相器中,V in ,V out 分别作为PMOS 和NMOS 的 和 ; 作为PMOS 的源极和体端, 作为NMOS 的源极和体端。 8.(2分)CMOS 逻辑电路的功耗可以分为 和 。 9.(3分)下图的传输门阵列中5DD V V =,各管的阈值电压1T V V =,电路中各节点的初始电压为0,如果不考虑衬偏效应,则各输出节点的输出电压Y 1= V ,Y 2= V ,Y 3= V 。 DD 1 3 2 10.(6分)写出下列电路输出信号的逻辑表达式:Y 1= ;Y 2= ;Y 3= 。 A B Y 1 A B 2 3 二、画图题:(共12分) =+的电路图,要求使用的1.(6分)画出由静态CMOS电路实现逻辑关系Y ABD CD MOS管最少。 2.(6分)用动态电路级联实现逻辑功能Y ABC =,画出其相应的电路图。 三、简答题:(每小题5分,共20分) 1.简单说明n阱CMOS的制作工艺流程,n阱的作用是什么? 2.场区氧化的作用是什么,采用LOCOS工艺有什么缺点,更好的隔离方法是什么? 数字IC设计流程及工具介绍 IC的设计过程可分为两个部分,分别为:前端设计(也称逻辑设计)和后端设计(也称物理设计),这两个部分并没有统一严格的界限,凡涉及到与工艺有关的设计可称为后端设计。 前端设计的主要流程: 1、规格制定 芯片规格,也就像功能列表一样,是客户向芯片设计公司(称为Fabless,无晶圆设计公司)提出的设计要求,包括芯片需要达到的具体功能和性能方面的要求。 2、详细设计 Fabless根据客户提出的规格要求,拿出设计解决方案和具体实现架构,划分模块功能。 3、HDL编码 使用硬件描述语言(VHDL,Verilog HDL,业界公司一般都是使用后者)将模块功能以代码来描述实现,也就是将实际的硬件电路功能通过HDL语言描述出来,形成RTL(寄存器传输级)代码。 4、仿真验证 仿真验证就是检验编码设计的正确性,检验的标准就是第一步制定的规格。看设计是否精确地满足了规格中的所有要求。规格是设计正确与否的黄金标准,一切违反,不符合规格要求的,就需要重新修改设计和编码。设计和仿真验证是反复迭代的过程,直到验证结果显示完全符合规格标准。仿真验证工具Mentor 公司的Modelsim,Synopsys的VCS,还有Cadence的NC-Verilog均可以对RTL 级的代码进行设计验证,该部分个人一般使用第一个-Modelsim。该部分称为前仿真,接下来逻辑部分综合之后再一次进行的仿真可称为后仿真。 5、逻辑综合――Design Compiler 仿真验证通过,进行逻辑综合。逻辑综合的结果就是把设计实现的HDL代码翻译成门级网表netlist。综合需要设定约束条件,就是你希望综合出来的电路在面积,时序等目标参数上达到的标准。逻辑综合需要基于特定的综合库,不同的库中,门电路基本标准单元(standard cell)的面积,时序参数是不一样的。所以,选用的综合库不一样,综合出来的电路在时序,面积上是有差异的。一般来说,综合完成后需要再次做仿真验证(这个也称为后仿真,之前的称为前仿真)逻辑综合工具Synopsys的Design Compiler,仿真工具选择上面的三种仿真工具均可。 6、静态时序分析——STA Static Timing Analysis(STA),静态时序分析,这也属于验证范畴,它主要是在时序上对电路进行验证,检查电路是否存在建立时间(setup time)和保持时间(hold time)的违例(violation)。这个是数字电路基础知识,一个寄存器出现这两个时序违例时,是没有办法正确采样数据和输出数据的,所以以寄存器为基础的数字芯片功能肯定会出现问题。STA工具有Synopsys的Prime Time。 7、形式验证 数字集成电路设计 实验报告 实验名称二输入与非门的设计 一.实验目的 a)学习掌握版图设计过程中所需要的仿真软件 b)初步熟悉使用Linux系统 二.实验设备与软件 PC机,RedHat,Candence 三.实验过程 Ⅰ电路原理图设计 1.打开虚拟机VMware Workstation,进入Linux操作系统RedHat。 2.数据准备,将相应的数据文件拷贝至工作环境下,准备开始实验。 3.创建设计库,在设计库里建立一个schematic view,命名为,然后进入电路 图的编辑界面。 4.电路设计 设计一个二输入与非门,插入元器件,选择PDK库(xxxx35dg_XxXx)中的nmos_3p3、 pmos_3p3等器件。形成如下电路图,然后check and save,如下图。 图1.二输入与非门的电路图 5.制作二输入与非门的外观symbol Design->Create Cellview -> From Cellview,在弹出的界面,按ok后出现symbol Generation options,选择端口排放顺序和外观,然后按ok出现symbol编辑界面。按照需 要编辑成想要的符号外观,如下图。保存退出。 图2.与非门外观 6.建立仿真电路图 方法和前面的“建立schemtic view”的方法一样,但在调用单元时除了调用analogL 库中的电压源、(正弦)信号源等之外,将之前完成的二输入与非门调用到电路图中,如下图。 图3.仿真电路图 然后设置激励源电压输出信号为高电平为3.5v,低电平为0的方波信号。 7.启动仿真环境 在ADE中设置仿真器、仿真数据存放路径和工艺库,设置好后选择好要检测的信号在电路中的节点,添加到输出栏中,运行仿真得到仿真结果图。 数字集成电路设计流程数字集成电路设计流程 数字集成电路设计流程 1. 设计输入 电路图或硬件描述语言 2. 逻辑综合 处理硬件描述语言,产生电路网表 3. 系统划分 将电路分成大小合适的块 4. 功能仿真 State Key Lab of ASIC & Systems, Fudan University 数字集成电路设计流程 5.布图规划 芯片上安排各宏模块的位置 6.布局 安排宏模块中标准单元的位置 7.布线 宏模块与单元之间的连接 8.寄生参数提取 提取连线的电阻、电容 9.版图后仿真 检查考虑连线后功能和时序是否正确 State Key Lab of ASIC & Systems, Fudan University 数字集成电路设计工具 . 主要的EDA vendor – Synopsys:逻辑 综合,仿真器, DFT – Cadence:版图 设计工具,仿真 器等 – Avanti:版图设 计工具 – Mentor:DFT, 物理验证工具 – Magma: BlastRTL, Blast Fusion State Key Lab of ASIC & Systems, Fudan University 选择设计工具的原则 ..只用“sign-off”的工具 –保证可靠性,兼容性 ..必须针对芯片的特点 –不同的芯片需要不同的设计工具 ..了解设计工具的能力 –速度、规模等 State Key Lab of ASIC & Systems, Fudan University 设计工具的选择 ..设计输入 –任何文本编辑工具 – Ultraedit, vi, 仿真器自带编辑器… 中国最具潜力的20家芯片设计企业 2005-09-16 专题特写:《国际电子商情》创刊二十周年系列报道 春华秋实:中国IC设计业走向可持续发展之路 《国际电子商情》伴随着中国电子产业飞速发展已经走过了整整二十个不平凡的春秋,我们热切的目光也一路见证了中国IC设计业从孕育到成长,从星星之火到阵容壮大。今天,我们聚集在创刊20周年庆的舞台上,与20家中国最具代表性的IC设计公司一道,细数回顾饱含酸甜苦辣的发展历程,展现他们创立以来的丰硕成果和未来发展规划,分享业界志士们对产业环境变化的衷心感言。 诚然,中国IC产业在过去十几年取得了巨大的成就,IC设计企业已接近500家,2004年销售收入过亿元人民币的企业达到了16家之多。但是IC企业仍然有很长的路要走,一方面产品市场范围过窄,主要集中于电源管理、信号处理、视频编解码、玩具控制等几个方面,在相当一段时间里仍将提供替代性产品为主;另一方面,企业知识产权的建立与保护机制有待健全和加强。所幸的是,本土IC设计企业已然清醒认识到这些问题,正在向具有自主知识产权、自我良性循环成长的可持续发展之路迈进。 安凯开曼公司 这是一家创办于硅谷、根植于中国的芯片设计公司。成立4年多来,员工总数与设计人员大幅增长,推出多媒体应用处理器(AK3210M、AK3220M)、多媒体协处理器(A2、A6)两条产品主线,并提供多媒体手机、个人媒体播放器、无线监控、车载电话等完整解决方案。目前,安凯公司正与重庆重邮信科股份有限公司紧密合作,联合开发具有中国自主知识产权的TD-SCDMA基带处理器芯片。 安凯认为,现在中国IC设计产业的竞争如火如荼,对于本土的IC设计公司而言,想要在这样的竞争中生存和壮大,必须要在国际强手留下的生存空间中拿出有知识产权的特色产品,即注重芯片差异化特征的修炼。安凯的目标是成为全球一流的移动手持设备多媒体应用处理器的主要 数字IC设计经典笔试题 张戎王舵蒋鹏程王福生袁波 摘要 本文搜集了近年来数字IC设计公司的经典笔试题目,内容涵盖FPGA、VerilogHDL编程和IC设计基础知识。 Abstract This article includes some classical tests which have been introduced into interview by companies in digital IC designing in recent years. These tests are varied from FPGA,verlog HDL to base knowledge in IC designing. 关键词 FPGA VerilogHDL IC设计 引言 近年来,国内的IC设计公司逐渐增多,IC公司对人才的要求也不断提高,不仅反映在对相关项目经验的要求,更体现在专业笔试题目难度的增加和广度的延伸。为参加数字IC 设计公司的笔试做准备,我们需要提前熟悉那些在笔试中出现的经典题目。 IC设计基础 1:什么是同步逻辑和异步逻辑? 同步逻辑是时钟之间有固定的因果关系。异步逻辑是各时钟之间没有固定的因果关系。 同步时序逻辑电路的特点:各触发器的时钟端全部连接在一起,并接在系统时钟端,只有当时钟脉冲到来时,电路的状态才能改变。改变后的状态将一直保持到下一个时钟脉冲的到来,此时无论外部输入 x 有无变化,状态表中的每个状态都是稳定的。 异步时序逻辑电路的特点:电路中除可以使用带时钟的触发器外,还可以使用不带时钟的触发器和延迟元件作为存储元件,电路中没有统一的时钟,电路状态的改变由外部输入的变化直接引起。 2:同步电路和异步电路的区别: 同步电路:存储电路中所有触发器的时钟输入端都接同一个时钟脉冲源,因而所有触发器的状态的变化都与所加的时钟脉冲信号同步。 异步电路:电路没有统一的时钟,有些触发器的时钟输入端与时钟脉冲源相连,只有这些触发器的状态变化与时钟脉冲同步,而其他的触发器的状态变化不与时钟脉冲同步。 3:时序设计的实质: 时序设计的实质就是满足每一个触发器的建立/保持时间的要求。 4:建立时间与保持时间的概念?数字集成电路设计_笔记归纳..

家芯片设计最有潜力的公司

用集成电路设计数字模拟电路芯片

电子设计常用芯片

51型MCU数字芯片的设计与验证

数字电路常用芯片应用设计

IC数字设计

数字集成电路设计与分析

常用基本数字集成电路应用设计

数字日历电路的设计

数字芯片介绍

《模拟集成电路设计原理》期末考试

数字集成电路设计实验报告

《集成电路设计原理》试卷及答案

数字IC设计流程及工具介绍

数字ic设计实验报告

数字ic设计流程word版

20家芯片设计最有潜力的公司

数字IC设计经典笔试题