PCIE总线基础知识

与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。PCIe总线使用的层次结构与网络协议栈较为类似。

4.1.1 端到端的数据传递

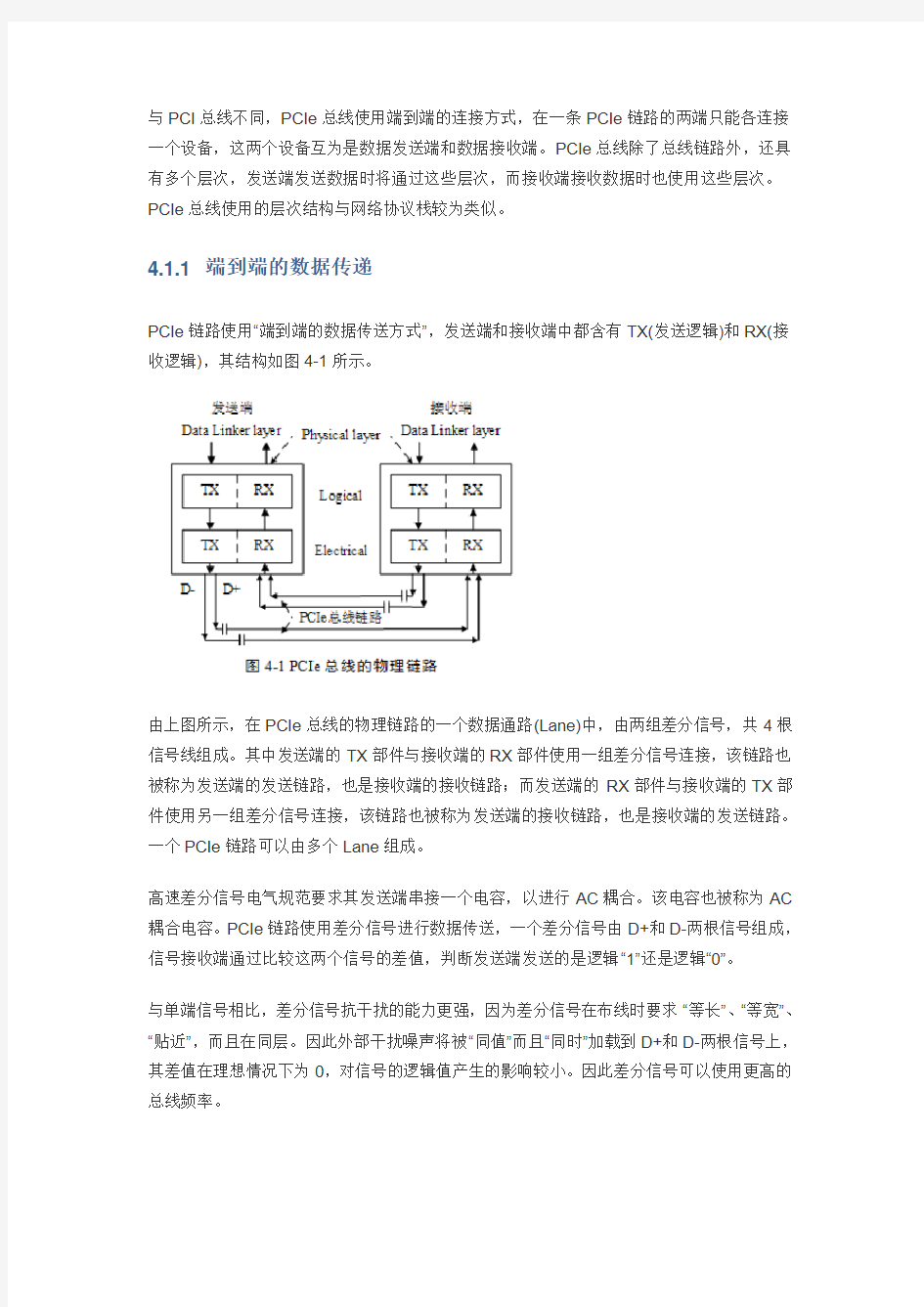

PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4-1所示。

由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe链路可以由多个Lane组成。

高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。该电容也被称为AC 耦合电容。PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。

与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。因此差分信号可以使用更高的总线频率。

此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。

PCIe链路可以由多条Lane组成,目前PCIe链路可以支持1、2、4、8、12、16和32个Lane,即×1、×2、×4、×8、×12、×16和×32宽度的PCIe链路。每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

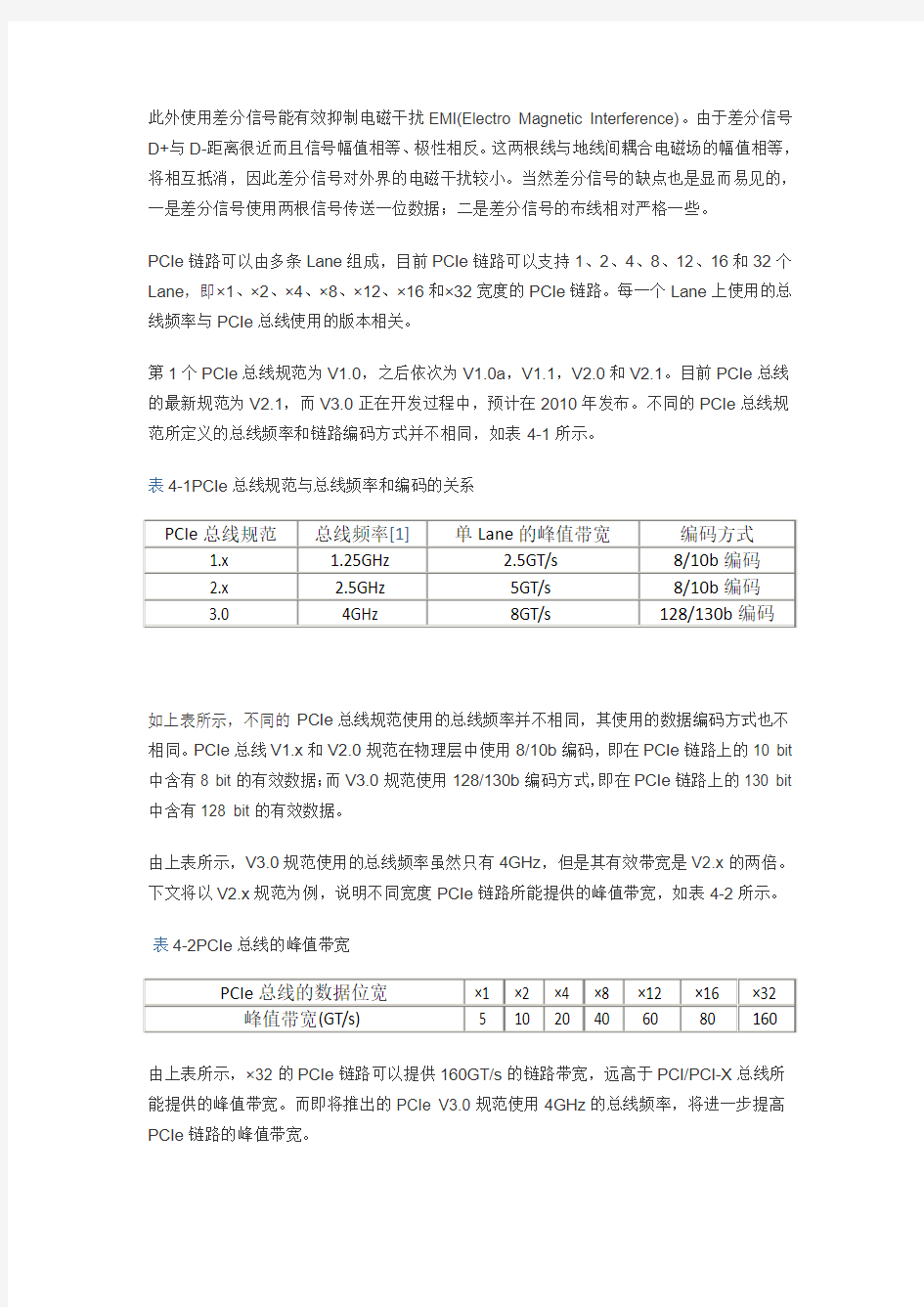

第1个PCIe总线规范为V1.0,之后依次为V1.0a,V1.1,V2.0和V2.1。目前PCIe总线的最新规范为V2.1,而V3.0正在开发过程中,预计在2010年发布。不同的PCIe总线规范所定义的总线频率和链路编码方式并不相同,如表4-1所示。

表4-1PCIe总线规范与总线频率和编码的关系

如上表所示,不同的PCIe总线规范使用的总线频率并不相同,其使用的数据编码方式也不相同。PCIe总线V1.x和V2.0规范在物理层中使用8/10b编码,即在PCIe链路上的10 bit 中含有8 bit的有效数据;而V3.0规范使用128/130b编码方式,即在PCIe链路上的130 bit 中含有128 bit的有效数据。

由上表所示,V3.0规范使用的总线频率虽然只有4GHz,但是其有效带宽是V2.x的两倍。下文将以V2.x规范为例,说明不同宽度PCIe链路所能提供的峰值带宽,如表4-2所示。

表4-2PCIe总线的峰值带宽

由上表所示,×32的PCIe链路可以提供160GT/s的链路带宽,远高于PCI/PCI-X总线所能提供的峰值带宽。而即将推出的PCIe V3.0规范使用4GHz的总线频率,将进一步提高PCIe链路的峰值带宽。

在PCIe总线中,使用GT(Gigatransfer)计算PCIe链路的峰值带宽。GT是在PCIe链路上传递的峰值带宽,其计算公式为总线频率×数据位宽×2。

在PCIe总线中,影响有效带宽的因素有很多,因而其有效带宽较难计算,这部分内容详见第8.4.1节。尽管如此,PCIe总线提供的有效带宽还是远高于PCI总线。PCIe总线也有其弱点,其中最突出的问题是传送延时。

PCIe链路使用串行方式进行数据传送,然而在芯片内部,数据总线仍然是并行的,因此PCIe 链路接口需要进行串并转换,这种串并转换将产生较大的延时。除此之外PCIe总线的数据报文需要经过事务层、数据链路层和物理层,这些数据报文在穿越这些层次时,也将带来延时。本书将在第8.4节详细讨论PCIe总线的延时与带宽之间的联系。

在基于PCIe总线的设备中,×1的PCIe链路最为常见,而×12的PCIe链路极少出现,×4和×8的PCIe设备也不多见。Intel通常在ICH中集成了多个×1的PCIe链路用来连接低速外设,而在MCH中集成了一个×16的PCIe链路用于连接显卡控制器。而PowerPC处理器通常能够支持×8、×4、×2和×1的PCIe链路。

PCIe总线物理链路间的数据传送使用基于时钟的同步传送机制,但是在物理链路上并没有时钟线,PCIe总线的接收端含有时钟恢复模块CDR(Clock Data Recovery),CDR将从接收报文中提取接收时钟,从而进行同步数据传递。

值得注意的是,在一个PCIe设备中除了需要从报文中提取时钟外,还使用了REFCLK+和REFCLK-信号对作为本地参考时钟,这个信号对的描述见下文。

4.1.2 PCIe总线使用的信号

PCIe设备使用两种电源信号供电,分别是V cc与V aux,其额定电压为3.3V。其中V cc为主电源,PCIe设备使用的主要逻辑模块均使用V cc供电,而一些与电源管理相关的逻辑使用V aux供电。在PCIe设备中,一些特殊的寄存器通常使用V aux供电,如Sticky Register,此时即使PCIe设备的V cc被移除,这些与电源管理相关的逻辑状态和这些特殊寄存器的内容也不会发生改变。

在PCIe总线中,使用V aux的主要原因是为了降低功耗和缩短系统恢复时间。因为V aux在多数情况下并不会被移除,因此当PCIe设备的V cc恢复后,该设备不用重新恢复使用V aux供电的逻辑,从而设备可以很快地恢复到正常工作状状态。

PCIe链路的最大宽度为×32,但是在实际应用中,×32的链路宽度极少使用。在一个处理器系统中,一般提供×16的PCIe插槽,并使用PETp0~15、PETn0~15和PERp0~15、PERn0~15共64根信号线组成32对差分信号,其中16对PETxx信号用于发送链路,另外16对PERxx信号用于接收链路。除此之外PCIe总线还使用了下列辅助信号。

1 PERST#信号

该信号为全局复位信号,由处理器系统提供,处理器系统需要为PCIe插槽和PCIe设备提供该复位信号。PCIe设备使用该信号复位内部逻辑。当该信号有效时,PCIe设备将进行复位操作。PCIe总线定义了多种复位方式,其中Cold Reset和Warm Reset这两种复位方式的实现与该信号有关,详见第4.1.5节。

2 REFCLK+和REFCLK-信号

在一个处理器系统中,可能含有许多PCIe设备,这些设备可以作为Add-In卡与PCIe插槽连接,也可以作为内置模块,与处理器系统提供的PCIe链路直接相连,而不需要经过PCIe 插槽。PCIe设备与PCIe插槽都具有REFCLK+和REFCLK-信号,其中PCIe插槽使用这组信号与处理器系统同步。

在一个处理器系统中,通常采用专用逻辑向PCIe插槽提供REFCLK+和REFCLK-信号,如图4-2所示。其中100Mhz的时钟源由晶振提供,并经过一个“一推多”的差分时钟驱动器生成多个同相位的时钟源,与PCIe插槽一一对应连接。

PCIe插槽需要使用参考时钟,其频率范围为100MHz±300ppm。处理器系统需要为每一个PCIe插槽、MCH、ICH和Switch提供参考时钟。而且要求在一个处理器系统中,时钟驱

动器产生的参考时钟信号到每一个PCIe插槽(MCH、ICH和Swith)的距离差在15英寸之内。通常信号的传播速度接近光速,约为6英寸/ns,由此可见,不同PCIe插槽间REFCLK+

和REFCLK-信号的传送延时差约为2.5ns。

当PCIe设备作为Add-In卡连接在PCIe插槽时,可以直接使用PCIe插槽提供的REFCLK+和REFCLK-信号,也可以使用独立的参考时钟,只要这个参考时钟在100MHz±300ppm范围内即可。内置的PCIe设备与Add-In卡在处理REFCLK+和REFCLK-信号时使用的方法类似,但是PCIe设备可以使用独立的参考时钟,而不使用REFCLK+和REFCLK-信号。

在PCIe设备配置空间的LinkControl Register中,含有一个“Common Clock Configuration”位。当该位为1时,表示该设备与PCIe链路的对端设备使用“同相位”的参考时钟;如果为0,表示该设备与PCIe链路的对端设备使用的参考时钟是异步的。

在PCIe设备中,“Common Clock Configuration”位的缺省值为0,此时PCIe设备使用的参考时钟与对端设备没有任何联系,PCIe链路两端设备使用的参考时钟可以异步设置。这个异步时钟设置方法对于使用PCIe链路进行远程连接时尤为重要。

在一个处理器系统中,如果使用PCIe链路进行机箱到机箱间的互连,因为参考时钟可以异步设置,机箱到机箱之间进行数据传送时仅需要差分信号线即可,而不需要参考时钟,从而极大降低了连接难度。

3 WAKE#信号

当PCIe设备进入休眠状态,主电源已经停止供电时,PCIe设备使用该信号向处理器系统提交唤醒请求,使处理器系统重新为该PCIe设备提供主电源V cc。在PCIe总线中,WAKE#信号是可选的,因此使用WAKE#信号唤醒PCIe设备的机制也是可选的。值得注意的是产生该信号的硬件逻辑必须使用辅助电源V aux供电。

WAKE#是一个Open Drain信号,一个处理器的所有PCIe设备可以将WAKE#信号进行线与后,统一发送给处理器系统的电源控制器。当某个PCIe设备需要被唤醒时,该设备首先置WAKE#信号有效,然后在经过一段延时之后,处理器系统开始为该设备提供主电源V cc,并使用PERST#信号对该设备进行复位操作。此时WAKE#信号需要始终保持为低,当主电源V cc上电完成之后,PERST#信号也将置为无效并结束复位,WAKE#信号也将随之置为无效,结束整个唤醒过程。

PCIe设备除了可以使用WAKE#信号实现唤醒功能外,还可以使用Beacon信号实现唤醒功能。与WAKE#信号实现唤醒功能不同,Beacon使用In-band信号,即差分信号D+和

D-实现唤醒功能。Beacon信号DC平衡,由一组通过D+和D-信号生成的脉冲信号组成。

这些脉冲信号宽度的最小值为2ns,最大值为16us。当PCIe设备准备退出L2状态(该状态为PCIe设备使用的一种低功耗状态)时,可以使用Beacon信号,提交唤醒请求。

4 SMCLK和SMDAT信号

SMCLK和SMDAT信号与x86处理器的SMBus(System Mangement Bus)相关。SMBus 于1995年由Intel提出,SMBus由SMCLK和SMDAT信号组成。SMBus源于I2C总线,但是与I2C总线存在一些差异。

SMBus的最高总线频率为100KHz,而I2C总线可以支持400KHz和2MHz的总线频率。此外SMBus上的从设备具有超时功能,当从设备发现主设备发出的时钟信号保持低电平超过35ms时,将引发从设备的超时复位。在正常情况下,SMBus的主设备使用的总线频率最低为10KHz,以避免从设备在正常使用过程中出现超时。

在SMbus中,如果主设备需要复位从设备时,可以使用这种超时机制。而I2C总线只能使用硬件信号才能实现这种复位操作,在I2C总线中,如果从设备出现错误时,单纯通过主设备是无法复位从设备的。

SMBus还支持Alert Response机制。当从设备产生一个中断时,并不会立即清除该中断,直到主设备向0b0001100地址发出命令。

上文所述的SMBus和I2C总线的区别还是局限于物理层和链路层上,实际上SMBus还含有网络层。SMBus还在网络层上定义了11种总线协议,用来实现报文传递。

SMBus在x86处理器系统中得到了大规模普及,其主要作用是管理处理器系统的外部设备,并收集外设的运行信息,特别是一些与智能电源管理相关的信息。PCI和PCIe插槽也为SMBus预留了接口,以便于PCI/PCIe设备与处理器系统进行交互。

在Linux系统中,SMBus得到了广泛的应用,ACPI也为SMBus定义了一系列命令,用于智能电池、电池充电器与处理器系统之间的通信。在Windows操作系统中,有关外部设备的描述信息,也是通过SMBus获得的。

5 JTAG信号

JTAG(Joint Test Action Group)是一种国际标准测试协议,与IEEE 1149.1兼容,主要用于芯片内部测试。目前绝大多数器件都支持JTAG测试标准。JTAG信号由TRST#、TCK、TDI、TDO和TMS信号组成。其中TRST#为复位信号;TCK为时钟信号;TDI和TDO分别与数据输入和数据输出对应;而TMS信号为模式选择。

JTAG允许多个器件通过JTAG接口串联在一起,并形成一个JTAG链。目前FPGA和EPLD 可以借用JTAG接口实现在线编程ISP(In-System Programming)功能。处理器也可以使用JTAG接口进行系统级调试工作,如设置断点、读取内部寄存器和存储器等一系列操作。除此之外JTAG接口也可用作“逆向工程”,分析一个产品的实现细节,因此在正式产品中,一般不保留JTAG接口。

6 PRSNT1#和PRSNT2#信号

PRSNT1#和PRSNT2#信号与PCIe设备的热插拔相关。在基于PCIe总线的Add-in卡中,PRSNT1#和PRSNT2#信号直接相连,而在处理器主板中,PRSNT1#信号接地,而PRSNT2#信号通过上拉电阻接为高。PCIe设备的热插拔结构如图4-3所示。

如上图所示,当Add-In卡没有插入时,处理器主板的PRSNT2#信号由上拉电阻接为高,而当Add-In卡插入时主板的PRSNT2#信号将与PRSNT1#信号通过Add-In卡连通,此时PRSNT2#信号为低。处理器主板的热插拔控制逻辑将捕获这个“低电平”,得知Add-In卡已经插入,从而触发系统软件进行相应地处理。

Add-In卡拔出的工作机制与插入类似。当Add-in卡连接在处理器主板时,处理器主板的PRSNT2#信号为低,当Add-In卡拔出后,处理器主板的PRSNT2#信号为高。处理器主板的热插拔控制逻辑将捕获这个“高电平”,得知Add-In卡已经被拔出,从而触发系统软件进行相应地处理。

不同的处理器系统处理PCIe设备热拔插的过程并不相同,在一个实际的处理器系统中,热拔插设备的实现也远比图4-3中的示例复杂得多。值得注意的是,在实现热拔插功能时,Add-in Card需要使用“长短针”结构。

如图4-3所示,PRSNT1#和PRSNT2#信号使用的金手指长度是其他信号的一半。因此当PCIe设备插入插槽时,PRSNT1#和PRSNT2#信号在其他金手指与PCIe插槽完全接触,并经过一段延时后,才能与插槽完全接触;当PCIe设备从PCIe插槽中拔出时,这两个信号首先与PCIe插槽断连,再经过一段延时后,其他信号才能与插槽断连。系统软件可以使用这段延时,进行一些热拔插处理。

4.1.3 PCIe总线的层次结构

PCIe总线采用了串行连接方式,并使用数据包(Packet)进行数据传输,采用这种结构有效去除了在PCI总线中存在的一些边带信号,如INTx和PME#等信号。在PCIe总线中,数据报文在接收和发送过程中,需要通过多个层次,包括事务层、数据链路层和物理层。PCIe 总线的层次结构如图4-4所示。

PCIe总线的层次组成结构与网络中的层次结构有类似之处,但是PCIe总线的各个层次都是使用硬件逻辑实现的。在PCIe体系结构中,数据报文首先在设备的核心层(Device Core)中产生,然后再经过该设备的事务层(Transaction Layer)、数据链路层(Data Link Layer)和

物理层(Physical Layer),最终发送出去。而接收端的数据也需要通过物理层、数据链路和事务层,并最终到达Device Core。

1 事务层

事务层定义了PCIe总线使用总线事务,其中多数总线事务与PCI总线兼容。这些总线事务可以通过Switch等设备传送到其他PCIe设备或者RC。RC也可以使用这些总线事务访问PCIe设备。

事务层接收来自PCIe设备核心层的数据,并将其封装为TLP(Transaction Layer Packet)后,发向数据链路层。此外事务层还可以从数据链路层中接收数据报文,然后转发至PCIe 设备的核心层。

事务层的一个重要工作是处理PCIe总线的“序”。在PCIe总线中,“序”的概念非常重要,也较难理解。在PCIe总线中,事务层传递报文时可以乱序,这为PCIe设备的设计制造了不小的麻烦。事务层还使用流量控制机制保证PCIe链路的使用效率。有关事务层的详细说明见第6章。

2 数据链路层

数据链路层保证来自发送端事务层的报文可以可靠、完整地发送到接收端的数据链路层。来自事务层的报文在通过数据链路层时,将被添加Sequence Number前缀和CRC后缀。数据链路层使用ACK/NAK协议保证报文的可靠传递。

PCIe总线的数据链路层还定义了多种DLLP(Data Link Layer Packet),DLLP产生于数据链路层,终止于数据链路层。值得注意的是,TLP与DLLP并不相同,DLLP并不是由TLP 加上Sequence Number前缀和CRC后缀组成的。

3 物理层

物理层是PCIe总线的最底层,将PCIe设备连接在一起。PCIe总线的物理电气特性决定了PCIe链路只能使用端到端的连接方式。PCIe总线的物理层为PCIe设备间的数据通信提供传送介质,为数据传送提供可靠的物理环境。

物理层是PCIe体系结构最重要,也是最难以实现的组成部分。PCIe总线的物理层定义了LTSSM(Link Training and Status StateMachine)状态机,PCIe链路使用该状态机管理链路状态,并进行链路训练、链路恢复和电源管理。

PCIe总线的物理层还定义了一些专门的“序列”,有的书籍将物理层这些“序列”称为

PLP(Phsical Layer Packer),这些序列用于同步PCIe链路,并进行链路管理。值得注意的是PCIe设备发送PLP与发送TLP的过程有所不同。对于系统软件而言,物理层几乎不可见,但是系统程序员仍有必要较为深入地理解物理层的工作原理。

4.1.4 PCIe链路的扩展

PCIe链路使用端到端的数据传送方式。在一条PCIe链路中,这两个端口是完全对等的,分别连接发送与接收设备,而且一个PCIe链路的一端只能连接一个发送设备或者接收设备。因此PCIe链路必须使用Switch扩展PCIe链路后,才能连接多个设备。使用Switch进行链路扩展的实例如图4-5所示。

在PCIe总线中,Switch[2]是一个特殊的设备,该设备由1个上游端口和2~n个下游端口组成。PCIe总线规定,在一个Switch中可以与RC直接或者间接相连[3]的端口为上游端口,在PCIe总线中,RC的位置一般在上方,这也是上游端口这个称呼的由来。在Switch中除了上游端口外,其他所有端口都被称为下游端口。下游端口一般与EP相连,或者连接下一级Switch继续扩展PCIe链路。其中与上游端口相连的PCIe链路被称为上游链路,与下游端口相连的PCIe链路被称为下游链路。

上游链路和下游链路是一个相对的概念。如上图所示,Switch与EP2连接的PCIe链路,对于EP2而言是上游链路,而对Switch而言是下游链路。

在上图所示的Switch中含有3个端口,其中一个是上游端口(Upstream Port),而其他两个为下游端口(Downstream Port)。其中上游端口与RC或者其他Switch的下游端口相连,而下游端口与EP或者其他Switch的上游端口相连。

在Switch中,还有两个与端口相关的概念,分别是Egress端口和Ingress端口。这两个端口与通过Switch的数据流向有关。其中Egress端口指发送端口,即数据离开Switch使用的端口;Ingress端口指接收端口即数据进入Switch使用的端口。

Egress端口和Ingress端口与上下游端口没有对应关系。在Switch中,上下游端口可以作为Egress端口,也可以作为Ingress端口。如图4-5所示,RC对EP3的内部寄存器进行写操作时,Switch的上游端口为Ingress端口,而下游端口为Egress端口;当EP3对主存储器进行DMA写操作时,该Switch的上游端口为Egress端口,而下游端口为Ingress端口。

PCIe总线还规定了一种特殊的Switch连接方式,即Crosslink连接模式。支持这种模式的Switch,其上游端口可以与其他Switch的上游端口连接,其下游端口可以与其他Switch的下游端口连接。

PCIe总线提供CrossLink连接模式的主要目的是为了解决不同处理器系统之间的互连,如图4-6所示。使用CrossLink连接模式时,虽然从物理结构上看,一个Switch的上/下游端口与另一个Switch的上/下游端口直接相连,但是这个PCIe链路经过训练后,仍然是一个端口作为上游端口,而另一个作为下游端口。

处理器系统1与处理器系统2间的数据交换可以通过Crosslink进行。当处理器系统1(2)访问的PCI总线域的地址空间或者Requester ID不在处理器系统1(2)内时,这些数据将被Crosslink端口接收,并传递到对端处理器系统中。Crosslink对端接口的P2P桥将接收来自另一个处理器域的数据请求,并将其转换为本处理器域的数据请求。

使用Crosslink方式连接两个拓扑结构完全相同的处理器系统时,仍然有不足之处。假设图4-6中的处理器系统1和2的RC使用的ID号都为0,而主存储器都是从0x0000-0000开始编址时。当处理器1读取EP2的某段PCI总线空间时,EP2将使用ID路由方式,将完

成报文传送给ID号为0的PCI设备,此时是处理器2的RC而不是处理器1的RC收到EP2的数据。因为处理器1和2的RC使用的ID号都为0,EP2不能区分这两个RC。

由上所述,使用Crosslink方式并不能完全解决两个处理器系统的互连问题,因此在有些Switch中支持非透明桥结构。这种结构与PCI总线非透明桥的实现机制类似,本章对此不做进一步说明。

使用非透明桥仅解决了两个处理器间数据通路问题,但是不便于NUMA结构对外部设备的统一管理。PCIe总线对此问题的最终解决方法是使用MR-IOV技术,该技术要求Switch 具有多个上游端口分别与不同的RC互连。目前PLX公司已经可以提供具有多个上游端口的Switch,但是尚未实现MR-IOV技术涉及的一些与虚拟化相关的技术。

即便MR-IOV技术可以合理解决多个处理器间的数据访问和对PCIe设备的配置管理,使用PCIe总线进行两个或者多个处理器系统间的数据传递仍然是一个不小问题。因为PCIe总线的传送延时仍然是制约其在大规模处理器系统互连中应用的重要因素。

培训资料-印刷制版基础知识

印刷、制版基础知识 第一节印刷基本知识 一、印刷的五大要素 1.原稿:原稿是整个制版、印刷工艺中的依据,直接关系到印刷品的艺术效果和复制还原效果。凹印制版常见原稿有:黑稿、彩稿、印刷品原稿、摄影原稿、设计光盘原稿等。 2.印版:印版即提供印刷用的模版,它是由原稿到印刷品的印刷过程中重要的媒介物。印版因着墨和不着墨部分的结构形式不同而分为凸版、凹版、平版和孔版四类。其功能是根据原稿,区分出图文部分与非图文部分,使非图文部分形成空白不接受油墨,而图文部分则接受油墨,在印刷时,使附着油墨的图文转移到承印物的表面,从而完成一色的印刷。 3.油墨:油墨是获得印刷图文的主要材料之一,是体现原稿色彩的重要因素。油墨的种类很多,主要根据印版种类、印刷形式、承印材料的不同而区分,凹版包装印刷油墨主要有里印油墨、表印油墨两大类,其中里印油墨又可分为PVC用油墨、OPP用油墨、PET用油墨等。 4.承印材料:承印材料指印刷过程中承载图文墨色的材料。凹版包装印刷的承印材料主要有纸张、薄膜、铝箔等。薄膜又包括聚乙烯(PE)、聚丙烯(PP)、聚氯乙烯(PVC)、聚脂(PET)等。 5.印刷设备:印刷设备主要指印刷、复合等机械,是实现印刷品生产的关键。 二、印刷种类 1.凸版印刷:凸版印刷简称凸印,俗称铅印,历史最久。目前我国印刷行业采用较多的活字版和铜锌版印刷。 2.凹版印刷:凹版印刷简称凹印,其图 文部分低于印版表面的空白部分。我国 的软包装印刷主要是采用凹版印刷。右 图为凹版印刷方式图解。 3.平版印刷:其印版上的图文和空白两 部分几乎处在同一平面上,故称为平版 印刷。胶印是常见的平版印刷方式。平 版印刷不是直接印刷,而间接印刷。 4.孔版印刷:孔版属于透过性印刷,利用细金属网透空的特性,将图文部分镂空而非图文部分以抗墨性胶质体保护,油墨置于版面上以刮版刮压,油墨透过镂空的图文部分转移到承印物上。常见的孔版印刷方式是丝网印刷,现在仍然应用广泛。 第二节凹版印刷的特点及国内凹印的发展 一、凹版印刷的特点 1.墨层厚实,墨色均匀。凹印能真实再现原稿效果,层次丰富、清晰,墨层厚实,墨色饱和度高,色泽鲜艳明亮,这是由凹印的特点所决定的。凹版印刷采用的是网穴结构,依靠墨量体积不同来表现层次。 2.印刷速度快?。现代凹版印刷机均采用圆压圆形式,特别是卷筒式凹版印刷机,印版滚筒和压印滚筒上没有空档,机器运转平稳,采用微机自动控制,印刷速度最高可达250米/分钟。 3.适应介质广泛。凹印适用的介质非常广,PVC、PET、PE、NY、CPP、OPP、BOPP、组合膜以及其它与以上材料有相同性质的薄膜类、纸张,甚至铝箔等。 4.产品适应范围广。通过选用不同的油墨,可以在纸张、塑料薄膜、纺织品、铝箔、玻璃纸等各种材料上印刷。凹版印刷机可以和柔印、丝印、烫印、凹凸压印、分切等多种工序组成自动化

PCIE基础知识

PCIe总线概述 随着现代处理器技术的发展,在互连领域中,使用离速差分总线替代并行总线是大势所趋。与单端并行信号相比,高速差分信号可以使用更高的时钟频率,从而使用更少的信号线, 完成之前需要许多单端并行数据信号才能达到的总线带宽。 PCI总线使用并行总线结构,在同一条总线上的所有外部设备共享总线带宽,而PCIe 总线使用了鬲速差分总线,并釆用端到端的连接方式,因此在每一条PCIe链路中只能连接两个设备。这使得PCIe与PCI总线釆用的拓扑结构有所不同。PCIe总线除了在连接方式上与PCI总线不同之外,还使用了一些在网络通信中使用的技术,如支持多种数据路由方式,基于多通路的数据传递方式,和基于报丈的数据传送方式,并充分考虑了在数据传送中出现服务质量QoS (Qual ity of Service)问题。 PCIe总线的基础知识 与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。PCIe 总线使用的层次结构与网络协议栈较为类似。 端到端的数据传递 PCIe链路使用“端到端的数据传送方式”.发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4-1所示。

Da" Linker layer “ Ph 、sical layer ■ Data Linker la^^r 图41PCIe 总线的物理链蒋 由上图所示,在PCIe 总线的物理链路的一个数扌居通路(Lane)中,由两组差分信号,共4根 信号线组成。其中发送端的TX 部件与接收端的RX 部件使用一组差分信号连接,该链路也被 称为发送端的发送链路,也是接收端的接收链路:而发送端的RX 部件与接收端的TX 部件使 用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个 PCIe 链路可以由多个Lane 组成。 离速差分信号电气规范要求其发送端串接一个电容,以进行AC 耦合。该电容也被称为AC 耦合电容。PCIe 链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成, 信号接收端通过比较这两个信号的差值,判斯发送端发送的是逻辑“1”还是逻辑“0”。 与单端信号相比,差分信号抗千扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、 “贴近”,而且在同层。因此外部干扰噪声将被“同值”而且“同吋”加载到D+和D-两根信 号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。因此差分信号可以使用 更商的总线频率。 此外使用差分信号能有效抑制电磁干扰EMI (Electro Magnetic Interference) o 由于差分 信号D+与D-距离很近而且信号幅值相等.极性相反。这两根线与地线间耦合电磁场的幅值 相等,将相互抵消,因此差分信号对外界的电触千扰较小。当然差分信号的缺点也是显而易 见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。 PCIe 链路可以由多条Lane 组成,目前PCIe 链路可以支持1、2. 4. 8、12、16和32个Lane, 即X1、X2、X4、X8、X12. X16和X32宽皮的PCIe 链路。每一个Lane 上使用的总线 频率与PCIe 总线使用的版本相关。 第1个PCIe 总线规范为,之后依次为… 和。目前PCIe 总线的置新规范为,而正在开发过 程中,预计在2010年发布。不同的PCIe 总线规范所定义的总线频率和链路编码方式并不相 同,如表4T 所示。

汽车CAN总线基础知识培训资料

汽车C A N总线基础知 识

CAN总线协议 控制器局域网总线(CAN,Controller Area Network)是一种用于实时应用的串行通讯协议总线,它可以使用双绞线来传输信号,是世界上应用最广泛的现场总线之一。CAN协议用于汽车中各种不同元件之间的通信,以此取代昂贵而笨重的配电线束。该协议的健壮性使其用途延伸到其他自动化和工业应用。CAN协议的特性包括完整性的串行数据通讯、提供实时支持、传输速率高达1Mb/s、同时具有11位的寻址以及检错能力。 CAN总线发展 控制器局域网CAN( Controller Area Network)属于现场总线的范畴,是一种有效支持分布式控制系统的串行通信网络。是由德国博世公司在20世纪80年代专门为汽车行业开发的一种串行通信总线。而且能够检测出产生的任何错误。当信号传输距离达到10km时,CAN仍可提供高达50kbit/s的数据传输速率。CAN总线的工作原理 CAN总线使用串行数据传输方式,可以1Mb/s的速率在40m的双绞线上运行,也可以使用光缆连接,而且在这种总线上总线协议支持多主控制器。[1]CAN与I2C总线的许多细节很类似,但也有一些明显的区别。当CAN总线上的一个节点(站)发送数据时,它以报文形式广播给网络中所有节点。对每个节点来说,无论数据是否是发给自己的,都对其进行接收。每组报文开头的11位字符为标识符,定义了报文的优先级,这种报文格式称为面向内容的编址方案。在同一系统中标识符是唯一的,不可能有两个站发送具有相同标识符的报文。当几个站同时竞争总线读取时,这种配置十分重要。

当一个站要向其它站发送数据时,该站的CPU将要发送的数据和自己的标识符传送给本站的CAN芯片,并处于准备状态;当它收到总线分配时,转为发送报文状态。CAN芯片将数据根据协议组织成一定的报文格式发出,这时网上的其它站处于接收状态。每个处于接收状态的站对接收到的报文进行检测,判断这些报文是否是发给自己的,以确定是否接收它。由于CAN总线是一种面向内容的编址方案,因此很容易建立高水准的控制系统并灵活地进行配置。我们可以很容易地在CAN总线中加进一些新站而无需在硬件或软件上进行修改。当所提供的新站是纯数据接收设备时,数据传输协议不要求独立的部分有物理目的地址。它允许分布过程同步化,即总线上控制器需要测量数据时,可由网上获得,而无须每个控制器都有自己独立的传感器。 CAN总线在空闲(没有节点传输报文)时是一直处于隐性状态。当有节点传输报文时显性覆盖隐性,由于CAN总线是一种串行总线,也就是说报文是一位一位的传输的,而且是数字信号(0和1),1代表隐性,0代表显性。在传送报文的过程中是显隐交替的,就像二进制数字0101001等,这样就能把信息发送出去,而总线空闲的时候是一直处于隐性的。 CAN总线特征 (1)报文(Message)总线上的数据以不同报文格式发送,但长度受到限制。当总线空闲时,任何一个网络上的节点都可以发送报文。 (2)信息路由(Information Routing)在CAN中,节点不使用任何关于系统配置的报文,比如站地址,由接收节点根据报文本身特征判断是否接收这帧信息。因此系统扩展时,不用对应用层以及任何节点的软件和硬件作改变,可以直接在CAN中增加节点。

凹印版辊的基本知识综述

上世纪90年代初,受国内包装市场飞速发展和国际 制版先进设备迅速更新的影响,制版设备与技术得到快速发展,制版企业遍地开花,版材市场供不应求。90年代中后期,随着计算机的普及与性能提高,制版质量大幅提高,制版周期不断缩短。经历了近20年的高速发展,我国软包装制版行业也经历了一个不断发展的过程。 俗话说,印刷品质量“三分在印刷,七分靠制版”。那么,当前我国塑料软包装行业制版技术如何?其市场状况怎 样?印刷制版过程中需要注意哪些问题?本期技术专题,编辑部将和您一起关注制版的相关技术。 凹版印刷作为印刷工艺的一种,以其印制品墨层厚实,颜色鲜艳、饱和度高、印版耐印率高、印品质量稳定、印刷速度快等优点在印刷包装及图文出版领域内占据极其重要 的地位。从应用情况来看,在国外,凹印主要用于杂志、产品目录等精细出版物,包装印刷和钞票、邮票等有价证券的印刷,而且也应用于装饰材料等特殊领域;在国内,凹印则主要用于软包装印刷,随着国内凹印技术的发展,也已经在纸张包装、木纹装饰、皮革材料、药品包装上得到广泛应用,

运城制版有限公司就是一家在各个领域均有水准的专业制 版公司,其使用的设备均从德国或瑞士进口,其生产的各种凹印版辊质量在全国都是首屈一指的,其生产的凹印版辊已有部分向国外出口。近年来,凹印版辊印刷大量采用醇溶性油墨和水性油墨、UV油墨,既符合了国家绿色环保印刷的要求,又能适应薄膜、复合材料、纸张等多种介质,因而在包装印刷领域保持了常胜不衰的局面,成为国内印刷行业中不可或缺的重要一员。 凹印版辊的制作工艺,从其发展的过程来看,有多种工艺选择,分别是碳素纸照相法、直接加网法、胶凹印转换电子雕刻、数字电子雕刻、激光雕刻后腐蚀、激光直接雕刻等等。在此,我主要谈谈其中目前最重要也是应用最广泛的电子雕刻凹印版辊的制作。 从凹印版辊的制作流程来看,主要有以下步骤:印版基体制作、印版辊筒镀铜处理、原稿(或设计)图像文件制作、印版图像电子雕刻制作、印版辊筒镀铬。其中,印版基体制作及印版镀铜辊筒处理是与原稿(或设计)图像文件制作是同步进行的,当印版镀铜辊筒处理与原稿(或设计)图像文件制作完成后,才可进行印版图像电子雕刻制作,最后印版镀铬,至此完成印版的全部制作过程。

计算机基础知识及答案(二)

计算机基础知识及答案( 二) 1 微型计算机采用的是冯? 诺依曼体系结构,其硬件系统由运算器、控制器、存储器、输入设备和 ___C___ 五部分组成。 A 键盘、鼠标器。 B 显示器、打印机。 C 输出设备。 D 系统总线。 2、在微型计算机中,其核心部件中央处理器CPU 被称之为—D—。 A关键部件。B主要部件。C必备部件。D微处理器MPU(Micro ProcessingUnit) 。 3、微处理器把运算器和__A ___ 集成在一块很小的硅片上,是一个独立的部件。 A 控制器。 B 内存储器。 C 输入设备。 D 输出设备。 4、微型计算机的基本构成有两个特点:一是采用微处理器,二是采用___D___ 。 A 键盘和鼠标器作为输入设备。 B 显示器和打印机作为输出设备。CROM 和RAM 乍为主存储器。D 总线系统。 5、根据微型计算机硬件构成的特点,可以将其硬件系统具体化为由微处理器、内存储器、接口电路、I/O 设备和__D ___ 组成。 A 键盘、鼠标器。 B 显示器、打印机。 C 外围设备。 D 总线系统。 6、在微型计算机系统组成中,我们把微处理器CPU 只读存储器ROM 和随机存储器RAME 部分统称为___D___ 。 A 硬件系统。 B 硬件核心模块。 C 微机系统。 D 主机。 7、微型计算机使用的主要逻辑部件是___D___ 。 A 电子管。 B 晶体管。 C 固体组件。 D 大规模和超大规模集成电路。 8、在微型计算机中,通常把输入/输出设备,统称为__D _____ 。

ACPU B 存储器。C 操作系统。D 外部设备。 9、下面是关于微型计算机总线的描述,正确的有___C___ 。 A 总线系统由系统总线、地址总线、数据总线和控制总线组成。 B 总线系统由接口总线、地 址总线、数据总线和控制总线组成。C系统总线由地址总线、数据总线和控制总线组成。D 地址总线、数据总线和控制总线的英文缩写分别为DB AB CBo 10、微型计算机的系统总线是CPU与其它部件之间传送D信息的公共通道。 A输入、输出、运算。B输入、输出、控制。C程序、数据、运算。D数据、地址、控制。 11、CPU与其它部件之间传送数据是通过A实现的。 A数据总线。B地址总线。C控制总线。D数据、地址和控制总线三者。 12、下面是关于数据总线(Data Bus )的描述,不正确的是_D ____________ 。 A数据总线用来传送数据信息。B数据总线的位数,决定了CPU 一次能够处理的数据的位数。CMPU H次能够处理的数据的位数称为字长。D字长越长的CPU处理信息所需的时间越长。 13、CPU与其它部件之间传送地址是通过B实现的。 A数据总线。B地址总线。C控制总线。D数据、地址和控制总线三者。 14、下面是关于地址总线(Address Bus )的描述,不正确的是_D _____________ 。 A地址总线用来传送地址信息。B地址总线的根数,决定了CPU可访问的内存最大范围。C若地址总线为n根,则该微处理器可访问内存的最大范围是2的n次方。D拥有32根地址总线的微处理 器,其可访问内存的最大范围是4000M 15、CPU与其它部件之间传送控制信号是通过_________ C_实现的。 A数据总线。B地址总线。C控制总线。D数据、地址和控制总线三者。

凹版印刷知识考试题库

凹版印刷知识考试题库 一、填空题: 1.油墨的主要成分包含{颜料}、{树脂{连接料}}、{助剂}、{溶剂}。 2.员工更换或研磨刮刀时,要{戴防割手套},更换下来的废弃刀片要放入{废刮刀专用桶}内,不得{随意丢入垃圾箱},以免割伤他人。 3.电眼间距的检测必须在每一卷的自检中进行,用{钢尺}测出一个版周的实际数值,,目测预估到小数点后一位,除以一个版周里的{版数},得到的数值即为电眼间距值。该数值必须控制在工作标准书所示Pitch值的允差范围之内。如有超出,须{及时调整相关生产参数)。 4.压胴使用过程中出现异常,由机台人员及时提出异常现象,用{油性笔}做好标示并提供{印刷异常样品},并填写{废压胴单}交带班主管签字后交版库,以便及时研磨修缮。 5.印刷过程中出现较严重品质异常,领机应首先{处理异常},然后{夹条标示}并{在流程单及MES 系统上注明},且应送{检品}复卷确认,视情况{整版不良去除或注明哪几条单条报废}。 6.在自检中油墨附着性用{24mm}宽的透明胶带粘在印刷面的油墨上,再以{1m/秒}的速度匀速撕下胶带,膜上的油墨{90%}未被粘下为合格,否则作异常提报。 7.常说的“5S”包含{整理}、{整顿}、{清洁}、{清扫}、{教养}五项。 8.印刷时色差有个标准范围,在标准范围内可以正常出货,而一旦超出这个范围,则就有可能报废。我们所说的这个范围是:dH{≤1.0}、dE{≤3.0}以内。 9.版胴不良的确认必须由领机提报给{带班主管}确认,提供{异常留样}并填写{版胴异常提报单},由{带班主管}签名,同时必须知会{版库人员},便于分析、判别、处理、改善版胴存在的问题。 10.诺克尔粘度仪控制面板上有两行显示粘度的数值,其中上面一行数字代表{油墨的实际粘度}。 11.我们常用色差仪检测在制品与标准样品之间的颜色差别程度,美能达CR-10色差仪上的dH、dC、dL、dE都代表不同的含义。其中dH数值后会跟有一个字母,此字母表明的是:与基准色相比较被测色在哪个方面发生了改变:“R”代表{偏红}、“B”代表{偏兰}、“Y”代表{偏黄}、“P”代表{偏紫}、“G”代表{偏绿}。 12.首自检取样数量要求{≥2版周},取样频次要求{每卷}取样1次。 13.为保证生产顺畅,交接班时,交班方至少给接班方准备{2H}生产的原物料;如果是换单交班的,则须完成{新订单的领料}。 14.半制品所用纸管应与原膜宽度相同,最长不能长出半成品{2cm}。 15.现场人员设备保养项目包括{清洁}、{检查}、{给油}三项。 16.版胴在上机前,应根据{排程}、{送版单}、{版套标示}、{版顶版号}进行确认。 17.上版时必须根据《工作指示单》要求,先确认印刷半成品{出卷方向},进而确定装版方向。 18.异常原因细部分析中的5M1E是指:{人}、{机器}、{材料}、{方法}、{环境}、{测量}。 19.《印刷制程检验标准》上规定,双向拉伸类薄膜:主要图案套色偏差{≤0.20mm},次要图案{≤0.35mm}。 20.印刷机的张力系统包含{印前张力}、{印后张力}、{收卷张力}、{放卷张力}、{收卷牵引辊张力}、{放卷牵引辊张力}六部分。 21.印刷时所用的单元机组都要打开加热开关,以便油墨及时干燥。那么设定温度时需要考虑{印刷面积的大小}、{印刷速度的快慢}、{印刷材质的不同}三个因素。 22.蒸煮油墨中添加固化剂的作用是{增加油墨的附着力}。 23.印刷机正常停机时,应先降速至{50 }m/min以下,再按停机按钮。 24.印刷首检的八项管制重点是:{外观}、{颜色准确性}、{条码正确性}、{图案文字正确性}、{出

计算机基础知识及答案二

----- 计算机基础知识及答案(二) 1、微型计算机采用的是冯·诺依曼体系结构,其硬件系统由运 算器、控制器、存储器、输 入设备和___C___五部分组成。 A 键盘、鼠标器。 B 显示器、打印机。 C 输出设备。 D 系统 总线。 2、在微型计算机中,其核心部件中央处理器CPU,被称之为 ___D___。 A 关键部件。 B 主要部件。C必备部件。D 微处理器 MPU(Micro Processing Unit)。 、微处理器把运算器和3集成在一块很小的硅片上,是一个独立的 部件。__A____ A 控制器。 B 内存储器。 C 输入设备。D输出设备。 4、微型计算机的基本构成有两个特点:一是采用微处理器,二

是采用___D___。 显示器和打印机作为输出设备。键盘和鼠标器作为输入设备。B A CROM和RAM作为主存储器。 总线系统。D 、根据微型计算机硬件构成的特点,可以将其硬件系统具体化为由微处理器、内存储器、5 组成。I/O 设备和__D____接口电路、 显示器、打印机。B A 键盘、鼠标器。总线系统。 D C 外围设备。 CPU、在微型计算机系统组成中,我们把微处理器6、只读存储器ROM和随机存储器RAM三 。部分统称为___D___ 主机。微机系统。 B 硬件系统。硬件核心模块。C D A 、微型计算机使用的主要逻辑部件是7。___D___ A 电子管。 B 晶体管。 C 固体组件。 D 大规模和超大规模集成电路。

8、在微型计算机中,通常把输入/ 输出设备,统称为__D____。ACPU。B 存储器。C操作系统。 D 外部设备。 9、下面是关于微型计算机总线的描述,正确的有___C___。 ----- ----- A 总线系统由系统总线、地址总线、数据总线和控制总线组成。 B 总线系统由接口总线、地 D系统总线由地址总线、数据总线和控制总线组成。C 址总线、数据总线和控制总线组成。 地址总线、数据总线和控制总线的英文缩写分别为DB、AB,CB。 10、微型计算机的系统总线是CPU与其它部件之间传___D___信息的公共通道。 送 A 输入、输出、运算。 B 输入、输出、控制。 C 程序、数据、运算。 D 数据、地址、控制。

PCI-Express总线基础知识

PCIe总线的基础知识 与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。PCIe 总线使用的层次结构与网络协议栈较为类似。 4.1.1 端到端的数据传递 PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4?1所示。 由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe链路可以由多个Lane组成。 高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。该电容也被称为AC 耦合电容。PCIe链路使用差分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。 与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。因此差分信号可以使用更高的总线频率。 此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。

现场总线基础知识

现场总线基础知识 现场总线技术综述 现场总线(Fieldbus)是80年代末、90年代初国际上发展形成的,用于过程自动化、制造自动化、楼宇自动化等领域的现场智能设备互连通讯网络。它作为工厂数字通信网络的基础,沟通了生产过程现场及控制设备之间及其与更高控制管理层次之间的联系。它不仅是一个基层网络,而且还是一种开放式、新型全分布控制系统。这项以智能传感、控制、计算机、数字通讯等技术为主要内容的综合技术,已经受到世界范围的关注,成为自动化技术发展的热点,并将导致自动化系统结构与设备的深刻变革。国际上许多实力、有影响的公司都先后在不同程度上进行了现场总线技术与产品的开发。现场总线设备的工作环境处于过程设备的底层,作为工厂设备级基础通讯网络,要求具有协议简单、容错能力强、安全性好、成本低的特点。 具有一定的时间确定性和较高的实时性要求,还具有网络负载稳定,多数为短帧传送、信息交换频繁等特点。由于上述特点,现场总线系统从网络结构到通讯技术,都具有不同上层高速数据通信网的特色。 一般把现场总线系统称为第五代控制系统,也称作FCS——现场总线控制系统。人们一般把50年代前的气动信号控制系统PCS称作第一代,把4~20mA等电动模拟信号控制系统称为第二代,把数字计算机集中式控制系统称为第三代,而把70年代中期以来的集散式分布控制系统DCS称作第四代。现场总线控制系统FCS作为新一代控制系统,一方面,突破了DCS系统采用通信专用网络的局限,采用了基于公开化、标准化的解决方案,克服了封闭系统所造成的缺陷;另一方面把DCS的集中与分散相结合的集散系统结构,变成了新型全分布式结构,把控制功能彻底下放到现场。可以说,开放性、分散性与数字通讯是现场总线系统最显著的特征。 现场总线技术在历经了群雄并起,分散割据的初始阶段后,尽管已有一定范围的磋商合并,但至今尚未形成完整统一的国际标准。其中有较强实力和影响的有:FoudationFieldbus (FF)、LonWorks、Profibus、HART、CAN、Dupline等。它们具有各自的特色,在不同应用领域形成了自己的优势。本文将在简要描述现场总线技术特点的基础,紧扣系统的可靠性、实用性等,介绍现场总线网络结构、体系结构等关键技术及目前较为流行的几种有实力的现场总线技术的现状,最后阐述现场总线的发展趋势与技术展望。 一、现场总线的技术特点 1、系统的开放性。开放系统是指通信协议公开,各不同厂家的设备之间可进行互连并实现信息交换,现场总线开发者就是要致力于建立统一的工厂底层网络的开放系统。这里的开放是指对相关标准的一致、公开性,强调对标准的共识与遵从。一个开放系统,它可以与任何遵守相同标准的其它设备或系统相连。一个具有总线功能的现场总线网络系统必须是开放的,开放系统把系统集成的权利交给了用户。用户可按自己的需要和对象把来自不同供应商的产品组成大小随意的系统。 2、互可操作性与互用性,这里的互可操作性,是指实现互连设备间、系统间的信息传送与沟通,可实行点对点,一点对多点的数字通信。而互用性则意味着不同生产厂家的性能类似的设备可进行互换而实现互用。 3、现场设备的智能化与功能自治性。它将传感测量、补偿计算、工程量处理与控制等

凹印版辊的基本知识

上世纪90年代初,受国内包装市场飞速发展和国际制版先进设备迅速更新的影响,制版设备与技术得到快速发展,制版企业遍地开花,版材市场供不应求。90年代中后期,随着计算机的普及与性能提高,制版质量大幅提高,制版周期不断缩短。经历了近20年的高速发展,我国软包装制版行业也经历了一个不断发展的过程。 俗话说,印刷品质量“三分在印刷,七分靠制版”。那么,当前我国塑料软包装行业制版技术如何?其市场状况怎 样?印刷制版过程中需要注意哪些问题?本期技术专题,编辑部将和您一起关注制版的相关技术。 凹版印刷作为印刷工艺的一种,以其印制品墨层厚实,颜色鲜艳、饱和度高、印版耐印率高、印品质量稳定、印刷速度快等优点在印刷包装及图文出版领域内占据极其重要 的地位。从应用情况来看,在国外,凹印主要用于杂志、产品目录等精细出版物,包装印刷和钞票、邮票等有价证券的印刷,而且也应用于装饰材料等特殊领域;在国内,凹印则主要用于软包装印刷,随着国内凹印技术的发展,也已经在纸张包装、木纹装饰、皮革材料、药品包装上得到广泛应用,

运城制版有限公司就是一家在各个领域均有水准的专业制版公司,其使用的设备均从德国或瑞士进口,其生产的各种凹印版辊质量在全国都是首屈一指的,其生产的凹印版辊已有部分向国外出口。近年来,凹印版辊印刷大量采用醇溶性油墨和水性油墨、UV油墨,既符合了国家绿色环保印刷的要求,又能适应薄膜、复合材料、纸张等多种介质,因而在包装印刷领域保持了常胜不衰的局面,成为国内印刷行业中不可或缺的重要一员。 凹印版辊的制作工艺,从其发展的过程来看,有多种工艺选择,分别是碳素纸照相法、直接加网法、胶凹印转换电子

计算机组成原理基本知识点

计算机组成原理基本知识点 1.冯.诺依曼计算机具有如下基本特点: a . 计算机内部采用二进制来表示指令和数据,即二进制原理。 b. 将编好的程序和原始数据事先存入存储器中,然后再启动计算机工作,使计算机在不需要人工 干预的情况下,自动、高速地从存储器中取出指令加以执行,程序存储原理c.计算机由运算器,存储器,控制器,输入设备和输出设备五大基本部件组成。 2.1024B=1KB ,1024KB=1MB ,1024MB=1GB ,1024GB=1TB 。 3.数值数据的校验:奇偶校验码,海明校验码,循环冗余校验码(CRC 码)。 4.存储器的分类: A ?按存储介质分类:磁存储器、半导体存储器、光存储器。 B ?按存储方式分类:随机存取存储器(RAM )、顺序存取存储器(SAM )、直接存取存储 器(DAM )、只读存储器(ROM )。 C.按信息可保存性分类:易失性存储器、永久性存储器。 D?按性能分类:通用寄存器、高速缓冲存储器(Cache)、主存、外存。 5 ?存储器系统的层次结构:高速缓冲存储器一一主存储器(内存)一一外存储器(辅存) 6?非易失性半导体存储器:掩膜式只读存储器(MROM )、可编程只读存储器(PROM )、可擦除可编程只读存储器(EPROM )、电擦除可编程只读存储器(EEPROM )、闪速存储器。7?刷新电路的工作方式:集中式刷新、分散式刷新、异步刷新。 &高速缓冲存储器:提高主存的存取速度。 9 ?指令就是要计算机执行某种操作的命令,又称为机器指令。 10. —台计算机中所有机器指令的集合,称为这台计算机的指令系统。 11 ?指令结构:操作码字段+地址码字段 12?精简指令系统计算机(RISC)、复杂指令系统计算机(CISC) 13. CPU的功能:指令控制、操作规程控制、时间控制、数据加工。 14. CPU中的主要寄存器:指令寄存器(IR)、程序计数器(PC)、地址寄存器(AR)、数据缓冲寄存器(DR)、累加寄存器(AC)、状态条件寄存器。 15. 微指令格式:水平型微指令、垂直型微指令。 16?总线是指能为多个功能部件服务的一组公用信息线,并且能够分时地发送和接受信息。 17. 总线的分类: A ?按连接部件分类:内部总线(片内总线)、系统总线、通信总线(外部总线) B ?按数据传送方式分类:并行总线、串行总线 C.按总线的通信定时方式分类:并行总线、异步总线 18. 输入/输出设备的编址方式:存储器映像编址(统一编址)、I/O独立编址 19?输入/输出数据的控制方式:程序直接控制方式、程序中断控制方式、直接内存访问方 式(DMA )、通道方式、I/O 处理器方式 20. 原码:纯小数不够字长时,数值位后补“ 0”纯整数不够时,符号位后、数值位前补0 21. 补码:正数不变,负数的符号位为1,数值位按位取反,末位加1 22. 已知一个数的补码,求它的真值的方法是:如果补码的符号位为0,则该数为正数,补码表示的数即为真值;如果补码的符号位为1,则该数为负数,数值为按位取反末位加1。

计算机总线技术基础知识

计算机总线技术基础知识 任何一个微处理器都要与一定数量的部件和外围设备连接,但如果将各部件和每一种外围设备都分别用一组线路与CPU直接连接,那么连线将会错综复杂,甚至难以实现。为了简化硬件电路设计、简化系统结构,常用一组线路,配置以适当的接口电路,与各部件和外围设备连接,这组共用的连接线路被称为总线。采用总线结构便于部件和设备的扩充,尤其制定了统一的总线标准则容易使不同设备间实现互连。 微机中总线一般有内部总线、系统总线和外部总线。内部总线是微机内部各外围芯片与处理器之间的总线,用于芯片一级的互连;而系统总线是微机中各插件板与系统板之间的总线,用于插件板一级的互连;外部总线则是微机和外部设备之间的总线,微机作为一种设备,通过该总线和其他设备进行信息与数据交换,它用于设备一级的互连。 另外,从广义上说,计算机通信方式可以分为并行通信和串行通信,相应的通信总线被称为并行总线和串行总线。并行通信速度快、实时性好,但由于占用的口线多,不适于小型化产品;而串行通信速率虽低,但在数据通信吞吐量不是很大的微处理电路中则显得更加简易、方便、灵活。串行通信一般可分为异步模式和同步模式。 随着微电子技术和计算机技术的发展,总线技术也在不断地发展和完善,而使计算机总线技术种类繁多,各具特色。下面仅对微机各类总线中目前比较流行的总线技术分别加以介绍。 一、内部总线 1.I2C总线 I2C(Inter-IC)总线10多年前由Philips公司推出,是近年来在微电子通信控制领域广泛采用的一种新型总线标准。它是同步通信的一种特殊形式,具有接口线少,控制方式简化,器件封装形式小,通信速率较高等优点。在主从通信中,可以有多个I2C总线器件同时接到I2C总线上,通过地址来识别通信对象。 2.SPI总线 串行外围设备接口SPI(serial peripheral interface)总线技术是Motorola公司推出的一种同步串行接口。Motorola公司生产的绝大多数MCU(微控制器)都配有SPI硬件接口,如68系列MCU。SPI总线是一种三线同步总线,因其硬件功能很强,所以,与SPI有关的软件就相当简单,使CPU有更多的时间处理其他事务。 3.SCI总线 串行通信接口SCI(serial communication interface)也是由Motorola公司推出的。它是一种通用异步通信接口UART,与MCS-51的异步通信功能基本相同。 二、系统总线

凹版印刷基础知识设计师必备的基础知识

凹版印刷基础知识----设计师必备的基础知识 凹版印刷基础知识 一、凹印印刷 凹印产品一直以精美、精细著称,从画报、图片、塑料薄膜包装到人民币,都是凹印工艺的杰作。除了单张纸凹印外,凹印一般采用轮转印刷,短墨路,正向单刮刀上墨,从当年的碳素纸腐蚀版、布美兰制版、电子雕刻制版,到今天的激光雕刻制 版,凹印走过了一段漫长的发展之路。 凹版印刷,采用直接印刷方式,印刷机的结构比平版印刷机简单,自动化程度高,印刷速度快,印版耐印力可达100万印以 上,是其它印刷方法无法相比的。 二、凹版的种类 凹版主要有照相凹版和雕刻凹版两大类。照相凹版又分为传统照相凹版(即碳素纸法或称影写凹版)和照相加网凹版。雕刻凹版分为手工雕刻、机械雕刻和电子雕刻。目前常用的是照相凹版、照相加网凹版和电子雕刻凹版。 1、照相凹版是在经重铬酸盐敏化过的碳素纸上,先晒制凹印网络,再晒制连续调阳图,然后将碳素纸上的图像转移到 滚筒上,通过显影、填版、腐蚀而制得印版。 2、照相加网凹版制版法是用喷涂法或滑环法将感光胶直接涂布在滚筒上,用加过凹网的阳图版直接曝光晒版,然后进行 显影、填版、腐蚀制得印版。 3、电子雕刻凹版是用电子雕刻机直接对凹版滚筒进行雕刻。它是通过扫描头对原稿进行扫描,得到的密度光信号,经过光电转换成为电信号,再经电子计算机进行一系列处理后,传输到输出端,驱动电子雕刻头,在铜滚筒表面上进行雕刻,而制 成凹印印版。现亦有激光雕刻和电子束雕刻。 4、凹版制版法性能比较表 项目制版方法网点形状阶调平滑性制版稳定性实地密度均匀性再版重复性加工周 期文字清晰度图案接头 影写凹版网点大小相同、深度不同优差差差长差有接缝 照相加网凹版网点大小不同、深度相同一般一般差差一般差有接缝电子雕刻凹版网点大小、深度均不同优优良优短良无接缝 三、对电雕版的质量要求 电子雕刻版(包括激光雕刻版和电子束雕刻版)的层次和阶调,是以网穴的大小和深浅来表现的。为保证电雕版的质量,行业标准中规定了网穴的大小及深浅。但网穴的大小及深浅受机型(不同公司的产品)、网线线数、刻刀的新旧程度、刻刀的角度、铜层硬度(铜层硬度为维氏180~210)及产品质量要求的影响,可变因素较多,行业标准中也仅以70线/cm,130°刻刀角度 和新刻刀为例。 表1,网穴形状和尺寸: 网穴种类形状高调网穴横对角线长度(mm) 暗调网穴横对角线长度(mm) 正菱形◇35~45 165~200 拉长菱形20~35 130~145 压扁菱形25~40 140~165 小正菱形◇15~25 110~120 彩色版套印精度也是影响产品质量的一个重要因素。影响印刷品套印精度的因素很多,印套印误差表所列数据为因雕刻版规 矩不准而造成的套印不准的套印允差。 四、凹版印刷机 凹版印刷机采用圆压圆轮转式的直接印刷方式,它的特点是,结构简单,印版耐印力高,印刷速度快,印刷品墨色厚实,层 次丰富,大批量印刷时成本较低。 凹版印刷机,按照印刷幅面,分为单张纸凹印机和卷筒纸凹印机。现在使用最多的是卷筒纸的凹版印刷机。 按照印刷色数分类,可分为单色凹印机和多色凹印机。 按照印刷色组的排列位置分类,可分为卫星式凹印机和组合式凹印机。卫星式凹印机几个色组共用一个压印滚筒,组合式凹 印机每个色组呈水平状排列成流水线。 凹版印刷机,根据印刷品的用途,常常配备一些辅助设备、提高印刷及印后加工的能力。例如,作为书刊用的凹印机,

4.1pcie总线的基础知识

4.1 PCIe总线的基础知识 与PCI总线不同,PCIe总线使用端到端的连接方式,在一条PCIe链路的两端只能各连接一个设备,这两个设备互为是数据发送端和数据接收端。PCIe总线除了总线链路外,还具有多个层次,发送端发送数据时将通过这些层次,而接收端接收数据时也使用这些层次。PCIe总线使用的层次结构与网络协议栈较为类似。 4.1.1 端到端的数据传递 PCIe链路使用“端到端的数据传送方式”,发送端和接收端中都含有TX(发送逻辑)和RX(接收逻辑),其结构如图4?1 所示。由上图所示,在PCIe总线的物理链路的一个数据通路(Lane)中,由两组差分信号,共4根信号线组成。其中发送端的TX部件与接收端的RX部件使用一组差分信号连接,该链路也被称为发送端的发送链路,也是接收端的接收链路;而发送端的RX部件与接收端的TX部件使用另一组差分信号连接,该链路也被称为发送端的接收链路,也是接收端的发送链路。一个PCIe链路可以由多个Lane组成。 高速差分信号电气规范要求其发送端串接一个电容,以进行AC耦合。该电容也被称为AC耦合电容。PCIe链路使用差

分信号进行数据传送,一个差分信号由D+和D-两根信号组成,信号接收端通过比较这两个信号的差值,判断发送端发送的是逻辑“1”还是逻辑“0”。 与单端信号相比,差分信号抗干扰的能力更强,因为差分信号在布线时要求“等长”、“等宽”、“贴近”,而且在同层。因此外部干扰噪声将被“同值”而且“同时”加载到D+和D-两根信号上,其差值在理想情况下为0,对信号的逻辑值产生的影响较小。因此差分信号可以使用更高的总线频率。 此外使用差分信号能有效抑制电磁干扰EMI(Electro Magnetic Interference)。由于差分信号D+与D-距离很近而且信号幅值相等、极性相反。这两根线与地线间耦合电磁场的幅值相等,将相互抵消,因此差分信号对外界的电磁干扰较小。当然差分信号的缺点也是显而易见的,一是差分信号使用两根信号传送一位数据;二是差分信号的布线相对严格一些。 PCIe链路可以由多条Lane组成,目前PCIe链路可以支持1、2、4、8、12、16和32个Lane,即×1、×2、×4、×8、×12、×16和×32宽度的PCIe链路。每一个Lane上使用的总线频率与PCIe总线使用的版本相关。

计算机基础知识及答案(二)

计算机基础知识及答案(二) 1、微型计算机采用的是冯·诺依曼体系结构,其硬件系统由运算器、控制器、存储器、输入设备和___C___五部分组成。 A键盘、鼠标器。B显示器、打印机。C输出设备。D系统总线。 2、在微型计算机中,其核心部件中央处理器CPU,被称之为___D___。 A关键部件。B主要部件。C必备部件。D微处理器MPU(Micro Processing Unit)。 3、微处理器把运算器和__A____集成在一块很小的硅片上,是一个独立的部件。 A控制器。B内存储器。C输入设备。D输出设备。 4、微型计算机的基本构成有两个特点:一是采用微处理器,二是采用___D___。 A键盘和鼠标器作为输入设备。B显示器和打印机作为输出设备。CROM和RAM作为主存储器。D总线系统。 5、根据微型计算机硬件构成的特点,可以将其硬件系统具体化为由微处理器、内存储器、接口电路、I/O设备和__D____组成。 A键盘、鼠标器。B显示器、打印机。C外围设备。D总线系统。 6、在微型计算机系统组成中,我们把微处理器CPU、只读存储器ROM和随机存储器RAM三部分统称为___D___。 A硬件系统。B硬件核心模块。C微机系统。D主机。 7、微型计算机使用的主要逻辑部件是___D___。 A电子管。B晶体管。C固体组件。D大规模和超大规模集成电路。 8、在微型计算机中,通常把输入/输出设备,统称为__D____。 ACPU。B存储器。C操作系统。D外部设备。 9、下面是关于微型计算机总线的描述,正确的有___C___。

A总线系统由系统总线、地址总线、数据总线和控制总线组成。B总线系统由接口总线、地址总线、数据总线和控制总线组成。C系统总线由地址总线、数据总线和控制总线组成。D 地址总线、数据总线和控制总线的英文缩写分别为DB、AB,CB。 10、微型计算机的系统总线是CPU与其它部件之间传送___D___信息的公共通道。 A输入、输出、运算。B输入、输出、控制。C程序、数据、运算。D数据、地址、控制。 11、CPU与其它部件之间传送数据是通过__A____实现的。 A数据总线。B地址总线。C控制总线。D数据、地址和控制总线三者。 12、下面是关于数据总线(Data Bus)的描述,不正确的是__D____。 A数据总线用来传送数据信息。B数据总线的位数,决定了CPU一次能够处理的数据的位数。CMPU一次能够处理的数据的位数称为字长。D字长越长的CPU,处理信息所需的时间越长。 13、CPU与其它部件之间传送地址是通过___B___实现的。 A数据总线。B地址总线。C控制总线。D数据、地址和控制总线三者。 14、下面是关于地址总线(Address Bus)的描述,不正确的是__D____。 A地址总线用来传送地址信息。B地址总线的根数,决定了CPU可访问的内存最大范围。C 若地址总线为n根,则该微处理器可访问内存的最大范围是2的n次方。D拥有32根地址总线的微处理器,其可访问内存的最大范围是4000M。 15、CPU与其它部件之间传送控制信号是通过____C__实现的。 A数据总线。B地址总线。C控制总线。D数据、地址和控制总线三者。 16、下面是关于控制总线(Control Bus)的描述,不正确的是__C____。 A控制总线用来传送控制器的各种制信息。B控制总线的数目由CPU的控制功能所决定。 C80486和PⅢ都是Intel公司推出的微处理器,它们的控制功能是相同的。D不同微处理器的控制功能具有较大的差异。 17、下面是关于微处理器MPU的描述,不正确的是___D___。 A微处理器是微型计算机的核心部件。B微处理器是一块包含运算器和控制器的大规模集成电路芯片。C微处理器的性能决定了微型计算机的档次。D我们在购买微型计算机时,应该不断跟踪微处理器的更新。