电子科技大学课件

电子科技大学课件点播及在线作业学习指南

一、网络教育学习模式

以网络课件学习、在线作业提交为主,纸介教材自学为辅。

二、网络课件学习及作业提交学号:20110210214024

1.登陆学习平台,进行在线课件学习密码066884

在正式取得学籍后,学校将根据教学计划在系统里为学生开设相应的学习课程,进入平台后就可以进行学习。

【操作】:

第一步:直接在浏览器的地址栏里输入学习平台网址:https://www.360docs.net/doc/ac2431022.html,/news/ 即可访问学习平台。

第二步:在网络学院的首页登录处输入用户名(学号),密码(默认为身份证号的末六位)如图1。

图1输入用户名和用户密码登录平台

学号查询办法:登陆网上《学生专栏》,(学生专栏的网址:https://www.360docs.net/doc/ac2431022.html,,用户名:中文全名,密码:身份证号码),学号信息请

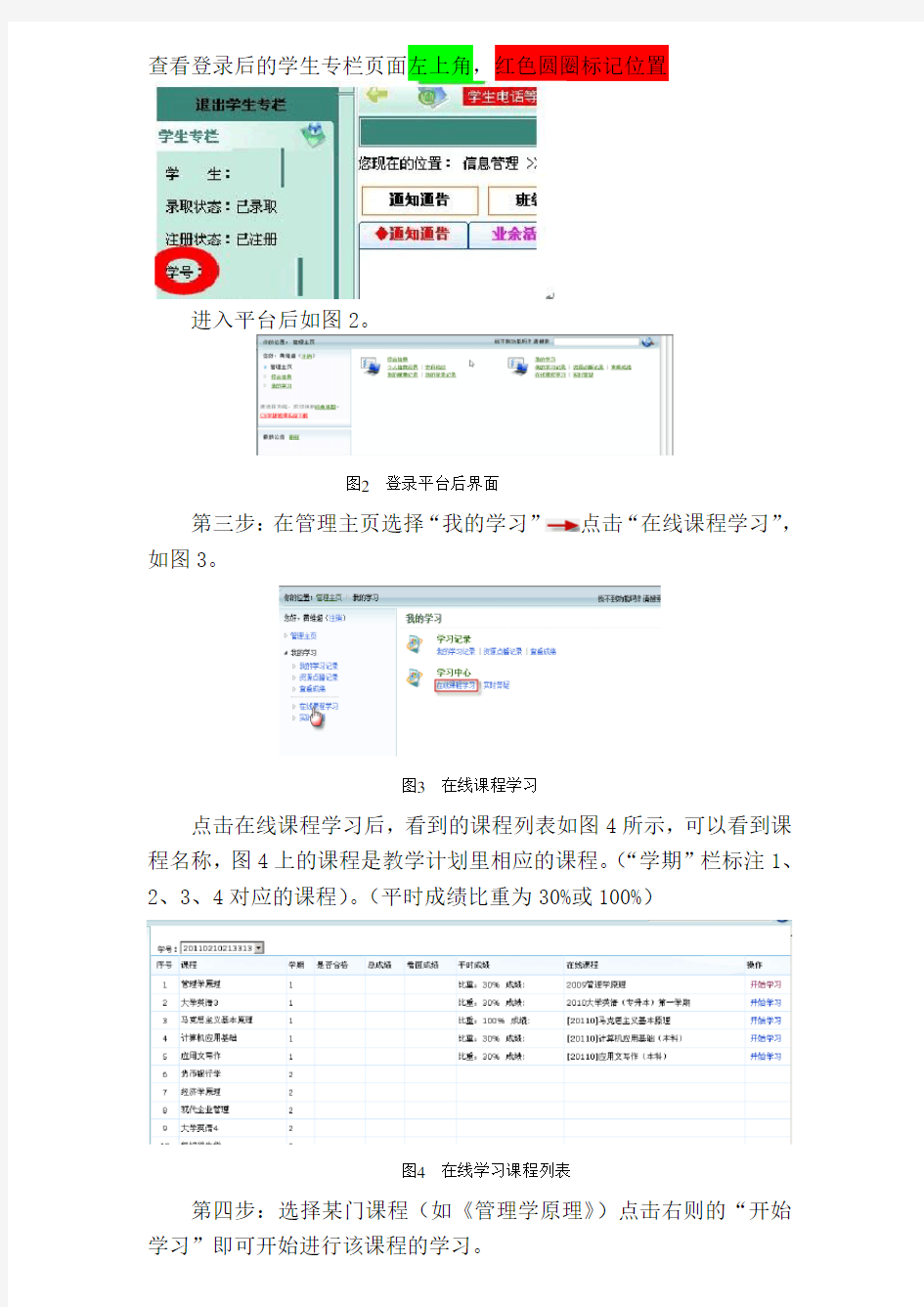

查看登录后的学生专栏页面左上角,红色圆圈标记位置

进入平台后如图2。

图2登录平台后界面

第三步:在管理主页选择“我的学习”点击“在线课程学习”,如图3。

图3在线课程学习

点击在线课程学习后,看到的课程列表如图4所示,可以看到课程名称,图4上的课程是教学计划里相应的课程。(“学期”栏标注1、2、3、4对应的课程)。(平时成绩比重为30%或100%)

图4在线学习课程列表

第四步:选择某门课程(如《管理学原理》)点击右则的“开始学习”即可开始进行该课程的学习。

点击“开始学习”后就可以进入课程的学习。进入课程学习中心后,如图5。界面左面有“学习进度”、“资料下载”(大纲及考前自测题)、“作业提交”(作业测验)、“管理”(学习小组、答疑中心)。界面右面可以看到“学习内容”,下面显示学习内容的六种状态,如图6。

图5课程中心

图6学习内容状态

第五步:点击学习内容中相应的学习节点进行学习,每一个学习节点至少要学习60秒并滚动旁边的滚动条才可以显示学习进度。完成学习后,则显示已经学习完毕,即可进行下一个节点的学习。如图7。学习节点及学习进度如图8。

图7学习节点状态

图8学习节点及学习进度

第六步:学习进度100%:需要对课程学习内容中课件链接、小节的内容逐个点击学习达到规定的学习时间,完成后系统会自动记录并在标题位置出现"√"标记,即表示该内容已经达到学习时间了。学习进度显示100%,平时成绩得15分。如图9。(温馨提示:如果学完仍显示99%进度的,要查看是否忘记点击学习内容中的课件连接)

图9学习进度条为绿色,显示100%

2.在线作业提交

默认情况下每一门课程的学习都会有三套作业题,分别是作业提交1、作业提交2、作业提交3。学生要取得相应的平时成绩必须完成并答对这三套作业题,否则不做这三套题的话平时成绩中的作业部分就会为0分,而这三套题目没有全部答对的话,也不会得满分15分。根据作业的不同要求,每个作业可以进行多次的提交(通常有5次机会),平台会以多次提交的同一作业的最高得分作为学生的平时成绩。重点提醒:作业内容选择完毕后需在系统规定的时间完成(通常是1个小时),并进行提交,否则将失去本次作业机会。(通常每次作业有5次提交机会)

【操作】:步骤1、课程中心点击“作业提交”中的作业(测验),如图10、图11。

图10–图11作业

步骤2、点击作业提交1,进入界面如下图12,并点击“开始考试”按钮,则可进行在线作业了。如图13(注意,务必在一个小时内文成作业并提交,否则没有平时成绩并浪费一次作业机会,共允许重考5次)

图12

图13

步骤3、作业提交后,可重新点击作业提交1,点击“查看考卷”按钮,进入考卷页面,可拖动旁边滚动条至底部,则可看到选项的答案,选错的题目,系统会显示出正确答案;选对的题目则显示“答对了”。提示:第二遍做的作业题目内容不变,但题目顺序以及答案的顺序都会进行调整。如图14-图15,(作业提交2、作业提交3与作业提交1的操作办法一样。)

图14

图15

3.非实时提问

在学习过程中遇到问题可以在答疑中心提出疑问,相应的课程老师将在最短的时间进行回复。

【操作】:课程中心答疑中心,如图12。

图11进入答疑中心

进入答疑中心后可以查看学生的相关的提问,也发起疑问,同时也可以查看课程的FAQ,如图13。

图12答疑中心

4.参与学习小组

学生开始进行学习后,可以参与由老师组织的一些学习小组,对相应的问题进行专题讨论等。

【操作】:课程中心学习小组,如图14。

图13进入学习小组

在第一次进入学习小组时,需要申请加入学习小组,如图15。

图14申请加入学习小组

申请加入学习小组后,就可以正常进入学习小组,如图16——图18。

图15进入学习小组

图16学习小组

图17就相应问题进行讨论

三、课程考试

1.课程期末考试时间:

每学期都安排期末考试,(通常安排两次),时间一般为学期期末结束后一个周末进行。(11秋本学期期末考试日期为:12月底,具体考试时间及考试安排见学生专栏通知通告。)

(备注:专升本学生要通过统考,考试时间为每年的4、9、12月,报名时间通常为考试前两个月左右,具体报名事宜请关注学生专栏通知通告。)

2.期末考试复习资料下载:

2.1 绝大部分考试复习资料可以在考前一周左右登陆《学生专栏》(网址https://www.360docs.net/doc/ac2431022.html,,用户名中文全名,密码身份证号码)查看通知进行下载。

2.2部分复习资料需要在科大的学习平台(网址:https://www.360docs.net/doc/ac2431022.html,)中的“大纲及考前自测题”进行下载。学习平台的课程在学习完成后,可以直接在课程中心下载该课程的学习指导、教学大纲、考试大纲、自测题进行复习。

【操作】:课程中心资料下载,如图19、图20。

图18大纲及考前自测题

图19大纲及考前自测题下载方式

2.3 未进入学习平台的课程需要进入资源中心下载该课程对应的复习资料。

3.课程最终成绩计算

3.1课程的最终成绩由两部分组成:课程的平时成绩+课程考试成绩*70%。(如在平台中查看成绩时,课程的平时成绩没有显示在成绩查询页面是因为系统还没有把平时成绩更新到个人的课程成绩,系统将在期末每次成绩录入前自动重新统计一次学习平台平时成绩,使学生获得新的总成绩。)

3.2课程的平时成绩计算:平时成绩共30分。课程的进度完成占15分,课程的作业及测试完成满分占15分。如果每一个学习节点在系统里都已经完成了指定的学习时间平时成绩的15分就可以得满分。作业的15分需要根据作业的完成情况而定。一般情况下一门课程有3次作业,每一次的作业满分为5分,得分由作业的批改情况决定。如果部分课程没有作业,则学习过程占总课程成绩的30分。

4.课程成绩查询

课程成绩在每一个学期考试完毕后,由学籍管理人员根据评卷结果直接录入平台,成绩经审核后学生就可以在平台里查询到。(通常为课程考试结束一至两个月之后,学生可以登录学习平台对学习成绩陆续进行查询)

【操作】:我的学习查看成绩,如图21。

图20查看成绩

查询成绩结果如图22。

图21课程成绩

每学期考试成绩录入系统后,学生若对成绩有疑问,应在下学期开学一个月内向教务处提交查卷申请:将有疑问的成绩截图发送到科大邮箱(kd@https://www.360docs.net/doc/ac2431022.html,)

5.补考或清考

总校出了课程补考的暂行规定,每学期的课程如缺考只有两次补考的机会(一次是开学后第一个月(每年4月和10月),一次是毕业前补考),且未按时毕业的毕业生只有一次清考的机会。建议不要缺考。

电子科技大学远程教育深圳学习中心 2011年9月

电子科技大学期末数字电子技术考试题a卷-参考答案教学内容

电子科技大学二零零九至二零一零学年第 二 学期期 末 考试 数字逻辑设计及应用 课程考试题 A 卷(120分钟)考试形式:闭卷 考试日期2010年7月12日 课程成绩构成:平时 20 分, 期中 20 分, 实验 0 分, 期末 60 分 一、To fill your answers in the blanks (1’×25) 1. If [X]10= - 110, then [X]two's-complement =[ 10010010 ]2, [X]one's-complement =[ 10010001 ]2. (Assumed the number system is 8-bit long) 2. Performing the following number system conversions: A. [10101100]2=[ 000111010010 ]2421 B. [1625]10=[ 0100100101011000 ]excess-3 C. [ 1010011 ]GRAY =[ 10011000 ]8421BCD 3. If ∑=C B A F ,,)6,3,2,1(, then F D ∑=C B A ,,( 1,4,5,6 )=C B A ,,∏(0,2,3,7 ). 4. If the parameters of 74LS-series are defined as follows: V OL max = 0.5 V , V OH min = 2.7 V , V IL max = 0.8 V , V IH min = 2.0 V , then the low-state DC noise margin is 0.3V ,the high-state DC noise margin is 0.7V . 5. Assigning 0 to Low and 1 to High is called positive logic. A CMOS XOR gate in positive logic is called XNOR gate in negative logic. 6. A sequential circuit whose output depends on the state alone is called a Moore machine. 7. To design a "001010" serial sequence generator by shift registers, the shift register should need 4 bit as least. 8. If we use the simplest state assignment method for 130 sates, then we need at least

2018年成都电子科技大学858信号与系统考研大纲硕士研究生入学考试大纲

主要考察学生掌握《信号与系统》中连续和离散时间信号与系统的基本概念、理论和分析方法;重点考察在时间域和变换域建立信号与系统的数学模型、信号分析、求解系统输出以及对系统本身性能判定的方法,具备通过上述知识解决实际应用问题的能力。 《信号与系统》是测控技术及仪器专业一门重要的专业基础课,是测控技术及仪器专业的学 生学习专业知识的一门入门课,通过本课程的学习,使学生了解连续和离散信号与系统的基本概念、理论和分析方法;理解在时间域与变换域建立信号与系统的数学模型、信号分析、求解系统 输出以及对系统本身性能的基本方法。熟练掌握基本概念与基本运算,并能加以灵活应用。 本课程介绍连续时间系统、离散时间系统、信号的时域和频域分析、信号的采样与恢复等基 本内容等。通过本课程的学习,学生可以获得信号与系统分析方面的基本知识,增强学生利用该 知识解决实际应用的能力。 二、内容 1、基本概念 1)连续时间和离散时间信号的基本分类和表示方法 2)奇异信号及其基本性质, 3)信号的基本运算、自变量的变换 4)系统的基本概念和基本性质。 2、线性时不变系统时域分析 1)线性时不变系统的时域分析方法 2)零输入响应和零状态响应的概念 3)卷积积分与卷积和的基本运算 3、线性时不变系统频域分析 1)线性时不变系统的傅里叶分析方法 2)连续时间信号傅里叶级数分解和傅里叶变换的物理意义 3)连续时间周期信号的傅里叶级数性质和 LTI 系统对复指数信号的响应计算方法 4)从基本变换对出发、灵活运用傅里叶变换的基本性质求解傅里叶变换(包括反变换) 5)系统的频率响应及有关滤波等概念, 6)信号的幅度调制、 4、信号的采样与恢复 1)采样的基本理论 2)采样定理以及采样后输出信号的频谱特点 3)零阶保持采样 4)信号的采样与恢复,欠采样造成的信号混淆。 5、拉普拉斯变换

电子科技大学数字无线电课后习题答案

作业 1:FM 对讲机中接收机的设计 系统参数:射频频率: 433MHz

信号带宽:15KHz (频偏 ?7.5KHz ,音频带宽 3.4KHz ) 调制方式:FM 要求:1. 给出一个可实现的系统结构 2. 设计系统各级的主要参数(如滤波器、振荡器等) 3. 画出各级的频谱结构

答案: 1. 二次变频超外差式接收机系统:

f0 ? 433MHz B ? 20MHz

f IF1

?

49.5MHz

f0 ? 49.5MHz B ? 100KHz

fIF2 ? 450KHz

f0 ? 450KHz B ? 15KHz

fLO1 ? 383.5MHz 或 482.5MHz

fLO2 ? 48.05MHz 或 49.95MHz

2.

15KHz

433

f (MHz)

334 383.5 433 482.5 532 f (MHz)

47.5 48.05 49.5 49.95 50.4 f (MHz)

450

f (KHz)

1.根据下图所示的数字基带接收机电路和 A 点给定的信号频谱, 画出图中 B、C、D、E、F 点的信号频谱。

cos?0t

?

e j?0t

? e? 2

j?0t

A

sin ?0t

?

e

j?0t

? e? 2j

j?0t

cos?ot

LPF

LPF

-sin?ot

zBI(t)

zBI(n)

B

C zBQ(t)

A/D

D

DSP

E

A/D

zBQ(n)

fs=2.5Bs

zB(n)= zBI(n) +j zBQ(n)

F

A点信号频谱:

X(f)

1

Bs

0.5

? f0 ? Bs ? f0

0

f0 f0 ? Bs f (Hz)

答案:

B点信号频谱: 经LPF滤除

?2 f0

ZBI ( f ) 1 0.5

?Bs 0 Bs

经LPF滤除

2 f0 f (Hz)

C点信号频谱:

j ? ZBQ ( f ) 1

0.5

?Bs

0 Bs

f (Hz)

大规模数字成电路习题解答

自我检测题 1.在存储器结构中,什么是“字”?什么是“字长”,如何表示存储器的容量? 解:采用同一个地址存放的一组二进制数,称为字。字的位数称为字长。习惯上用总的位数来表示存储器的容量,一个具有n字、每字m位的存储器,其容量一般可表示为n ×m位。 2.试述RAM和ROM的区别。 解:RAM称为随机存储器,在工作中既允许随时从指定单元内读出信息,也可以随时将信息写入指定单元,最大的优点是读写方便。但是掉电后数据丢失。 ROM在正常工作状态下只能从中读取数据,不能快速、随时地修改或重新写入数据,内部信息通常在制造过程或使用前写入, 3.试述SRAM和DRAM的区别。 解:SRAM通常采用锁存器构成存储单元,利用锁存器的双稳态结构,数据一旦被写入就能够稳定地保持下去。动态存储器则是以电容为存储单元,利用对电容器的充放电来存储信息,例如电容器含有电荷表示状态1,无电荷表示状态0。根据DRAM的机理,电容内部的电荷需要维持在一定的水平才能保证内部信息的正确性。因此,DRAM在使用时需要定时地进行信息刷新,不允许由于电容漏电导致数据信息逐渐减弱或消失。 4.与SRAM相比,闪烁存储器有何主要优点? 解:容量大,掉电后数据不会丢失。 5.用ROM实现两个4位二进制数相乘,试问:该ROM需要有多少根地址线?多少根数据线?其存储容量为多少? 解:8根地址线,8根数据线。其容量为256×8。 6.简答以下问题: (1)CPLD和FPGA有什么不同? FPGA可以达到比CPLD更高的集成度,同时也具有更复杂的布线结构和逻辑实现。FPGA更适合于触发器丰富的结构,而CPLD更适合于触发器有限而积项丰富的结构。 在编程上FPGA比CPLD具有更大的灵活性;CPLD功耗要比FPGA大;且集成度越高越明显;CPLD比FPGA有较高的速度和较大的时间可预测性,产品可以给出引脚到引脚的最大延迟时间。CPLD的编程工艺采用E2 CPLD的编程工艺,无需外部存储器芯片,使用简单,保密性好。而基于SRAM编程的FPGA,其编程信息需存放在外部存储器上,需外部存储器芯片,且使用方法复杂,保密性差。 (2)写出三家CPLD/FPGA生产商名字。 Altera,lattice,xilinx,actel 7.真值表如表T5.7所示,如从存储器的角度去理解,AB应看为地址,F0F1F2F3应看为数据。 表T5.7

电子科大2010年信号与系统期末考题及标准答案

………密………封………线………以………内………答………题………无………效…… 电子科技大学二零 一 零 至二零 一 一 学年第 一 学期期 末 考试 SIGNALS AND SYSTEMS 课程考试题 A 大纲A 卷 ( 120 分钟) 考试形式: 一页纸开卷 考试日期 20 年 月 日 课程成绩构成:平时 10 分, 期中 20 分, 实验 10 分, 期末 60 分 Attention: Y ou must answer the following questions in English. 1.(15 points ) Suppose ()1x t and ()2x t are two band-limited signals, where π ωω200,0)(1>=for j X ,π ωω500, 0)(2>=for j X . Impulse-train sampling is performed on ()()() 1234/22=+-*y t x t x t to obtain ()()()p n y t y nT t nT δ+∞ =-∞ = -∑ .Give out the expression of )(ωj Y in terms of ) (1ωj X and )(2ωj X ,where )(ωj Y is the Fourier transform of ) (t y . Specify the largest values of the sampling period T which ensures that ()t y is recoverable from ()t y p .

数字集成电路知识点整理

Digital IC:数字集成电路是将元器件和连线集成于同一半导体芯片上而制成的数字逻辑电路或系统第一章引论 1、数字IC芯片制造步骤 设计:前端设计(行为设计、体系结构设计、结构设计)、后端设计(逻辑设计、电路设计、版图设计)制版:根据版图制作加工用的光刻版 制造:划片:将圆片切割成一个一个的管芯(划片槽) 封装:用金丝把管芯的压焊块(pad)与管壳的引脚相连 测试:测试芯片的工作情况 2、数字IC的设计方法 分层设计思想:每个层次都由下一个层次的若干个模块组成,自顶向下每个层次、每个 模块分别进行建模与验证 SoC设计方法:IP模块(硬核(Hardcore)、软核(Softcore)、固核(Firmcore ))与设计复用Foundry (代工)、Fabless (芯片设计)、Chipless (IP设计)"三足鼎 立” 一-oC发展的模式 3、数字IC的质量评价标准(重点:成本、延时、功耗,还有能量啦可靠性啦驱动能力啦之类的) NRE (Non-Recurrent Engineering)成本 设计时间和投入,掩膜生产,样品生产 一次性成本 Recurrent 成本 工艺制造(silicon processing ),封装(packaging ),测试(test) 正比于产量 每个集成电路的成本-kceurrenr成本+ 一、此上成木 总产量 管芯成本十芯片濯试成本+封装成本 Recurrent Jjfc 本----------- ----------------------- 最终测试成品率| 一阶RC网路传播延时:正比于此电路下拉电阻和负载电容所形成的时间常数 C上的电压从上升到50%的时间 &二In (2)r = 0.69 功耗:emmmm 自己算 4、EDA设计流程 IP设计-------- >系统设计(SystemC ) ----- > 模块设计(verilog ) 版图设计(.ICC --------- 电路级设计(.v基本不可读)综合过程中用到的文件类型(都是synopsys): 可以相互转化 .db (不可读)< ----------- > .lib (可读) 加了功耗信息

电子科技大学数字电路期末考试样题

电子科技大学数字电路期 末考试样题 Last revision on 21 December 2020

一、填空题 1.五个变量构成的所有最小项之和等于 ( )。 2.已知某数的二进制原码表示为 ( 110110) 2 , 则其对应的8-bit 补码表示为 ( )2。 3.已知∑=C B A F ,,)3,0(,则∑='C B A F ,,( )。 4.要使D 触发器按'*Q Q =工作,则D 触发器的输入D=( )。 5.用移位寄存器产生1101010序列,至少需要( )位的移位寄存器。 二、单项选择题: 1. 若要将一异或门当作反相器(非门)使用,则输入端A 、B 端的连接方式是( )。 A. A 或B 中有一个接“0” B. A 或B 中有一个接“1” C. A 和B 并联使用 D. 不能实现 2.组合电路的竞争冒险是由于( )引起的。 A. 电路不是最简 B. 电路有多个输出 C. 电路中使用不同的门电路 D. 电路中存在延时 3.某一逻辑函数真值表确定后,下面描述该函数逻辑功能的表达式中,具有唯一性的是( )。 A .该逻辑函数的最简与或式 B .该逻辑函数的积之和标准型 C .该逻辑函数的最简或与式 D .该逻辑函数的和之积式 4.若最简状态转换表中,状态数为n ,则所需状态变量数K 为 ( )的整数.

00 00 01 01 10 1011 11图 A .n K 2log = B .n K 2log < C . n K 2log ≥ D . n K 2log ≤ 5.某计数器的状态转换图如图1所示,其该计数器的模为( )。 A . 八 B. 五 C. 四 D. 三 三、 组合电路分析: 1.求逻辑函数 Z Y X Y X Z X F ?'?+?+?'= 的最简积之和表达式。 2.已知逻辑函数∑=Z Y X F ,,)7,5,1(, 请写出该函数的标准和(最小项之和)表达式: 3.找出逻辑表达式X W Y W F ?+'?'=对应的电路的所有静态冒险。 四、组合电路设计: 1、试用一片三输入八输出译码器74X138和适当的与非门实现函数: 画出电路连接图。译码器如右图所示。 2、一个多路复用器,具有4个2位输入总线P 、Q 、R 、T ,3个选择输入端S2~S0根据表1选定4个输入总线中的一个来驱动2位输出总线Y 。如图2所示,可以使用一片74x153(四选一多路复用器)和一个码转换器实现该功能,试写出图2中“码转换器”对应的真值表和逻辑表达式。 1(21)C S S '=?,0(10)C S S '=? 五、 时钟同步状态机设计: 表1 S 2 S 1 S 0 选择的输入 0 0 0 P 0 0 1 P 0 1 0 P 0 1 1 Q 1 0 0 P 1 0 1 P 1 1 0 R 码

电子科技大学数字电路期末考试样题

000 001 010 011 100 101 110 111 图1 一、填空题 1.五个变量构成的所有最小项之和等于 ( )。 2.已知某数的二进制原码表示为 ( 110110) 2 , 则其对应的8-bit 补码表示为 ( )2。 3.已知∑=C B A F ,,)3,0(,则∑='C B A F ,,( )。 4.要使D 触发器按'*Q Q =工作,则D 触发器的输入D=( )。 5.用移位寄存器产生1101010序列,至少需要( )位的移位寄存器。 二、单项选择题: 1. 若要将一异或门当作反相器(非门)使用,则输入端A 、B 端的连接方式是( )。 A. A 或B 中有一个接“0” B. A 或B 中有一个接“1” C. A 和B 并联使用 D. 不能实现 2.组合电路的竞争冒险是由于( )引起的。 A. 电路不是最简 B. 电路有多个输出 C. 电路中使用不同的门电路 D. 电路中存在延时 3.某一逻辑函数真值表确定后,下面描述该函数逻辑功能的表达式中,具有唯一性的是( )。 A .该逻辑函数的最简与或式 B .该逻辑函数的积之和标准型 C .该逻辑函数的最简或与式 D .该逻辑函数的和之积式 4.若最简状态转换表中,状态数为n ,则所需状态变量数K 为 ( )的整数. A .n K 2log = B .n K 2log < C . n K 2log ≥ D . n K 2log ≤ 5.某计数器的状态转换图如图1所示,其该计数器的模为( )。 A . 八 B. 五 C. 四 D. 三 三、 组合电路分析: 1.求逻辑函数 Z Y X Y X Z X F ?'?+?+?'= 的最简积之和表达式。 2.已知逻辑函数∑=Z Y X F ,,)7,5,1(, 请写出该函数的标准和(最小项之和)表达式: 3.找出逻辑表达式X W Y W F ?+'?'=对应的电路的所有静态冒险。 四、组合电路设计:

电子科技大学课件

电子科技大学课件点播及在线作业学习指南 一、网络教育学习模式 以网络课件学习、在线作业提交为主,纸介教材自学为辅。 二、网络课件学习及作业提交学号:20110210214024 1.登陆学习平台,进行在线课件学习密码066884 在正式取得学籍后,学校将根据教学计划在系统里为学生开设相应的学习课程,进入平台后就可以进行学习。 【操作】: 第一步:直接在浏览器的地址栏里输入学习平台网址:https://www.360docs.net/doc/ac2431022.html,/news/ 即可访问学习平台。 第二步:在网络学院的首页登录处输入用户名(学号),密码(默认为身份证号的末六位)如图1。 图1输入用户名和用户密码登录平台 学号查询办法:登陆网上《学生专栏》,(学生专栏的网址:https://www.360docs.net/doc/ac2431022.html,,用户名:中文全名,密码:身份证号码),学号信息请

查看登录后的学生专栏页面左上角,红色圆圈标记位置 进入平台后如图2。 图2登录平台后界面 第三步:在管理主页选择“我的学习”点击“在线课程学习”,如图3。 图3在线课程学习 点击在线课程学习后,看到的课程列表如图4所示,可以看到课程名称,图4上的课程是教学计划里相应的课程。(“学期”栏标注1、2、3、4对应的课程)。(平时成绩比重为30%或100%) 图4在线学习课程列表 第四步:选择某门课程(如《管理学原理》)点击右则的“开始学习”即可开始进行该课程的学习。

点击“开始学习”后就可以进入课程的学习。进入课程学习中心后,如图5。界面左面有“学习进度”、“资料下载”(大纲及考前自测题)、“作业提交”(作业测验)、“管理”(学习小组、答疑中心)。界面右面可以看到“学习内容”,下面显示学习内容的六种状态,如图6。 图5课程中心 图6学习内容状态 第五步:点击学习内容中相应的学习节点进行学习,每一个学习节点至少要学习60秒并滚动旁边的滚动条才可以显示学习进度。完成学习后,则显示已经学习完毕,即可进行下一个节点的学习。如图7。学习节点及学习进度如图8。 图7学习节点状态

《数字集成电路》期末试卷A(含答案)

浙江工业大学 / 学年第一学期 《数字电路和数字逻辑》期终考试试卷 A 姓名 学号 班级 任课教师 一、填空题(本大题共10小题,每空格1分,共10分) 请在每小题的空格中填上正确答案。错填、不填均无分。 1.十进制数(68)10对应的二进制数等于 ; 2.描述组合逻辑电路逻辑功能的方法有真值表、逻辑函数、卡诺图、逻辑电路图、波形图和硬件描述语言(HDL )法等,其中 描述法是基础且最直接。 3.1A ⊕可以简化为 。 4.图1所示逻辑电路对应的逻辑函数L 等于 。 A B L ≥1 & C Y C 图1 图2 5.如图2所示,当输入C 是(高电平,低电平) 时,AB Y =。 6.两输入端TTL 与非门的输出逻辑函数AB Z =,当A =B =1时,输出低电平且V Z =0.3V ,当该与非门加上负载后,输出电压将(增大,减小) 。 7.Moore 型时序电路和Mealy 型时序电路相比, 型电路的抗干扰能力更强。 8.与同步时序电路相比,异步时序电路的最大缺陷是会产生 状态。 9.JK 触发器的功能有置0、置1、保持和 。 10.现有容量为210×4位的SRAM2114,若要将其容量扩展成211×8位,则需要 片这样 的RAM 。 二、选择题(本大题共10小题,每小题2分,共20分) 在每小题列出的四个备选项中只有一个是符合题目要求的,请将其代码填写在题后的括号内。错选、多选或未选均无分。 11.十进制数(172)10对应的8421BCD 编码是 。 【 】 A .(1111010)8421BCD B .(10111010)8421BCD C .(000101110010)8421BC D D .(101110010)8421BCD 12.逻辑函数AC B A C B A Z +=),,(包含 个最小项。 【 】

数字集成电路复习资料

第一章 数字集成电路介绍 第一个晶体管,Bell 实验室,1947 第一个集成电路,Jack Kilby ,德州仪器,1958 摩尔定律:1965年,Gordon Moore 预言单个芯片上晶体管的数目每18到24个月翻一番。(随时间呈指数增长) 抽象层次:器件、电路、门、功能模块和系统 抽象即在每一个设计层次上,一个复杂模块的内部细节可以被抽象化并用一个黑匣子或模型来代替。这一模型含有用来在下一层次上处理这一模块所需要的所有信息。 固定成本(非重复性费用)与销售量无关;设计所花费的时间和人工;受设计复杂性、设计技术难度以及设计人员产出率的影响;对于小批量产品,起主导作用。 可变成本 (重复性费用)与产品的产量成正比;直接用于制造产品的费用;包括产品所用部件的成本、组装费用以及测试费用。每个集成电路的成本=每个集成电路的可变成本+固定成本/产量。可变成本=(芯片成本+芯片测试成本+封装成本)/最终测试的成品率。 一个门对噪声的灵敏度是由噪声容限NM L (低电平噪声容限)和NM H (高电平噪声容限)来度量的。为使一个数字电路能工作,噪声容限应当大于零,并且越大越好。NM H = V OH - V IH NM L = V IL - V OL 再生性保证一个受干扰的信号在通过若干逻辑级后逐渐收敛回到额定电平中的一个。 一个门的VTC 应当具有一个增益绝对值大于1的过渡区(即不确定区),该过渡区以两个有效的区域为界,合法区域的增益应当小于1。 理想数字门 特性:在过渡区有无限大的增益;门的阈值位于逻辑摆幅的中点;高电平和低电平噪声容限均等于这一摆幅的一半;输入和输出阻抗分别为无穷大和零。 传播延时、上升和下降时间的定义 传播延时tp 定义了它对输入端信号变化的响应有多快。它表示一个信号通过一个门时所经历的延时,定义为输入和输出波形的50%翻转点之间的时间。 上升和下降时间定义为在波形的10%和90%之间。 对于给定的工艺和门的拓扑结构,功耗和延时的乘积一般为一常数。功耗-延时积(PDP)----门的每次开关事件所消耗的能量。 一个理想的门应当快速且几乎不消耗能量,所以最后的质量评价为。能量-延时积(EDP) = 功耗-延时积2 。 第三章、第四章CMOS 器件 手工分析模型 ()0 12' 2 min min ≥???? ??=GT DS GT D V V V V V L W K I 若+-λ ()DSAT DS GT V V V V ,,m in min = 寄生简化:当导线很短,导线的截面很大时或当所采用的互连材料电阻率很低时,电感的影响可以忽略:如果导线的电阻很大(例如截面很小的长铝导线的情形);外加信号的上升和下降时间很慢。 当导线很短,导线的截面很大时或当所采用的互连材料电阻率很低时,采用只含电容的模型。 当相邻导线间的间距很大时或当导线只在一段很短的距离上靠近在一起时:导线相互间的电容可以被忽略,并且所有的寄生电容都可以模拟成接地电容。 平行板电容:导线的宽度明显大于绝缘材料的厚度。 边缘场电容:这一模型把导线电容分成两部分:一个平板电容以及一个边缘电容,后者模拟成一条圆柱形导线,其直径等于该导线的厚度。 多层互连结构:每条导线并不只是与接地的衬底 耦合(接地电容),而且也与处在同一层及处在相邻层上的邻近导线耦合(连线间电容)。总之,再 多层互连结构中导线间的电容已成为主要因素。 这一效应对于在较高互连层中的导线尤为显著, 因为这些导线离衬底更远。 例4.5与4.8表格 电压范围 集总RC 网络 分布RC 网络 0 → 50%(t p ) 0.69 RC 0.38 RC 0 → 63%(τ) RC 0.5 RC 10% → 90%(t r ) 2.2 RC 0.9 RC 0 → 90% 2.3 RC 1.0 RC 例4.1 金属导线电容 考虑一条布置在第一层铝上的10cm 长,1μm 宽的铝线,计算总的电容值。 平面(平行板)电容: ( 0.1×106 μm2 )×30a F/μm2 = 3pF 边缘电容: 2×( 0.1×106 μm )×40aF/μm = 8pF 总电容: 11pF 现假设第二条导线布置在第一条旁边,它们之间只相隔最小允许的距离,计算其耦合电 容。 耦合电容: C inter = ( 0.1×106 μm )×95 aF/μm2 = 9.5pF 材料选择:对于长互连线,铝是优先考虑的材料;多晶应当只用于局部互连;避免采用扩散导线;先进的工艺也提供硅化的多晶和扩散层 接触电阻:布线层之间的转接将给导线带来额外的电阻。 布线策略:尽可能地使信号线保持在同一层上并避免过多的接触或通孔;使接触孔较大可以降低接触电阻(电流集聚在实际中将限制接触孔的最大尺寸)。 采电流集聚限制R C , (最小尺寸):金属或多晶至n+、p+以及金属至多晶为 5 ~ 20 Ω ;通孔(金属至金属接触)为1 ~ 5 Ω 。 例4.2 金属线的电阻 考虑一条布置在第一层铝上的10cm 长,1μm 宽的铝线。假设铝层的薄层电阻为0.075Ω/□,计算导线的总电阻: R wire =0.075Ω/□?(0.1?106 μm)/(1μm)=7.5k Ω 例4.5 导线的集总电容模型 假设电源内阻为10k Ω的一个驱动器,用来驱动一条10cm 长,1μm 宽的Al1导线。 电压范围 集总RC 网络 分布RC 网络 0 → 50%(t p ) 0.69 RC 0.38 RC 0 → 63%(τ) RC 0.5 RC 10% → 90%(t r ) 2.2 RC 0.9 RC 0 → 90% 2.3 RC 1.0 RC 使用集总电容模型,源电阻R Driver =10 k Ω,总的集总电容C lumped =11 pF t 50% = 0.69 ? 10 k Ω ? 11pF = 76 ns t 90% = 2.2 ? 10 k Ω ? 11pF = 242 ns 例4.6 树结构网络的RC 延时 节点i 的Elmore 延时: τDi = R 1C 1 + R 1C 2 + (R 1+R 3) C 3 + (R 1+R 3) C 4 + (R 1+R 3+R i ) C i 例4.7 电阻-电容导线的时间常数 总长为L 的导线被分隔成完全相同的N 段,每段的长度为L/N 。因此每段的电阻和电容分别为rL/N 和cL/N R (= rL) 和C (= cL) 是这条导线总的集总电阻 和电容()()()N N RC N N N rcL Nrc rc rc N L DN 2121 (22) 22 +=+=+++??? ??=τ 结论:当N 值很大时,该模型趋于分布式rc 线;一条导线的延时是它长度L 的二次函数;分布rc 线的延时是按集总RC 模型预测的延时的一半. 2rcL 22= RC DN =τ 例4.8 铝线的RC 延时.考虑长10cm 宽、1μm 的Al1导线,使用分布RC 模型,c = 110 aF/μm 和r = 0.075 Ω/μm t p = 0.38?RC = 0.38 ? (0.075 Ω/μm) ? (110 aF/μm) ? (105 μm)2 = 31.4 ns Poly :t p = 0.38 ? (150 Ω/μm) ? (88+2?54 aF/μm) ? (105 μm)2 = 112 μs Al5: t p = 0.38 ? (0.0375 Ω/μm) ? (5.2+2?12 aF/μm) ? (105 μm)2 = 4.2 ns 例4.9 RC 与集总C 假设驱动门被模拟成一个电压源,它具有一定大小的电源内阻R s 。 应用Elmore 公式,总传播延时: τD = R s C w + (R w C w )/2 = R s C w + 0.5r w c w L 2 及 t p = 0.69 R s C w + 0.38 R w C w 其中,R w = r w L ,C w = c w L 假设一个电源内阻为1k Ω的驱动器驱动一条1μm 宽的Al1导线,此时L crit 为 2.67cm 第五章CMOS 反相器 静态CMOS 的重要特性:电压摆幅等于电源电压 → 高噪声容限。逻辑电平与器件的相对尺寸无关 → 晶体管可以采用最小尺寸 → 无比逻辑。稳态时在输出和V dd 或GND 之间总存在一条具有有限电阻的通路 → 低输出阻抗 (k Ω) 。输入阻抗较高 (MOS 管的栅实际上是一个完全的绝缘体) → 稳态输入电流几乎为0。在稳态工作情况下电源线和地线之间没有直接的通路(即此时输入和输出保持不变) → 没有静态功率。传播延时是晶体管负载电容和电阻的函数。 门的响应时间是由通过电阻R p 充电电容C L (电阻R n 放电电容C L )所需要的时间决定的 。 开关阈值V M 定义为V in = V out 的点(在此区域由于V DS = V GS ,PMOS 和NMOS 总是饱和的) r 是什么:开关阈值取决于比值r ,它是PMOS 和NMOS 管相对驱动强度的比 DSATn n DSATp p DD M V k V k V V = ,r r 1r +≈ 一般希望V M = V DD /2 (可以使高低噪声容限具有相近的值),为此要求 r ≈ 1 例5.1 CMOS 反相器的开关阈值 通用0.25μm CMOS 工艺实现的一个CMOS 反相器的开关阈值处于电源电压的中点处。 所用工艺参数见表3.2。假设V DD = 2.5V ,最小尺寸器件的宽长比(W/L)n 为1.5 ()()()()()() ()() V V L W V V V V k V V V V k L W L W M p DSATp Tp M DSATp p DSATn Tn M DSATn n n p 25.125.55.15.35.320.14.025.1263.043.025.10.163.01030101152266==?==----?-???----=---= 分析: V M 对于器件比值的变化相对来说是不敏感 的。将比值设为3、2.5和2,产生的V M 分别为1.22V 、1.18V 和 1.13V ,因此使PMOS 管的宽度小于完全对称所要求的值是可以接受的。 增加PMOS 或NMOS 宽度使V M 移向V DD 或GND 。不对 称的传输特性实际上在某些设计中是所希望的。 噪声容限:根据定义,V IH 和V IL 是dV out /dV in = -1(= 增益)时反相器的工作点 逐段线性近似V IH = V M - V M /g V IL = V M + (V DD - V M )/g 过渡区可以近似为一段直线,其增益等于在开关阈值V M 处的增益g 。它与V OH 及 V OL 线的交点用来定义V IH 和V IL 。点。

奥本海姆 信号与系统 习题参考答案 电子科技大学

Chapter 2 2.1 Solution: Because x[n]=(1 2 0 –1)0, h[n]=(2 0 2)1-, then (a). So, ]4[2]2[2]1[2][4]1[2][1---+-+++=n n n n n n y δδδδδ (b). according to the property of convolutioin: ]2[][12+=n y n y (c). ]2[][13+=n y n y 2.3 Solution: ][*][][n h n x n y = ][][k n h k x k -= ∑∞ -∞= ∑∞ -∞ =-+--= k k k n u k u ]2[]2[)21(2 ][2 11)21()21(][)21(1 2)2(02 22n u n u n n k k --==+-++=-∑ ][])2 1 (1[21n u n +-= the figure of the y[n] is: 2.5 Solution: We have known: ?? ?≤≤=elsewhere n n x ....090....1][,,, ???≤≤=elsewhere N n n h ....00....1][, , ,(9≤N )

Then, ]10[][][--=n u n u n x , ]1[][][---=N n u n u n h ∑∞ -∞ =-= =k k n u k h n h n x n y ][][][*][][ ∑∞ -∞ =-------= k k n u k n u N k u k u ])10[][])(1[][( So, y[4] ∑∞ -∞ =-------= k k u k u N k u k u ])6[]4[])(1[][( ???????≥≤=∑∑==4,...14, (14) N N k N k =5, then 4≥N And y[14] ∑∞ -∞ =------= k k u k u N k u k u ]) 4[]14[])(1[][( ???????≥≤=∑∑==14,...114, (114) 5 5 N N k N k =0, then 5 1 电子科技大学 2004年攻读工程硕士专业学位研究生入学试题 考试科目:数字电路 注意事项: 所有答案必须写在答题纸上,否则答案无效。 一、单项选择题(20分,每小题2分) 1.(25.1)10的二进制数是( )。 A. 10011.0001 B. 11001.0001 C. 10011.1000 D. 10011.1000 2.11101的补码是( )。 A. 00011 B. 00010 C. 10011 D. 10010 3.正逻辑的“或”门在负逻辑中是( )门。 A. 或门 B. 与门 C. 或非门 D. 与非门 4.若输入变量A ,B 全为1时,输出F=0,则其输出与输入的关系是( )。 A. 异或 B. 同或 C .与非 D. 或非 5.已知F=BD ABC +,选出下列( )可以肯定使F=0的情况: A. A=0,BC=1 B. B=1,C=1 C. C=1,D=0 D. BC=1,D=1 6.n 变量的最小项应有( )个。 A. n B. 2n C .n 2 D. 2n 7.逻辑函数)(C A B A F +=的对偶函数'F 是 ( )。 A.)('C A B A F ++= B. )('C A B A F ++= C. )('C A B A F ++= D. ) ('C A B A F += 8.时序逻辑电路中一定包含( )。 A. 触发器 B. 组合逻辑电路 C. 移位寄存器 D. 存储器 9.如右图所示逻辑电路的逻辑关系是( )。 A. A B B A F += B. ))((B A B A F ++= C. B A AB F += D.))((B A B A F ++= 10.))((C A B A F ++=,当B=0,且( )时,电路存在竞争-冒险。 A. 0=A B. 1=A C. 0=C D.1=C 二、化简(10分,每小题5分) 1. 用公式法化简下列逻辑函数为F 积之和式。 C AB C B BC A AC F ++=+ 2. 用卡若图法化简)15,11,7,5,3,1()13,9,6,4,0(),,,d m D C B A F ∑+∑=(为最简与或式。 图一 电子科技大学数字电路 期末考试样题 HUA system office room 【HUA16H-TTMS2A-HUAS8Q8-HUAH1688】 一、填空题 1.五个变量构成的所有最小项之和等于 ( )。 2.已知某数的二进制原码表示为 ( 110110) 2 , 则其对应的8-bit 补码表示为 ( )2。 3.已知∑=C B A F ,,)3,0(,则∑='C B A F ,,( )。 4.要使D 触发器按'*Q Q =工作,则D 触发器的输入D=( )。 5.用移位寄存器产生1101010序列,至少需要( )位的移位寄存器。 二、单项选择题: 1. 若要将一异或门当作反相器(非门)使用,则输入端A 、B 端的连接方式是( )。 A. A 或B 中有一个接“0” B. A 或B 中有一个接“1” C. A 和B 并联使用 D. 不能实现 2.组合电路的竞争冒险是由于( )引起的。 A. 电路不是最简 B. 电路有多个输出 C. 电路中使用不同的门电路 D. 电路中存在延时 3.某一逻辑函数真值表确定后,下面描述该函数逻辑功能的表达式中,具有唯一性的是( )。 A .该逻辑函数的最简与或式 B .该逻辑函数的积之和标准型 C .该逻辑函数的最简或与式 D .该逻辑函数的和之积式 4.若最简状态转换表中,状态数为n ,则所需状态变量数K 为 ( )的整数. A .n K 2log = B .n K 2log < C . n K 2log ≥ D . n K 2log ≤ 5.某计数器的状态转换图如图1所示,其该计数器的模为( )。 A . 八 B. 五 C. 四 D. 三 三、 组合电路分析: 1.求逻辑函数 Z Y X Y X Z X F ?'?+?+?'= 的最简积之和表达式。 2.已知逻辑函数∑=Z Y X F ,,)7,5,1(, 请写出该函数的标准和(最小项之和)表达式: 3.找出逻辑表达式X W Y W F ?+'?'=对应的电路的所有静态冒险。 四、组合电路设计: 1、试用一片三输入八输出译码器74X138和适当的与非门实现函数: 画出电路连接图。译码器如右图所示。 一、设计目标:尝试对语音信号进行时频域分析和处理的基本方法 二、设计工具:MATLAB 三、设计原理: 通过MATLAB的函数wavread()可以读入一个.wav格式的音频文件,并将该文件保存到指定的数组中。例如下面的语句(更详细的命令介绍可以自己查阅MATLAB的帮助)中,将.wav读入后存放到矩阵y中。 y = wavread('Yourwav.wav'); 对于单声道的音频文件,y只有一行,即一个向量;对于双声道的音频文件,y有两行,分别对应了两个声道的向量。我们这里仅对一个声道的音频进行分析和处理即可。注意:.wav文件的采样频率为44.1KHz,采样后的量化精度是16位,不过我们不用关心其量化精度,因为在MATLAB读入后,已将其转换成double 型的浮点数表示。 四、设计要求 在获得了对应音频文件的数组后,我们可以对其进行一些基本的分析和处理。可以包括: 1、对语音信号进行频域分析,找到语音信号的主要频谱成分所在的带宽,验证 为何电话可以对语音信号采用8KHz的采样速率。 2、分析男声和女声的差别。我们知道男声和女声在频域上是有些差别的,一般 大家都会认为女声有更多高频的成分,验证这种差别。同时,提出一种方法,能够对一段音频信号是男声信号、还是女声信号进行自动的判断。 3、.wav文件的采样速率为44.1KHz,仍然远远高于我们通常说的语音信号需要 的频谱宽度,例如在电话对语音信号的采样中,我们仅仅使用8KHz的采样速率。对读入的音频数据进行不同速率的降采样,使用wavplay()命令播放降采样后的序列,验证是否会对信号的质量产生影响。降采样的方法很简单,例如命令y = wavread('SpecialEnglish.wav');将语音文件读入后保存在向量y中,这时对应的采样频率为44.1KHz。使用y1 = y(1:2:length(y)) 电子科技大学通信学院标准实验报告(实验)课程名称信号的基本表示及时域 电子科技大学教务处制表 电 子 科 技 大 学 实 验 报 告 学生姓名: 学 号: 指导教师: 实验地点: 基础实验大楼306,308 实验时间: 一、实验室名称:数字信号处理实验室 二、实验项目名称:基于Simulink 的LTI 因果系统的建模 三、实验学时:4 四、实验原理: 1.系统的方框图表示 N 阶线性实系数微分方程和差分方程描述的因果LTI 系统的系统函数H(s)、H(z)可分别表示如下: 120121212()1M M N N b b s b s b s H s a s a s a s ------+++ += +++ + 120121212()1M M N N b b z b z b z H z a z a z a z ------+++ += +++ + 由上面两式容易得到系统的基本组成单元。连续时间系统需用的3 种基本运算器为:数乘器、加法器和积分器;离散时间系统常用的基本运算器为:数乘器、加法器和单位延迟器。如图3-1所示。 系统函数的代数属性为分析LTI 系统的互联和由微分或差分方程描述的LTI 系统方框图表示的构成提供了一个方便的工具。系统的方框图连接一般有直接型、级联型和并联型3 种 实现结构。以连续时间系统为例,如图3-2。 (a)连续/离数乘器 (b)连续/离加法器 (c)积分器 (d)单位延迟器 图3-1 连续/离散时间基本运算单元模型 )(s X ) (s Y (a) 直接型的实现框图 (s X ) (s Y (b) 级联型的实现框图 ) (s X ) (s Y (c) 并联型的实现框图 图3-2 系统方框图的基本实现结构电子科技大学年数字电路试题

电子科技大学数字电路期末考试样题完整版

电子科大信号与系统语音信号分析课程设计报告

电子科大信号与系统实验三报告