AllegroSI信号完整性仿真激励源设置

DDR信号完整性仿真频率的确定

——孙海峰仿真过程中,我们必须了解如何来确定各类总线的仿真激励源,即Memory Contoller-DIMM之间的各类总线信号工作中的实际频率及其时序特性等,或者认为是DDR-DIMM工作中的外部输入激励信号——因为仿真过程中,必须设置DIMM的模拟激励源,即CPU驱动端的信号,才能仿真DIMM接收端信号SI/窜扰等状况。

实际工作中,DDR各类信号工作频率特征如下图所示:

在此基础上,我们如何确定DDR最佳的仿真激励源,如何确定最佳SI仿真频率呢?接下来,将做出详细的阐述。

1、确定DDR核心频率

DDR核心频率,即DDR上DRAM颗粒的工作频率,它与DDR数据传输位数有关,由于:DDR等效数据传输频率=DRAM核心频率×DDR读取位数,那么我们即可了解DRAM核心频率=数据等效传输频率/读取位数。

对于不同类型的DDR,数据读取位数为:

DDR1(DDR SDRAM):2 bit pre-fetch,同时读取(预取)2n的数据——数据读取位数2;

DDR2:4 bit pre-fetch,同时读取(预取)4n的数据——数据读取位数4;

DDR3:8 bit pre-fetch,同时读取(预取)8n的数据——数据读取位数8;结论:我们可以从数据传输频率,结合DDR类型,计算出核心频率。

2、确定DDR Controller(CPU)-DDR差分时钟仿真激励源

——CK+/CK-差分时钟总线

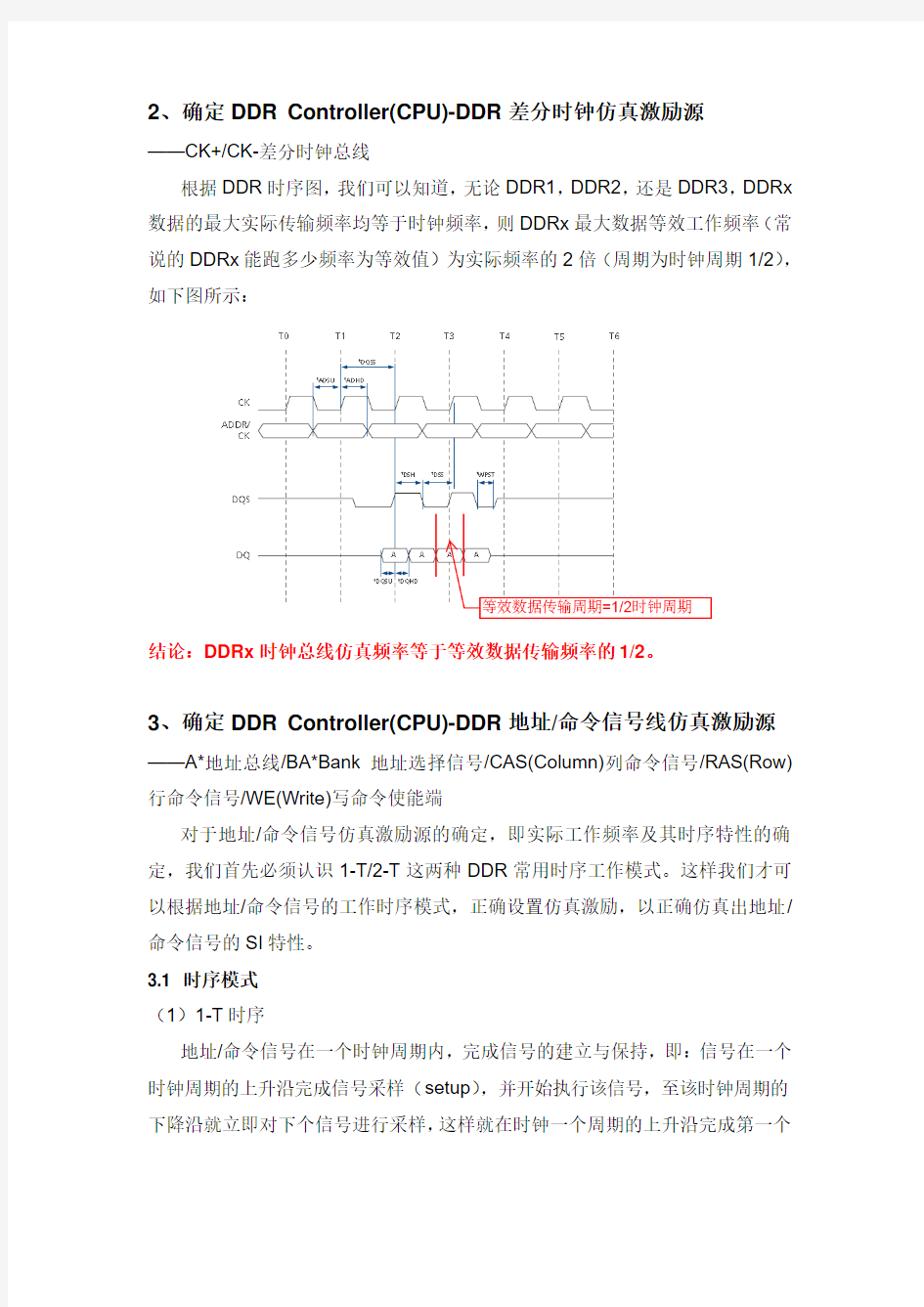

根据DDR时序图,我们可以知道,无论DDR1,DDR2,还是DDR3,DDRx 数据的最大实际传输频率均等于时钟频率,则DDRx最大数据等效工作频率(常说的DDRx能跑多少频率为等效值)为实际频率的2倍(周期为时钟周期1/2),如下图所示:

结论:DDRx时钟总线仿真频率等于等效数据传输频率的1/2。

3、确定DDR Controller(CPU)-DDR地址/命令信号线仿真激励源——A*地址总线/BA*Bank地址选择信号/CAS(Column)列命令信号/RAS(Row)行命令信号/WE(Write)写命令使能端

对于地址/命令信号仿真激励源的确定,即实际工作频率及其时序特性的确定,我们首先必须认识1-T/2-T这两种DDR常用时序工作模式。这样我们才可以根据地址/命令信号的工作时序模式,正确设置仿真激励,以正确仿真出地址/命令信号的SI特性。

3.1 时序模式

(1)1-T时序

地址/命令信号在一个时钟周期内,完成信号的建立与保持,即:信号在一个时钟周期的上升沿完成信号采样(setup),并开始执行该信号,至该时钟周期的下降沿就立即对下个信号进行采样,这样就在时钟一个周期的上升沿完成第一个

信号采样,并开始运行,在相同时钟周期的下降沿立即对下个信号进行采样,这样地址/命令信号即在一个时钟周期内完成建立与保持,如下图所示。

由此可知:信号在一个时钟周期的上升沿和下降沿均采样!

(2)2-T时序

地址/命令信号在两个时钟周期内,完成信号的建立并保持较长的时间,以便地址/命令能够得到充分执行。即:信号在第一个时钟周期的上升沿完成采样(setup),并开始运行该信号命令,至第二个时钟周期,信号完成执行后(Hold)处于无效电平状态NOP,至第三个时钟周期的上升沿,下一个信号才开始采样,这样地址/命令信号在两个时钟周期内刚好完成一次数据建立与保持,此即为地址/命令信号时序的2-T模式,如下图所示。

由此可知:信号在只在时钟的上升沿采样!

两种时序模式的优缺点如下:

1-T时序地址/命令信号实现效率高,每个周期都能进行信号的传递与执行;然而,缺点也很明显,一个地址/命令与下一个地址/命令信号之间,往往没有信

号没有足够的建立时间与保持时间,没有足够的信号调整时间,时序上得不到保证,需要进行严格的SI仿真才能完成设计。

2-T时序下地址/命令信号具有足够的信号响应时间,有足够的建立时间与保持时间,时序得到有效的保证,能够确保地址/命令信号的正确传输;然而,这种方式信号的利用效率没有1-T时序高。

3.2 地址/命令信号仿真激励源

(1)仿真频率确定

由时序模式的不同,我们可以确定:在1-T模式下,非周期的地址/命令信号的最大工作频率即为A0-A1=0-1-0-1…状态下,等效为2倍时钟频率(T ADD=2T CLK);同理,在2-T模式下,地址/命令信号的最大工作频率是时钟频率的1/4(T ADD =4×T ADD)。

例如:DDR2 533工作在2-T模式下,数据总线频率533MHz,则时钟总线频率266MHz,地址/命令总线工作频率即为133/2=67MHz,且此推论符合DDR2器件资料定义标准(最大电平转换效率为工作频率2倍,即133MHz),如下图所示。

(2)时序特性确定

两种时序工作模式下,对应地址/命令信号与时钟信号的标准时序特性如下图所示:

结论:地址/命令信号1-T时序模式下,地址/命令仿真频率=1/2时钟频率,此为最差情况;2-T时序模式下,地址/命令仿真频率=1/4时钟频率=1/8数据等效传输频率。无论哪种时序模式,命令信号提前时钟交叉点1/2时钟周期,地址信号也提前时钟交叉点1/2个时钟周期(时钟交叉点为信号采样点)。

4、确定DDR Controller(CPU)-DDR控制信号线仿真激励源——CKE时钟使能端/CS片选信号

对于控制信号仿真激励源,无论地址/命令信号工作在什么时序模式下(1-T/2-T),控制信号始终工作在1-T时序模式,即控制信号逻辑状态总宽度(逻辑1+逻辑0)等于时钟周期,如下图所示。

由上图可以了解,控制信号逻辑“1-0”周期最大为时钟周期T(CLK),然而由于高阻状态在仿真中无法实现,因此,信号完整性仿真中,仍然设定控制信号总周期为2T(CLK),即:有效电平宽度(逻辑1)+无效电平宽度(逻辑0)+高阻宽度(无效逻辑)。

结论:控制信号CS#/CKE仿真频率=1/2时钟频率。控制信号提前时钟1/2时钟周期。

5、如何确定DDR Controller(CPU)-DDR源同步信号仿真激励源——DQS*源同步总线

源同步总线信号即为数据总线的“时钟”,源同步信号与时钟信号一致,只是由于DDR工作产生的延时,会使DQS与CLK之间产生少两延时,如下图所示。

结论:源同步信号是与时钟存在一定偏移的,并与时钟频率一致的周期信号(f DQS=f CLK)。

6、确定DDR Controller(CPU)-DDR数据总线仿真激励源

——DQ*数据总线

DDR数据信号传输频率没有固定值,因为每半个时钟周期数据传输一个状态,而不同状态组成的数据流实际没有周期性,因为所传输的数据时随机的——数据信号是非周期信号。当传输数据为0-1-0-1-……交替状态时,数据信号达到最大传输频率,并等于时钟频率。因此非周期性的数据信号最大可能的工作频率等于时钟频率。其时序特性如下图所示。

等效数据传输率的概念——数据信号传输时,每个状态即一个数据,即为一个等效数据周期周期,因此,数据信号总线存在等效工作频率的概念,即为时钟频率的2倍。

结论:数据信号仿真频率等于时钟频率。数据信号提前源同步时钟1/4时钟周期。

当然,一般情况下,我们是根据系统数据总线所需的工作频率,来选择时钟、核心频率等参数,并由此来选择DDR型号的,因此数据总线工作频率是仿真时计算各类总线频率的基础。

综上所述,我们可以了解DDRx各类总线工作频率的关系,由此我们可以确定各类总线信号进行信号完整性仿真时,激励源的频率设置。这样就可以帮助我们在信号完整性仿真中正确选择激励频率,以确保仿真结果的正确性与设计指导性。

例如,DDR-333(DDR1)信号完整性仿真频率可依次确定如下:

(1)等效数据传输频率333MHz;

(2)差分时钟仿真频率166MHz;

(3)地址/命令信号仿真频率88MHz;

(4)控制信号仿真频率166MHz;

(5)源同步信号仿真频率166MHz;

(6)数据总线仿真频率166MHz

附录1:

以DDR2为例,信号工作频率为:

其中,各项参数意义如下:

核心频率——DDR内部颗粒工作频率;

总线频率——DDR外部输入的时钟信号频率;

等效传输频率——DDR数据信号为非周期性信号,其等效频率;

数据传输率——DDR外部数据总线DQ上数据的传输速率,与等效总线传输频率相对应,即多少字节每秒MB/S,如:1MHz=1MT/s=8MB/s

五款信号完整性仿真工具介绍

现在的高速电路设计已经达到GHz的水平,高速PCB设计要求从三维设计理论出发对过孔、封装和布线进行综合设计来解决信号完整性问题。高速PCB设计要求中国工程师必须具备电磁场的理论基础,必须懂得利用麦克斯韦尔方程来分析PCB设计过程中遇到的电磁场问题。目前,Ansoft公司的仿真工具能够从三维场求解的角度出发,对PCB设计的信号完整性问题进行动态仿真。 (一)Ansoft公司的仿真工具 现在的高速电路设计已经达到GHz的水平,高速PCB设计要求从三维设计理论出发对过孔、封装和布线进行综合设计来解决信号完整性问题。高速PCB设计要求中国工程师必须具备电磁场的理论基础,必须懂得利用麦克斯韦尔方程来分析PCB设计过程中遇到的电磁场问题。目前,Ansoft公司的仿真工具能够从三维场求解的角度出发,对PCB设计的信号完整性问题进行动态仿真。 Ansoft的信号完整性工具采用一个仿真可解决全部设计问题: SIwave是一种创新的工具,它尤其适于解决现在高速PCB和复杂IC封装中普遍存在的电源输送和信号完整性问题。 该工具采用基于混合、全波及有限元技术的新颖方法,它允许工程师们特性化同步开关噪声、电源散射和地散射、谐振、反射以及引线条和电源/地平面之间的耦合。该工具采用一个仿真方案解决整个设计问题,缩短了设计时间。 它可分析复杂的线路设计,该设计由多重、任意形状的电源和接地层,以及任何数量的过孔和信号引线条构成。仿真结果采用先进的3D图形方式显示,它还可产生等效电路模型,使商业用户能够长期采用全波技术,而不必一定使用专有仿真器。 (二)SPECCTRAQuest Cadence的工具采用Sun的电源层分析模块: Cadence Design Systems的SpecctraQuest PCB信号完整性套件中的电源完整性模块据称能让工程师在高速PCB设计中更好地控制电源层分析和共模EMI。 该产品是由一份与Sun Microsystems公司签署的开发协议而来的,Sun最初研制该项技术是为了解决母板上的电源问题。 有了这种新模块,用户就可根据系统要求来算出电源层的目标阻抗;然后基于板上的器件考虑去耦合要求,Shah表示,向导程序能帮助用户确定其设计所要求的去耦合电容的数目和类型;选择一组去耦合电容并放置在板上之后,用户就可运行一个仿真程序,通过分析结果来发现问题所在。 SPECCTRAQuest是CADENCE公司提供的高速系统板级设计工具,通过它可以控制与PCB layout相应的限制条件。在SPECCTRAQuest菜单下集成了一下工具: (1)SigXplorer可以进行走线拓扑结构的编辑。可在工具中定义和控制延时、特性阻抗、驱动和负载的类型和数量、拓扑结构以及终端负载的类型等等。可在PCB详细设计前使用此工具,对互连线的不同情况进行仿真,把仿真结果存为拓扑结构模板,在后期详细设计中应用这些模板进行设计。 (2)DF/Signoise工具是信号仿真分析工具,可提供复杂的信号延时和信号畸变分析、IBIS 模型库的设置开发功能。SigNoise是SPECCTRAQUEST SI Expert和SQ Signal Explorer Expert进行分析仿真的仿真引擎,利用SigNoise可以进行反射、串扰、SSN、EMI、源同步及系统级的仿真。 (3)DF/EMC工具——EMC分析控制工具。 (4)DF/Thermax——热分析控制工具。 SPECCTRAQuest中的理想高速PCB设计流程: 由上所示,通过模型的验证、预布局布线的space分析、通过floorplan制定拓朴规则、由规

cadence信号完整性仿真步骤

Introduction Consider the proverb, “It takes a village to raise a child.” Similarly, multiple design team members participate in assuring PCB power integrity (PI) as a design moves from the early concept phase to becoming a mature product. On the front end, there’s the electrical design engineer who is responsible for the schematic. On the back end, the layout designer handles physical implemen-tation. Typically, a PI analysis expert is responsible for overall PCB PI and steps in early on to guide the contributions of others. How quickly a team can assure PCB PI relates to the effectiveness of that team. In this paper, we will take a look at currently popular analysis approaches to PCB PI. We will also introduce a team-based approach to PCB PI that yields advantages in resource utilization and analysis results. Common Power Integrity Analysis Methods There are two distinct facets of PCB PI – DC and AC. DC PI guarantees that adequate DC voltage is delivered to all active devices mounted on a PCB (often using IR drop analysis). This helps to assure that constraints are met for current density in planar metals and total current of vias and also that temperature constraints are met for metals and substrate materials. AC PI concerns the delivery of AC current to mounted devices to support their switching activity while meeting constraints for transient noise voltage levels within the power delivery network (PDN). The PDN noise margin (variation from nominal voltage) is a sum of both DC IR drop and AC noise. DC PI is governed by resistance of the metals and the current pulled from the PDN by each mounted device. Engineers have, for many years, applied resistive network models for approximate DC PI analysis. Now that computer speeds are faster and larger addressable memory is available, the industry is seeing much more application of layout-driven detailed numerical analysis techniques for DC PI. Approximation occurs less, accuracy is higher, and automation of How a Team-Based Approach to PCB Power Integrity Analysis Yields Better Results By Brad Brim, Sr. Staff Product Engineer, Cadence Design Systems Assuring power integrity of a PCB requires the contributions of multiple design team members. Traditionally, such an effort has involved a time-consuming process for a back-end-focused expert at the front end of a design. This paper examines a collaborative team-based approach that makes more efficient use of resources and provides more impact at critical points in the design process. Contents Introduction (1) Common Power Integrity Analysis Methods (1) Applying a Team-Based Approach to Power Integrity Analysis (3) Summary (6) For Further Information (7)

PCB板级信号完整性的仿真及应用

作者简介:曹宇(1969-),男,上海人,硕士,工程师. 第6卷第 6期 2006年12月泰州职业技术学院学报 JournalofTaizhouPolytechnicalInstituteVol.6No.6 Dec.2006摘要:针对高速数字电路印刷电路板的板级信号完整性,分析了IBIS模型在板级信号完整 性分析中的作用。利用ADS仿真软件,采用电磁仿真建模和电路瞬态仿真测试了某个 实际电路版图,给出了实际分析结果。 关键词:信号完整性;IBIS;仿真;S参数 中图分类号:TP391.9文献标识码:A文章编号:1671-0142(2006)06-0030-03 信号完整性(SI,SignalIntegrity)的概念是针对高速数字信号提出来的。以往的数字产品,其时钟或数据频率在几十兆之内时,信号的上升时间大多在几个纳秒,甚至几十纳秒以上。数字化产品设计工程师关注最多的是“数字设计”保证逻辑正确。随着数字技术的飞速发展,原先只是在集成电路芯片设计中需要考虑的问题[1]在PCB板级设计中正在逐步显现出来,并由此提出了信号完整性的概念。 在众多的讲述信号完整性的论文和专著中[2,3],对信号完整性的描述都是从信号传输过程中可能出现的问题(比如串扰,阻抗匹配,电磁兼容,抖动等)本身来讨论信号完整性,对信号完整性没有一个统一的定义。事实上,信号完整性是指信号在通过一定距离的传输路径后在特定接收端口相对指定发送端口信号的还原程度,这个还原程度是指在指定的收发参考端口,发送芯片输出处及接收芯片输入处的波形需满足系统设计的要求[4]。 1、板级信号完整性分析 1.1信号完整性分析内容的确定 信号完整性分析工作是一项产品开发全流程工作,从产品设计阶段开始一直延续到产品定型。PCB板级设计同样如此。在系统设计阶段,产品还没有进入试制,需要建立相应的系统模型并得到仿真结果以验证设计思想和设计体系正确与否,这个阶段称前仿真;前仿真通过后,产品投入试制,样品出来后再进行相应的测试和仿真,这个阶段称后仿真。假如将每一块PCB板视为一个系统,影响这个系统正常工作的信号问题涉及到所有的硬件和软件,包括芯片、封装、PCB物理结构、电源及电源传输网络和协议。 对系统所有部分都进行仿真验证是不现实的。应根据系统设计的要求选定部分内容进行测试仿真。本文所提及的“板级信号完整性分析”仅针对芯片引脚和走线的互连状态分析。 当被传输的信号脉冲时间参量(如上升时间、传输时间等)已缩短至和互连线上电磁波传输时间处于同一个量级时,信号在互连线上呈现波动效应,应采用微波传输线或分布电路的模型来对待互连线,从而产生了时延、畸变、回波、相邻线之间的干扰噪声等所谓的“互连效应”[1]。 假设PCB板上芯片引脚的输入输出信号都是“干净”的,那么只要考虑互连线路本身的互连效应。事实上,每个芯片引脚在封装时都有其独特的线路特性,这些特性是由其内部的晶体管特性决定的,同样的信号在不同引脚上的传输效率差异很大。因此,在分析信号传输的互连效应时必须考虑芯片内部的电路特性以提取相对准确的电路模型,并在此基础上作进一步的分析。这个模型就是在业界被广泛使用的IBIS模型。 1.2IBIS标准模型的建立 PCB板级信号完整性的仿真及应用 曹宇,丁志刚,宗宇伟 (上海计算机软件技术开发中心,上海201112)

基于dds的实用信号源的设计与制作 完美版

摘要 信号发生器是一种能产生标准信号的电子仪器,是工业生产和电工、电子实验室中经常使用的电子仪器之一。本文采用分立元器件设计了可输出正弦波和脉冲波的信号发生器,介绍了信号发生器的工作原理、电路参数计算方法、电路仿真结果,并进行了电路制作。 所设计的信号发生器由振荡电路、稳幅电路、正弦波调幅电路、电压比较电路、脉冲波调幅电路组成。采用RC振荡方式产生振荡信号,通过二极管IN4148和运放TL082实现振荡信号稳幅,调幅之后输出正弦波信号,再经电压比较器和调幅电路实现脉冲波的占空比和幅度的变化。采用了多级电阻和多级双联电位器实现频率的分段和步进。 本文设计的信号发生器具有结构简单、成本低、体积小等特点,经仿真和实际电路制作验证,其产生的正弦波和脉冲波频率、占空比、信号幅度可调,频率步进5Hz,矩形波可步进调整占空比, 不影响频率, 步长小于1%, 波形有较好的边沿特性。 关键词:信号发生器;频率歩进;占空比

一、实用信号源的设计和制作任务 在给定±15V电源电压条件下,设计并制作一个正弦波和脉冲波信号源。 二、要求 1.基本要求 (1)正弦波信号源 ①信号频率:20Hz~20kHz步进调整,步长为5Hz ②频率稳定度:优于10-4 ③非线性失真系数≤3% (2)脉冲波信号源 ①信号频率:20Hz~20kHz步进调整,步长为5Hz ②上升时间和下降时间:≤1μs ③平顶斜降:≤5% ④脉冲占空比:2%~98%步进可调,步长为2% (3)上述两个信号源公共要求 ①频率可预置。 ②在负载为600Ω时,输出幅度为3V。 ③完成5位频率的数字显示。

2.发挥部分 (1)正弦波和脉冲波频率步长改为1Hz。 (2)正弦波和脉冲波幅度可步进调整,调整范围为100mV~3V,步长为100mV。 (3)正弦波和脉冲波频率可自动步进,步长为1Hz。 (4)降低正弦波非线性失真系数。 三、评分标准 项目 得 分 基本要求设计与总结报告:方案设计与论证,理论计 算与分析,电路图,测试方法与数据,结果 分析 50 实际制作完成情况50 发挥部分完成第一项10 完成第二项10 完成第三项 5 完成第四项 5 特色与创新20

PCB设计与信号完整性仿真

本人技术屌丝一枚,从事PCB相关工作已达8年有余,现供职于世界闻名的首屈一指的芯片设计公司,从苦逼的板厂制板实习,到初入Pcblayout,再到各种仿真的实战,再到今天的销售工作,一步一步一路兢兢业业诚诚恳恳,有一些相关领悟和大家分享。买卖不成也可交流。 1.谈起硬件工作,是原理图,pcb,码农的结合体,如果你开始了苦逼的pcblayout工作,那么将是漫长的迷茫之路,日复一日年复一年,永远搞不完的布局,拉线。眼冒金星不是梦。最多你可以懂得各种模块的不同处理方式,各种高速信号的设计,但永远只能按照别人的意见进行,毫无乐趣。 2.谈起EDA相关软件,形象的说,就普通的PROTEL/AD来说你可能只有3-6K,对于pads 可能你有5-8K,对于ALLEGRO你可能6-10K,你会哀叹做的东西一样,却同工不同酬,没办法这就是市场,我们来不得无意义的抱怨。 3.众所周知,一个PCB从业者最好的后路就是仿真工作,为什么呢?一;你可以懂得各种模块的设计原则,可以优化不准确的部分,可以改善SI/PI可以做很多,这往往是至关重要的,你可以最大化节约成本,减少器件却功效相同;二;从一个pcblayout到仿真算是水到渠成,让路走的更远; 三:现实的说薪资可以到达11-15K or more,却更轻松,更有价值,发言权,你不愿意吗? 现在由于本人已技术转销售,现在就是生意人了哈哈,我也查询过各种仿真资料我发现很少,最多不过是Mentor Graphics 的HyperLynx ,candense的si工具,

但是他们真的太low了,精确度和完整性根本不能保证,最多是定性的能力,无法定量。真正的仿真是完整的die到die的仿真,是完整的系统的,是需要更高级的仿真软件,被收购的xxsigrity,xx ansys,hspicexx,adxx等等,这些软件才是真正的仿真。 本人提供各种软件及实战代码,例子,从基本入门到高级仿真,从电源仿真,到ddr仿真到高速串行仿真,应有尽有,,完全可以使用,想想以后的高薪,这点投入算什么呢?舍不得孩子套不住狼哦。 所有软件全兼容32位和64位系统。 切记本人还提供学习手册,你懂的,完全快速进入仿真领域。你懂的! 希望各位好好斟酌,自己的路是哪个方向,是否想更好的发展,舍得是哲学范畴,投资看得是利润的最大化,学会投资吧,因为他值得拥有,骚年! 注:本人也可提供培训服务,面面俱到,形象具体,包会! 有购买和学习培训兴趣的请联系 QQ:2941392162

实用信号源的设计和制作(DOC)

实用信号源的设计和制作 目录 第1章设计任务书 (1) 1.1任务 (1) 1.2要求 (1) 第2章总体方案设计 (2) 2.1本设计总体方案 (2) 2.2正弦波信号生成方案 (2) 2.2.1振荡信号的生成方法 (3) 2.2.2RC振荡原理与振荡条件 (3) 2.2.3振荡电路的稳幅方法 (5) 2.3频率步进方案 (6) 第3章电路设计和仿真分析 (8) 3.1RC振荡与稳幅电路设计 (8) 3.1.1电路参数计算 (8) 3.1.2电路仿真与分析 (10) 3.2正弦波调幅电路设计 (11) 3.2.1电路参数计算 (11) 3.2.2电路仿真与分析 (12) 3.3脉冲波生成电路设计 (13) 3.3.1电路参数计算 (13) 3.3.2电路仿真与分析 (14) 3.4频率计的设计 (18) 第4章设计总结 (20) 参考文献 (21) 附录Ⅰ仿真电路图 (22) 附录Ⅱ 10MHZ频率计 (23)

第1章设计任务书 1.1任务 在给定±15V电源电压条件下,设计并制作一个正弦波和脉冲波信号源。 1.2要求 1.基本要求 (1)正弦波信号源 ① 信号频率:20Hz~20kHz步进调整,步长为5Hz ② 频率稳定度:优于10-4 ③ 非线性失真系数≤3% (2)脉冲波信号源 ① 信号频率:20Hz~20kHz步进调整,步长为5Hz ② 上升时间和下降时间:≤1μs ③ 平顶斜降:≤5% ④ 脉冲占空比:2%~98%步进可调,步长为2% (3)上述两个信号源公共要求 ① 频率可预置。 ② 在负载为600Ω时,输出幅度为3V。 ③ 完成5位频率的数字显示。 2.发挥部分 (1)正弦波和脉冲波频率步长改为1Hz。 (2)正弦波和脉冲波幅度可步进调整,调整范围为100mV~3V,步长为100mV。(3)正弦波和脉冲波频率可自动步进,步长为1Hz。 (4)降低正弦波非线性失真系数。

Altium Demo系列_信号完整性分析SI仿真

信号完整性分析SI仿真Demo Altium Designer的SI仿真功能,可以在原理图阶段假定PCB环境进行布线前预仿真,帮助用户进行设计空间探索,也可以在PCB布线后按照实际设计环境进行仿真验证,并辅以虚拟端接,参数扫描等功能,帮助用户考察和优化设计,增强设计信心。 1.在Windows下打开SI_demo子目录,双击打开演示案例项目 SI_demo.prjpcb,当前项目树中只有一页原理图SI_demo.schdoc,双击 SI_demo.schdoc打开原理图。观察到图中有U2和U3两个IC器件。 2.为器件指定IBIS模型(如果元件库中该器件已有正确的IBIS模型,则可跳 过步骤2) 通过双击器件U2,弹出以下窗口:

点击Add右边的下拉箭头,选择Signal Integrity,为器件U2指定SI仿真用的IBIS模型。 在弹出的SI模型选择窗口中点击 Import IBIS,选择U2对应的IBIS模 型文件导入,本例中U2的IBIS模型 文件为SI_demo文件夹中的文件 5107_lmi.ibs,后面各窗口一直点击 OK,直到回到原理图界面,U2的模 型设定完成。 双击器件U3,按照同样的步骤为U3 指定IBIS模型,其对应的IBIS模型 文件为:edd2516akta01.ibs

3.为关注的网络设定规则 通过点击主菜单下的Place->Directives->Blanket,放置一个方框,将所关注的网络名称框住(本例中已经框住了LMID00-LMID15共16位数据总线)。 然后同样通过Place->Directives->PCB Layout, 放置一个PCB Rule规则符号,置于方框的边界上。

基于FPGA的实用多功能信号发生器的设计与制作

基于FPGA的实用多功能信号发生器 的设计与制作

基于FPGA的实用多功能信号发生器的设计与制作 摘要 多功能信号发生器已成为现代测试领域应用最为广泛的通用仪器之一,代表了信号源的发展方向。直接数字频率合成(DDS)是二十世纪七十年代初提出的一种全数字的频率合成技术,其查表合成波形的方法可以满足产生任意波形的要求。由于现场可编程门阵列(FPGA)具有高集成度、高速度、可实现大容量存储器功能的特性,能有效地实现DDS技术,极大的提高函数发生器的性能,降低生产成本。 本文首先介绍了函数信号发生器的研究背景和DDS的理论。然后详尽地叙述了利用Verilog HDL描述DDS模块的设计过程,以及设计过程中应注意的问题。文中详细地介绍了多种信号的发生理论、实现方法、实现过程、部分Verilog HDL代码以及利用Modelsim仿真的结果。 文中还介绍了Altera公司的DE2多媒体开发平台的部分功能及使用,并最终利用DE2平台完成了多功能信号发生器的大部分功能。包括由LCD显示和按键输入构成的人机界面和多种信号的发生。数字模拟转换器是BURR-BROWN 公司生产的DAC902。 该信号发生器能输出8种不同的信号,并且能对输出信号的频率、相位以及调制信号的频率进行修改设定。 关键词:信号发生器;DDS;FPGA;DE2

Practical FPGA-based multi function signal generator design and production Abstract Multi function signal generator has become the most widely used in modern testing field of general instrument, and has represented one of the development direction of the source. Direct digital frequency synthesis (DDS) is a totaly digital frequency synthesis technology, which been put forward in the early 1970s. Using a look-up table method to synthetic waveform, it can satisfy any requirement of waveform produce. Due to the field programmable gates array (FPGA) with high integrity, high speed, and large storage properties, it can realize the DDS technology effectively, increase signal generator’s performance and reduce production costs. Firstly, this article introduced the function signal generator of the research background and DDS theory. Then, it described how to design a DDS module by Verilog HDL, and introduced various signal occurs theory, method and the implementation process, Verilog HDL code and simulation results. This paper also introduces the function of DE2 multimedia development platform, and completed most of the functions of multi-function signal generator on DE2 platform finally. Including the occurrence of multiple signal and the man-machine interface which composed by LCD display and key input. Digital-to-analog converters is DAC902, which produced by company BURR-BROWN. This signal generator can output eight different kinds of signals, and the frequency of the output signal, phase and modulation frequency signal also can be modifyed. Key Words: Signal generator; DDS; FPGA; DE2

五款信号完整性仿真分析工具

SI 五款信号完整性仿真工具介绍 (一)Ansoft公司的仿真工具 现在的高速电路设计已经达到GHz的水平,高速PCB设计要求从三维设计理论出发对过孔、封装和布线进行综合设计来解决信号完整性问题。高速PCB 设计要求中国工程师必须具备电磁场的理论基础,必须懂得利用麦克斯韦尔方程来分析PCB设计过程中遇到的电磁场问题。目前,An soft公司的仿真工具能够从三维场求解的角度出发,对PCB 设计的信号完整性问题进行动态仿真。 Ansoft 的信号完整性工具采用一个仿真可解决全部设计问题: Slwave是一种创新的工具,它尤其适于解决现在高速PCB和复杂IC封装中普遍存在的电源输送和信号完整性问题。 该工具采用基于混合、全波及有限元技术的新颖方法,它允许工程师们特性化同步开关噪声、电源散射和地散射、谐振、反射以及引线条和电源/地平面之间的耦合。该工具采用一个仿真方案解决整个设计问题,缩短了设计时间。 它可分析复杂的线路设计,该设计由多重、任意形状的电源和接地层,以及任何 数量的过孔和信号引线条构成。仿真结果采用先进的3D 图形方式显示,它还可产生等效电路模型,使商业用户能够长期采用全波技术,而不必一定使用专有仿 (二)SPECCTRAQuest Cade nee的工具采用Sun的电源层分析模块: Cade nee Design System 的SpeeetraQuest PCB信号完整性套件中的电源完整性模块据称能让工程师在高速PCB设计中更好地控制电源层分析和共模EMI 。 该产品是由一份与Sun Microsystems公司签署的开发协议而来的,Sun最初研制该项技术是为了解决母板上的电源问题。 有了这种新模块,用户就可根据系统要求来算出电源层的目标阻抗;然后基于板上的器件考虑去耦合要求,Shah表示,向导程序能帮助用户确定其设计所要求的去耦合电容的数目和类型;选择一组去耦合电容并放置在板上之后,用户就可运行一个仿真程序,通过分析结果来发现问题所在。 SPECCTRAQuest是CADENCE公司提供的高速系统板级设计工具,通过它可以控制与PCB layout相应的限制条件。在SPECCTRAQuest菜单下集成了一下工具: (1)SigXplorer 可以进行走线拓扑结构的编辑。可在工具中定义和控制延时、特性阻抗、驱动和负载的类型和数量、拓扑结构以及终端负载的类型等等。可在

《信号完整性与电源完整性的仿真分析与设计》

信号完整性与电源完整性的仿真分析与设计 1简介 信号完整性是指信号在通过一定距离的传输路径后在特定接收端口相对指定发送端口信号的还原程度。在讨论信号完整性设计性能时,如指定不同的收发参考端口,则对信号还原程度会用不同的指标来描述。通常指定的收发参考端口是发送芯片输出处及接收芯片输入处的波形可测点,此时对信号还原程度主要依靠上升/下降及保持时间等指标来进行描述。而如果指定的参考收发端口是在信道编码器输入端及解码器输出端时,对信号还原程度的描述将会依靠误码率来描述。 电源完整性是指系统供电电源在经过一定的传输网络后在指定器件端口相对该器件对工作电源要求的符合程度。同样,对于同一系统中同一个器件的正常工作条件而言,如果指定的端口不同,其工作电源要求也不同(在随后的例子中将会直观地看到这一点)。通常指定的器件参考端口是芯片电源及地连接引脚处的可测点,此时该芯片的产品手册应给出该端口处的相应指标,常用纹波大小或者电压最大偏离范围来表征。 图一是一个典型背板信号传输的系统示意图。本文中“系统”一词包含信号传输所需的所有相关硬件及软件,包括芯片、封装与PCB板的物理结构,电源及电源传输网络,所有相关电路实现以及信号通信所需的协议等。从设计目的而言,需要硬件提供可制作的支撑及电信号有源/无源互联结构;需要软件提供信号传递的传输协议以及数据内容。

图1 背板信号传输的系统示意图 在本文的以下内容中,将会看到由于这些支撑与互联结构对电信号的传输呈现出一定的频率选择性衰减,从而会使设计者产生对信号完整性及电源完整性的担忧。而不同传输协议及不同数据内容的表达方式对相同传输环境具备不同适应能力,使得设计者需要进一步根据实际的传输环境来选择或优化可行的传输协议及数据内容表达方式。 为描述方便起见以下用“完整性设计与分析”来指代“信号完整性与电源完整性设计与分析”。 2 版图完整性问题、分析与设计 上述背板系统中的硬件支撑及无源互联结构基本上都在一种层叠平板结构上实现。这种层叠平板结构可以由三类元素组成:正片结构、负片结构及通孔。正片结构是指该层上的走线大多为不同逻辑连接的信号线或离散的电源线,由于在制版光刻中所有的走线都会以相同图形的方式出现,所以被称为正片结构,有时也被称为信号层;负片结构则是指该层上基本上是相同逻辑连接的一个或少数几个连接(通常是电源连接或地连接),通常会以大面积敷铜的方式来实现,此时光刻工艺中用相反图形来表征更加容易,所以被称为负片结构,有时也称为平面层(细分为电源平面层和地平面层);而通孔用来进行不同层之间的物理连接。目前的制造工艺中,无论是芯片、封装以及PCB 板大多都是在类似结构上实现。 1001010… -0.50.00.51.01.5 -1.0 2.0V c o r e , V

Cadence SI信号完整性仿真技术

Cadence PCB SI仿真流程 ——孙海峰 高速高密度多层PCB板的SI/EMC(信号完整性/电磁兼容)问题长久以来一直是设计者所面对的最大挑战。然而,随着主流的MCU、DSP和处理器大多工作在100MHz以上(有些甚至工作于GHz级以上),以及越来越多的高速I/O埠和RF前端也都工作在GHz级以上,再加上应用系统的小型化趋势导致的PCB 空间缩小问题,使得目前的高速高密度PCB板设计已经变得越来越普遍。许多产业分析师指出,在进入21世纪以后,80%以上的多层PCB设计都将会针对高速电路。 高速讯号会导致PCB板上的长互连走线产生传输线效应,它使得PCB设计者必须考虑传输线的延迟和阻抗搭配问题,因为接收端和驱动端的阻抗不搭配都会在传输在线产生反射讯号,而严重影响到讯号的完整性。另一方面,高密度PCB板上的高速讯号或频率走线则会对间距越来越小的相邻走线产生很难准确量化的串扰与EMC问题。SI和EMC的问题将会导致PCB设计过程的反复,而使得产品的开发周期一再延误。 一般来说,高速高密度PCB需要复杂的阻抗受控布线策略才能确保电路正常工作。随着新型组件的电压越来越低、PCB板密度越来越大、边缘转换速率越来越快,以及开发周期越来越短,SI/EMC挑战便日趋严峻。为了达到这个挑战的要求,目前的PCB设计者必须采用新的方法来确保其PCB设计的可行性与可制造性。过去的传统设计规则已经无法满足今日的时序和讯号完整性要求,而必须采取包含仿真功能的新款工具才足以确保设计成功。 Cadence的Allegro PCB SI提供了一种弹性化且整合的信号完整性问题解决方案,它是一种完整的SI/PI(功率完整性)/EMI问题的协同解决方案,适用于高速PCB设计周期的每个阶段,并解决与电气性能相关的问题。 Allegro PCB SI信号完整性分析的操作步骤,就是接下来将要介绍的。

工程师常用模拟电路设计2

工程师常用模拟电路设计、计算、仿真及制作 第二章双极结型三极管、场效应管应用电路 2.1双极结型三极管及其应用电路 2.1.1基极分压式射极偏置共射放大电路 电路如图2.1所示。 共射放大电路是用途非常广泛的低频电压放大电路。也是所有模拟电路教材讨论最多的电路。在设计、制作时有许多需要注意的问题。在图2.1所示电路中。通过仿真,仿真波形如图2.2所示,我们可以看到,电路具有很强的电压放大能力。因此该电路一般作为低频低压放大器使用。在该电路中,其静态工作点: ) (4342 w 12R R I V V I I R V V I I V R R R R V C CC CE C B BE B E C CC B +-== -= ≈++=β下取β=100,V BE =0.7V ,R W 下=0.75R W ,则: V B =3.3V ,I C =1.3mA ,I B =13uA ,V CE =5.5V. 电路的电压放大倍数为: 图2.2共射放大电路仿真波形 图2.1共射放大电路原理图

E T V I V R R A )(ββ++=- =1200r r ) //(be be 53计算可得: r be ≈2.22K Ω,A V ≈-68. 电路的输入、输出电阻分别为: Ri=(R 1+R W 下)//R 2//r be ≈r be =2.22K Ω Ro=R 3=3K Ω. 由图2.3可知,该电路的中频增益为37.187dB 。 利用仿真测出该电路的f L ≈75Hz ,f H ≈23.6MHz 。 通频带宽度约为23.6MHz. 该电路在设计与制作中应注意如下问题: (1)多数情况下,电源电压一般取9~15V 左右。因此静态工作点中的V B 一般取3~5V ,R1中流过的电流一般取基极电流的5~10倍。因此可以大致确定R1、R2和Rw 的数值。 (2)通过调整Rw 的值,确定合适的静态工作点。增减Rw ,使饱和失真和截止失真最小或者两者基本同时出现,该点即为合适的静态工作点。 (3)电路的下限频率与耦合电容和旁路电容有关,适当增大耦合电容和旁路电容可使下限频率下降。 2.1.2共集电极放大电路 共集电极放大电路又称为射极输出器或射极跟随器。电路如图2.4所示。 共集电极放大电路静态工作点的要求与共射电路类似,不再赘述。 在模拟电路教材中,我们已知: (1)共集电极电路A V ≈1; (2)输入电阻大; (3)输出电阻小。 (4)电路具有很强的电流放大作用: A i =1+β 共集电极放大电路在设计制作中应注意: (1)电路的静态工作点的调试与共射电路类似; (2)充分利用共集电极电路的特性,如电压跟随作用,阻抗变换作用、电流放大作用图2.3共射放大电路仿真频率测试 图2.4共集电极放大电路

实用信号源的设计和制作

实用信号源的设计和制作(综合课程设计报告)

目录 一、实验要求 (3) 1. 任务: (3) 2. 技术指标: (3) 3. 要求: (4) 4. 主要参考元件: (4) 二、方案设计与论证 (4) 【总体方案设计】 (4) 【可行性分析】 (4) 1.信号发生芯片选取 (4) 2.频率调节与方波占空比调节 (5) 3.测频与数码管显示 (7) 三、理论分析与计算 (7) 1) ICL8038外围电路电阻电容选取 (7) 2)LM318运算放大部分 (9) 3)NE555时基电路 (9) 4)CD4026时序分析 (10) 四、测试方法、数据及现象 (11) 五、问题分析及解决 (18) 六、实验总结 (20)

一、实验要求 1. 任务: 在给定15V电源电压条件下, 设计并制作一个信号源。 2. 技术指标: 【要求1】: (1) 正弦波信号源(20HZ~10KHZ) a、信号频率:20HZ~10KHZ连续可调; b、频率稳定度:优于10-4 c、非线性失真系数:≤3%; (2) 脉冲波信号源(20HZ~10KHZ) a、信号频率:20HZ~10KHZ连续可调, b、上升和下降时间:≤1us; c、平顶斜降:≤ 5%。 d、脉冲占空比:2%到98%连续可调。 (3) 上述两个信号源公共要求 a、频率可预置, b、在负载为600Ω时,输出幅度为3V, c、完成5位频率的数字显示 d、在信号频率:20HZ~10KHZ连续可调时,占空比不变,波形对称不失真。 【要求2】 1)正弦波和脉冲波频率可连续调整。 2)正弦波和脉冲波幅度可调整,调整范围可分为3档,(100mV~1V,1V~2V, 2V~3V), 在负载为600Ω时。(峰-峰值6V)

工程师必须懂得眼图分析方法解读

信号完整性分析基础系列之一 ——关于眼图测量(上) 汪进进美国力科公司深圳代表处 内容提要:本文将从作者习惯的无厘头漫话风格起篇,从四个方面介绍了眼图测量的相关知识:一、串行数据的背景知识; 二、眼图的基本概念; 三、眼图测量方法; 四、力科示波器在眼图测量方面的特点和优势。全分为上、下两篇。上篇包括一、二部分。下篇包括三、四部分。 您知道吗?眼图的历史可以追溯到大约47年前。在力科于2002年发明基于连续比特位的方法来测量眼图之前,1962年-2002的40年间,眼图的测量是基于采样示波器的传统方法。 您相信吗?在长期的培训和技术支持工作中,我们发现很少有工程师能完整地准确地理解眼图的测量原理。很多工程师们往往满足于各种标准权威机构提供的测量向导,Step by Step,满足于用“万能”的Sigtest软件测量出来的眼图给出的Pass or Fail结论。这种对于Sigtest的迷恋甚至使有些工程师忘记了眼图是可以作为一项重要的调试工具的。 在我2004年来力科面试前,我也从来没有听说过眼图。那天面试时,老板反复强调力科在眼图测量方面的优势,但我不知所云。之后我Google“眼图”,看到网络上有限的几篇文章,但仍不知所云。刚刚我再次Google“眼图”,仍然没有找到哪怕一篇文章讲透了眼图测量。 网络上搜到的关于眼图的文字,出现频率最多的如下,表达得似乎非常地专业,但却在拒绝我们的阅读兴趣。 “在实际数字互连系统中,完全消除码间串扰是十分困难的,而码间串扰对误码率的影响目前尚无 法找到数学上便于处理的统计规律,还不能进行准确计算。为了衡量基带传输系统的性能优劣,在实验室中,通常用示波器观察接收信号波形的方法来分析码间串扰和噪声对系统性能的影响,这就是眼图分析法。 如果将输入波形输入示波器的Y轴,并且当示波器的水平扫描周期和码元定时同步时,适 当调整相位,使波形的中心对准取样时刻,在示波器上显示的图形很象人的眼睛,因此被称为眼图(Eye Map)。 二进制信号传输时的眼图只有一只“眼睛”,当传输三元码时,会显示两只“眼睛”。眼图是 由各段码元波形叠加而成的,眼图中央的垂直线表示最佳抽样时刻,位于两峰值中间的水平线是判决门限电平。 在无码间串扰和噪声的理想情况下,波形无失真,每个码元将重叠在一起,最终在示波器 上看到的是迹线又细又清晰的“眼睛”,“眼”开启得最大。当有码间串扰时,波形失真,码元不完全重合,眼图的迹线就会不清晰,引起“眼”部分闭合。若再加上噪声的影响,则使眼图的线条变得模糊,“眼”开启得小了,因此,“眼”张开的大小表示了失真的程度,反映了码间串扰的强弱。由此可知,眼图

五款信号完整性仿真分析工具

SI五款信号完整性仿真工具介绍 (一)Ansoft公司的仿真工具 现在的高速电路设计已经达到GHz的水平,高速PCB设计要求从三维设计理论出发对过孔、封装和布线进行综合设计来解决信号完整性问题。高速PCB设计要求中国工程师必须具备电磁场的理论基础,必须懂得利用麦克斯韦尔方程来分析PCB设计过程中遇到的电磁场问题。目前,Ansoft公司的仿真工具能够从三维场求解的角度出发,对PCB设计的信号完整性问题进行动态仿真。 Ansoft的信号完整性工具采用一个仿真可解决全部设计问题: SIwave是一种创新的工具,它尤其适于解决现在高速PCB和复杂IC封装中普遍存在的电源输送和信号完整性问题。 该工具采用基于混合、全波及有限元技术的新颖方法,它允许工程师们特性化同步开关噪声、电源散射和地散射、谐振、反射以及引线条和电源/地平面之间的耦合。该工具采用一个仿真方案解决整个设计问题,缩短了设计时间。 它可分析复杂的线路设计,该设计由多重、任意形状的电源和接地层,以及任何数量的过孔和信号引线条构成。仿真结果采用先进的3D图形方式显示,它还可产生等效电路模型,使商业用户能够长期采用全波技术,而不必一定使用专有仿真器。 (二)SPECCTRAQuest Cadence的工具采用Sun的电源层分析模块: Cadence Design Systems的SpecctraQuest PCB信号完整性套件中的电源完整性模块据称能让工程师在高速PCB设计中更好地控制电源层分析和共模EMI。 该产品是由一份与Sun Microsystems公司签署的开发协议而来的,Sun最初研制该项技术是为了解决母板上的电源问题。 有了这种新模块,用户就可根据系统要求来算出电源层的目标阻抗;然后基于板上的器件考虑去耦合要求,Shah表示,向导程序能帮助用户确定其设计所要求的去耦合电容的数目和类型;选择一组去耦合电容并放置在板上之后,用户就可运行一个仿真程序,通过分析结果来发现问题所在。 SPECCTRAQuest是CADENCE公司提供的高速系统板级设计工具,通过它可以控制与PCB layout相应的限制条件。在SPECCTRAQuest菜单下集成了一下工具: (1)SigXplorer可以进行走线拓扑结构的编辑。可在工具中定义和控制延时、特性阻抗、驱动和负载的类型和数量、拓扑结构以及终端负载的类型等等。可在