版图设计考试重点

机械设计综合实验指导书与实验报告

机械设计综合实验指导书 及实验报告 班级 学号 姓名 机械基础实验中心雷代明 2017年3月 第一部分机械设计

实验一机械零件认知与分析实验 一、实验目的 1、熟悉常用的机械零件的基本结构,以便对所学理论知识产生一定的感性认识。 2、分析常用机械零件的基本构造及制造原理。 3、了解常用机械零件的实际使用情况。 二、实验内容 通过观察,掌握常用的机械零件的基本结构及应用场合。 三、实验简介 机械零件陈列观摩,共包括: (1)螺纹联接与应用 (2)键、花键、销、铆、焊、铰接 (3)带传动 (4)链传动 (5)齿轮传动 (6)蜗杆传动 (7)滑动轴承与润滑密封 (8)滚动轴承与装置设计 (9)轴的分析与设计 (10)联轴器与离合器。 共10个陈列柜,罗列了机械设计内容中大多数常用的基本零件与标准件,并对相应的零件进行了结构和基本受力分析,联接和安装的基本方法的说明,有些常用的零件还给出了简单的应用举例。 通过本实验的观摩,学生可以对照书本所学的基本内容,初步领会机械设计的一些常用零部件的基本设计与应用原理,从而达到举一反三的教学目的,对其所学的课本理论知识进一步巩固和深化。 四、实验要求 1、学生必须带上课本,以便于与书本内容进行对照观察。 2、进入实验室必须保持安静,不得大声喧哗,以免影响其他同学。 3、不得私自打开陈列柜,不得用手触摸各种机械零件模型。 4、服从实验人员的安排,认真领会机械零件的构造原理。 五、思考题 1、常用螺纹联接的方法有哪些? 2、说明无键联结的优缺点. 3、在带传动中,带张紧的方法有哪些?

4、轴上零件轴向常用的定位方法有哪些?举例说明。 第二章滑动轴承实验 实验二滑动轴承基本性能实验 一、概述 滑动轴承用于支承转动零件,是一种在机械中被广泛应用的重要零部件。根据轴承的工作原理,滑动轴承属于滑动摩擦类型。滑动轴承中的润滑油若能形成一定的油膜厚度而将作相对转动的轴承与轴颈表面分开,则运动副表面就不发生接触,从而降低摩擦、减少磨损,延长轴承的使用寿命。 根据流体润滑形成原理的不同,润滑油膜分为流体静压润滑(外部供压式)及流体动压润滑(内部自生式),本章讨论流体动压轴承实验。 流体动压润滑轴承其工作原理是通过轴颈旋转,借助流体粘性将润滑油带入轴颈与轴瓦配合表面的收敛楔形间隙内,由于润滑油由大端入口至小端出口的流动过程中必须满足流体流动连续性条件,从而润滑油在间隙内就自然形成周向油膜压力(见图2-1),在油膜压力作用下,轴颈由图2-1(a)所示的位置被推向图2-1(b)所示的位置。 当动压油膜的压力p在载荷F方向分力的合力与载荷F平衡时,轴颈中心处于某一相应稳定的平衡位置O1,O1位置的坐标为O1(e,φ)。其中e=OO1,称为偏心距;φ为偏位角(轴承中心0与轴颈中心0l连线与外载荷F作用线间的夹角)。 随着轴承载荷、转速、润滑油种类等参数的变化以及轴承几何参数(如宽径比、相对间隙)的不同,轴颈中心的位置也随之发生变化。对处于工况参数随时间变化下工作的非

PCB版图设计报告

兰州交通大学电信学院课程设计实验报告 实验名称:负反馈放大电路PCB设计 无线话筒PCB设计(选作) 试验日期: 2012年6月25日 班级: 电子科学与技术092班 姓名: 刘光智 学号: 200910112

Altium designer简介 Altium Designer 提供了唯一一款统一的应用方案,其综合电子产品一体化开发所需的所有必须技术和功能。Altium Designer 在单一设计环境中集成板级和FPGA系统设计、基于FPGA和分立处理器的嵌入式软件开发以及PCB版图设计、编辑和制造。并集成了现代设计数据管理功能,使得Altium Designer成为电子产品开发的完整解决方案-一个既满足当前,也满足未来开发需求的解决方案。 一、实验目的 1.了解并学会运用Altium designer软件绘制简单PCB 2.会运用Alitum designer软件设计库元件 3.掌握印刷电路板布线流程 4.掌握印刷电路板设计的基本原则 二、设计内容 1.要求用Alitum designer软件画出电路原理图 2.按照所画原理图自动生成PCB版图 3.会自己设计元件和库 三、实验步骤(负反馈放大器PCB设计) 1、新建工程、为工程添加项目:在D盘新建一个自己的文件夹重命名为ffk,运行Alitum designer软件,然后单击文件/新建/工程/PCB工程,然后右击所建的PCB工程选择给工程添加原理图,然后添加PCB,建完PCB工程保存工程到D/ffk内,保存时三个文件都命名为ffk.扩展名 2、画原理图:在原理图窗口画出所要画的PCB原理图,本次实验所画电路图如图1: 图1 3、对所画电路图进行编译:点击工程/Compile Document mic.SchDoc,然后点击工程/Compile PCB Project PCB_mic.PrjPCB,然后打开Messages窗口查看编译结果,若有错误按照提示对错误进行改正再编译,直至没有错误结束编译

集成电路版图基础知识练习

一、填空 1.ls (填写参数)命令用于显示隐藏文件。(-a) 2.进入当前目录的父目录的命令为 (%cd ..) 3.查看当前工作目录的命令为:(%pwd) 4.目录/home//uuu已建立,当前工作目录为/home/,采用绝对路径进入/home//uuu 的命令为:(%cd /home//uuu) 5.假设对letter文件有操作权限,命令%chmod a+rw letter会产生什么结果:(对 所有的用户增加读写权限。) 6.显示当前时间的命令为:(%date) 7.打开系统管理窗口的命令为:(%admintool) 8.与IP地址为166.111.4.80的主机建立FTP连接的命令为:(%ftp 166.111.4.80 or %ftp %open 166.111.4.80) 9.建立FTP连接后,接收单个文件的命令为:(%get) 10.建立FTP连接后,发送多个文件的命令为:(%mput) 11.有一种称为0.13um 2P5M CMOS单井工艺, 它的特征线宽为______,互连层共有 _____层,其电路类型为_______。0.13um 7 CMOS 12.请根据实际的制造过程排列如下各选项的顺序: a.生成多晶硅 b.确定井的位置和大小 c.定义扩散区,生成源漏区 d.确定有源区的位置和大小 e.确定过孔位置 正确的顺序为:___ _________________。bdace 13.集成电路中的电阻主要有__________, ____________, _____________三种。井电 阻,扩散电阻,多晶电阻 14.为方便版图绘制,通常将Contact独立做成一个单元,并以实例的方式调用。若该 Contact单元称为P型Contact,由4个层次构成,则该四个层次分别为:_________,_________, _________, ___________. active, P+ diffusion, contact, metal. 15.CMOS工艺中,之所以要将衬底或井接到电源或地上,是因为 ___________________________________。报证PN结反偏,使MOS器件能够正常工 作。 16.版图验证主要包括三方面:________,__________,__________; 完成该功能的 Cadence工具主要有(列举出两个):_________,_________。DRC, LVS, ERC, Diva, Dracula 17.造成版图不匹配的因数主要来自两个方面:一是制造工艺引起的,另一个是 __________;后者又可以进一步细分为两个方面:_______________, _____________。片上环境波动,温度波动,电压波动。 18.DRC包括几种常见的类型,如最大面积(Maximum Dimension),最小延伸(Minimum Extension),此外还有_________,_________,_________。最小间距,最小宽度,最小包围(Minimum Enclosure)。 19.减少天线效应的三种方法有:____________,____________,__________。插入二 极管,插入缓冲器,Jumper (或者,通过不同的金属层绕线)。 20.由于EDA工具的不统一,出现了各种不同的文件格式,如LEF, DEF等,业界公认 的Tape out的文件格式为 _______,它不可以通过文本编辑器查看,因为它是

D锁存器版图设计实验报告

第一章:绪论 1.1 简介 1.1.1 集成电路 集成电路版图设计是电路系统设计与集成电路工艺之间的中间环节。通过集成电路版图设计,将立体的电路系统转变为二维平面图形。利用版图制作掩模板,就可以由这些图形限定工艺加工过程,最终还原为基于半导体材料的立体结构。 以最基本的MOS器件为例,工艺生产出的器件应该包含源漏扩散区、栅极以及金属线等结构层。按照电路设计的要求,在版图中用不同图层分别表示这些结构层,画好各个图层所需的图形,图形的大小等于工艺生产得到的器件尺寸。正确摆放各图层图形之间的位置关系,绘制完成的版图基本就是工艺生产出的器件俯视图。 器件参数如MOS管的沟道尺寸,由电路设计决定,等于有源区与栅极重叠部分的尺寸。其他尺寸由生产工艺条件决定,不能随意设定。 在工艺生产中,相同结构层相连即可导电,而不同结构层之间是由氧化层隔绝的,相互没有连接关系,只有制作通孔才能在不同结构层之间导电。与工艺生产相对应的版图中默认不同图层之间的绝缘关系,因此可以不必画氧化层,却必须画各层之间的通孔。另外,衬底在版图设计过程中默认存在,不必画出。而各个N阱、P阱均由工艺生产过程中杂质掺杂形成,版图中必须画出相应图形。 1.1.2 版图设计基本知识 版图设计是创建工程制图(网表)的精确的物理描述的过程,而这一物理描述遵守由制造工艺、设计流程以及仿真显示为可行的性能要求所带来的一系列约束。版图设计得好坏,其功能正确与否,必须通过验证工具才能确定。版图的验证通常包括三大部分:设计规则检查(DRC)、电学规则检查(ERC)和版图与电路图对照(LVS)。只有通过版图验证的芯片设计才进行制版和工艺流片。 设计规则的验证是版图与具体工艺的接口, 因此就显得尤为重要, Cadence 中进行版图验证的工具主要有dracula和diva。Dracula 为独立的验证工具, 不仅可以进行设计规则验证(DRC) , 而且可以完成电学规则验证(ERC)、版图与电路验证(LV S)、寄生参数提取(L PE) 等一系列验证工作, 功能强于Diva。 1.2 软件介绍 Cadence是一个大型的EDA软件,它几乎可以完成电子设计的方方面面,包括ASIC 设计、FPGA设计和PCB板设计。Cadence在仿真、电路图设计、自动布局布线、

微机综合设计实验报告

微机接口实验报告 学院:计算机与通信工程学院专业:计算机科学与技术 班级: 学号: 姓名: 综合设计实验

带分频的AD转换 实现功能: 利用8254实现分频功能,再利用AD0809实现数模转换功能。 设计思路: 首先利用8254芯片的计时功能,将CLK0端输入的1MHz的脉冲信号分频为0.1MHz的脉冲,并且从OUT0端输出,然后将输出的脉冲信号作为AD0809数模转换单元的输入信号,从而实现8254的分频功能和AD0809的数模转换功能。 设计接线图: 实验代码: (加粗为分频部分代码,未加粗为AD转换部分代码) IO8254_MODE EQU 283H ;8254控制寄存器端口地址 IO8254_COUNT0 EQU 280H ;8254计数器0端口地址 IO0809 EQU 298H ;AD0809DE STACK1 SEGMENT STACK DW 256 DUP(?) STACK1 ENDS CODE SEGMENT ASSUME CS:CODE START: MOV DX, IO8254_MODE ;初始化8254工作方式 MOV AL,37H ;计数器0,方式3 00110111 OUT DX,AL MOV DX,IO8254_COUNT0 ;装入计数初值 MOV AX,000AH ;10D=0AH(可以自己设计分频倍数或者利用多个计数器实现更大倍数的分频) MOV AL,03H

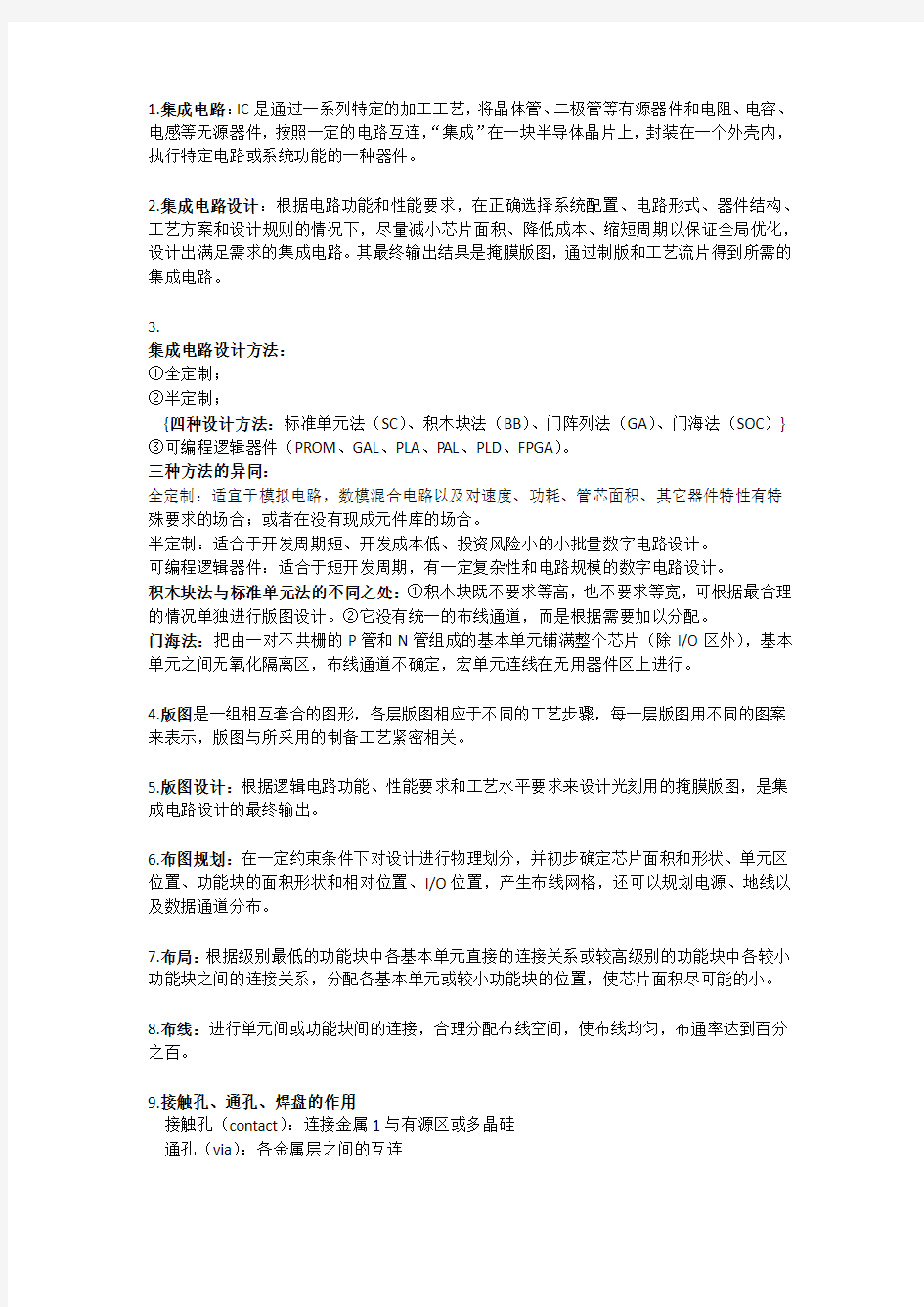

OUT DX,AL MOV AL,AH OUT DX,AL MOV DX, IO0809 ;启动A/D转换器 OUT DX, AL MOV CX, 0FFH ;延时 DELAY: LOOP DELAY IN AL, DX ;从A/D转换器输入数据 MOV BL,AL ;将AL保存到BL MOV CL, 4 SHR AL, CL ;将AL右移四位 CALL DISP ;调显示子程序显示其高四位 MOV AL, BL AND AL, 0FH CALL DISP ;调显示子程序显示其低四位 MOV AH, 02 MOV DL, 20H ;加回车符 INT 21H MOV DL, 20H INT 21H PUSH DX MOV DL, 0FFH ;判断是否有键按下 MOV AH, 06H INT 21H POP DX JE START ;若没有转START MOV AH, 4CH ;退出 INT 21H DISP PROC NEAR ;显示子程序 MOV DL, AL CMP DL, 9 ;比较DL是否>9 JLE DDD ;若不大于则为'0'-'9',加30h为其ASCII码 ADD DL, 7 ;否则为'A'-'F',再加7 DDD: ADD DL,30H ;显示 MOV AH, 02 INT 21H RET DISP ENDP CODE ENDS END START

数字集成电路设计实验报告

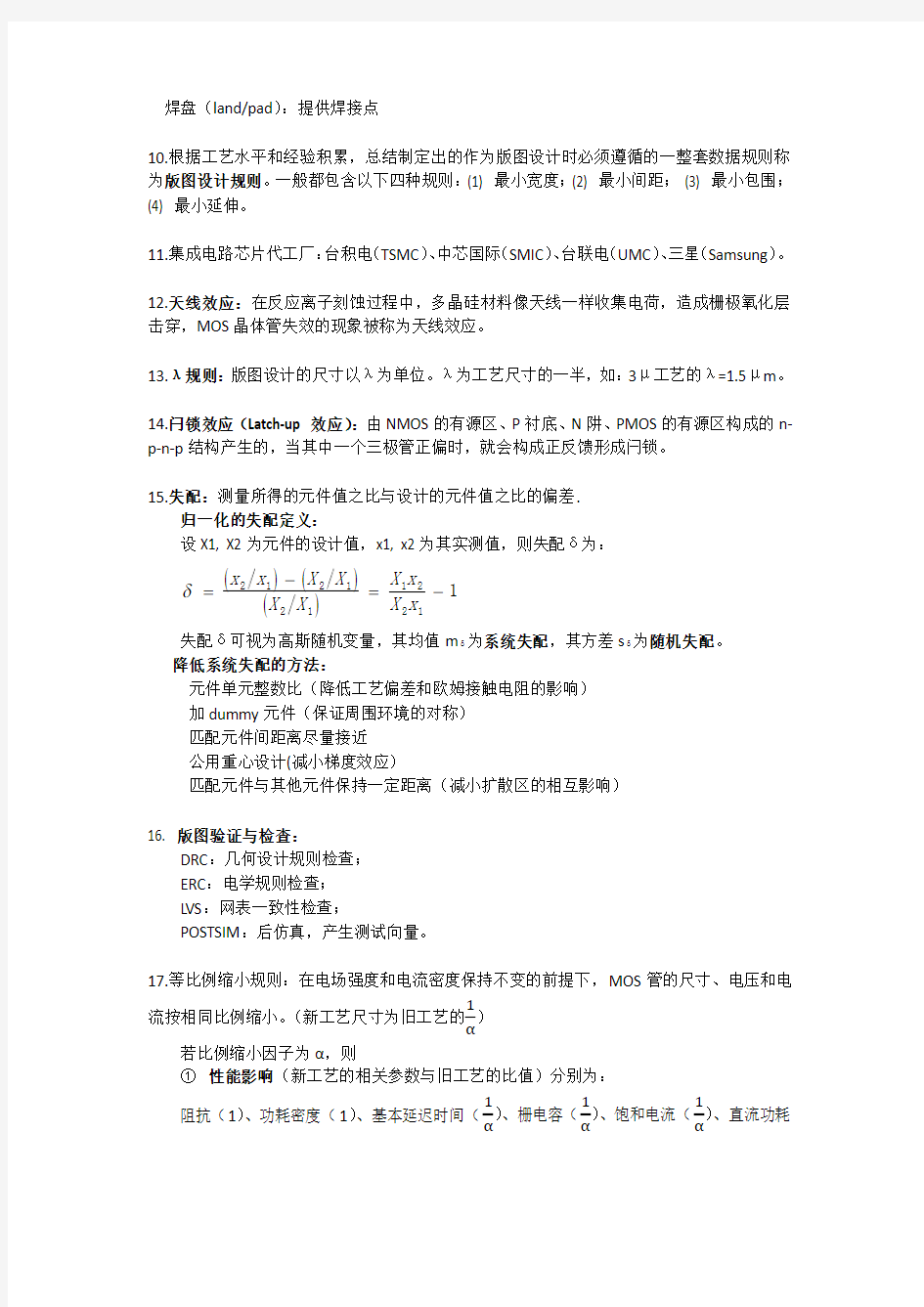

哈尔滨理工大学数字集成电路设计实验报告 学院:应用科学学院 专业班级:电科12 - 1班 学号:32 姓名:周龙 指导教师:刘倩 2015年5月20日

实验一、反相器版图设计 1.实验目的 1)、熟悉mos晶体管版图结构及绘制步骤; 2)、熟悉反相器版图结构及版图仿真; 2. 实验内容 1)绘制PMOS布局图; 2)绘制NMOS布局图; 3)绘制反相器布局图并仿真; 3. 实验步骤 1、绘制PMOS布局图: (1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层; (4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层; (7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察; 2、绘制NMOS布局图: (1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览; 3、绘制反相器布局图: (1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice 模拟; 4. 实验结果 nmos版图

集成电路版图设计论文

集成电路版图设计 班级12级微电子姓名陈仁浩学号2012221105240013 摘要:介绍了集成电路版图设计的各个环节及设计过程中需注意的问题,然后将IC版图设计与PCB版图设计进行对比,分析两者的差异。最后介绍了集成电路版图设计师这一职业,加深对该行业的认识。 关键词: 集成电路版图设计 引言: 集成电路版图设计是实现集成电路制造所必不可少的设计环节,它不仅关系到集成电路的功能是否正确,而且也会极大程度地影响集成电路的性能、成本与功耗。近年来迅速发展的计算机、通信、嵌入式或便携式设备中集成电路的高性能低功耗运行都离不开集成电路掩模版图的精心设计。一个优秀的掩模版图设计者对于开发超性能的集成电路是极其关键的。 一、集成电路版图设计的过程 集成电路设计的流程:系统设计、逻辑设计、电路设计(包括:布局布线验证)、版图设计版图后仿真(加上寄生负载后检查设计是否能够正常工作)。集成电路版图设计是集成电路从电路拓扑到电路芯片的一个重要的设计过程,它需要设计者具有电路及电子元件的工作原理与工艺制造方面的基础知识,还需要设计者熟练运用绘图软件对电路进行合理的布局规划,设计出最大程度体现高性能、低功耗、低成本、能实际可靠工作的芯片版图。集成电路版图设计包括数字电路、模拟电路、标准单元、高频电路、双极型和射频集成电路等的版图设计。具体的过程为: 1、画版图之前,应与IC 工程师建立良好沟通在画版图之前,应该向电路设计者了解PAD 摆放的顺序及位置,了解版图的最终面积是多少。在电路当中,哪些功能块之间要放在比较近的位置。哪些器件需要良好的匹配。了解该芯片的电源线和地线一共有几组,每组之间各自是如何分布在版图上的? IC 工程师要求的工作进度与自己预估的进度有哪些出入? 2、全局设计:这个布局图应该和功能框图或电路图大体一致,然后根据模块的面积大小进行调整。布局设计的另一个重要的任务是焊盘的布局。焊盘的安排要便于内部信号的连接,要尽量节省芯片面积以减少制作成本。焊盘的布局还应该便于测试,特别是晶上测试。 3、分层设计:按照电路功能划分整个电路,对每个功能块进行再划分,每一个模块对应一个单元。从最小模块开始到完成整个电路的版图设计,设计者需要建立多个单元。这一步就是自上向下的设计。 4、版图的检查: (1)Design Rules Checker 运行DRC,DRC 有识别能力,能够进行复杂的识别工作,在生成最终送交的图形之前进行检查。程序就按照规则检查文件运行,发现错误时,会在错误的地方做出标记,并且做出解释。

计算机操作系统综合设计实验报告实验一

计算机操作系统综合设计 实验一 实验名称:进程创建模拟实现 实验类型:验证型 实验环境: win7 vc++6.0 指导老师: 专业班级: 姓名: 学号: 联系电话: 实验地点:东六E507 实验日期:2017 年 10 月 10 日 实验报告日期:2017 年 10 月 10 日 实验成绩:

一、实验目的 1)理解进程创建相关理论; 2)掌握进程创建方法; 3)掌握进程相关数据结构。 二、实验内容 windows 7 Visual C++ 6.0 三、实验步骤 1、实验内容 1)输入给定代码; 2)进行功能测试并得出正确结果。 2、实验步骤 1)输入代码 A、打开 Visual C++ 6.0 ; B、新建 c++ 文件,创建basic.h 头文件,并且创建 main.cpp 2)进行功能测试并得出正确结果 A 、编译、运行main.cpp B、输入测试数据 创建10个进程;创建进程树中4层以上的数型结构 结构如图所示:。

createpc 创建进程命令。 参数: 1 pid(进程id)、 2 ppid(父进程id)、3 prio(优先级)。 示例:createpc(2,1,2) 。创建一个进程,其进程号为2,父进程号为1,优先级为2 3)输入创建进程代码及运行截图 4)显示创建的进程

3、画出createpc函数程序流程图 分析createpc函数的代码,画出如下流程图:

四、实验总结 1、实验思考 (1)进程创建的核心内容是什么? 答: 1)申请空白PCB 2)为新进程分配资源 3)初始化进程控制块 4)将新进程插入到就绪队列 (2)该设计和实际的操作系统进程创建相比,缺少了哪些步骤? 答:只是模拟的创建,并没有分配资源 2、个人总结 通过这次课程设计,加深了对操作系统的认识,了解了操作系统中进程创建的过程,对进程创建有了深入的了解,并能够用高 级语言进行模拟演示。一分耕耘,一分收获,这次的课程设计让 我受益匪浅。虽然自己所做的很少也不够完善,但毕竟也是努 力的结果。另外,使我体会最深的是:任何一门知识的掌握, 仅靠学习理论知识是远远不够的,要与实际动手操作相结合才能 达到功效。

版图设计实验报告

版图设计实验报告 课程名称:集成电路版图设计 姓名: 学号; 专业;电子科学与技术 教师;老师

目录 (一)实验目的 (3) (二)实验步骤 (4) 1,搭建环境···································································································· 2,运用ic6151··························································································· 3,作图··········································································································· 4,Run DRC·························································································· 5,画原理图··························································································· 6,Run LVS········································································································(三)实验总结·················································································································

集成电路版图设计笔试面试大全

集成电路版图设计笔试面试大全 1. calibre语句 2. 对电路是否了解。似乎这个非常关心。 3. 使用的工具。 , 熟练应用UNIX操作系统和L_edit,Calibre, Cadence, Virtuoso, Dracula 拽可乐(DIVA),等软件进行IC版图 绘制和DRC,LVS,ERC等后端验证 4. 做过哪些模块 其中主要负责的有Amplifier,Comparator,CPM,Bandgap,Accurate reference,Oscillator,Integrated Power MOS,LDO blocks 和Pad,ESD cells以及top的整体布局连接 5. 是否用过双阱工艺。 工艺流程见版图资料 在高阻衬底上同时形成较高的杂质浓度的P阱和N阱,NMOS、PMOS分别做在这两个阱中,这样可以独立调节两种沟道MOS管的参数,使CMOS电路达到最优特性,且两种器件间距离也因采用独立的阱而减小,以适合于高密度集成,但是工艺较复杂。 制作MOS管时,若采用离子注入,需要淀积Si3N4,SiO2不能阻挡离子注入,进行调沟或调节开启电压时,都可以用SiO2层进行注入。 双阱CMOS采用原始材料是在P+衬底(低电阻率)上外延一层轻掺杂的外延层P-(高电阻率)防止latch-up效应(因为低电阻率的衬底可以收集衬底电流)。 N阱、P阱之间无space。

6. 你认为如何能做好一个版图,或者做一个好版图需要注意些什么需要很仔细的回答~答:一,对于任何成功的模拟版图设计来说,都必须仔细地注意版图设计的floorplan,一般floorplan 由设计和应用工程师给出,但也应该考虑到版图工程师的布线问题,加以讨论调整。总体原则是 模拟电路应该以模拟信号对噪声的敏感度来分类。例如,低电平信号节点或高阻抗节点,它们与输入信号典型相关,因此认为它们对噪声的敏感度很高。这些敏感信号应被紧密地屏蔽保护起来,尤其是与数字输出缓冲器隔离。高摆幅的模拟电路,例如比较器和输出缓冲放大器应放置在敏感模拟电路和数字电路之间。数字电路应以速度和功能来分类。显而易见,因为数字输出缓冲器通常在高速时驱动电容负载,所以应使它离敏感模拟信号最远。其次,速度较低的逻辑电路位于敏感模拟电路和缓冲输出之间。注意到敏感模拟电路是尽可能远离数字缓冲输出,并且最不敏感的模拟电路与噪声最小的数字电路邻近。 芯片布局时具体需考虑的问题,如在进行系统整体版图布局时,要充分考虑模块之间的走线,避免时钟信号线对单元以及内部信号的干扰。模块间摆放时要配合压焊点的分布,另外对时钟布线要充分考虑时延,不同的时钟信号布线应尽量一致,以保证时钟之间的同步性问题。而信号的走线要完全对称以克服外界干扰。 二(电源线和地线的布局问题

电子电路综合设计实验报告

电子电路综合设计实验报告 实验5自动增益控制电路的设计与实现 学号: 班序号:

一. 实验名称: 自动增益控制电路的设计与实现 二.实验摘要: 在处理输入的模拟信号时,经常会遇到通信信道或传感器衰减强度大幅变化的情况; 另外,在其他应用中,也经常有多个信号频谱结构和动态围大体相似,而最大波幅却相差甚多的现象。很多时候系统会遇到不可预知的信号,导致因为非重复性事件而丢失数据。此时,可以使用带AGC(自动增益控制)的自适应前置放大器,使增益能随信号强弱而自动调整,以保持输出相对稳定。 自动增益控制电路的功能是在输入信号幅度变化较大时,能使输出信号幅度稳定不变或限制在一个很小围变化的特殊功能电路,简称为AGC 电路。本实验采用短路双极晶体管直接进行小信号控制的方法,简单有效地实现AGC功能。 关键词:自动增益控制,直流耦合互补级,可变衰减,反馈电路。 三.设计任务要求 1. 基本要求: 1)设计实现一个AGC电路,设计指标以及给定条件为: 输入信号0.5?50mVrm§ 输出信号:0.5?1.5Vrms; 信号带宽:100?5KHz; 2)设计该电路的电源电路(不要际搭建),用PROTE软件绘制完整的电路原理图(SCH及印制电路板图(PCB 2. 提高要求: 1)设计一种采用其他方式的AGC电路; 2)采用麦克风作为输入,8 Q喇叭作为输出的完整音频系统。 3. 探究要求: 1)如何设计具有更宽输入电压围的AGC电路; 2)测试AGC电路中的总谐波失真(THD及如何有效的降低THD 四.设计思路和总体结构框图 AGC电路的实现有反馈控制、前馈控制和混合控制等三种,典型的反馈控制AGC由可变增益放大器(VGA以及检波整流控制组成(如图1),该实验电路中使用了一个短路双极晶体管直接进行小信号控制的方法,从而相对简单而有效实现预通道AGC的功能。如图2,可变分压器由一个固定电阻R和一个可变电阻构成,控制信号的交流振幅。可变电阻采用基极-集电极短路方式的双极性晶体管微分电阻实现为改变Q1电阻,可从一个由电压源V REG和大阻值电阻F2组成的直流源直接向短路晶体管注入电流。为防止Rb影响电路的交流电压传输特性。R2的阻值必须远大于R1。

《超大规模集成电路设计》考试习题(含答案)完整版分析

1.集成电路的发展过程经历了哪些发展阶段?划分集成电路的标准是什么? 集成电路的发展过程: ?小规模集成电路(Small Scale IC,SSI) ?中规模集成电路(Medium Scale IC,MSI) ?大规模集成电路(Large Scale IC,LSI) ?超大规模集成电路(Very Large Scale IC,VLSI) ?特大规模集成电路(Ultra Large Scale IC,ULSI) ?巨大规模集成电路(Gigantic Scale IC,GSI) 划分集成电路规模的标准 2.超大规模集成电路有哪些优点? 1. 降低生产成本 VLSI减少了体积和重量等,可靠性成万倍提高,功耗成万倍减少. 2.提高工作速度 VLSI内部连线很短,缩短了延迟时间.加工的技术越来越精细.电路工作速度的提高,主要是依靠减少尺寸获得. 3. 降低功耗 芯片内部电路尺寸小,连线短,分布电容小,驱动电路所需的功率下降. 4. 简化逻辑电路 芯片内部电路受干扰小,电路可简化. 5.优越的可靠性 采用VLSI后,元件数目和外部的接触点都大为减少,可靠性得到很大提高。 6.体积小重量轻 7.缩短电子产品的设计和组装周期 一片VLSI组件可以代替大量的元器件,组装工作极大的节省,生产线被压缩,加快了生产速度. 3.简述双阱CMOS工艺制作CMOS反相器的工艺流程过程。 1、形成N阱 2、形成P阱 3、推阱 4、形成场隔离区 5、形成多晶硅栅 6、形成硅化物 7、形成N管源漏区 8、形成P管源漏区 9、形成接触孔10、形成第一层金属11、形成第一层金属12、形成穿通接触孔13、形成第二层金属14、合金15、形成钝化层16、测试、封装,完成集成电路的制造工艺 4.在VLSI设计中,对互连线的要求和可能的互连线材料是什么? 互连线的要求 低电阻值:产生的电压降最小;信号传输延时最小(RC时间常数最小化) 与器件之间的接触电阻低 长期可靠工作 可能的互连线材料 金属(低电阻率),多晶硅(中等电阻率),高掺杂区的硅(注入或扩散)(中等电阻率)

吉林大学无机化学研究生化学综合设计实验报告--全

化学综合和设计实验 实验报告 姓名:李玲云 学号:2014332036 专业:无机化学

扫描电子显微镜和EDS能谱演示实验 一、实验目的 1、初步了解扫描电子显微镜的工作原理、基本构造、操作及用途 2、掌握样品的制备方法 二、扫描电子显微镜的工作原理及用途 从电子枪阴极发出的直径20cm~30cm的电子束,受到阴阳极之间加速电压的作用,射向镜筒,经过聚光镜及物镜的会聚作用,缩小成直径约几毫微米的电子探针。在物镜上部的扫描线圈的作用下,电子探针在样品表面作光栅状扫描并且激发出多种电子信号。这些电子信号被相应的检测器检测,经过放大、转换,变成电压信号,最后被送到显像管的栅极上并且调制显像管的亮度。显像管中的电子束在荧光屏上也作光栅状扫描,并且这种扫描运动与样品表面的电子束的扫描运动严格同步,这样即获得衬度与所接收信号强度相对应的扫描电子像,这种图象反映了样品表面的形貌特征。第二节扫描电镜生物样品制备技术大多数生物样品都含有水分,而且比较柔软,因此,在进行扫描电镜观察前,要对样品作相应的处理。扫描电镜样品制备的主要要求是:尽可能使样品的表面结构保存好,没有变形和污染,样品干燥并且有良好导电性能。 在高压(2~20kV)的作用下,利用聚焦得到非常细的高能电子束,使其在试样上扫描(电子束与试样表层物质相互作用),激发出背散射电子、二次电子等信息,通过对上述信息的接收、放大和显示

成像,对试样表面进行分析。 根据量子力学理论,物质中存在着隧道现象,电子可以通过隧道穿过一个能级高度大于其总能量的势垒而出现在势垒的另一侧。因此,物质的表面电子可以借助隧道作用散逸出来,在物质表面附近形成电子云。在导体表面电子云中某位置的电子几率密度,会随着此位置与表面距离的增大而以指数形式迅速衰减。 扫描电子显微镜被广泛应用于材料科学、生物医学、信息产业、地质、石油化工和其它相关学科领域。是在微观尺度范围内,对样品的形貌进行观察、分析和测量的工具。现在的扫描电子显微镜,在配备相应附件后,可以获得试样表面的化学成分,晶体缺陷、电势、磁场及晶体取向等信息,是对固体物质表层进行综合分析的仪器。 吉林大学无机合成与制备化学国家重点实验室拥有场发射扫描电子显微镜。该显微镜通过接收二次电子信息来对样品表面形貌进行分析。显微镜的扫描倍数从25到650000倍,最大分辨率可达到1nm。显微镜有Oxford的能谱附件,可以进行样品的能谱测试。该显微镜不能对具有较强磁性的物质进行分析。 三、扫描电子显微镜的构造 1、电子光学系统(镜筒) 电子枪、三个电磁透镜、扫描线圈、试样室 电子枪中的灯丝产生高能电子束,电子枪的引出电压直接反映了灯丝状态的好坏(5kV~8kV不等)。每次实验都必须注意并记录电子枪引出电压。

集成电路版图设计报告

集成电路版图设计实验报告 班级:微电子1302班 学号:1306090226 姓名:李根 日期:2016年1月10日

一:实验目的: 熟悉IC设计软件Cadence Layout Editor的使用方法,掌握集成电路原理图设计,原理图仿真以及版图设计的流程方法以及技巧。 二:实验内容 1.Linux常用命令及其经典文本编辑器vi的使用 ①:了解Linux操作系统的特点。 ②:熟练操作如何登录、退出以及关机。 ③:学习Linux常用的软件以及目录命令。 ④:熟悉经典编辑器vi的基本常用操作。 2.CMOS反相器的设计和分析 ①:进行cmos反相器的原理图设计。 ②:进行cmos反相器的原理图仿真。 ③:进行cmos反相器的版图设计。 3.CMOS与非门的设计和分析 ①:进行cmos与非门的原理图设计。 ②:进行cmos与非门的原理图仿真。 ③:进行cmos与非门的版图设计 4.CMOS D触发器的设计和分析 ①:进行cmosD触发器的原理图设计。 ②:进行cmosD触发器的原理图仿真。 ③:进行cmosD触发器的版图设计。 5.对以上的学习进行总结 ①:总结收获学习到的东西。 ②:总结存在的不足之处。 ③:展望集成电路版图设计的未来。 三:实验步骤(CMOS反相器) 1.CMOS反相器原理图设计 内容:首先建立自己的Library,建立一个原理图的cell,其次进行原理图通过调用库里面的器件来绘制原理图,然后进行检错及修正,具体操作如下:在Terminal视窗下键入icfb,打开CIW; Tool→Library Manager; File→New→Library; 在name栏填上Library名称; 选择Compile a new techfile; 键入~/0.6um.tf; File→New→Cell view,在cell name键入inv,tool选择schematic,单击OK; 点击Schematic视窗上的指令集Add→Instance,出现Add Instance视窗; 通过Browse analogLib库将要用到的元件添加进来;

福州大学集成电路版图设计实验报告

福州大学物信学院 《集成电路版图设计》 实验报告 姓名:席高照 学号:111000833 系别:物理与信息工程 专业:微电子学 年级:2010 指导老师:江浩

一、实验目的 1.掌握版图设计的基本理论。 2.掌握版图设计的常用技巧。 3.掌握定制集成电路的设计方法和流程。 4.熟悉Cadence Virtuoso Layout Edit软件的应用 5.学会用Cadence软件设计版图、版图的验证以及后仿真 6.熟悉Cadence软件和版图设计流程,减少版图设计过程中出现的错误。 二、实验要求 1.根据所提供的反相器电路和CMOS放大器的电路依据版图设计的规则绘制电路的版图,同时注意CMOS查分放大器电路的对称性以及电流密度(通过该电路的电流可能会达到5mA) 2.所设计的版图要通过DRC、LVS检测 三、有关于版图设计的基础知识 首先,设计版图的基础便是电路的基本原理,以及电路的工作特性,硅加工工艺的基础、以及通用版图的设计流程,之后要根据不同的工艺对应不同的设计规则,一般来说通用的版图设计流程为①制定版图规划记住要制定可能会被遗忘的特殊要求清单②设计实现考虑特殊要求及如何布线创建组元并对其进行布局③版图验证执行基于计算机的检查和目视检查,进行校正工作④最终步骤工程核查以及版图核查版图参数提取与后仿真 完成这些之后需要特别注意的是寄生参数噪声以及布局等的影响,具体是电路而定,在下面的实验步骤中会体现到这一点。 四、实验步骤 I.反相器部分: 反相器原理图:

反相器的基本原理:CMOS反相器由PMOS和NMOS构成,当输入高电平时,NMOS导通,输出低电平,当输入低电平时,PMOS导通,输出高电平。 注意事项: (1)画成插齿形状,增大了宽长比,可以提高电路速度 (2)尽可能使版图面积最小。面积越小,速度越高,功耗越小。 (3)尽可能减少寄生电容和寄生电阻。尽可能增加接触孔的数目可以减小接触电阻。(4)尽可能减少串扰,电荷分享。做好信号隔离。 反相器的版图: 原理图电路设计: 整体版图:

集成电路版图设计电路设计微电子工艺IC芯片笔试面试题目-----超全了

如对您有帮助,请购买打赏,谢谢您! 集成电路设计基础(工艺、版图、流程、器件) 1、什么叫Latchup,如何预防闩锁效应?(仕兰、科广试题) Q1为一纵向PNP BJT, 基极(base)是nwell, 基极到集电极(collector)的增益可达数百倍;Q2是一横向的NPN BJT,基极为P substrate,到集电极的增益可达数十倍;Rwell是nwell的寄生电阻;Rsub是substrate电阻。 以上四元件构成可控硅(SCR)电路,当无外界干扰未引起触发时,两个BJT 处于截止状态,集电极电流是C-B的反向漏电流构成,电流增益非常小,此时Latch up不会产生。当其中一个BJT的集电极电流受外部干扰突然增加到一定值时,会反馈至另一个BJT,从而使两个BJT因触发而导通,VDD至GND(VSS)间形成低抗通路,Latch up由此而产生。 产生Latch up 的具体原因: ? 芯片一开始工作时VDD变化导致nwell和P substrate间寄生电容中产生足够的电流,当VDD变化率大到一定地步,将会引起Latch up。 ? 当I/O的信号变化超出VDD-GND(VSS)的范围时,有大电流在芯片中产生,也会导致SCR的触发。 ? E SD静电加压,可能会从保护电路中引入少量带电载子到well或substrate中,也会引起SCR的触发。 ? 当很多的驱动器同时动作,负载过大使power和gnd突然变化,也有可能打开SCR的一个BJT。 ? Well 侧面漏电流过大。 消除“Latch-up”效应的方法: 版图设计时: ①为减小寄生电阻Rs和Rw,版图设计时采用双阱工艺、多增加电源和地 接触孔数目,加粗电源线和地线,对接触进行合理规划布局,减小有害 的电位梯度; ②避免source和drain的正向偏压; ③使用Guard ring: P+ ring环绕nmos并接GND;N+ ring环绕pmos并接 VDD,一方面可以降低Rwell和Rsub的阻值,另一方面可阻止载流子到达BJT的基极。如果可能,可再增加两圈ring; ④Substrate contact和well contact应尽量靠近source,以降低Rwell和Rsub 的阻值; ⑤使nmos尽量靠近GND,pmos尽量靠近VDD,保持足够的距离在pmos 和nmos之间以降低引发SCR的可能; ⑥除在I/O处需采取防Latch up的措施外,凡接I/O的内部mos 也应圈 guard ring; ⑦I/O处尽量不使用pmos(nwell)。 工艺设计时: 降低寄生三极管的电流放大倍数:以N阱CMOS为例,为降低两晶体管的放大倍数,有效提高抗自锁的能力,注意扩散浓度的控制。为减小寄生PNP管的寄生电阻Rs,可在高浓度硅上外延低浓度硅作为衬底,抑制自锁效应。工艺上采用深阱扩散增加基区宽度可以有效降低寄生NPN管的放大倍数; 具体应用时:使用时尽量避免各种串扰的引入,注意输出电流不易过大。 器件外部的保护措施?低频时加限流电阻(使电源电流<30mA)?尽量减小电路中的电容值。(一般C<0.01μF)

版图设计实验报告

实验报告册 课程名称:集成电路版图设计教程姓名: 学号: 院系: 专业: 教师: 2016 年5 月15 日 实验一: OP电路搭建

一、实验目的: 1.搭建实体电路。 2.为画版图提供参考。 3.方便导入网表。 4.熟悉使用cadence。 二、实验原理和内容: 根据所用到的mn管分析各部分的使用方法,简化为几个小模块,其中有两个差分对管。合理运用匹配规则,不同的MOS管可以通过打孔O来实现相互的连接。 三、实验步骤: 1.新建设计库。在file→new→library;在name输入自己的学号;右边选择:attch to……;选择sto2→OK。然后在tools→library manager下就可看到自己建的库。 2.新建CellView。在file→new→CellView;cell栏输入OP,type →选择layout。 3.加器件。进入自己建好的电路图,选择快捷键I进行调用器件。MOS 管,在browse下查找sto2,然后调用出自己需要的器件。

4.连线。注意:若线的终点没有别的电极或者连线,则要双击左键才能终止画线。一个节点只能引出3根线。无论线的起点或是终点,光标都应进入红色电极接电。 5.加电源,和地符号。电源Vdd和地Vss的符号在analoglib库中选择和调用,然后再进行连线。 (可以通过Q键来编辑器件属性,把实验规定的MOS管的width和length数据输入,这样就可以在电路图的器件符号中显示出来) 6.检查和保存。命令是check and save。(检查主要针对电路的连接关系:连线或管脚浮空,总线与单线连接错误等)如果有错和警告,在‘schematic check’中会显示出错的原因,可以点击查看纠正。(画完后查看完整电路按快捷键F,连线一定要尽量节约空间,简化电路) 四、实验数据和结果: 导出电路网表的方法:新建文件OP,file→Export→OP(library browser 选NAND2),NAND.cdl,Analog √

集成电路基础工艺和版图设计测试试卷

集成电路基础工艺和版图设计测试试卷 (考试时间:60分钟,总分100分) 第一部分、填空题(共30分。每空2分) 1、NMOS是利用电子来传输电信号的金属半导体;PMOS是利用空穴来传输电信号的金属半导体。 2、集成电路即“IC”,俗称芯片,按功能不同可分为数字集成电路和模拟集成电路,按导电类型不同可分为 双极型集成电路和单极型集成电路,前者频率特性好,但功耗较大,而且制作工艺复杂,不利于大规模集成;后者工作速度低,但是输入阻抗高、功耗小、制作工艺简单、易于大规模集成。 3、金属(metal)—氧化物(oxid)—半导体(semiconductor)场效应晶体管即MOS管,是一个四端有源器件,其四端分别是栅 极、源极、漏极、背栅。 4、集成电路设计分为全定制设计方法和半定制设计方法,其中全定制设计方法又分为基于门阵列和标准单元 的设计方法,芯片利用率最低的是基于门阵列的设计方法。 第二部分、不定项选择题(共45分。每题3分,多选,错选不得分,少选得1分) 1、在CMOS集成电路中,以下属于常用电容类型的有(ABCD) A、MOS电容 B、双层多晶硅电容 C、金属多晶硅电容 D、金属—金属电容 2、在CMOS集成电路中,以下属于常用电阻类型的有(ABCD) A、源漏扩散电阻 B、阱扩散电阻 C、沟道电阻 D、多晶硅电阻 3、以下属于无源器件的是(CD ) A、MOS晶体管 B、BJT晶体管 C、POL Y电阻 D、MIM电容 4、与芯片成本相关的是(ABC) A、晶圆上功能完好的芯片数 B、晶圆成本 C、芯片的成品率 D、以上都不是 5、通孔的作用是(AB ) A、连接相邻的不同金属层 B、使跳线成为可能 C、连接第一层金属和有源区 D、连接第一层金属和衬底 6、IC版图的可靠性设计主要体现在(ABC)等方面,避免器件出现毁灭性失效而影响良率。 A、天线效应 B、闩锁(Latch up) C、ESD(静电泄放)保护 D、工艺角(process corner)分析 7、减小晶体管尺寸可以有效提高数字集成电路的性能,其原因是(AB) A、寄生电容减小,增加开关速度 B、门延时和功耗乘积减小 C、高阶物理效应减少 D、门翻转电流减小 8、一般在版图设计中可能要对电源线等非常宽的金属线进行宽金属开槽,主要是抑制热效应对芯片的损害。下面哪些做法符合宽金属开槽的基本规则?(ABCD) A、开槽的拐角处呈45度角,减轻大电流密度导致的压力 B、把很宽的金属线分成几个宽度小于规则最小宽度的金属线 C、开槽的放置应该总是与电流的方向一致 D、在拐角、T型结构和电源PAD区域开槽之前要分析电流流向 9、以下版图的图层中与工艺制造中出现的外延层可能直接相接触的是(AB)。 A、AA(active area) B、NW(N-Well) C、POLY D、METAL1