华侨大学微电子器件与电路实验实验报告(IC2019)实验7

微电子器件与电路实验(集成)实验报告

姓名学号实验时间2019.06 操作成绩报告成绩实验成绩

实验名称实验七集成MOSFET寄生电容参数提取

实验设备(1)计算机 (2)操作系统:Centos

(3)软件平台:Cadence Virtuoso (4)工艺模型TSMC RF0.18um

实验目的1.掌握MOSFET CV特性曲线特点

2.掌握饱和区MOSFET栅漏交叠电容CGD和沟道宽度之间的关系

3.掌握饱和区MOSFET漏区CDD电容和沟道宽度之间的关系

4. 掌握饱和区MOSFET漏区耗尽电容CJD和漏端电压之间的关系

实验要求

1. 实验前按要求阅读器件说明文档,阅读实验操作文档,熟悉实验过程及操作步骤

2. 实验过程中按实验报告要求操作、仿真、记录数据(波形)

3. 实验结果经指导老师检查、验收,经允许后方可关机,离开实验室

4、实验后按要求处理数据和波形,回答问题。实验报告打印后,于下次实验时间缴交。

实验内容:

实验7.1 NMOS电容CV特性分析

给定尺寸的NMOS,对VGS进行DC分析,分析MOS电容CV特性,并测得单位面积电容C□。

实验7.2 PMOS电容CV特性分析

给定尺寸的NMOS,对VGS进行DC分析,分析MOS电容CV特性,并测得单位面积电容C□。

实验7.3 MOS饱和区交叠电容和沟道宽度关系

给定尺寸的NMOS,对W进行DC分析,分析MOS交叠电容Cgd和W关系曲线。

实验7.4 MOS饱和区漏区电容和沟道宽度关系

给定尺寸的NMOS,对W进行DC分析,分析MOS漏区电容Cdd和W关系曲线。

实验7.5 MOS饱和区漏区耗尽电容和漏区电压关系

给定尺寸的NMOS,对VD进行DC分析,分析MOS漏区耗尽电容Cjd和VD关系曲线。

华侨大学信息科学与工程学院电子工程系

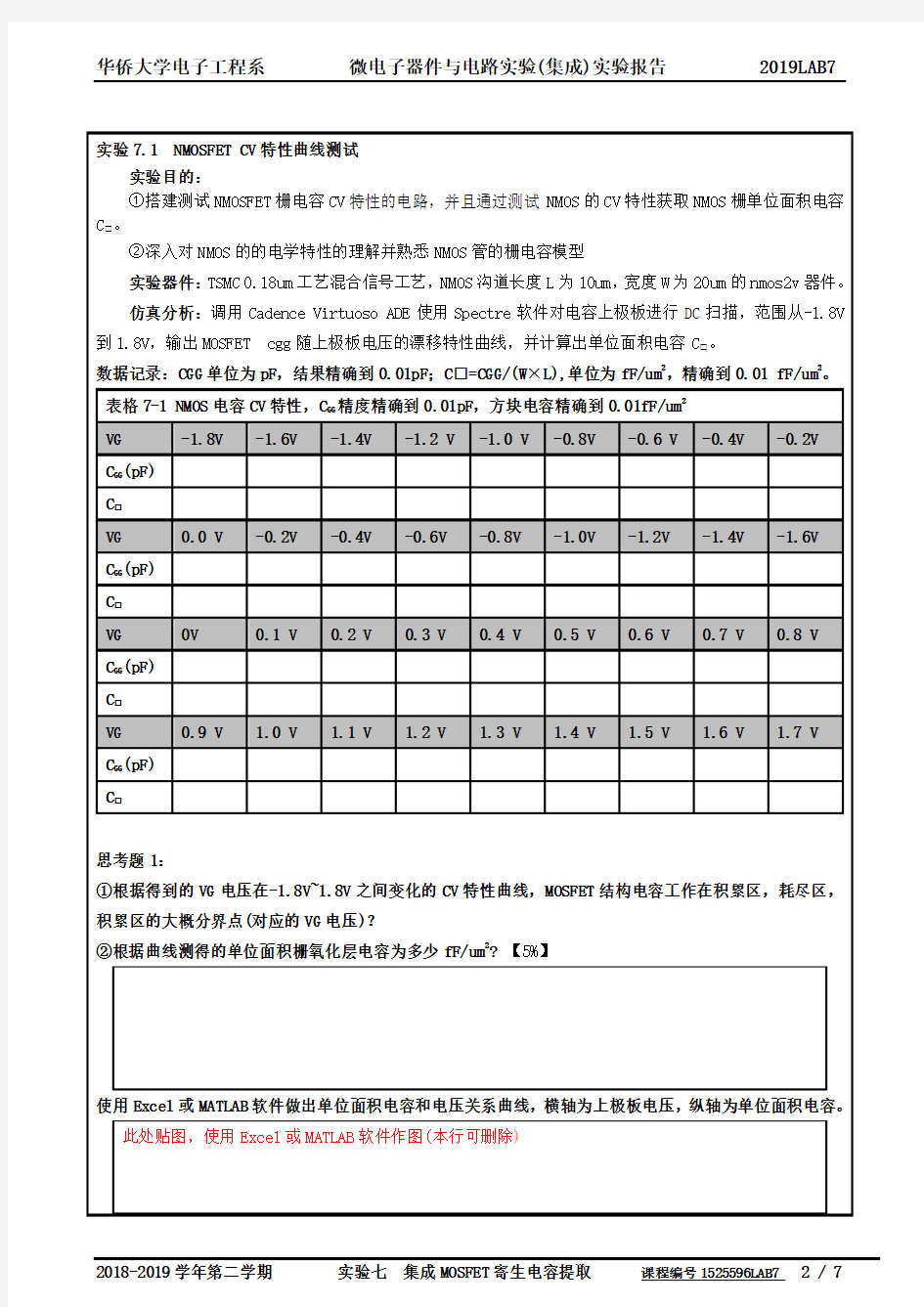

实验五--时序逻辑电路实验报告

实验五时序逻辑电路(计数器和寄存器)-实验报告 一、实验目的 1.掌握同步计数器设计方法与测试方法。 2.掌握常用中规模集成计数器的逻辑功能和使用方法。 二、实验设备 设备:THHD-2型数字电子计数实验箱、示波器、信号源 器件:74LS163、74LS00、74LS20等。 三、实验原理和实验电路 1.计数器 计数器不仅可用来计数,也可用于分频、定时和数字运算。在实际工程应用中,一般很少使用小规模的触发器组成计数器,而是直接选用中规模集成计数器。 2.(1) 四位二进制(十六进制)计数器74LS161(74LS163) 74LSl61是同步置数、异步清零的4位二进制加法计数器,其功能表见表5.1。 74LSl63是同步置数、同步清零的4位二进制加法计数器。除清零为同步外,其他功能与74LSl61相同。二者的外部引脚图也相同,如图5.1所示。 表5.1 74LSl61(74LS163)的功能表 清零预置使能时钟预置数据输入输出 工作模式R D LD EP ET CP A B C D Q A Q B Q C Q D 0 ××××()××××0 0 0 0 异步清零 1 0 ××D A D B D C D D D A D B D C D D同步置数 1 1 0 ××××××保持数据保持 1 1 ×0 ×××××保持数据保持 1 1 1 1 ××××计数加1计数3.集成计数器的应用——实现任意M进制计数器 一般情况任意M进制计数器的结构分为3类,第一类是由触发器构成的简单计数器。第二类是由集成二进制计数器构成计数器。第三类是由移位寄存器构成的移位寄存型计数器。第一类,可利用时序逻辑电路的设计方法步骤进行设计。第二类,当计数器的模M较小时用一片集成计数器即可以实现,当M较大时,可通过多片计数器级联实现。两种实现方法:反馈置数法和反馈清零法。第三类,是由移位寄存器构成的移位寄存型计数器。 4.实验电路: 十进制计数器 同步清零法 同步置数法

集成电路设计实验报告

集成电路设计 实验报告 时间:2011年12月

实验一原理图设计 一、实验目的 1.学会使用Unix操作系统 2.学会使用CADENCE的SCHEMA TIC COMPOSOR软件 二:实验内容 使用schematic软件,设计出D触发器,设置好参数。 二、实验步骤 1、在桌面上点击Xstart图标 2、在User name:一栏中填入用户名,在Host:中填入IP地址,在Password:一栏中填入 用户密码,在protocol:中选择telnet类型 3、点击菜单上的Run!,即可进入该用户unix界面 4、系统中用户名为“test9”,密码为test123456 5、在命令行中(提示符后,如:test22>)键入以下命令 icfb&↙(回车键),其中& 表示后台工作,调出Cadence软件。 出现的主窗口所示: 6、建立库(library):窗口分Library和Technology File两部分。Library部分有Name和Directory 两项,分别输入要建立的Library的名称和路径。如果只建立进行SPICE模拟的线路图,Technology部分选择Don’t need a techfile选项。如果在库中要创立掩模版或其它的物理数据(即要建立除了schematic外的一些view),则须选择Compile a new techfile(建立新的techfile)或Attach to an existing techfile(使用原有的techfile)。 7、建立单元文件(cell):在Library Name中选择存放新文件的库,在Cell Name中输 入名称,然后在Tool选项中选择Composer-Schematic工具(进行SPICE模拟),在View Name中就会自动填上相应的View Name—schematic。当然在Tool工具中还有很多别的

微电子实验报告一

实验一MOS管的基本特性 班级姓名学号指导老师袁文澹 一、实验目的 1、熟练掌握仿真工具Hspice相关语法; 2、熟练掌握MOS管基本特性; 3、掌握使用HSPICE对MOS电路进行SPICE仿真,以得到MOS电路的I-V曲线。 二、实验内容及要求 1、熟悉Hspice仿真工具; 2、使用Hspice仿真MOS的输出特性,当VGs从0~5V变化,Vds分别从1V、2V、3V、4V 和5V时的输出特性曲线; 三、实验原理 1、N沟道增强型MOS管电路图 a)当Vds=0时,Vgs=0的话不会有电流,即输出电流Id=0。 b)当Vgs是小于开启电压的一个确定值,不管Vds如何变化,输出电流Id都不会改变。 c)当Vgs是大于开启电压的一个确定值,在一定范围内增大Vds时,输出电流Id增大。但当 出现预夹断之后,再增大Vds,输出电流Id不会再变化。 2、NMOS管的输出特性曲线

四、实验方法与步骤 实验方法: 计算机平台:(在戴尔计算机平台、Windows XP操作系统。) 软件仿真平台:(在VMware和Hspice软件仿真平台上。) 实验步骤: 1、编写源代码。按照实验要求,在记事本上编写MOS管输出特性曲线的描述代码。并以aaa.sp 文件扩展名存储文件。 2、打开Hspice软件平台,点击File中的aaa.sp一个文件。 3、编译与调试。确定源代码文件为当前工程文件,点击Complier进行文件编译。编译结果有错误或警告,则将要调试修改直至文件编译成功。 4、软件仿真运行及验证。在编译成功后,点击simulate开始仿真运行。点击Edit LL单步运行查看结果,无错误后点击Avanwaves按照程序所述对比仿真结果。 5、断点设置与仿真。… 6、仿真平台各结果信息说明. 五、实验仿真结果及其分析 1、仿真过程 1)源代码 *Sample netlist for GSMC $对接下来的网表进行分析 .TEMP 25.0000 $温度仿真设定 .option abstol=1e-6 reltol=1e-6 post ingold $设定abstol,reltol的参数值 .lib 'gd018.l' TT $使用库文件 * --- Voltage Sources --- vdd VDD 0 dc=1.8 $分析电压源 vgs g 0 0 $分析栅源电压 vds d 0 dc=5 $分析漏源电压 vbs b 0 dc=0 $分析衬源电压 * --- Inverter Subcircuit --- Mnmos d g 0 b NCH W=30U L=6U $Nmos管的一些参数 * --- Transient Analysis --- .dc vds 0 5 0.1 SWEEP vgs 1 5 1 $双参数直流扫描分析 $vds从0V~5V,仿真有效点间隔取0.1 $vgs取1V、2V、3V、4V、5V

东南大学 数字电路实验 第4章_时序逻辑电路

东南大学电工电子实验中心 实验报告 课程名称:数字逻辑电路设计实践 第 4 次实验 实验名称:基本时序逻辑电路 院(系):信息科学与工程学院专业:信息工程姓名:学号: 实验室: 实验组别: 同组人员:无实验时间: 评定成绩:审阅教师:

时序逻辑电路 一、实验目的 1.掌握时序逻辑电路的一般设计过程; 2.掌握时序逻辑电路的时延分析方法,了解时序电路对时钟信号相关参数的基本要求; 3.掌握时序逻辑电路的基本调试方法; 4.熟练使用示波器和逻辑分析仪观察波形图,并会使用逻辑分析仪做状态分析。 二、实验原理 1.时序逻辑电路的特点(与组合电路的区别): ——具有记忆功能,任一时刻的输出信号不仅取决于当时的输出信号,而且还取决于电路原来的值,或者说还与以前的输入有关。 2.时序逻辑电路的基本单元——触发器(本实验中只用到D触发器) 触发器实现状态机(流水灯中用到) 3.时序电路中的时钟 1)同步和异步(一般都是同步,但实现一些任意模的计数器时要异步控制时钟端) 2)时钟产生电路(电容的充放电):在内容3中的32768Hz的方波信号需要自己通过 电路产生,就是用到此原理。 4.常用时序功能块 1)计数器(74161) a)任意进制的同步计数器:异步清零;同步置零;同步置数;级联 b)序列发生器 ——通过与组合逻辑电路配合实现(计数器不必考虑自启动) 2)移位寄存器(74194) a)计数器(一定注意能否自启动) b)序列发生器(还是要注意分析能否自启动) 三、实验内容 1.广告流水灯 a.实验要求 用触发器、组合函数器件和门电路设计一个广告流水灯,该流水等由8个LED组成,工作时始终为1暗7亮,且这一个暗灯循环右移。 ①写出设计过程,画出设计的逻辑电路图,按图搭接电路。 ②将单脉冲加到系统时钟端,静态验证实验电路。 ③将TTL连续脉冲信号加到系统时钟端,用示波器和逻辑分析仪观察并记录时钟脉冲 CLK、触发器的输出端Q2、Q1、Q0和8个LED上的波形。 b.实验数据 ①设计电路。 1)问题分析 流水灯的1暗7亮对应8个状态,故可采用3个触发器实现;而且题目要求输出8个信号控制8个灯的亮暗,故可以把3个触发器的输出加到3-8译码器的控制端,对应的8个译码器输出端信号控制8个灯的亮暗。

《集成电路设计》课程设计实验报告

《集成电路设计》课程设计实验报告 (前端设计部分) 课程设计题目:数字频率计 所在专业班级:电子科 作者姓名: 作者学号: 指导老师:

目录 (一)概述 2 2 一、设计要求2 二、设计原理 3 三、参量说明3 四、设计思路3 五、主要模块的功能如下4 六、4 七、程序运行及仿真结果4 八、有关用GW48-PK2中的数码管显示数据的几点说明5(三)方案分析 7 10 11

(一)概述 在电子技术中,频率是最基本的参数之一,并且与许多电参量的测量方案、测量结果都有十分密切的关系,因此频率的测量就显得十分重要。测量频率的方法有多种,数字频率计是其中一种。数字频率计是计算机、通讯设备、音频视频等科研生产领域不可缺少的测量仪器,是一种用十进制数字显示被测信号频率的数字测量仪器。数字频率计基本功能是测量诸如方波等其它各种单位时间内变化的物理量。在进行模拟、数字电路的设计、安装、调试过程中,由于其使用十进制数显示,测量迅速,精确度高,显示直观,经常要用到频率计。 频率计的基本原理是应用一个频率稳定度高的时基脉冲,对比测量其它信号的频率。时基脉冲的周期越长,得到的频率值就越准确。通常情况下是计算每秒内待测信号的脉冲个数,此时我们称闸门时间是1秒。闸门时间也可以大于或小于1秒,闸门的时间越长,得到的频率值就越准确,但闸门的时间越长则每测一次频率的间隔就越长,闸门时间越短,测的频率值刷新就越快,但测得的频率精度就受影响。 本文内容粗略讲述了我们小组的整个设计过程及我在这个过程中的收获。讲述了数字频率计的工作原理以及各个组成部分,记述了在整个设计过程中对各个部分的设计思路、程序编写、以及对它们的调试、对调试结果的分析。 (二)设计方案 一、设计要求: ⑴设计一个数字频率计,对方波进行频率测量。 ⑵频率测量可以采用计算每秒内待测信号的脉冲个数的方法实现。

微电子科学与工程专业本科培养计划

微电子科学与工程专业本科培养计划 Undergraduate Program for Specialty in Microelectronic Science and Engineering 一、培养目标 Ⅰ.Program Objectives 本专业培养掌握微电子科学与工程专业必需的基础知识、基本理论和基本实验技能,能够从事该领域的各种微电子材料、器件、封装、测试、集成电路设计与系统的科研、教学、科技开发、工程技术、生产管理等工作的高级专门人才。 This program trains advanced talents with basic knowledge, theory and experimental skills necessary for Microelectronic Science and Engineering. These talents can be engaged in various works in microelectronic materials, devices, packaging, testing, integrated circuit design and system as well as the scientific research, education, technique development, engineering technology, production management. 二、基本规格要求 Ⅱ.Learning Outcomes 毕业生应获得以下几个方面的知识和能力: 1、具有扎实的自然科学基础,良好的人文社会科学基础和外语能力; 2、掌握本专业领域较宽的基础理论知识,主要包括固体物理、半导体物理、微电子材料、微电子器件、集成电路设计等方面的基础理论知识;在本专业领域内具备从事科学研究的能力; 3、受到良好的工程实践训练,掌握各种微电子器件与集成电路的分析、设计与制造方法,具有独立进行微电子材料及器件性能分析、集成电路设计、微电子工艺流程的基本能力;具备一定的工程开发和组织管理能力; 4、了解本专业的最新发展动态和发展前景,了解微电子产业的发展状况。 The program requires that the learners have the knowledge and abilities listed as follows: 1. Have solid foundation in natural science, basic fine knowledge in humanities and social sciences

微电子综合实验报告

微电子综合实验报告实验题目:⒚同或门电路仿真 班级:电子科学与技术1201 姓名:XXX 学号:XXX 时间:2015.5—2015.6

一、电路图。 OUT A B (IN1) (IN2) 分别给上图中的每个管子和结点标注,如下所述: P管分别标记为:MP1、MP2、MP3;N管分别标记为:MN1、MN2、MP3;A、B端分别标记为:IN1、IN2;输出端标记为:OUT;N 管之间连接点标记为:1;连接反相器的点标记为:2;如上图所示。 其真值表如下所示:

二、电路仿真表。 *dounand MN1 1 IN1 0 0 NMOS L=0.6U W=2.4U MN2 2 IN2 1 0 NMOS L=0.6U W=2.4U MN3 OUT 2 0 0 NMOS L=0.6U W=2.4U MP1 IN2 IN1 2 VDD PMOS L=0.6U W=4.4U MP2 IN1 IN2 2 VDD PMOS L=0.6U W=4.4U MP3 OUT 2 VDD VDD PMOS L=0.6U W=4.4U VDD VDD 0 DC 5V VIN1 IN1 0 PULSE(0 5 0 0.1N 0.1N 5N 10N) VIN2 IN2 0 PULSE(0 5 0 0.1N 0.1N 10N 20N) .TRAN 1N 100N UIC .LIB './HJ.L' TT .END 下图为无负载电容,IN1=10ns,IN2=20ns时的波形图。 从图中可以发现,本来输出应该是5v,实际输出只有4.8v,可见输出有阈值损失。 原因是N管传高电平、P管传低电平时,输出半幅,所以存在阈值损失。 三、输出加负载电容。 1、C=0.2p ;IN1=10ns ;IN2=20ns 时波形如下:

数字逻辑电路实验报告

数字逻辑电路 实验报告 指导老师: 班级: 学号: 姓名: 时间: 第一次试验一、实验名称:组合逻辑电路设计

二、试验目的: 1、掌握组合逻辑电路的功能测试。 2、验证半加器和全加器的逻辑功能。 3、、学会二进制数的运算规律。 三、试验所用的器件和组件: 二输入四“与非”门组件3片,型号74LS00 四输入二“与非”门组件1片,型号74LS20 二输入四“异或”门组件1片,型号74LS86 四、实验设计方案及逻辑图: 1、设计一位全加/全减法器,如图所示: 电路做加法还是做减法是由M决定的,当M=0时做加法运算,当M=1时做减法运算。当作为全加法器时输入信号A、B和Cin分别为加数、被加数和低位来的进位,S 为和数,Co为向上的进位;当作为全减法时输入信号A、B和Cin分别为被减数,减数和低位来的借位,S为差,Co为向上位的借位。 (1)输入/输出观察表如下: (2)求逻辑函数的最简表达式 函数S的卡诺图如下:函数Co的卡诺如下: 化简后函数S的最简表达式为: Co的最简表达式为:

(3)逻辑电路图如下所示: 2、舍入与检测电路的设计: 用所给定的集成电路组件设计一个多输出逻辑电路,该电路的输入为8421码,F1为“四舍五入”输出信号,F2为奇偶检测输出信号。当电路检测到输入的代码大于或等于5是,电路的输出F1=1;其他情况F1=0。当输入代码中含1的个数为奇数时,电路的输出F2=1,其他情况F2=0。该电路的框图如图所示: (1)输入/输出观察表如下: B8 B4 B2 B1 F2 F1 0 0 0 0 0 0 0 0 0 1 1 0 0 0 1 0 1 0 0 0 1 1 0 0 0 1 0 0 1 0 0 1 0 1 0 1 0 1 1 0 0 1 0 1 1 1 1 1 1 0 0 0 1 1 1 0 0 1 0 1 1 0 1 0 0 1 1 0 1 1 1 1 1 1 0 0 0 1 1 1 0 1 1 1

cmos模拟集成电路设计实验报告

北京邮电大学 实验报告 实验题目:cmos模拟集成电路实验 姓名:何明枢 班级:2013211207 班内序号:19 学号:2013211007 指导老师:韩可 日期:2016 年 1 月16 日星期六

目录 实验一:共源级放大器性能分析 (1) 一、实验目的 (1) 二、实验内容 (1) 三、实验结果 (1) 四、实验结果分析 (3) 实验二:差分放大器设计 (4) 一、实验目的 (4) 二、实验要求 (4) 三、实验原理 (4) 四、实验结果 (5) 五、思考题 (6) 实验三:电流源负载差分放大器设计 (7) 一、实验目的 (7) 二、实验内容 (7) 三、差分放大器的设计方法 (7) 四、实验原理 (7) 五、实验结果 (9) 六、实验分析 (10) 实验五:共源共栅电流镜设计 (11) 一、实验目的 (11) 二、实验题目及要求 (11) 三、实验内容 (11) 四、实验原理 (11) 五、实验结果 (14) 六、电路工作状态分析 (15) 实验六:两级运算放大器设计 (17) 一、实验目的 (17) 二、实验要求 (17) 三、实验内容 (17) 四、实验原理 (21) 五、实验结果 (23) 六、思考题 (24) 七、实验结果分析 (24) 实验总结与体会 (26) 一、实验中遇到的的问题 (26) 二、实验体会 (26) 三、对课程的一些建议 (27)

实验一:共源级放大器性能分析 一、实验目的 1、掌握synopsys软件启动和电路原理图(schematic)设计输入方法; 2、掌握使用synopsys电路仿真软件custom designer对原理图进行电路特性仿真; 3、输入共源级放大器电路并对其进行DC、AC分析,绘制曲线; 4、深入理解共源级放大器的工作原理以及mos管参数的改变对放大器性能的影响 二、实验内容 1、启动synopsys,建立库及Cellview文件。 2、输入共源级放大器电路图。 3、设置仿真环境。 4、仿真并查看仿真结果,绘制曲线。 三、实验结果 1、实验电路图

电工电子工艺基础实验报告完整版

电工电子工艺基础实验报告完整版 电工电子工艺基础实验报告专业年级: 学号: 姓名: 指导教师: 2013 年 10 月 7 日

目录 一.手工焊点焊接方法与工艺,贴片、通孔元器件焊接工艺。 二.简述磁控声光报警器的工作原理,画出电路组成框图,实物图片。 三.简述ZX—2005型稳压源/充电器的工作原理,画出电路组成框图,实物图片;附上实习报告。四.简述流水灯工作原理,画出电路组成框图,实物图。 五.简述ZX2031FM微型贴片收音机的工作原理,画出电路组成框图,实物图。 六.简述HTDZ1208型—复合管OTL音频功率放大器的工作原理,画出电路组成框图,实物图。七.总的实训体会,收获,意见。 一.手工焊点焊接方法与工艺,贴片、通孔元器件焊接工艺。 (1)电烙铁的拿法 反握法:动作稳定,不易疲劳,适于大功率焊接。 正握法:适于中等功率电烙铁的操作。

握笔法:一般多采用握笔法,适于轻巧型的电烙铁,其 烙铁头就是直的,头端锉成一个斜面或圆锥状,适于焊 接面积较小的焊盘。 (2)焊锡的拿法 (3)焊接操作五步法 左手拿焊条,右手拿焊铁,处于随时可焊状态。 加热焊件、送入焊条、移开焊条、移开电烙铁。(4)采用正确的加热方法 让焊件上需要锡侵润的各部分均匀受热 (5)撤离电烙铁的方法 撤离电烙铁应及时,撤离时应垂直向上撤离 (6)焊点的质量要求 有可靠的机械强度、有可靠的电气连接。 (7)合格焊点的外观 焊点形状近似圆锥体,椎体表面呈直线型、表面光泽 且平滑、焊点匀称,呈拉开裙状、无裂纹针孔夹 渣。 (8)常见焊点缺陷分析 二.简述磁控声光报警器的工作原理,画出

时序逻辑电路实验报告

时序逻辑电路实验报告 一、实验目的 1. 加深理解时序逻辑电路的工作原理。 2. 掌握时序逻辑电路的设计方法。 3. 掌握时序逻辑电路的功能测试方法。 二、实验环境 1、PC机 2、Multisim软件工具 三、实验任务及要求 1、设计要求: 要求设计一个计数器完成1→3→5→7→9→0→2→4→6→8→1→…的循环计数(设初值为1),并用一个数码管显示计数值(时钟脉冲频率为约1Hz)。 2、实验内容: (1)按要求完成上述电路的功能。 (2)验证其功能是否正确。 四、实验设计说明(简述所用器件的逻辑功能,详细说明电路的设计思路和过程) 首先根据题目要求(即要完成1到9的奇数循环然后再0到8的偶数循环)画出真值表,如下图。画出真值表后,根据真值表画出各次态对应的卡诺图,如下图。然后通过化简卡诺图,得到对应的次态的状态方 程;

然后开始选择想要用于实现的该电路的器件,由于老师上课时所用的例题是用jk触发器完成的,我觉得蛮不错的,也就选择了同款的jk触发器;选好器件之后,根据状态方程列出jk触发器的驱动方程。然后根据驱动方程连接好线路图,为了连接方便,我也在纸上预先画好了连接图,以方便照着连接。接下来的工作就是在multisim上根据画好的草图连接器件了,然后再接上需要的显示电路,即可完成。

五、实验电路(画出完整的逻辑电路图和器件接线图)

六、总结调试过程所遇到的问题及解决方法,实验体会 1、设计过程中遇到过哪些问题?是如何解决的? 在设计过程中最大的问题还是忘记设计的步骤吧,因为老师是提前将实验内容已经例题讲解给我们听的,而我开始实验与上课的时间相隔了不短的时间,导致上课记下来的设计步骤忘得七七八八,不过好在是在腾讯课堂上得网课,有回放,看着回放跟着老师的思路走一遍后,问题也就迎刃而解了,后面的设计也就是将思路步骤走一遍而已,没再遇到什么困难。 2、通过此次时序逻辑电路实验,你对时序逻辑电路的设计是否有更清楚的认识?若没有,请分析原因;若有,请说明在哪些方面更加清楚。 通过这次时序逻辑电路实验,我最大的感触就是实验设计的思路与步骤一定要清晰,思路与步骤的清晰与否真的是造成实验设计是否困难的最重要的因素。清晰的话,做起实验来如同顺水推舟,毫不费力,不清晰的话则如入泥潭,寸步难行。

微电子科学与工程专业

微电子科学与工程专业 一、培养目标 本专业培养德、智、体等方面全面发展,具备微电子科学与工程专业扎实的自然科学基础、系统的专业知识和较强的实验技能与工程实践能力,能在微电子科学技术领域从事研究、开发、制造和管理等方面工作的专门人才。 二、专业特色 微电子科学与工程是在物理学、电子学、材料科学、计算机科学、集成电路设计制造学等多个学科和超净、超纯、超精细加工技术基础上发展起来的一门新兴学科。微电子技术是近半个世纪以来得到迅猛发展的一门高科技应用性学科,是21世纪电子科学技术与信息科学技术的先导和基础,是发展现代高新技术和国民经济现代化的重要基础,被誉为现代信息产业的心脏和高科技的原动力。本专业主要学习半导体器件物理、功能电子材料、固体电子器件,集成电路设计与制造技术、微机械电子系统以及计算机辅助设计制造技术等方面的基础知识和实践技能,培养出来的学生在微电子技术领域初步具有研究和开发的能力。 三、培养标准 本专业学生要求在物理学、电子技术、计算机技术和微电子学等方面掌握扎实的基础理论,掌握微电子器件及集成电路的原理、设计、制造、封装与应用技术,接受相关实验技术的良好训练,掌握文献资料检索基本方法,具有较强的实验技能与工程实践能力,在微电子科学与工程领域初步具有研究和开发的能力。 毕业生应获得以下几方面的知识和能力: 1. 具有较好的人文科学素养、创新精神和开阔的科学视野; 2. 树立终身学习理念,具有较强的在未来生活和工作中继续学习的能力; 3. 具有较扎实的自然科学基本理论基础; 4. 具备微电子材料、微电子器件、集成电路、集成系统、计算机辅助设计、封装技术和测试技术等方面的理论基础和实验技能; 5. 了解本专业领域的科技发展动态及产业发展状况,熟悉国家电子信息产业政策及国内外有关知识产权的法律法规; 6.掌握文献检索及运用现代信息技术获取相关信息的基本方法; 7.具有归纳、整理和分析实验结果以及撰写论文、报告和参与学术交流的能力。 77

集成电路综合实验报告

集成电路设计综合实验 题目:集成电路设计综合实验 班级:微电子学1201 姓名: 学号:

集成电路设计综合实验报告 一、实验目的 1、培养从版图提取电路的能力 2、学习版图设计的方法和技巧 3、复习和巩固基本的数字单元电路设计 4、学习并掌握集成电路设计流程 二、实验内容 1. 反向提取给定电路模块(如下图1所示),要求画出电路原理图,分析出其所完成的逻辑功能,并进行仿真验证;再画出该电路的版图,完成DRC验证。 图1 1.1 查阅相关资料,反向提取给定电路模块,并且将其整理、合理布局。 1.2 建立自己的library和Schematic View(电路图如下图2所示)。 图2 1.3 进行仿真验证,并分析其所完成的逻辑功能(仿真波形如下图3所示)。

图3 由仿真波形分析其功能为D锁存器。 锁存器:对脉冲电平敏感,在时钟脉冲的电平作用下改变状态。锁存器是电平触发的存储单元,数据存储的动作取决于输入时钟(或者使能)信号的电平值,当锁存器处于使能状态时,输出才会随着数据输入发生变化。简单地说,它有两个输入,分别是一个有效信号EN,一个输入数据信号DATA_IN,它有一个输出Q,它的功能就是在EN有效的时候把DATA_IN的值传给Q,也就是锁存的过程。 只有在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号。其中使能端A 加入CP信号,C为数据信号。输出控制信号为0时,锁存器的数据通过三态门进行输出。所谓锁存器,就是输出端的状态不会随输入端的状态变化而变化,仅在有锁存信号时输入的状态被保存到输出,直到下一个锁存信号到来时才改变。锁存,就是把信号暂存以维持某种电平状态。 1.4 生成Symbol测试电路如下(图4所示) 图4

实验五时序逻辑电路实验报告

实验五时序逻辑电路(计数器和寄存器)-实验报告一、实验目的 1掌握同步计数器设计方法与测试方法。 2 ?掌握常用中规模集成计数器的逻辑功能和使用方法。 二、实验设备 设备:THHD-2型数字电子计数实验箱、示波器、信号源 器件:74LS163、74LS00、74LS20 等。 三、实验原理和实验电路 1计数器 计数器不仅可用来计数,也可用于分频、定时和数字运算。在实际工程应用中,一般很少使用小规模的触发器组成计数器,而是直接选用中规模集成计数器。 2. (1)四位二进制(十六进制)计数器74LS161 (74LS163) 74LS161是同步置数、异步清零的4位二进制加法计数器,其功能表见表。 74LS163是同步置数、同步清零的4位二进制加法计数器。除清零为同步外,其他功能与74LS161相同。二者的外部引脚图也相同,如图所示。 3.集成计数器的应用一一实现任意M进制计数器

Eft CR IK rh th Ih ET 7-I1A C1M /( 制扭环计数 同步清零法器 同步置数法 般情况任意M 进制计数器的结构分为 3类,第一类是由触发器构成的简单计数器。 第 二类是 由集成二进制计数器构成计数器。第三类是由移位寄存器构成的移位寄存型计数器。 第一类,可利用时序逻辑电路的设计方法步骤进行设计。 第二类,当计数器的模 M 较小时用 一片集成计数器即可以实现,当 M 较大时,可通过多片计数器级联实现。两种实现方法:反 馈置数法和反馈清零法。第三类,是由移位寄存器构成的移位寄存型计数器。 4?实验电路: 十进制计数器 1

图74LS161 (74LS163)外部引脚图 四、实验内容及步骤 1 .集成计数器实验 (1)按电路原理图使用中规模集成计数器74LS163和与非门74LS00,连接成一个同步置数或同步清零十进制计数器,并将输出连接至数码管或发光二极管。然后使用单次脉冲作为触发输入,观察数码管或发光二极管的变化,记录得到电路计数过程和状态的转换规律。 (2)根据电路图,首先用D触发器74LS7474构成一个不能自启的六进制扭环形计数器,同样将输出连接至数码管或发光二极管。然后使用单次脉冲作为触发输入,观察数码管或发光二 极管的变化,记录得到电路计数过程和状态的转换规律。注意观察电路是否能自启,若不能自启,则将电路置位有效状态。接下来再用D触发器74LS7474构成一个能自启的六进制扭环 形计数器,重复上述操作。 2?分频实验 依据实验原理图用74LS163及74LS00组成一个具有方波输出的六分频电路。选择适当时钟输入方式及频率(CP接连续波脉冲),用双踪示波器观察并记录时钟与分频输出信号的时序波形。 五、实验结果及数据分析 1 .集成计数实验同步清零和同步置数的十进制加一计数器状态转换过程分别如下所示: 0000 : 0001 : 0010 : 0011 ; 0100 爲00*卄庇爲爲卄yh 六进制扭环形计数器的状态转换过程如下:

数字集成电路设计实验报告

哈尔滨理工大学数字集成电路设计实验报告 学院:应用科学学院 专业班级:电科12 - 1班 学号:32 姓名:周龙 指导教师:刘倩 2015年5月20日

实验一、反相器版图设计 1.实验目的 1)、熟悉mos晶体管版图结构及绘制步骤; 2)、熟悉反相器版图结构及版图仿真; 2. 实验内容 1)绘制PMOS布局图; 2)绘制NMOS布局图; 3)绘制反相器布局图并仿真; 3. 实验步骤 1、绘制PMOS布局图: (1) 绘制N Well图层;(2) 绘制Active图层; (3) 绘制P Select图层; (4) 绘制Poly图层; (5) 绘制Active Contact图层;(6) 绘制Metal1图层; (7) 设计规则检查;(8) 检查错误; (9) 修改错误; (10)截面观察; 2、绘制NMOS布局图: (1) 新增NMOS组件;(2) 编辑NMOS组件;(3) 设计导览; 3、绘制反相器布局图: (1) 取代设定;(2) 编辑组件;(3) 坐标设定;(4) 复制组件;(5) 引用nmos组件;(6) 引用pmos组件;(7) 设计规则检查;(8) 新增PMOS基板节点组件;(9) 编辑PMOS基板节点组件;(10) 新增NMOS基板接触点; (11) 编辑NMOS基板节点组件;(12) 引用Basecontactp组件;(13) 引用Basecontactn 组件;(14) 连接闸极Poly;(15) 连接汲极;(16) 绘制电源线;(17) 标出Vdd 与GND节点;(18) 连接电源与接触点;(19) 加入输入端口;(20) 加入输出端口;(21) 更改组件名称;(22) 将布局图转化成T-Spice文件;(23) T-Spice 模拟; 4. 实验结果 nmos版图

华桥大学微电子器件与电路实验实验报告IC2019实验2

实验报告)微电子器件与电路实验(集成 学号实验时间姓名 2019.04 实验成绩实验操作教师签字 实验二集成二极管电学特性分析实验名称(1)计算机 (2)操作系统:Centos 实验设备TSMC RF0.18um工艺模型软件平台:Cadence Virtuoso (4)(3)1.掌握变量扫描分析、OP分析、DC Sweep下分析器件电学模型参数 2.掌握二极管电流和结面积和结周长关系,加深对集成二极管电学特性的理解实验目的特性的测试方法 3.掌握二极管CV 掌握单边突变结二极管掺杂浓度测量方法 4.实验 要求 1. 实验前按要求阅读器件说明文档,阅读实验操作文档,熟悉实验过程及操作步骤 2. 实验过程中按实验报告要求操作、仿真、记录数据(波形) 3. 实验结果经指导老师检查、验收,经允许后方可关机,离开实验室 ,、实验后按要求处理数据和波形,回答问题。实验报告打印后,于下次实验时间缴交。3实验内容: 【20%】 2.1 集成二极管电流随结面积变化特性(变量分析)实验对给定的二极管固定二极管的L,然后对二极管结W进行变量分析,测得二极管电流和结面积之间的关系曲线,通过曲线斜率估计二极管电流和结面积是否满足线性关系,回答思考题1 【20%】分析)2.2 实验集成二极管电流随结周长变化特性(OP使用不同结周长的二极管单元并联成结面积相同的二极管器件,测得相同偏置条件下的二极管电流,通过对比不同二极管电流之间的差异,确定二极管电流和结周长的关系,回答思考题2 【30%】 CV特性测试(DC分析下器件电学模型参数分析)集成二极管实验2.3 对给定结面积的二极管进行DC分析,分析二极管结电容和反偏电压之间的关系,测得CV特性曲线。并根据《微电子器件与电路》所学知识,回答思考题3、4、5。 【30%】实验2.4 集成二极管内建电势差及掺杂浓度测量2测试不同结电压下单边突变结二极管的单位结面积电容,根据单边突变结1/C关系曲线特点计算得到二极管的掺杂浓度和内建电势差。

CMOS数字集成电路设计_八位加法器实验报告

CMOS数字集成电路设计课程设计报告 学院:****** 专业:****** 班级:****** 姓名:Wang Ke qin 指导老师:****** 学号:****** 日期:2012-5-30

目录 一、设计要求 (1) 二、设计思路 (1) 三、电路设计与验证 (2) (一)1位全加器的电路设计与验证 (2) 1)原理图设计 (2) 2)生成符号图 (2) 3)建立测试激励源 (2) 4)测试电路 (3) 5)波形仿真 (4) (二)4位全加器的电路设计与验证 (4) 1)原理图设计 (4) 2)生成符号图 (5) 3)建立测试激励源 (5) 4)测试电路 (6) 5)波形仿真 (6) (三)8位全加器的电路设计与验证 (7) 1)原理图设计 (7) 2)生成符号图 (7) 3)测试激励源 (8) 4)测试电路 (8) 5)波形仿真 (9) 6)电路参数 (11) 四、版图设计与验证 (13) (一)1位全加器的版图设计与验证 (13) 1)1位全加器的版图设计 (13) 2)1位全加器的DRC规则验证 (14) 3)1位全加器的LVS验证 (14) 4)错误及解决办法 (14) (二)4位全加器的版图设计与验证 (15) 1)4位全加器的版图设计 (15) 2)4位全加器的DRC规则验证 (16) 3)4位全加器的LVS验证 (16) 4)错误及解决办法 (16) (三)8位全加器的版图设计与验证 (17) 1)8位全加器的版图设计 (17) 2)8位全加器的DRC规则验证 (17) 3)8位全加器的LVS验证 (18) 4)错误及解决办法 (18) 五、设计总结 (18)

EDA实验报告

电子科技大学成都学院 实验报告册 课程名称:EDA实验与实践 姓名:魏亮 学号:2940710618 院系:微电子技术系 专业:集成电路设计与集成系统(嵌入式) 教师:李海 2011 年12 月12 日

实验一:计数器 一、实验目的: 学习计数器的设计,仿真和硬件测试; 进一步熟悉Verilog HDL的编程方法。 二、实验原理和内容: 本实验的原理是利用复位信号rst,时钟信号clk,输出cout ,实现由0自加到学号(即18)。 本实验的内容是利用Quartus Ⅱ建立一个自加至18的计数器,并进行仿真测试。 三、实验步骤: 1. 启动Quartus Ⅱ建立一个空白工程,然后命名为count . qpf 。 2. 新建Verilog HDL源程序文件count.v,输入程序代码并保存, 然后进行综合编译,若在编译过程中发现错误,则找出并更正错误, 直到编译成功为止。 3. 建立波形仿真文件并进行仿真验证。 四、实验数据和结果: module count (clk,rst,cout); input clk,rst; output[5:0] cout; reg[5:0] cout; always @ (posedge clk) begin if(rst) begin cout=cout+1; if(cout==5'b10011) cout=0; end end endmodule

五、实验总结: 进一步熟悉仿真测试和Verilog HDL 编程方法。

实验二:流水灯 一、实验目的: 通过次试验进一步了解、熟悉和掌握CPLD/FPGA开发软件的使用方法及Verilog HDL的编程方法;学习简单的时序电路的设计和硬件 测试。 二、实验原理和内容: 本实验的内容是建立可用于控制LED流水灯的简单硬件电路,要求在实验箱上时间LED1~LED8发光二极管流水灯显示。 原理:在LED1~LED8引脚上周期性的输出流水数据,如原来输出的数据是11111100则表示点亮LED1、LED2。流水一次后,输出数据应 该为11111000,而此时则应点亮LED1~LED3三个LED发光二极管,这 样就可以实现LED流水灯,为了方便观察,在源程序中加入了一个分频 程序来控制流水速率。 三、实验步骤: (1)启动QuartusII建立空白工程,然后命名为led.qpf。 (2)新建Verilog HDL源程序文件led.v,输入程序代码并保存(源程序参考实验内容),进行综合编译,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。 (3)FPGA引脚分配,在Quartus II主界面下,选择Assignments→Pins,按照实验课本附录进行相应的引脚分配,引脚分配好以后保存。 (4)对该工程文件进行最后的编译,若在编译过程中发现错误,则找出并更正错误,直至编译成功为止。 (5)打开试验箱的电源开关,执行下载命令,把程序下载到FPGA试验箱中,观察流水灯的变化。 四、实验数据和结果: module led(led,clk); input clk; output[7:0] led; reg[7:0] led_r; reg[31:0] count; assign led=led_r[7:0]; always @ (posedge clk) begin count<=count+1';

福州大学集成电路版图设计实验报告

福州大学物信学院 《集成电路版图设计》 实验报告 姓名:席高照 学号:111000833 系别:物理与信息工程 专业:微电子学 年级:2010 指导老师:江浩

一、实验目的 1.掌握版图设计的基本理论。 2.掌握版图设计的常用技巧。 3.掌握定制集成电路的设计方法和流程。 4.熟悉Cadence Virtuoso Layout Edit软件的应用 5.学会用Cadence软件设计版图、版图的验证以及后仿真 6.熟悉Cadence软件和版图设计流程,减少版图设计过程中出现的错误。 二、实验要求 1.根据所提供的反相器电路和CMOS放大器的电路依据版图设计的规则绘制电路的版图,同时注意CMOS查分放大器电路的对称性以及电流密度(通过该电路的电流可能会达到5mA) 2.所设计的版图要通过DRC、LVS检测 三、有关于版图设计的基础知识 首先,设计版图的基础便是电路的基本原理,以及电路的工作特性,硅加工工艺的基础、以及通用版图的设计流程,之后要根据不同的工艺对应不同的设计规则,一般来说通用的版图设计流程为①制定版图规划记住要制定可能会被遗忘的特殊要求清单②设计实现考虑特殊要求及如何布线创建组元并对其进行布局③版图验证执行基于计算机的检查和目视检查,进行校正工作④最终步骤工程核查以及版图核查版图参数提取与后仿真 完成这些之后需要特别注意的是寄生参数噪声以及布局等的影响,具体是电路而定,在下面的实验步骤中会体现到这一点。 四、实验步骤 I.反相器部分: 反相器原理图:

反相器的基本原理:CMOS反相器由PMOS和NMOS构成,当输入高电平时,NMOS导通,输出低电平,当输入低电平时,PMOS导通,输出高电平。 注意事项: (1)画成插齿形状,增大了宽长比,可以提高电路速度 (2)尽可能使版图面积最小。面积越小,速度越高,功耗越小。 (3)尽可能减少寄生电容和寄生电阻。尽可能增加接触孔的数目可以减小接触电阻。(4)尽可能减少串扰,电荷分享。做好信号隔离。 反相器的版图: 原理图电路设计: 整体版图:

微电子行业前景与就业形势

微电子行业前景与就业形势 当前,我们正在经历新的技术革命时期,虽然它包含了新材料、新能源、生物工程、海洋工程、航空航天技术和电子信息技术等等,但是影响最大,渗透性最强,最具有新技术革命代表性的乃是以微电子技术为核心的电子信息技术。 自然界和人类社会的一切活动都在产生信息,信息是客观事物状态和运动特征的一种普通形式,它是为了维持人类的社会、经济活动所需的第三种资源(材料、能源和信息)。社会信息化的基础结构,是使社会的各个部分通过计算机网络系统,连结成为一个整体。在这个信息系统中由通讯卫星和高速大容量光纤通讯将各个信息交换站联结,快速、多路地传输各种信息。在各信息交换站中,有多个信息处理中心,例如图形图像处理中心、文字处理中心等等;有若干信息系统,例如企事业单位信息系统,工厂和办公室自动化系统,军队连队信息系统等等;在处理中心或信息系统中还包含有许多终端,这些终端直接与办公室、车间、连队的班排、家庭和个人相连系。像人的神经系统运行于人体一样,信息网络系统把社会各个部分连结在信息网中,从而使社会信息化。海湾战争中,以美国为首的多国部队的通讯和指挥系统基本上也是这样一个网络结构,它的终端是直接武装到班的膝上(legtop)计算机,今后将发展到个人携带的PDA(Person-al Date Assistant)。 实现社会信息化的关键部件是各种计算机和通讯机,但是它的基础都是微电子。当1946年2月在美国莫尔学院研制成功第一台名为电子数值积分器和计算器(Electronic Numlerical Inte-grator and Computer)即ENIAC问世的时候,是一个庞然大物,由18000个电子管组成,占地150平方米,重30吨,耗电140KW,足以发动一辆机车,然而不仅运行速度只有每秒5000次,存储容量只有千位,而且平均稳定运行时间才7分钟。试设想一下,这样的计算机能够进入办公室、企业车间和连队吗所以当时曾有人认为,全世界只要有4台ENIAC就够了。可是现在全世界计算机不包括微机在内就有几百万台。造成这个巨大变革的技术基础是微电子技术,只有在1948年Bell实验室的科学家们发明了晶体管(这可以认为是微电子技术发展史上的第一个里程碑),特别是1959年硅平面工艺的发展和集成电路的发明(这可以认为是微电子技术第二个里程碑),才出现了今天这样的以集成电路技术为基础的电子信息技术和产业。而1971年微机的问世(这可以认为是微电子技术第三个里程碑),使全世界微机现在的拥有率达到%,在美国每年由计算机完成的工作量超过4000亿人年的手工工作量。美国欧特泰克公司总裁认为:微处理器、宽频道连接和智能软件将是下世纪改变人类社会和经济的三大技术创新。 当前,微电子技术发展已进入“System on Chip”的时代,不仅可以将一个电子子系统或整个电子系统“集成”在一个硅芯片上,完成信息加工与处理的功能,而且随着微电子技术的成熟与延拓,可以将各种物理的、化学的敏感器(执行信息获取的功能)和执行器与信息处理系统“集成”在一起,从而完成信息获取、处理与执行的系统功能,一般称这种系统为微机电系统(MEMS:Micro Electronics Machinery System),可以认为这是微电子技术又一次革命性变革。集成化芯片不仅具有“系统”功能,并且可以以低成本、高效率的大批量生产,可靠性好,耗能少,从而使电子信息技术广泛地应用于国民经济、国防建设乃至家庭生活的各个方面。在日本每个家庭平均约有100个芯片,它已如同细胞组成人体一样,成为现代工农业、国防装备和家庭耐用消费品的细胞。集成电路产业产值以年增长率≥13%,在技术上,集成度年增长率46%的速率持续发展,世界上还没有一个产业能以这样高的速度持续地增长。1990年日本以微电子为基础的电子工业产值已超过号称为第一产业的汽车工业而成为第一大产业。2000年电子信息产业,将成为世界第一产业。集成电路的原料主