配置Xilinx FPGA芯片步骤图解

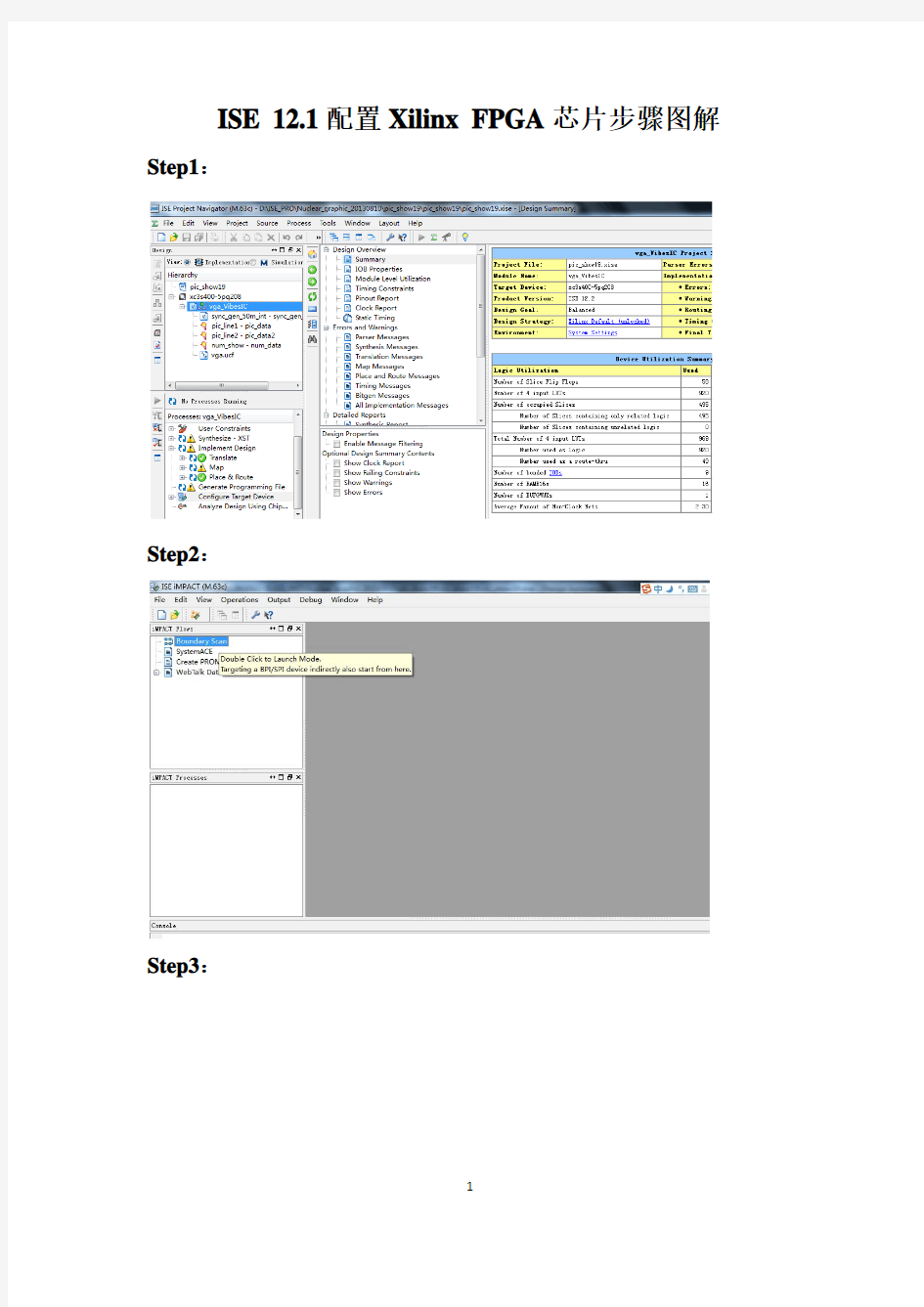

ISE 12.1配置Xilinx FPGA芯片步骤图解Step1:

Step2:

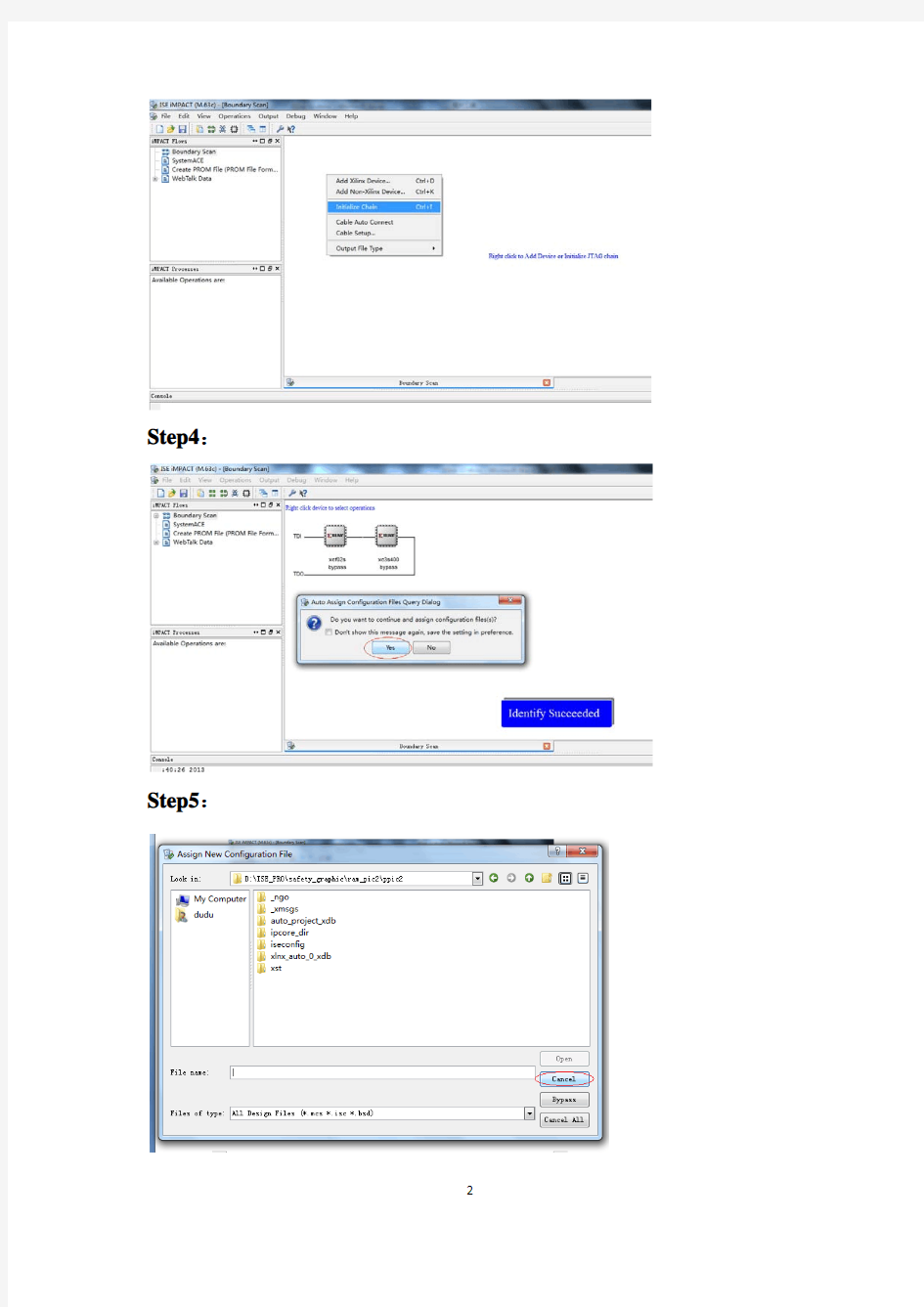

Step3:

Step4:

Step5:

Step6:

Step7:

Step8:

Step1:

Step2:

Step3:

Step4:

Step5:

Step6:

Step7:

Step8:

Step9:

Step10:

Step11:

Step12:

Step13:

Step14:

Step15:

FPGA芯片比较20100511

FPGA芯片选型比较 Cyclone III的EP3CE10采用了60nm制造工艺,是一款功耗很低、成本很低且高性能的FPGA。 Cyclone IV的 EP4CE10也采用了60nm制造工艺,是一款新的产品。该器件实现了低成本、高性能和低功耗,在手持式软件无线电等低功耗应用中,其功耗比以前的Cyclone产品低25%。 同样,Spartan-3E FPGA系列的XC3S500E芯片采用了90nm制造工艺技术生产。其单位逻辑单元的成本是FPGA行业中相当低的。它的低成本也是非常的吸引人。 现将三种产品的相关参数比较如下: 以下是Cyclone 的FAE对Cyclone IV 与Spartan 6 的比较表格,因为Spartan 6比Spartan 3高一个级别,所以这个比较有一定的参考性。 FAE也总结了Cyclone系列在技术上的的优势

1,CycloneIV/III的最高频率高于Spatarn3、Spartn6系列, 性能明显要好,(可以在QuartusII和ISE中验证比较同一程序) 2,CycloneIV/III的功耗略低于Spatarn3、Spartn6,当然,差距不是特别大 3,开发软件方面,QuartusII的编译时间明显比ISE短,界面上更加方便使用 4, CycloneIV/III市场占有率一直高于Spatarn3、Spartn6 5, Altera的CycloneIV和Xilinx的Spartan6都是新器件,很多客户都关心供货情况。由于CycloneIV和CylconeIII可以做到兼容(只有3个管脚不同,在设计时略加处理,就可以做到兼容设计),如果CycloneIV供货有问题,可以用CylconeIII直接替代,而Xilinx Spartan6很多器件还没量产,也没有兼容型号,一旦出现供货问题,很难处理。 当然这些很多是Altera单方面的解释,他这款CycloneIV的供货问题也是存在的。具体要等两天xilinx他们的工业级芯片报价出来再做价格比较,因为从整个FPGA市场占有率来说xilinx肯定有他们拥有很大市场占有率的道理。

cc2590 芯片手册

FEATURES APPLICATIONS DESCRIPTION CC2590BLOCK DIAGRAM RF_P RXTX RF_N PAEN EN CC2590 https://www.360docs.net/doc/e11988459.html,........................................................................................................................................................................................SWRS080–SEPTEMBER2008 2.4-GHz RF Front End,14-dBm output power ?All2.4-GHz ISM Band Systems ?Seamless Interface to2.4-GHz Low Power RF Devices from Texas Instruments?Wireless Sensor Networks ?Wireless Industrial Systems ?Up to+14-dBm(25mW)Output Power ?IEEE802.15.4and ZigBee Systems ?6-dB Typical Improved Sensitivity on CC24xx ?Wireless Consumer Systems and CC2500,CC2510,and CC2511 ?Wireless Audio Systems ?Few External Components –Integrated Switches –Integrated Matching Network CC2590is a cost-effective and high performance RF –Integrated Balun Front End for low-power and low-voltage 2.4-GHz –Integrated Inductors wireless applications. –Integrated PA CC2590is a range extender for all existing and future –Integrated LNA 2.4-GHz low-power RF transceivers,transmitters and ?Digital Control of LNA Gain by HGM Pin System-on-Chip products from Texas Instruments.?100-nA in Power Down(EN=PAEN=0)CC2590increases the link budget by providing a power amplifier for increased output power,and an ?Low Transmit Current Consumption LNA with low noise figure for improved receiver –22-mA at3-V for+12-dBm,PAE=23% sensitivity. ?Low Receive Current Consumption CC2590provides a small size,high output power RF – 3.4-mA for High Gain Mode design with its4x4-mm QFN-16package. – 1.8-mA for Low Gain Mode CC2590contains PA,LNA,switches,RF-matching,? 4.6-dB LNA Noise Figure,including T/R Switch and balun for simple design of high performance and external antenna match wireless applications. ?RoHS Compliant4×4-mm QFN-16Package ? 2.0-V to3.6-V Operation Please be aware that an important notice concerning availability,standard warranty,and use in critical applications of Texas Instruments semiconductor products and disclaimers thereto appears at the end of this data sheet.

FPGA配置芯片的网上汇总较杂需自己总结修订稿

F P G A配置芯片的网上汇总较杂需自己总结公司标准化编码 [QQX96QT-XQQB89Q8-NQQJ6Q8-MQM9N]

FPGA配置芯片 FPGA器件有三类配置下载方式:主动配置方式(AS)和被动配置方式(PS)和最常用的(JTAG)配置方式。 AS由FPGA器件引导配置操作过程,它控制着外部存储器和初始化过程,EPCS系列.如EPCS1,EPCS4配置器件专供AS模式,目前只支持Cyclone系列。使用Altera串行配置器件来完成。Cyclone期间处于主动地位,配置期间处于从属地位。配置数据通过DATA0引脚送入 FPGA。配置数据被同步在DCLK输入上,1个时钟周期传送1位数据。(见附图) PS则由外部计算机或控制器控制配置过程。通过加强型配置器件(EPC16,EPC8,EPC4)等配置器件来完成,在PS配置期间,配置数据从外部储存部件,通过DATA0引脚送入FPGA。配置数据在DCLK上升沿锁存,1个时钟周期传送1位数据。(见附图) JTAG接口是一个业界标准,主要用于芯片测试等功能,使用IEEE Std 联合边界扫描接口引脚,支持JAM STAPL标准,可以使用Altera下载电缆或主控器来完成。 FPGA在正常工作时,它的配置数据存储在SRAM中,加电时须重新下载。在实验系统中,通常用计算机或控制器进行调试,因此可以使用PS。在实用系统中,多数情况下必须由FPGA主动引导配置操作过程,这时FPGA将主动从外围专用存储芯片中获得配置数据,而此芯片中fpga配置信息是用普通编程器将设计所得的pof格式的文件烧录进去。 专用配置器件:epc型号的存储器? 常用配置器件:epc2,epc1,epc4,epc8,epc1441(现在好象已经被逐步淘汰了)等? 对于cyclone cycloneII系列器件,ALTERA还提供了针对AS方式的配置器件,EPCS系列.如EPCS1,EPCS4配置器件也是串行配置的.注意,他们只适用于cyclone系列. 除了AS和PS等单BIT配置外,现在的一些器件已经支持PPS,FPS等一些并行配置方式,提升配置了配置速度。当然所外挂的电路也和PS有一些区别。还有处理器配置比如JRUNNER 等等,如果需要再baidu 吧,至少不下十种。比如Altera公司的配置方式主要有Passive Serial(PS),Active Serial(AS),Fast Passive Parallel(FPP),Passive Parallel Synchronous(PPS),Passive Parallel Asynchronous(PPA),Passive Serial Asynchronous(PSA),JTAG等七种配置方式,其中Cyclone支持的配置方式有PS,AS,JTAG三种. 对FPGA芯片的配置中,可以采用AS模式的方法,如果采用EPCS的芯片,通过一条下载线进行烧写的话,那么开始的"nCONFIG,nSTATUS"应该上拉,要是考虑多种配置模式,可以采用跳线设计。让配置方式在跳线中切换,上拉电阻的阻值可以采用10K 在PS模式下tip:如果你用电缆线配置板上的FPGA芯片,而这个FPGA芯片已经有配置芯片在板上,那你就必须隔离缆线与配置芯片的信号.(祥见下图).一般平时调试时不会把配置芯片焊上的,这时候用缆线下载程序.只有在调试完成以后,才把程序烧在配置芯片中, 然后将芯片焊上.或者配置芯片就是可以方便取下焊上的那种.这样出了问题还可以方便地调试. 在AS模式下tip: 用过一块板子用的AS下载,配置芯片一直是焊在板子上的,原来AS方式在用线缆对配置芯片进行下载的时候,会自动禁止对FPGA的配置,而PS方式需要电路上隔离。 一般是用jtag配置epc2和flex10k,然后 epc2用ps方式配置flex10k.这样用比较好.(这是我在网上看到的,可以这样用吗怀疑中)望达人告知.

芯片手册

74系列 74ls48 BCD—7段译码器-内部上拉输出驱动 1 7473 TTL 带清除负触发双J-K触发器 1 7474 TTL 带置位复位正触发双D触发器 2 7476 TTL 带预置清除双J-K触发器 2 7483 TTL 四位二进制快速进位全加器 3 7485 TTL 四位数字比较器 4 7486 TTL 2输入端四异或门 5 7490 TTL 可二-五分频十进制计数器 5 7495 TTL 四位并行输入-输出移位寄存器7 74107 TTL 带清除主从双J-K触发器8 74109 TTL 带预置清除正触发双J-K触发器8 74122 TTL 可再触发单稳态多谐振荡器9 74126 TTL 三态输出低有效四总线缓冲门9 74138 TTL 3-8线译码器-复工器10 74139 TTL 双2-4线译码器-复工器11 74150 TTL 16选1数据选择-多路开关12 74154 TTL 4线—16线译码器13 74157 TTL 同相输出四2选1数据选择器14 74160 TTL 可预置BCD异步清除计数器15 74165 TTL 八位并行入-串行输出移位寄存器16 74166 TTL 八位并入-串出移位寄存器16 74169 TTL 二进制四位加-减同步计数器17 74173 TTL 三态输出四位D型寄存器18 74174 TTL 带公共时钟和复位六D触发器18 74175 TTL 带公共时钟和复位四D触发器19 74180 TTL 9位奇数-偶数发生器-校验器20 74185 TTL 二进制—BCD代码转换器21 74192 TTL 可预置BCD双时钟可逆计数器22 74194 TTL 四位双向通用移位寄存器22 74197 TTL 二进制可预置锁存器-计数器23 74245 TTL 八同相三态总线收发器23 74247 TTL BCD—7段15V输出译码-驱动器23 74248 TTL BCD—7段译码-升压输出驱动器24 74273 TTL 带公共时钟复位八D触发器24 74299 TTL 三态输出八位通用移位寄存器25 74323 TTL 三态输出八位双向移位-存贮寄存器25 CD系列 4008 CMOS 4位二进制并行进位全加器26 4013 CMOS 带置位-复位的双D触发器28 4014 CMOS 8级同步并入串入-串出移位寄存器29

三大FPGA芯片公司的主要产品系列和特点

Altera、Xilinx、Actel Altera作为世界老牌可编程逻辑器件的厂家,是可编程逻辑器件的发明者,开发软件 MAX+PLUSII和QuartusII。Altera 的主流FPGA分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Cyclone,CycloneII;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Startix,StratixII等,用户可以根据自己实际应用要求进行选择。在性能可以满足的情况下,优先选择低成本器件。 * Cyclone(飓风):Altera中等规模FPGA,2003年推出,0.13um工艺,1.5v内核供电,与Stratix结构类似,是一种低成本FPGA系列,是目前主流产品,其配置芯片也改 用全新的产品。 简评:Altera最成功的器件之一,性价比不错,是一种适合中低端应用的通用FPGA,推荐使用。 * CycloneII:Cyclone的下一代产品,2005年开始推出,90nm工艺,1.2v内核供电,属于低成本FPGA,性能和Cyclone相当,提供了硬件乘法器单元 简评:刚刚推出的新一代低成本FPGA,目前市场零售还不容易买到,估计从2005年年底开始,将逐步取代Cyclone器件,成为Altera在中低FPGA市场中的主力产品。 * Stratix :altera大规模高端FPGA,2002年中期推出,0.13um工艺,1.5v内核供电。集成硬件乘加器,芯片内部结构比Altera以前的产品有很大变化。 简评:Startix芯片在2002年的推出,改变了Altera在FPGA市场上的被动局面。该 芯片适合高端应用。随着2005年新一代StratixII器件的推出,将被StratixII逐渐取代。 * StratixII: Stratix的下一代产品,2004年中期推出,90nm工艺,1.2v内核供电,大 容量高性能FPGA。 简评:性能超越Stratix,是未来几年中,Altera在高端FPGA市场中的主力产品。 *StrtratixV为altera目前的高端产品,采用28-nm工艺,提供了28G的收发器件,适合高端的FPGA产品开发 Xilinx是FPGA的发明者,拥有世界一半以上的市场,提供90%的高端65nmFPGA产品,开发软件为ISE。Xilinx的主流FPGA分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Spartan系列;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Virtex系列,用户可以根据自己实际应用要求进行选择。在性能可以满足的情况下,优先选择低成本器件。 * Spartan-3/3L: 新一代FPGA产品,结构与VirtexII类似,全球第一款90nm工艺FPGA,1.2v内核,于2003年开始陆续推出。 简评:成本低廉,总体性能指标不是很优秀,适合低成本应用场合,是Xilinx未来几年在低端FPGA市场上的主要产品,目前市场上中低容量型号很容易购买到,大容量相对少 一些。 * Spartan-3E:基于Spartan-3/3L,对性能和成本进一步优化 * Spartan-6:xilinx最新推出的低成本FPGA

74HC595中文芯片手册

74HC595 8位移位寄存器与输出锁存器 功能描述 这种高速移位寄存器采用先进的硅栅CMOS技术。该装置具有高的抗干扰性和标准CMOS集成电路的低功率消耗,以及用于驱动15个LS-TTL负载的能力。 此装置包含馈送一个8位D型存储寄存器的8位串行入,并行出移位寄存器。存储寄存器具有8 TRI-STATE e输出。提供了用于两个移位寄存器和存储寄存器独立的时钟。 移位寄存器有直接首要明确,串行输入和串行输出(标准)引脚级联。两个移位寄存器和存储寄存器的使用正边沿触发的时钟。如果两个时钟被连接在一起时,移位寄存器的状态 将总是提前存储寄存器的一个时钟脉冲。 该54HC/74HC逻辑系列就是速度,功能和引脚输出与标准54LS/74LS逻辑系列兼容。所有输入免受损害,由于静电放电由内部二极管钳位到VCC和地面。 产品特点 1低静态电流:80 mA最大值(74HC系列) 2低输入电流为1mA最大 38位串行输入,并行出移位寄存器以存储 4宽工作电压范围:2V ± 6V 5级联 6移位寄存器直接明确 7保证移频率:DC至30兆赫

TL/F/5342-1 Top View Order Number MM54HC5S5 or MM74HC595 DuaHn-Line Package RCK SCK SCLR G Function X X X H Q A thruQH = TRI-STATE X X L L Shift Register cleared Q H -O X T H L Shift Register clocked C)N = Qnd ,Qo = SER T X H L Con tents of Shift Register transferred to output latches Operating Conditions Supply Voltage (V QC ) -0.5 to +7.0V DC Input Voltage (V IM ) -1.5 toV C c+15V DC OutpiX Voltage (V OUT ) -0.5 toVcc+0.5V Clamp Diode Current (I IK . I(X ) ±20 mA DC Output Current, per pin (lour) ±35 mA DC Vcc or GND Current, per pin (Icc) ±70 mA Storage Temperature Range (T STG ) -65"Cto+15(rC Power Dissipation (P Q ) (Note 3) 600 mW S.O. Package only 500 mW Lead Temp. (TO (Sobering 10 seconds) 2?TC Min Max Units Supply Voltage (Vcc) 2 6 V DC Input or Outpu* Voltage 0 Vcc V (Vw. VOUT ) Operating Temp. Range (T A ) MM74HC -40 +85 ?c MM54HC -55 + 125 ?c Input Rise or Fall Times VOC-20V 1000 ns V QC -4.5V 500 ns Vcc-6.0V 400 ns Absolute Maximum Ratings (Notes 1&2) If Military/Aerospace specified devices are required, please contact the National Semiconductor Sales Office/Distributors for availability and specifications ?

S3C2416芯片手册-中文不完整版

微软中国[键入公司地址] [键入电话号码] [键入传真号码] [选取日期]微软中国 [在此处键入文档摘要。摘要通常为文档内容的简短概括。在此处键入文档摘要。摘要通常为文档内容的简短概括。]

目录 1、产品概述 (3) 1、引言 (3) 2、特点 (3) 3、框图 (3) 4、引脚分配 (1) 4.1信号说明 (13) 2系统控制器 (35) 1概述 (35) 2、特点 (35) 3、框图 (36) 4、功能说明 (36) 4.1复位管理及类型 (36) 4.2硬件复位 (37) 4.3看门狗复位 (38) 4.4软件复位 (38) 4.5唤醒复位 (38) 5时钟管理 (39) 5.1时钟发生器概述 (39) 5.2时钟源选择 (39) 5.3PLL(锁相回路) (40) 5.4在正常操作下,改变PLL设置 (41) 5.5系统时钟控制 (41) 5.6ARM和总线时钟分频比 (42) 5.7配置时钟寄存器以产生AMBA时钟特定的频率 (42) 5.8ESYSCLK控制 (43) 6、电源管理 (43) 6.1功率模式状态图 (43) 6.2节能模式 (44) 6.3唤醒事件 (47) 6.4输出端口状态,以及停止和睡眠模式 (47) 6.5省电模式进入/退出条件 (48) 7寄存器说明 (48) 7.1地址映射 (48) 8独立的寄存器说明 (49) 8.1时钟源控制寄存器(LOCKCON0,LOCKCON1,OSCSET,MPLLCON,与 EPLLCON) (49) 8.2时钟控制寄存器(CLKSRC,CLKDIV,HCLKCON,PCLKCON,与SCLKCON) (51) 8.3电源管理寄存器(PWRMODE与PWRCFG) (54) 8.4复位控制寄存器(SWRST和RSTCON) (56) 8.5在普通模式和从休眠模式唤醒下,(I/O)保持位控制。 (56) 8.6系统控制器状态寄存器(WKUPSTAT与RSTSTAT) (57)

FPGA芯片介绍

Arria II GX FPGA器件 高无忌 2012511009 Arria?II 器件系列专为易操作性而设计。经过成本优化的40-nm 器件系列体系结构具有低功耗、可编程逻辑引擎、以及一体化的收发器和I/O 等特性。像PhyscialInterface for PCIExpress?(PCIe?)、Ethernet 和DDR3 存储器这样的公共接口在您的设计中可以很容易地通过Quartus?II 软件、SOPC Builder 设计软件以及Altera 所提供的多种硬/ 软知识产权(IP) 解决方案来实现。对于要求收发器运行在高达6.375 Gbps的应用程序设计而言,Arria II GX FPGA 器件系列能够使设计变得更快更容易。 Arria II GX FPGA器件特性 Arria II GX FPGA器件的关键特性如下: ■40-nm 低功耗FPGA 引擎 ■自适应逻辑模块(ALM) 实现了业界最高的逻辑效率 ■八输入分段查找表(LUT) ■存储器逻辑阵列模块(MLAB),用于小型FIFO 的有效实现 ■高达550 MHz 的高性能数字信号处理(DSP) ■可配置成9 x 9 位、12 x 12 位、18 x 18 位和36 x 36 位全精度乘法器,以及 18 x 36 位高精度乘法器 ■硬编码的加法器、减法器、累加器和求和功能 ■通过Altera 的MATLAB 和DSP Builder 软件实现的完全集成的设计流程 ■最大系统带宽 ■多达24个基于全双工时钟数据恢复(CDR)的收发器,支持600 Mbps到6.375 Gbps 的数据速率 ■专用电路,支持用于常用串行协议的物理层功能,这些串行协议包括:PCIeGen1 与PCIe Gen2、Gbps Ethernet、Serial RapidIO?(SRIO)、通用公共无线电接口(CPRI)、OBSAI、SD/HD/3G/ASI 串 行数字接口(SDI), XAUI 和ReducedXAUI(RXAUI)、HiGig/HiGig+、SATA/ 串行附加SCSI(SAS)、GPON、SerialLite II、光纤通道、SONET/SDH、Interlaken、串行数据转换器(JESD204) 和SFI-5。■采用嵌入式硬核IP模块的完整PIPE协议解决方案,嵌入式硬核IP模块提供了物理层 和介质存取控制(PHY/MAC) 层,数据链路层和传输层功能性 ■针对高带宽系统接口进行的优化 ■多达726个用户I/O管脚分布在支持多种单端和差分I/O标准的多达20个模块化的 I/O bank 中 ■高速LVDS I/O 支持,具有串化器/ 解串器(SERDES) 和运行在150 Mbps 到 1.25 Gbps数据速率上的动态相位对齐(DPA) 电路 ■低功耗 ■体系结构的功耗降低技术 ■100 mW @ 3.125 Gbps的物理介质附加子层(PMA) 的典型功耗 ■集成到Quartus II 开发软件的功耗优化 ■高级实用性和安全特性 ■并行和串行配置选项

CY7C1051DV33芯片手册

PRELIMINARY 8-Mbit (512K x 16) Static RAM CY7C1051DV33 Features ?High speed —t AA = 10 ns ?Low active power —I CC = 110 mA @ 10 ns ?Low CMOS standby power —I SB2 = 20 mA ?2.0V data retention ?Automatic power-down when deselected ?TTL-compatible inputs and outputs ?Easy memory expansion with CE and OE features ? Available in lead-free 48-ball FBGA and 44-pin TSOP II packages Functional Description [1] The CY7C1051DV33 is a high-performance CMOS Static RAM organized as 512K words by 16 bits. Write to the device by taking Chip Enable (CE) and Write Enable (WE) inputs LOW. If Byte LOW Enable (BLE) is LOW,then data from IO pins (IO 0–IO 7), is written into the location specified on the address pins (A 0–A 18). If Byte HIGH Enable (BHE) is LOW, then data from IO pins (IO 8–IO 15) is written into the location specified on the address pins (A 0–A 18). Read from the device by taking Chip Enable (CE) and Output Enable (OE) LOW while forcing the Write Enable (WE) HIGH.If Byte LOW Enable (BLE) is LOW, then data from the memory location specified by the address pins will appear on IO 0–IO 7.If Byte HIGH Enable (BHE) is LOW, then data from memory will appear on IO 8 to IO 15. See the “Truth Table” on page 8 for a complete description of Read and Write modes. The input/output pins (IO 0–IO 15) are placed in a high-impedance state when the device is deselected (CE HIGH), the outputs are disabled (OE HIGH), the BHE and BLE are disabled (BHE, BLE HIGH), or a Write operation (CE LOW,and WE LOW) is in progress. The CY7C1051DV33 is available in a 44-pin TSOP II package with center power and ground (revolutionary) pinout, as well as a 48-ball fine-pitch ball grid array (FBGA) package. Note 1.For guidelines on SRAM system design, please refer to the “System Design Guidelines” Cypress application note, available on the internet at https://www.360docs.net/doc/e11988459.html, . 1415Logic Block Diagram A 1A 2A 3A 4A 5A 6A 7A 8 COLUMN DECODER R O W D E C O D E R S E N S E A M P S INPUT BUFFER 512K × 16ARRAY A 0A 11A 13A 12A A A 16A 17A 18 A 9A 10IO 0–IO 7OE IO 8–IO 15 CE WE BLE BHE

FPGA芯片选择策略和原则

FPGA芯片选择策略和原则 一:设计考虑 1,器件的硬件资源 硬件资源是器件选型的重要标准。硬件资源包括逻辑资源、I/O资源、布线资源、DSP 资源、存储器资源、锁相环资源、串行收发器资源和硬核微处理器资源等。 1.1 逻辑资源、I/O资源、布线资源 逻辑资源和I/O资源的需求是每位设计人员最关心的问题,一般都会考虑到,可是, 过度消耗I/O资源和布线资源可能产生的问题却很容易被忽视。主流FPGA器件中,逻辑资源都比较丰富,一般可以满足应用需求。可是,在比较复杂的数字系统中,过度I/O资源的消耗可能会导致2个问题: 1)FPGA负荷过重,器件发热严重,严重影响器件的速度性能、工作稳定性和寿命,设计中要考虑器件的散热问题; 2)局部布线资源不足,电路的运行速度明显降低,有时甚至使设计不能适配器件,设计失败。 应用经验参考: 1)在做复杂数字信号处理时,位数比较高的乘法器和除法器对全局布线资源的消耗量比较大; 2)在做逻辑设计时,双向I/O口对局部布线资源的消耗量比较大; 3)在利用存储器资源设计滤波器的应用场合,局部布线资源的消耗量比较大; 4)在电气接口标准比较多,而逻辑比较复杂的应用场合,局部布线资源的消耗量比较大。 据Altera公司推荐,设计中最好能预留30%以上的逻辑资源、20%以上的I/O资源和30%以上的布线资源。而且,从两家公司器件的结构看,Xllinx公司器件的可编程逻辑块 相对于Altera公司要复杂一些,使用起来要灵活一些。在一些复杂的、控制信号比较多的设计中,适合选用Xllinx公司的产品。不过Xllinx公司器件布线资源是分段的,器件延时的可预测性要差一些。在这些应用场合,最好首先做设计仿真,对设计消耗的布线资源,尤其是很容易被忽视的局部布线资源,要有一个比较充分的了解,然后在考虑器件选型,是比较理想的。 1.2 DSP资源 在做乘法运算比较多而且对速度性能要求比较高的应用场合,最好能选用带DSP资源比较多的器件,例如,Altera公司的StatixⅡ和StatixⅢ系列,Xllinx公司的Virtex-4 SX 和Virtex-5 SX系列等。

FPGA可编程逻辑器件芯片XC5VLX155T-1FFG1136C中文规格书

Virtex-5 FPGA Electrical Characteristics Virtex?-5 FPGAs are available in -3, -2, -1 speed grades, with -3 having the highest performance. Virtex-5 FPGA DC and AC characteristics are specified for both commercial and industrial grades. Except the operating temperature range or unless otherwise noted, all the DC and AC electrical parameters are the same for a particular speed grade (that is, the timing characteristics of a -1 speed grade industrial device are the same as for a -1 speed grade commercial device). However, only selected speed grades and/or devices might be available in the industrial range.All supply voltage and junction temperature specifications are representative of worst-case conditions. The parameters included are common to popular designs and typical applications. This Virtex-5 FPGA data sheet, part of an overall set of documentation on the Virtex-5 family of FPGAs, is available on the Xilinx website: ?Virtex-5 Family Overview ?Virtex-5 FPGA User Guide ?Virtex-5 FPGA Configuration Guide ?Virtex-5 FPGA XtremeDSP? Design Considerations ?Virtex-5 FPGA Packaging and Pinout Specification ?Embedded Processor Block in Virtex-5 FPGAs Reference Guide ?Virtex-5 FPGA RocketIO? GTP Transceiver User Guide ?Virtex-5 FPGA RocketIO GTX Transceiver User Guide ?Virtex-5 FPGA Embedded Tri-Mode Ethernet MAC User Guide ?Virtex-5 FPGA Integrated Endpoint Block User Guide for PCI Express? Designs ?Virtex-5 FPGA System Monitor User Guide ? Virtex-5 FPGA PCB Designer’s Guide All specifications are subject to change without notice. Virtex-5 FPGA DC Characteristics DS202 (v5.5) June 17, 2016Product Specification Table 1:Absolute Maximum Ratings Symbol Description Units V CCINT Internal supply voltage relative to GND –0.5 to 1.1V V CCAUX Auxiliary supply voltage relative to GND –0.5 to 3.0V V CCO Output drivers supply voltage relative to GND –0.5 to 3.75V V BATT Key memory battery backup supply –0.5 to 4.05V V REF Input reference voltage –0.5 to 3.75V V IN (3) 3.3V I/O input voltage relative to GND (4) (user and dedicated I/Os) –0.75 to 4.05V 3.3V I/O input voltage relative to GND (restricted to maximum of 100 user I/Os)(5)–0.95 to 4.4 (Commercial Temperature) V –0.85 to 4.3 (Industrial Temperature)2.5V or below I/O input voltage relative to GND (user and dedicated I/Os)–0.75 to V CCO +0.5 V I IN Current applied to an I/O pin, powered or unpowered ±100 mA Total current applied to all I/O pins, powered or unpowered ±100mA V TS Voltage applied to 3-state 3.3V output (4) (user and dedicated I/Os) –0.75 to 4.05V Voltage applied to 3-state 2.5V or below output (user and dedicated I/Os)–0.75 to V CCO +0.5 V T STG Storage temperature (ambient)–65to 150°C T SOL Maximum soldering temperature (2)+220 °C T J Maximum junction temperature (2) +125 °C Notes: 1.Stresses beyond those listed under Absolute Maximum Ratings might cause permanent damage to the device. These are stress ratings only, and functional operation of the device at these or any other conditions beyond those listed under Operating Conditions is not implied. Exposure to Absolute Maximum Ratings conditions for extended periods of time might affect device reliability. 2.For soldering guidelines, refer to UG112: Device Package User Guide . For thermal considerations, refer to UG195: Virtex-5 FPGA Packaging and Pinout Specification on the Xilinx website. 3. 3.3V I/O absolute maximum limit applied to DC and AC signals. 4.For 3.3V I/O operation, refer to UG190: Virtex-5 FPGA User Guide, Chapter 6, 3.3V I/O Design Guidelines . 5.For more flexibility in specific designs, a maximum of 100 user I/Os can be stressed beyond the normal specification for no more than 20% of a data period .

三大FPGA芯片公司的主要产品系列和特点教学教材

三大F P G A芯片公司的主要产品系列和特 点

Altera、Xilinx、Actel Altera作为世界老牌可编程逻辑器件的厂家,是可编程逻辑器件的发明者,开发软件MAX+PLUSII和QuartusII。Altera 的主流FPGA分为两大类,一种侧重低成本应用,容量中等,性能可以满足一般的逻辑设计要求,如Cyclone,CycloneII;还有一种侧重于高性能应用,容量大,性能能满足各类高端应用,如Startix,StratixII等,用户可以根据自己实际应用要求进行选择。在性能可以满足的情况下,优先选择低成本器件。 * Cyclone(飓风):Altera中等规模FPGA,2003年推出,0.13um工艺,1.5v内核供电,与Stratix结构类似,是一种低成本FPGA系列,是目前主流产品,其配置芯片也改用全新的产品。 简评:Altera最成功的器件之一,性价比不错,是一种适合中低端应用的通用FPGA,推荐使用。 * CycloneII:Cyclone的下一代产品,2005年开始推出,90nm工艺,1.2v内核供电,属于低成本FPGA,性能和Cyclone相当,提供了硬件乘法器单元 简评:刚刚推出的新一代低成本FPGA,目前市场零售还不容易买到,估计从2005年年底开始,将逐步取代Cyclone器件,成为Altera在中低FPGA 市场中的主力产品。 * Stratix :altera大规模高端FPGA,2002年中期推出,0.13um工艺,1.5v内核供电。集成硬件乘加器,芯片内部结构比Altera以前的产品有很大变化。 简评:Startix芯片在2002年的推出,改变了Altera在FPGA市场上的被动局面。该芯片适合高端应用。随着2005年新一代StratixII器件的推出,将被StratixII逐渐取代。 * StratixII: Stratix的下一代产品,2004年中期推出,90nm工艺,1.2v内核供电,大容量高性能FPGA。 简评:性能超越Stratix,是未来几年中,Altera在高端FPGA市场中的主力产品。 *StrtratixV为altera目前的高端产品,采用28-nm工艺,提供了28G的收发器件,适合高端的FPGA产品开发