(完整版)OrCADCaptureCIS(Cadence原理图绘制)

OrCAD Capture CIS(Cadence原理图绘制)

1.新建原理图 (2)

1,打开软件 (2)

2,设置标题栏 (2)

3,创建工程文件 (4)

4,设置颜色 (4)

2.制作原理库 (6)

1,创建元件库 (6)

2,修改元件库位置,新建原理图封库 (6)

3,原理封装库的操作 (7)

3.绘制原理图 (9)

1.加入元件库,放置元件 (9)

2.原理图的操作 (10)

3. browse命令的使用技巧 (12)

4.元件的替换与更新 (13)

4.导出网表 (14)

1.原理图器件序号修改 (14)

2.原理图规则检查 (15)

3.显示DRC错误信息 (16)

4.创建网表 (17)

5.生成元件清单(.BOM) (18)

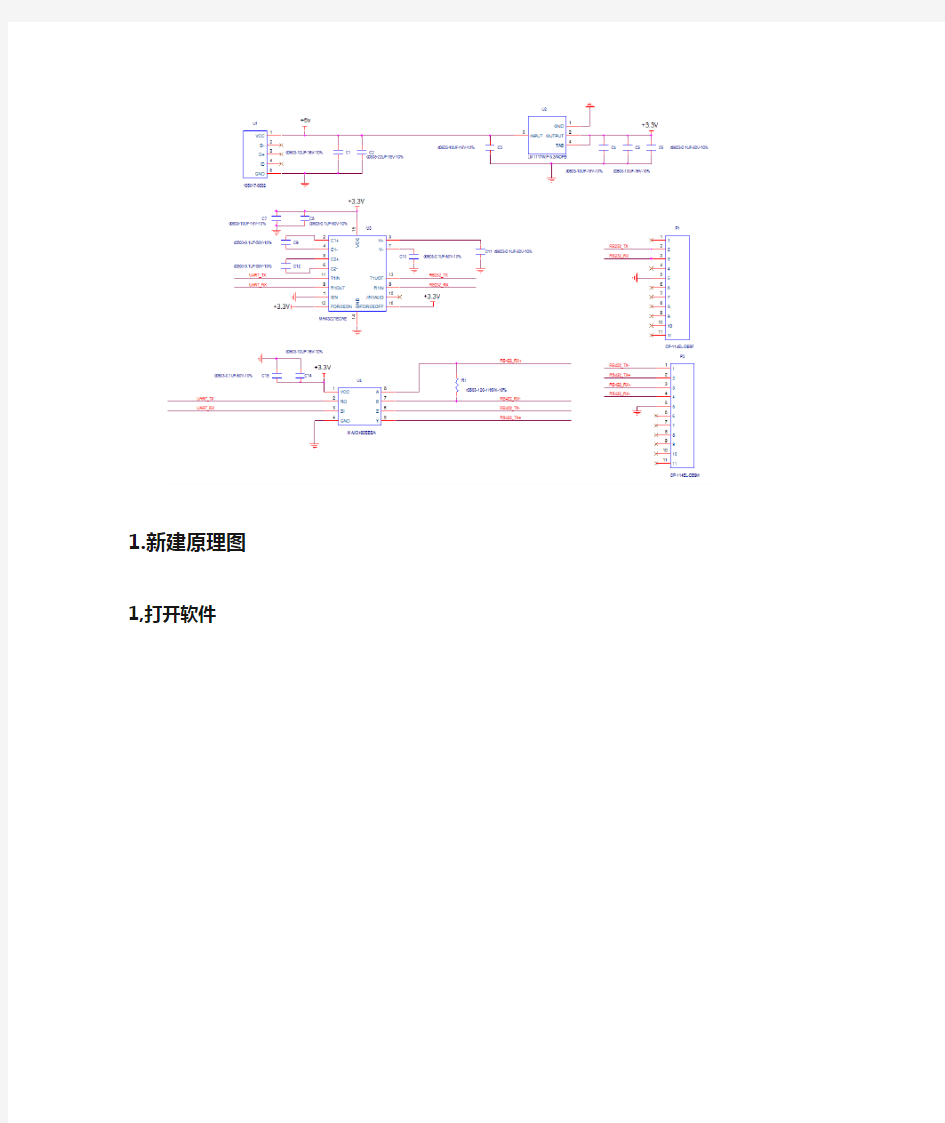

设计目的:创建如图RS232转换RS422原理图

1.新建原理图

1,打开软件

2,设置标题栏

Options-------DesignTemplate

创建完原理图工程后,也可以修改标题栏Options--------Schematic Page Properties

3,创建工程文件File------New------Projet

4,设置颜色

Options--------Preferences

2.制作原理库

1,创建元件库

File-------New----Library

2,修改元件库位置,新建原理图封库

点击如图位置鼠标右击,点击Save As另存为。New Part新建一个封装库。

3,原理封装库的操作

Place------Pin 放置管脚

选中管脚,按住键盘Ctrl同时鼠标拖动器件完成管脚的复制

选中管脚鼠标右击Edit Properties 编辑选中管脚信息,如下图

Place------Rectangle 放置矩形

Place------line 放置线

Place------Text 放置文字

Place------ellipse 放置椭圆

Options-----Part Properties 原理封装库属性Options-----Package Properties 原理封装库信息View------- Package 显示这个封装库的所有部分快捷键I-----放大O----缩小Delete-------删除

最终根据操作完成MAX3221ECAE原理图库的编辑

3.绘制原理图

1.加入元件库,放置元件

1.打开原理图工程,打开原理图

2.Place-------Part(快捷键P)添加封装

注:软件自带库路径,如下图所示

常用到的电容电阻库

2.原理图的操作

1.快捷键I-----放大O----缩小Delete-------删除W-------放置走线R----旋转方向按住Alt键拖动器件可以切断网络连接

Edit-----Mirror-----Horizontally 水平方向镜像

Edit-----Mirror------ vertically垂直方向镜像

Edit-----Mirror---------Both整体镜像

Edit-----Properties显示修改PCB封装信息

2.选中器件,按住键盘Ctrl同时鼠标拖动器件完成器件的复制

3.放置走线 1.鼠标左键双击终止布线2.画线时按住键盘Shift 任意角度走线

4.放置电源

5.放置地

6.放置空网络

7.放置节点

8.相同原理图放置网络连接(快捷键N)

9. 放置总线

10. 总线入口(F4连续放置总线入口网络等自动递增)

11. 不同原理图页面的网络连接

12. 放置文字

13.Options--------Preferences

3. browse命令的使用技巧

1.选中.dsn文件如图

2.Edit----Browse-----Parts显示修改器件信息Edit----Browse-----Nets显示修改网络信息

Edit----Browse-----DRC markers显示DRC错误信息

Edit----Browse-----off-page connectors显示不同原理图页面的网络连接4.元件的替换与更新

1.选中打开原理图工程中Design cache,如图

鼠标右击Cleanup Cache清除原理图中不存在的元件封装库

2.鼠标右击Design cache下所需要更新替换的封装库

Replace Cache-------替换元件封装库,如图所示

Update Cache--------更新封装库

最终经过以上操作完成如图所示原理图绘制

4.导出网表

注:导网表之前的注意事项:

1.原理图器件序号修改

2.原理图规则检查

3.PCB封装库是否正确无误,属性是否正确

4.网络管脚顺序是否准确

5.如果建立网络表时出现错误,查看“Sessions log”中错误信息1.原理图器件序号修改

1.选中.dsn文件如图

2.Tools-------Annotate

第一步:清除所有器件序号第二步:重新增加器件序号

2.原理图规则检查

Tools-----Design Rules Check

3.显示DRC错误信息

Edit----Browse-----DRC markers

4.创建网表

Tools------Create Netlist

如果建立网络表时出现错误,查看“Sessions.log与netlist.log”中错误信息

5.生成元件清单(.BOM) 注:生成清单前请先创建网表

1,先选中如图.dsn文件

2,Tools---------Bill of Materials

按照公司规范进行元件清单处理:10KMCSY清单.xlsx

Allegro中文教程

Allegro培训教材 目录 第一章 焊盘制作-------------------------------------------------------2 1.1 用Pad Designer 制作焊盘---------------------------------------2 1.2 制作圆形热风焊盘----------------------------------------------7 第二章 建立封装------------------------------------------------------10 2.1 新建封装文件-------------------------------------------------10 2.2 设置库路径---------------------------------------------------11 2.3 画元件封装---------------------------------------------------12 第三章 元器件布局----------------------------------------------------22 3.1 建立电路板(PCB)----------------------------------------------22 3.2 导入网络表---------------------------------------------------23 3.3 摆放元器件---------------------------------------------------26 第四章 PCB布线------------------------------------------------------31 4.1 PCB 层叠结构-------------------------------------------------31 4.2 布线规则设置-------------------------------------------------34 4.2.1 对象(object)--------------------------------------------35 4.2.2 建立差分对----------------------------------------------37 4.2.3 差分对规则设置------------------------------------------38 4.2.4 CPU与DDR内存芯片走线约束规则--------------------------40 4.2.5 设置物理线宽和过孔--------------------------------------46 4.2.6 设置间距约束规则----------------------------------------52 4.2.7 设置相同网络间距规则------------------------------------56 4.3 Allegro PCB布线----------------------------------------------56 4.3.1 手工拉线------------------------------------------------56 4.3.2 应用区域规则--------------------------------------------60 4.3.3 扇出布线------------------------------------------------61 4.3.4 差分布线------------------------------------------------63 4.3.5 等长绕线------------------------------------------------65 4.3.6 分割平面------------------------------------------------66 第五章 光绘文件输出--------------------------------------------------69 5.1 Artwork 参数设置---------------------------------------------69 5.2 生成钻孔文件-------------------------------------------------75 5.3 输出底片文件-------------------------------------------------79

OrCAD Capture CIS Cadence原理图绘制

OrCADCaptureCIS(Cadence原理图绘制) 1,打开软件........................................ 2,设置标题栏..................................... 3,创建工程文件................................... 4,设置颜色........................................ 2.制作原理库.......................................... 1,创建元件库...................................... 2,修改元件库位置,新建原理图封库................. 3,原理封装库的操作............................... 3.绘制原理图.......................................... 1.加入元件库,放置元件............................ 2.原理图的操作.................................... 3.browse命令的使用技巧 ........................... 4.元件的替换与更新................................ 4.导出网表............................................ 1.原理图器件序号修改.............................. 2.原理图规则检查.................................. 3.显示DRC错误信息................................ 4.创建网表........................................ 5.生成元件清单(.BOM)..................................

Cadence原理图绘制流程

第一章设计流程 传统的硬件系统设计流程如图1-1所示,由于系统速率较低,整个系统基本工作在集中参数模型下,因此各个设计阶段之间的影响很小。设计人员只需要了解本阶段的基本知识及设计方法即可。但是随着工艺水平的不断提高,系统速率快速的提升,系统的实际行为和理想模型之间的差距越来越大,各设计阶段之间的影响也越来越显著。为了保证设计的正确性,设计流程也因此有所变动,如图1-2所示,主要体现在增加了系统的前仿真和后仿真。通过两次仿真的结果来预测系统在分布参数的情况下是否能够工作正常,减少失败的可能性。 细化并调整以上原理图设计阶段的流 程,并结合我们的实际情况,原理图设计 阶段应该包括如下几个过程: 1、 阅读相关资料和器件手册 在这个阶段应该阅读的资料包括,系统的详细设计、数据流分析、各器件手册、器件成本等。 2、 选择器件并开始建库 在这个阶段应该基本完成从主器件到各种辅助器件的选择工作,并根据选择结果申请建库。 3、 确认器件资料并完成详细设计框图 为保证器件的选择符合系统的要求,在这一阶段需要完成各部分电路具体连接方式的设计框图,同时再次确认器件的相关参数符合系统的要求,并能够和其他器件正确配合。 4、 编写相关文档 这些文档可以包括:器件选择原因、可替换器件列表、器件间的连接框图、相关设计的来源(参考设计、曾验证过的设计等),参数选择说明,高速连接线及其它信息说明。 5、 完成EPLD 内部逻辑设计,并充分考虑可扩展性。

在编写相关文档的的同时需要完成EPLD内部逻辑的设计,确定器件容量及连接方式可行。 6、使用Concept-HDL绘制原理图 7、检查原理图及相关文档确保其一致性。 以上流程中并未包括前仿真的相关内容,在设计中可以根据实际情况,有选择的对部分重要连线作相关仿真,也可以根据I/O的阻抗,上升下降沿变化规律等信息简单分析判断。此流程中的各部分具体要求、注意事项、相关经验和技巧有待进一步完善。

cadence入门教程

本文介绍cadence软件的入门学习,原理图的创建、仿真,画版图和后仿真等一全套过程,本教程适合与初学着,讲到尽量的详细和简单,按照给出的步骤可以完全的从头到尾走一遍,本教程一最简单的反相器为例。 打开终端,进入文件夹目录,输入icfb&启动软件,主要中间有个空格。 启动后出现下图: 点击Tools的Library Manager,出现如下: 上面显示的是文件管理窗口,可以看到文件存放的结构,其中Library就是文件夹,Cell就是一个单元,View就是Cell的不同表现形式,比如一个mos管是一个Cell,但是mos管有原理图模型,有版图模型,有hspice参数模型,有spectre参数模型等,这就列举了Cell的4个View。他们之间是树状的关系,即,Library里面有多个Cell,一个Cell里面有多个View。应该保持一个好习惯就是每个工程都应该建立一个Library,Cell和View之间的管理将在后面介绍。

现在建立工程,新建一个Library,如下左图,出现的对话框如下有图: 在上右图中选择合适的目录,并敲入名字,这里取的是inv,这就是新建的文件夹的名字,以后的各种文件都在这个文件夹下。OK后出现下面对话框 这个对话框是选择是否链接techfile,如果只是原理图仿真而不用画版图,就选择Dont need a techfile,这里我们要画版图,而且有工艺库,选择Attach to an existing techfile,OK 后出现下面对话框:

在technology Library选择tsmc18rf,我们使用的是这个工艺库。Inv的文件夹就建好了,在Library Manager就有它了,如下图: 文件夹建好了后,我们要建立原理图,在inv的Library里面新建Cell如下:

Cadence从原理图到PCB

Cadence从原理图到PCB的流程图: 一.原理图 1.建立工程 2.绘制原理图 3. 生成网络表(Net List): 在画板的时候需要导入网络表,在这之前可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools—Annotate;再进行DRC检测。DRC之后可以尝试去生成网络表了,在工程管理界面下,选Tools--Create Netlist, 二.PCB 1. 打开PCB Editor,在弹出的对话框中选择Allegro PCB Design GXL(legacy),然后点击Ok进入PCB编辑器。接下来就是利用向导建立电路板了,包括确定板子的大小、层数、形状等等参数。 File-new 在弹出的对话框中的Drawing Type选择Board(wizard),然后确定文件名,Browse存盘路径等,最后点Ok进入向导。

注意:板子的路径应该和前面生成网表的路径保持一致。 2.导入网络表 接上一个步骤,将网络表导入到刚建好的PCB中。 在此之前还有一个很重要的工作要做,就是指定PCB封装的路径。点击Setup--User Preferences,在弹出对话框中的Categories中选中Design_paths,分别为padpath和psmpath指定路径,即将PCB元件封装路径添加到padpath和psmpath中,以告知Allegro从指定的路径寻找封装。

元件的PCB封装需要自己做或是直接用别人做好的,封装准备好后往PCB 中导入网络表,点击File--Import--Logic,在Import directory中指定在原理图部分生成的网络表文件路径,其他设置使用默认值即可,点击Import Cadence即可导入网络表。 3.叠层设计,规则设定,布局布线 暂时简单描述下元件的放置,布局,布线,具体的叠层设计,设计规则等后面再详细补充

于博士Cadence视频教程原理图设计pdf

Cadence SPB 15.7 快速入门视频教程 的SPB 16.2版本 第01讲 - 第15讲:OrCAD Capture CIS原理图创建 第16讲 - 第26讲:Cadence Allegro PCB创建封装 第27讲 - 第36讲:Cadence Allegro PCB创建电路板和元器件布局 第37讲 - 第46讲:Cadence Allegro PCB设置布线规则 第47讲 - 第56讲:Cadence Allegro PCB布线 第57讲 - 第60讲:Cadence Allegro PCB后处理、制作光绘文件 第1讲 课程介绍,学习方法,了解CADENCE软件 1.要开发的工程 本教程以下面的例子来开始原理图设计和PCB布线 2.教程内容

3.软件介绍 Design Entry CIS:板级原理图工具 Design Entry HDL:设计芯片的原理图工具,板级设计不用 Layout Plus:OrCAD自带的PCB布线工具,功能不如PCB Editor强大 Layout Plus SmartRoute Calibrate:OrCAD自带的PCB布线工具,功能不如PCB Editor强大PCB Editor:Cadence 的PCB布线工具 PCB Librarian:Cadence 的PCB封装制作工具 PCB Router:Cadence 的自动布线器 PCB SI:Cadence 的PCB信号完整性信号仿真的工具 SigXplorer:Cadence 的PCB信号完整性信号仿真的工具 4.软件列表

5.开始学习Design Entry CIS 启动:Start/Cadence SPB 16.2/Design Entry CIS 启动后,显示下图: 里面有很多选项,应该是对应不同的License 本教程使用:OrCAD Capture CIS 我个人认为:Allegro PCB Design CIS XL是所有可选程序中,功能最强大的,但不知道,强在哪里;而且本教程的原理图文件可以使用上表中不同的程序打开 6.选择OrCAD Capture CIS,启动后显示下图

60分钟学会OrCAD中文教程(SIG007版)

于博士信号完整性研究网 https://www.360docs.net/doc/ec7856932.html, 60分钟学会OrCAD Capture CIS 作者:于争 博士 2009年4月28日

目录 1 建立工程及设置......................................................................................................................- 1 - 2 工程管理器..............................................................................................................................- 4 - 3 原理图页相关操作..................................................................................................................- 5 - 4 创建元件库..............................................................................................................................- 6 - 5 元件库编辑一些知识技巧......................................................................................................- 9 - 6 如何创建不规则图形元件....................................................................................................- 10 - 7 分裂元件................................................................................................................................- 15 - 8 把一个元件分多个部分画出来............................................................................................- 16 - 8.1 Homogeneous类型元件画法......................................................................................- 16 - 8.2 Heterogeneous类型元件画法..................................................................................- 17 - 8.3 分裂元件使用方法.....................................................................................................- 19 - 9 加入元件库放置元件............................................................................................................- 21 - 9.1普通元件放置方法......................................................................................................- 21 - 9.2 电源和地的放置方法.................................................................................................- 23 - 10 同一个页面内建立互连......................................................................................................- 24 - 11 不同页面间建立互联的方法..............................................................................................- 26 - 12 使用总线..............................................................................................................................- 27 - 12.1 如何创建总线...........................................................................................................- 27 - 12.2 放置非90度转角总线.............................................................................................- 28 - 12.3 总线命名...................................................................................................................- 28 - 12.4 总线与信号线连接...................................................................................................- 28 - 13 浏览工程及使用技巧..........................................................................................................- 29 - 13.1 浏览parts................................................................................................................- 30 - 13.2 浏览nets..................................................................................................................- 31 - 14 原理图中搜索......................................................................................................................- 32 - 14.1 搜索元件...................................................................................................................- 33 - 14.2 查找网络 flat nets...............................................................................................- 34 - 15 元件替换与更新..................................................................................................................- 35 - 15.1 批量替换 replace cache.......................................................................................- 35 - 15.2 批量更新 update cache.........................................................................................- 36 - 15.3 两个命令的区别.......................................................................................................- 36 - 16 一些基本操作......................................................................................................................- 36 - 16.1选择元件....................................................................................................................- 36 - 16.2 移动元件...................................................................................................................- 37 - 16.3 元件的旋转...............................................................................................................- 37 - 16.4 元件的镜像翻转.......................................................................................................- 37 - 16.5 修改元件属性放置文本...........................................................................................- 37 - 17 添加footprint属性..............................................................................................................- 38 - 17.1 单个元件添加Footprint属性...............................................................................- 38 - 17.2 批量添加Footprint属性.......................................................................................- 41 - 18 生成Netlist..........................................................................................................................- 44 - 19 生成元件清单......................................................................................................................- 47 - 20 打印原理图..........................................................................................................................- 51 -

Cadence 原理图库设计

Cadence原理图库设计 一.工具及库文件目录结构 Cadence提供Part Developer库开发工具供大家建原理图库使用。 Cadence 的元件库必具备如下文件目录结构为: Library----------cell----------view(包括Sym_1,Entity,Chips,Part-table) Sym_1:存放元件符号 Entity:存放元件端口的高层语言描述 Chips:存放元件的物理封装说明和属性 Part-table:存放元件的附加属性,用于构造企业特定部件 我们可以通过定义或修改上述几个文件的内容来创建和修改一个元件库,但通过以下几个步骤来创建元件库则更直观可靠一些。 二.定义逻辑管脚 在打开或新建的Project Manager中,如图示,打开Part Developer。 然后出现如下画面, 点击Create New,下图新菜单中提示大家选择库路径,新建库元件名称及器件类型。

点击ok后,Part Developer首先让大家输入元件的逻辑管脚。一个原理图符号可以有标量管脚和矢量管脚。 标量管脚在符号中有确定位置,便于检查信号与管脚的对应,但矢量管脚却可使原理图更简洁,适用于多位 总线管脚。 点击上图中的Edit,编辑器会让我们对首或尾带有数字的字符串的多种输入方式(A1; 1A; 1A1)进行选择,一但选定,编辑器即可对同时具有数字和字母的管脚输入进行矢量或标量界定。 管脚名首尾均不带数字的字符串如A; A1A则自动被识别为标量管脚。 按照元件手册决定管脚名称及逻辑方向,选择是否为低电平有效,点击ADD即可加入新的管脚。 (注:不论是标量或矢量管脚,均可采用集体输入,如在Pin Names栏可输入A1-A8, 1C-16C)

CADENCE从原理图到PCB步骤(精)

CADENCE从原理图到PCB步骤 一.原理图 1.建立工程 与其他绘图软件一样,OrCAD以Project来管理各种设计文件。点击开始菜单,然后依次是所有程序-- Allegro SPB 15.5--Design Entry CIS,在弹出的Studio Suite Selection对话框中选择第一项OrCAD_Capture_CIS_option with capture,点击Ok进入Capture CIS。接下来是File--New--Project,在弹出的对话框中填入工程名、路径等等,点击Ok进入设计界面。2.绘制原理图 新建工程后打开的是默认的原理图文件SCHEMATIC1 PAGE1,右侧有工具栏,用于放置元件、画线和添加网络等等,用法和Protel类似。点击上侧工具栏的Project manager(文件夹树图标)进入工程管理界面,在这里可以修改原理图文件名、设置原理图纸张大小和添加原理图库等等。 1)修改原理图纸张大小: 双击SCHEMATIC1文件夹,右键点击PAGE1,选择Schematic1 Page Properties,在Page Size 中可以选择单位、大小等; 2)添加原理图库: File--New--Library,可以看到在Library文件夹中多了一个library1.olb的原理图库文件,右键单击该文件,选择Save,改名存盘; 3)添加新元件: 常用的元件用自带的(比如说电阻、电容的),很多时候都要自己做元件,或者用别人做好的元件。右键单击刚才新建的olb库文件,选New Part,或是New Part From Spreadsheet,后者以表格的方式建立新元件,对于画管脚特多的芯片元件非常合适,可以直接从芯片Datasheet中的引脚描述表格中直接拷贝、粘贴即可(pdf格式的Datasheet按住Alt键可以按列选择),可以批量添加管脚,方便快捷。 4)生成网络表(Net List): 在画板的时候需要导入网络表,在这之前原理图应该差不多完工了,剩下的工作就是查缺补漏。可以为元件自动编号,在工程管理界面下选中.dsn文件,然后选Tools—Annotate (注解),在弹出的对话框中选定一些编号规则,根据需求进行修改或用默认设置即可。进行DRC检测也是在生成网络表之前的一项重要工作,可以避免出现一些不必要的设计错误。DRC之后可以尝试去生成网络表了,还是在工程管理界面下,选Tools--Create Netlist,可以在弹出的对话框中选择网络表的存放路径,其他默认设置即可,生成网络表的过程中如果出错,可以通Windows--Session Log查看出错的原因,比如说有元器件忘了添加封装等。 5)更新元件到原理图: 当元件库中的某个元件修改后需要原理图也同步更新时,可以不必重新放置元件(万一有100个或更多该元件岂不是要疯了),在工程管理界面下,双击Design Cache文件夹,选中刚才修改的元件,右键单击选择Update Cache,一路yes下去即可将原理图中该元件全部更新。 6)一些细节: 画原理图时的放大和缩小分别是按键“i”(Zoom In)和“o”(Zoom Out)和Protel有所区别;在创建元件封装的时候,除了GND可以同名以外,不能有其他同名的管脚,否者报错,不过貌似报错也没有影响,因为打开OrCAD自带的元件库时(比如Xilinx的FPGA),也有除GND外的同名管脚;添加网络标号的快捷键是“n”,不过在OrCAD中网络标号无法复制,记得Protel中是可以通过复制已有的网络标号来添加新的网络标号的。

分钟学会OrCAD中文教程

60 分钟学会OrCAD Capture CIS 于博士信号完整性研究网 分钟学会OrCAD Capture CIS 作者:于争博士 2009 年 4 月 28 日 文章来源:于博士信号完整性研究网分钟学会OrCAD Capture CIS 目录 1 建立工程及设置......................................................................................................................- 1 - 2 工程管理器..............................................................................................................................- 4 - 3 原理图页相关操作..................................................................................................................- 5 - 4 创建元件库..............................................................................................................................- 6 - 5 元件库编辑一些知识技巧......................................................................................................- 9 - 6 如何创建不规则图形元件....................................................................................................- 10 - 7 分裂元件................................................................................................................................- 15 - 8 把一个元件分多个部分画出来............................................................................................- 16 - Homogeneous 类型元件画法......................................................................................- 16 - Heterogeneous 类型元件画法..................................................................................- 17 - 分裂元件使用方法.....................................................................................................- 19 - 9 加入元件库放置元件............................................................................................................- 21 - 普通元件放置方法......................................................................................................- 21 - 电源和地的放置方法.................................................................................................- 23 - 10 同一个页面内建立互连......................................................................................................- 24 - 11 不同页面间建立互联的方法..............................................................................................- 26 - 12 使用总线..............................................................................................................................- 27 - 如何创建总线...........................................................................................................- 27 - 放置非90 度转角总线.............................................................................................- 28 -

cadence入门教程

Cadence 系列软件从schematic到layout入门 一.客户端软件使用及icfb启动 要使用工作站上的软件,我们必须在PC中使用xwinpro等工具连接到工作站上。从开始菜单中,运行xwinpro的xSettings,按照下图设置: 点击上图的Settings在出现的窗口中按如下设置(connect host选择为192.168.1.137):

设置完后,从开始菜单中运行xwinpro的xsessions,应该就可以进入登陆界面,用户名为user1,密码为root。 二、Schematic Cadence系列软件包含了电路图工具Schematic,晶体管级电路仿真工具Spectre,以及版图工具Virtuoso等。一般来说,我们先用Schematic画好电路原理图然后进行仿真,最后用Virtuoso手动画版图或者直接进行版图综合,最后对版图进行L VS,DRC等验证。 在登陆进工作站后,点击鼠标右键,选择tools——>terminal,在弹出的terminal窗口中敲入命令icfb&就可以启动cadence了。 图1 icfb的主界面 我们以建立一个反相器电路为例子: 在icfb中,任何一个电路,不论是已经存在的可以引用的库,还是用户新建立的一个电路,都是一个library. 一个library一般有若干个Cell(单元电路),每个cell有若干个

schematic(电路原理)和若干个layout(版图)。所以,我们要做的第一步,就是先创建一个自己的“库”,File菜单->new->library 图2 新建一个库的界面 从这个新建一个library的界面,我们必须输入新建立的库的名称,并且选择好这个库应该存放的目录,然后注意看右边的三个选项,关于新建立的库是否需要链接到Technology File 的问题。首先,这个Technology File一般是指工艺库,由Foundry提供。如果最终做的电路是需要画出Layout(版图)的,就必须要有工艺库,如果不需要画Layout,那就可以不需要工艺库。由于我们需要演示这一步,所以就选择Attach to an existing techfile。(也可以在建立之后,再Attach to an existing techfile)。 输入name: testinv, (大家在做的时候自己起一个名字)。 现在,我们就已经建立好了一个新的“库”,为了给这个库增加schematic(电路图)和Layout(版图)我们就必须对这个库进行“管理”,从icfb的主菜单(图1)中的Tools菜单->Library Manager.

如何将altium designer的原理图和PCB转入cadence里

说明: 1)本教程适用于将altium designer的原理图和PCB转入cadence(分别对应capture CIS和allegro)里。对于protel 99se,可以将其先导入较新版本的AD里,再转入cadence中。 2)整个过程中使用的软件包括altium designer Summer 08,cadence16.6,orCAD10.3-capture(免安装精简版),PADS9.3三合一完美精简版。其中,后面两个软件较小,便于下载。 3)原理图的转化路线是,从altium designer导出的.dsn文件,用orcad10.3-capture打开后,保存为cadence16.6可以打开的文件。因为较新版本的cadence不能直接打开AD转换出来的.dsn文件。如果你不是这些版本的软件,也可以参考本人的方法进行尝试。 4)pcb转化的顺序是,altium designer导出的文件,导入PADS9.3打开,然后导出.asc文件。随后利用allegro对pads的接口,将pads文件导入。 1. 原理图的导入 1.1选中原理图的项目文件,即.PRJPCB文件,右键-》save projec as,选择.dsn文件,输入要保存的文件名,保存。注意输入新的文件名的时候要把文件名的后缀手动改掉。 1.2打开orCAD10.3-capture文件夹下面的capture.exe(如果同一台电脑装了新版本的cadence,例如cadence16.6的话,环境变量中的用户变量会有冲突。具体地来说对于orCAD10.3来说,CDS_LIC_FILE的值必须是安装目录\orCAD10.3-capture\crack\license.dat。而对于cadence16.6来说,环境变量必须是5280@localhost。因此要使用orCAD10.3的话,必须将CDS_LIC_FILE的值改掉,否则无法打开。等下使用cadence16.6,就必须将值改回来)。 1.3使用orCAD10.3将刚才保存的.dsn文件打开,并保存成project。 1.4 随后就可以使用新版本的cadence的capture CIS打开保存的文件(注意改环境变量中的用户变量CDS_LIC_FILE)。 2. PCB的导入 由于allegro可以根据已有的brd文件生成元器件的封装,因此将PCB导入allegro后使用者免于重新使用allegro绘制一遍封装。 1.1打开pads9.3,file-》new,按照默认配置建立一个文件,保存。 1.2file-》import,选中要转换的.pcb文件,打开,保存在C盘的PADS Projects文件夹下面。 (安装PADS9.3三合一完美精简版时会自动在C盘产生这个文件夹。) 1.3file-》export,将文件保存为.asc文件。接下来回弹出下图所示的对话框。注意要将.pcb 文件和.asc文件保存在同一个目录下,即C盘的PADS Projects文件夹下面,否则allegro