北邮数字逻辑期中试题及参考材料规范标准答案

北京邮电大学

《数字电路与逻辑设计》期中考试试题

2015.4.11

班级姓名班内序号

注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。

一、(每题1分,共20分)判断(填√或×)、单项选择题

(请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。)1.ECL逻辑门与TTL门相比,主要优点是抗干扰能力强。(╳)2.CMOS门电路在使用时允许输入端悬空,并且悬空的输入端相当于输入逻辑“1”。( ╳)

3.若对4位二进制码(B3B2B1B0)进行奇校验编码,则校验位C= B3⊕B2⊕B1⊕B0⊕1。(√)

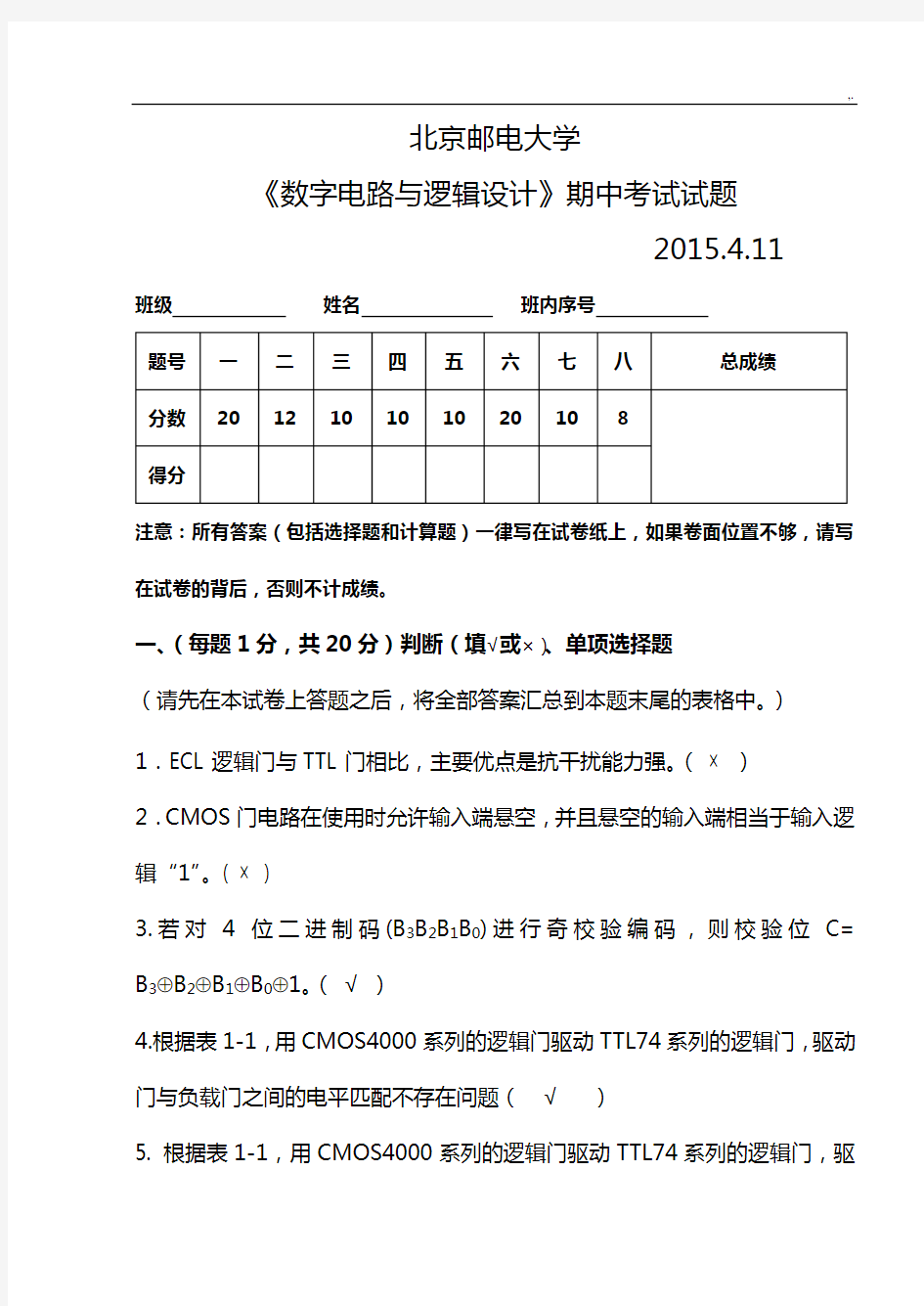

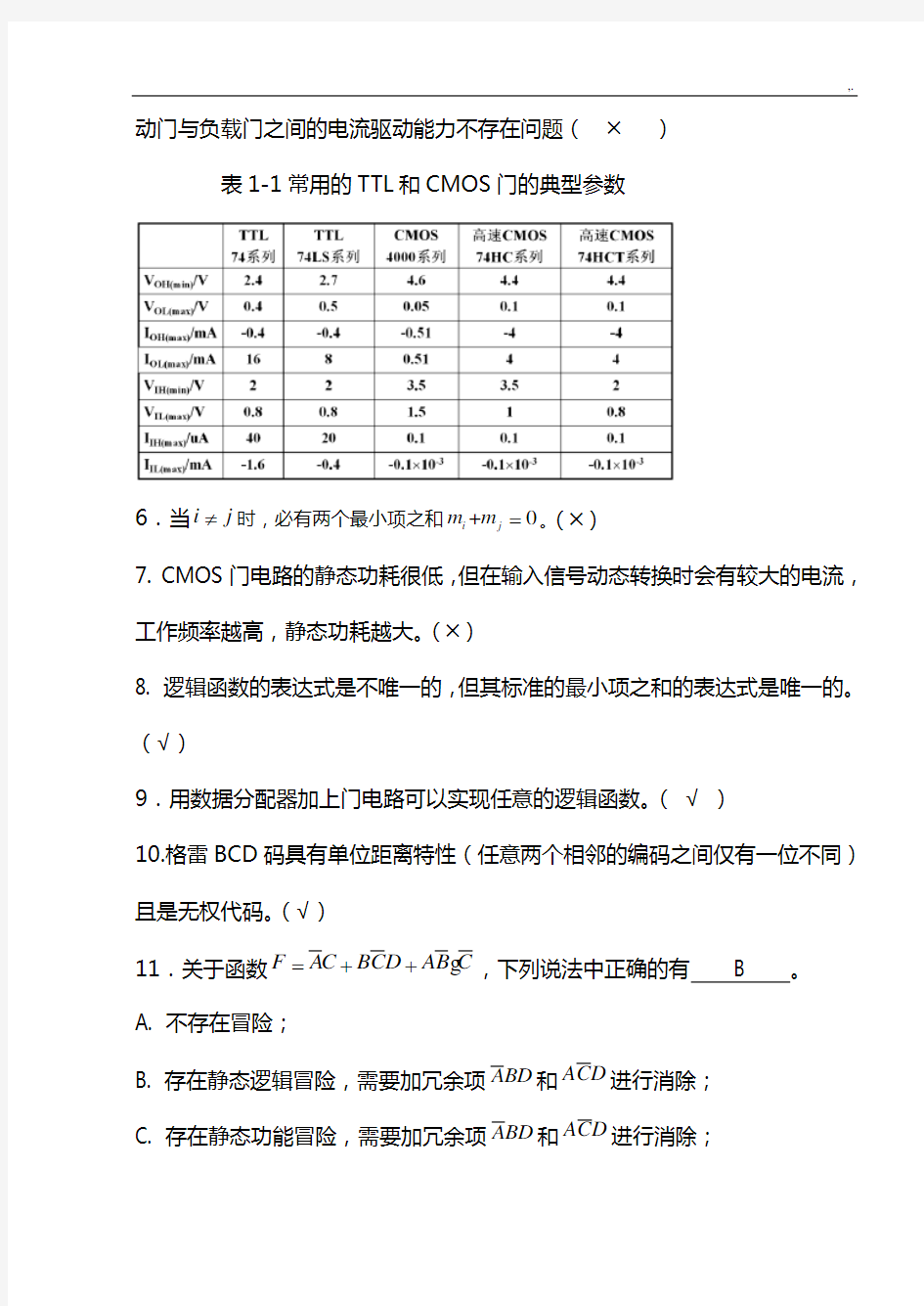

4.根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电平匹配不存在问题(√)

5. 根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱

动门与负载门之间的电流驱动能力不存在问题(╳)

表1-1常用的TTL和CMOS门的典型参数

6.当i j≠时,必有两个最小项之和+0

m m=。(╳)

i j

7. CMOS门电路的静态功耗很低,但在输入信号动态转换时会有较大的电流,工作频率越高,静态功耗越大。(╳)

8. 逻辑函数的表达式是不唯一的,但其标准的最小项之和的表达式是唯一的。(√)

9.用数据分配器加上门电路可以实现任意的逻辑函数。(√)

10.格雷BCD码具有单位距离特性(任意两个相邻的编码之间仅有一位不同)且是无权代码。(√)

=++g,下列说法中正确的有 B 。11.关于函数F A C BCD AB C

A. 不存在冒险;

B. 存在静态逻辑冒险,需要加冗余项ABD和ACD进行消除;

C. 存在静态功能冒险,需要加冗余项ABD和ACD进行消除;

D. 当输入ABCD 从 0001→0100变化时存在静态逻辑冒险。 12.逻辑函数F=A ⊕B 和G=A ⊙B 满足关系 D 。 A.F G =

B.0F G +=

C.1F G =g

D.0F G =e

13.若逻辑函数∑=)6,3,2,1(),,(m C B A F ,∑=)7,5,4,3,2,0(),,(m C B A G ,则

=?G F A 。 A.32m m +

B.1

C.AB

D.AB

14.若干个具有三态输出的电路输出端接到一点工作时,必须保证 B 。 A.任何时刻最多只能有一个电路处于高阻态,其余应处于工作态。 B.任何时刻最多只能有一个电路处于工作态,其余应处于高阻态。 C.任何时刻至少有一个电路处于高阻态,其余应处于工作态。 D.任何时刻至少有一个电路处于工作态,其余应处于高阻态。 15.可以用来传输连续变化的模拟信号的电路是 D 。 A. 三态输出的门电路。; B. 漏极开路的CMOS 门电路; C. ECL 门电路; D. CMOS 传输门

16.逻辑表达式的对偶式为 B 。

A . B.

C.

D.

17.下列说法中正确的是 D 。

A .三态门的输出端可以直接并联,实现线或逻辑功能。

B. OC门的输出端可以直接并联,实现线或逻辑功能。

C.OD门的输出端可以直接并联,实现线或逻辑功能。

D.ECL门的输出端可以直接并联,实现线或逻辑功能。

18.某集成电路芯片,查手册知其最大输出低电平U OLmax=0.5V,最大输入低电平U ILmax=0.8V,最小输出高电平U OHmin=2.7V,最小输入高电平U IHmin=2.0V,则其低电平噪声容限U NL和高电平噪声容限U NH分别是C 。

A. 1.5V、2.2V

B.2.2V、1.2V

C. 0.3V、0.7V

D.1.9V、1.5V

19.下列说法中不属于组合电路的特点的是 C 。

A.组合电路由逻辑门构成;

B.组合电路不含记忆存储单元;

C.组合电路的输出到输入有反馈回路;

D.任何时刻组合电路的输出只与当时的输入有关,而与电路过去的输入无关。20.在图1-1的CMOS门电路中,输出为高电平的有 D 。

V

A. B. C. D.

图1-1

1A T A B

1B T 2A

T 2B

T 3

T 4

T 1

D 2

D 3

D 1A R 1B R 3

R 4

R 2

R F

L

M N

O C D 1'

D 2'

D CC V B D A B D B D C C D

二、(共12分)器件的内部电路如图2-1所示,A ,B 为输入,F 为输出。(1),写出L 、M 、N 、O 、F 点与输入A 、B 间的相对逻辑关系表达式。(2),画出该器件的符号。 解:

(1)L=AB M=CD

N AB CD =+ O AB CD =+ F N O AB CD ===+

(10分)

图2-1

(2)

(2分)

三、(10分) 请用最少的或非门设计一个检出8421BCD 码能被4整除的逻辑电路(输入变量为ABCD ,且提供反变量):

(1)根据功能需求完成表3-1真值表的填写;

(2)并写出该函数的标准与或表达式(使用;F=∑ +∑ 形式);(3)将真值表填入图3-1的卡诺图,并用卡诺图法简化为最简或与式;(4)用或非门实现该函数,画出逻辑图。

表3-1

数字逻辑电路期末考试试卷及答案

期末考试试题(答案) 考试科目:数字逻辑电路 试卷类别:3卷 考试时间:110 分钟 XXXX 学院 ______________系 级 班 姓名 学号 题号 一 二 三 四 总分 得分 一、选择题(每小题2分,共20分) 1. 八进制(273)8中,它的第三位数2 的位权为___B___。 A .(128)10 B .(64)10 C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。 A .A B F = B . C AB F += C .C A AB F += D . C B AB F += 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A . 原码 B .ASCII 码 C . 补码 D . BCD 码 4.对于如图所示波形,其反映的逻辑关系是___B_____。 A .与关系 B . 异或关系 C .同或关系 D .无法判断 5. 连续异或1985个1的结果是____B_____。 A .0 B .1 C .不确定 D .逻辑概念错误 得分 评卷人 装 订 线 内 请 勿 答 题

6. 与逻辑函数D C B A F+ + + =功能相等的表达式为___C_____。 D C B A F+ + + =B.D C B A F+ + + = D.D C B A F+ + = 7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。 8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为 _____D_____。 A.500KHz B.200KHz C.100KHz D.50KHz 9.下列器件中,属于时序部件的是_____A_____。 A.计数器B.译码器C.加法器D.多路选择器 装

《数字逻辑》考试答案

中国石油大学(北京)远程教育学院 《数字逻辑》期末复习题 一、单项选择题 1. TTL 门电路输入端悬空时,应视为( A ) A. 高电平 B. 低电平 C. 不定 D. 高阻 2. 最小项D C B A 的逻辑相邻项是( D ) A .ABCD B .D B C A C .C D AB D .BCD A 3. 全加器中向高位的进位1+i C 为( D ) A. i i i C B A ⊕⊕ B.i i i i i C B A B A )(⊕+ C.i i i C B A ++ D.i i i B C A )(⊕ 4. 一片十六选一数据选择器,它应有( A )位地址输入变量 A. 4 B. 5 C. 10 D. 16 5. 欲对78个信息以二进制代码表示,则最少需要( B )位二进制码 A. 4 B. 7 C. 78 D. 10 6. 十进制数25用8421BCD 码表示为(B ) A.10 101 B.0010 0101 C.100101 D.10101 7. 常用的BCD 码有(C ) A:奇偶校验码 B:格雷码 C:8421码 D:ASCII 码 8. 已知Y A AB AB =++,下列结果中正确的是(C ) A:Y=A B:Y=B C:Y=A+B D: Y A B =+ 9. 下列说法不正确的是( D ) A:同一个逻辑函数的不同描述方法之间可相互转换 B:任何一个逻辑函数都可以化成最小项之和的标准形式 C:具有逻辑相邻性的两个最小项都可以合并为一项 D:任一逻辑函数的最简与或式形式是唯一的 10. 逻辑函数的真值表如下表所示,其最简与或式是(C )

A: ABC ABC ABC ++ B: ABC ABC ABC ++ C: BC AB + D: BC AC + 11.以下不是逻辑代数重要规则的是( D ) 。 A. 代入规则 B. 反演规则 C. 对偶规则 D. 加法规则 12.已知函数E)D (C B A F +?+=的反函数应该是( A ) 。 A. [])E (D C B A F +?+?= B. [])E D (C B A F +?+?= C. [])E (D C B A F +?+?= D. [] )E D (C B A F +?+?= 13.组合逻辑电路一般由( A )组合而成。 A 、门电路 B 、触发器 C 、计数器 D 、寄存器 14.求一个逻辑函数F 的对偶式,可将F 中的( A )。 A 、“·”换成“+”,“+”换成“·”,常数中的“0”“1”互换 B 、原变量换成反变量,反变量换成原变量 C 、变量不变 D 、常数中的“0”换成“1”,“1”换成“0” 15.逻辑函数()()()()=++++=E A D A C A B A F ( A ) 。 A. AB+AC+AD+AE B. A+BCED C. (A+BC)(A+DE) D. A+B+C+D+E 16.下列逻辑电路中,不是组合逻辑电路的有( D ) A 、译码器 B 、编码器 C 、全加器 D 、寄存器 17.逻辑表达式A+BC=( C )

北邮数字逻辑期中试题及参考答案全新

北京邮电大学 《数字电路与逻辑设计》期中考试试题 2015.4.11 班级姓名班内序号 题号一二三四五六七八总成绩 分数20 12 10 10 10 20 10 8 得分 注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。 一、(每题1分,共20分)判断(填√或×)、单项选择题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。) 1.ECL逻辑门与TTL门相比,主要优点是抗干扰能力强。(╳)2.CMOS门电路在使用时允许输入端悬空,并且悬空的输入端相当于输入逻辑“1”。( ╳ ) 3.若对4位二进制码(B 3B 2 B 1 B )进行奇校验编码,则校验位C= B 3 ⊕B 2 ⊕B 1 ⊕B ⊕1。 (√) 4.根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电平匹配不存在问题(√) 5. 根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电流驱动能力不存在问题(╳) 表1-1常用的TTL和CMOS门的典型参数

6.当i j ≠时,必有两个最小项之和+0i j m m =。(╳) 7. CMOS 门电路的静态功耗很低,但在输入信号动态转换时会有较大的电流,工作频率越高,静态功耗越大。(╳) 8. 逻辑函数的表达式是不唯一的,但其标准的最小项之和的表达式是唯一的。(√) 9.用数据分配器加上门电路可以实现任意的逻辑函数。( √ ) 10.格雷BCD 码具有单位距离特性(任意两个相邻的编码之间仅有一位不同)且是无权代码。(√) 11.关于函数F A C BCD AB C =++g ,下列说法中正确的有 B 。 A. 不存在冒险; B. 存在静态逻辑冒险,需要加冗余项ABD 和ACD 进行消除; C. 存在静态功能冒险,需要加冗余项ABD 和ACD 进行消除; D. 当输入ABCD 从 0001→0100变化时存在静态逻辑冒险。 12.逻辑函数F=A ⊕B 和G=A ⊙B 满足关系 D 。 A.F G = B.0F G += C.1F G =g D.0F G =e 13.若逻辑函数∑=)6,3,2,1(),,(m C B A F ,∑=)7,5,4,3,2,0(),,(m C B A G ,则 =?G F A 。 A.32m m + B.1 C.AB D.AB 14.若干个具有三态输出的电路输出端接到一点工作时,必须保证 B 。 A.任何时刻最多只能有一个电路处于高阻态,其余应处于工作态。 B.任何时刻最多只能有一个电路处于工作态,其余应处于高阻态。 C.任何时刻至少有一个电路处于高阻态,其余应处于工作态。 D.任何时刻至少有一个电路处于工作态,其余应处于高阻态。 15.可以用来传输连续变化的模拟信号的电路是 D 。 A. 三态输出的门电路。; B. 漏极开路的CMOS 门电路; C. ECL 门电路; D. CMOS 传输门 16.逻辑表达式[()]F AB C D E B =++?的对偶式为 B 。

数字逻辑期末复习题

一、选择题(每小题2分,共20分) 1. 八进制(273)8中,它的第三位数2 的位权为___B___。 A .(128)10 B .(64)10 C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。 A .A B F = B . C AB F += C .C A AB F += D . C B AB F += 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A . 原码 B .ASCII 码 C . 补码 D . BCD 码 4.对于如图所示波形,其反映的逻辑关系是___B_____。 A .与关系 B . 异或关系 C .同或关系 D .无法判断 5. 连续异或1985个1的结果是____B_____。 A .0 B .1 C .不确定 D .逻辑概念错误 6. 与逻辑函数D C B A F +++= 功能相等的表达式为 ___C_____。 A . D C B A F +++= B . D C B A F +++=

C . D C B A F = D .D C B A F ++= 7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。 Q 的频率为_____D_____。 . 100KHz D .50KHz 9.下列器件中,属于时序部件的是_____A_____。 A . 计数器 B . 译码器 C . 加法器 D .多路选择器 10.下图是共阴极七段LED 数码管显示译码器框图,若要显示字符“5”,则译码器输出a ~g 应为____C______。 A . 0100100 B .1100011 C . 1011011 D .0011011

数字逻辑电路期末考试卷及答案

- - 优质资料 期末考试试题(答案) 考试科目:数字逻辑电路 试卷类别:3卷考试时间:110 分钟 XXXX 学院 ______________系级班 学号 题号 一 二 三 四 总分 得分 一、选择题(每小题2分,共20分) 1. 八进制(273)8中,它的第三位数2 的位权为___B___。 A .(128)10 B .(64)10 C .(256)10 D .(8)10 2. 已知逻辑表达式C B C A AB F ++=,与它功能相等的函数表达式_____B____。 A .A B F =B . C AB F += C .C A AB F += D .C B AB F += 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A . 原码 B .ASCII 码 C . 补码 D .BCD 码 4.对于如图所示波形,其反映的逻辑关系是___B_____。 得分 评卷人 装 订 线 内 请 勿 答 题

- 优 A .与关系 B . 异或关系 C .同或关系 D .无法判断 5. 连续异或1985个1的结果是____B_____。 A .0 B .1 C .不确定 D .逻辑概念错误 6. 与逻辑函数D C B A F +++=功能相等的表达式为___C_____。 A .D C B A F +++=D C B A F +++= .D C B A F ++= 7.下列所给三态门中,能实现C=0时,F=AB ;C=1时,F 为高阻态的逻辑功能的是____A______。 8. 如图所示电路,若输入CP 脉冲的频率为100KHZ ,则输出Q 的频率为_____D_____。 A . 500KHz B .200KHz

数字逻辑电路期末考试试卷及答案

期末考试试题(答案) 一、选择题(每小题2分,共20分) 1.八进制(273)8中,它的第三位数2 的位权为___B___。 A.(128)10B.(64)10C.(256)10 D.(8)10 2. 已知逻辑表达式C B C A AB F+ + =,与它功能相等的函数表达式 _____B____。 A.AB F=B.C AB F+ = C.C A AB F+ =D.C B AB F+ = 3. 数字系统中,采用____C____可以将减法运算转化为加法运算。 A.原码B.ASCII码C.补码D.BCD码4.对于如图所示波形,其反映的逻辑关系是___B_____。 A.与关系B.异或关系C.同或关系D.无法判断 5.连续异或1985个1的结果是____B_____。 A.0B.1 C.不确定D.逻辑概念错误 6. 与逻辑函数D C B A F+ + + =功能相等的表达式为___C_____。 A.D C B A F+ + + =B.D C B A F+ + + = C.D C B A F=D.D C B A F+ + = 7.下列所给三态门中,能实现C=0时,F=AB;C=1时,F为高阻态的逻辑功能的是____A______。 B A F & ? F B A &

8. 如图所示电路,若输入CP脉冲的频率为100KHZ,则输出Q的频率为_____D_____。 A. 500KHz B.200KHz C. 100KHz D.50KHz 9.下列器件中,属于时序部件的是_____A_____。 A.计数器B.译码器C.加法器D.多路选择器 10.下图是共阴极七段LED数码管显示译码器框图,若要显示字符“5”,则译码器输出a~g应为____C______。 A. 0100100 B.1100011 C. 1011011 D.0011011 二、填空题(每小题2分,共20分) 11.TTL电路的电源是__5__V,高电平1对应的电压范围是__2.4-5____V。 12.N 个输入端的二进制译码器,共有___N2____个输出端。对于每一组输入代码,有____1____个输出端是有效电平。 13.给36个字符编码,至少需要____6______位二进制数。 14.存储12位二进制信息需要___12____个触发器。

《数字逻辑》期末考试A卷参考答案

《数字逻辑》期末考试 A 卷参考答案 、判断题:下面描述正确的打’/,错误的打‘X’(每小题1分,共10 分) 1、为了表示104个信息,需7位二进制编码[V ] 2、BCD码能表示0至15之间的任意整数[X ] 3、余3码是有权码[X ] 4、2421码是无权码[X ] 5、二值数字逻辑中变量只能取值 6、计算机主机与鼠标是并行通信 7、计算机主机与键盘是串行通信8、占空比等于脉冲宽度除于周期0和1,且表示数的大小[X ] [X ] [V ] [V ] 9、上升时间和下降时间越长,器件速度越慢[V ] 10、卡诺图可用来化简任意个变量的逻辑表达式[X ] 、写出图中电路的逻辑函数表达式。(每小题5分,共10分) 1、F=A B 2、F= AB CD 2分,共20分)

1、在图示电路中.能实现逻辑功能F = ATH 的电路是 A ° TTL 电路 (A) F = ABCD (B) F = AH ? CD - (C) F= A + B + C + D (D) F = A + B ? C + D (E) F= A BCD 4 . 己知F 二ABC + CD ■可以肯定使F = 0的情况是 _° (A) A=0, BC= 1; (B) B= 1 , C= 1 } (C) AB= 1, CD=Q. (D) BC= 1 , D= 1 5、逻辑函数A B+BCD+A C+ B C 可化简为A,B,C,D 。 (A) AB + AC + BC (B) AB + C (A4-B) (C) AB + CAB A — O ? =1 1 Q A |— I 1 F ?- & 1 Q A B L I l — (B) 悬0 ---- 空 。— A — & Bo — Co- & B A 3 ?满足如图所示电路的输岀函数F 的表达式为丄3 B 1 o — V OF

09年数字逻辑期末试卷(A卷)试题及答案

09年数字逻辑期末试卷(A卷)试题及答案

华东师范大学期末试卷(A ) 2009 — 2010 学年第 一 学期 课程名称:___数字逻辑______ 学生姓名:___________________ 学 号:___________________ 专 业:___________________ 年级/班级:__________________ 课程性质:公共必修、公共选修、专业必修、专业选修 ………………………………………………………………………………………… 一、填空题 (20分,每空2分) 1. (34.5)10 = ( (1) 11 0100.0101 )8421BCD = ( (2) 100010.1 )2 = ( (3) 2 2.8 )16 。 2. ()Y A B C CD =++的对偶式为___(4)Y ’A C B C A D ''''''=++ 。 3. 在数字系统中,要实现线与功能可选用___(5)OC/OD 门;要实现总线结构可选用___(6)传输 门。 4. 化简F (A,B,C,D )=∑m(3,5,6,7,10)+d (0,1,2,4,8)可得 (7) F =A ’+B ’D ’ 。 5. 已知某左移寄存器,现态为011001,若空位补0,则次态为 (8)110010 。 6. 二进制数(- 10110)2的反码和补码分别为 (9)101001 和 (10)101010 。

二、选择题(20分,每题2分) 1.在下列逻辑部件中.不属于组合逻辑部件的是 D 。 A.译码器 B.编码器 C.全加器 D.寄存器 2.逻辑表达式A+BC = B 。 A.A+C B.(A+B)(A+ C) C.A+B+ABC D.B+C 3.能得出X=Y的是 C A.X+Z=Y+Z B.XZ=YZ C. X+Z=Y+Z且XZ=YZ D.以上都不能 4.为将D触发器转换为T触发器,图中所示电路的虚框内应是 _ A_。 A.同或门B.异或门 C.与非 门D.或非门 5.设A1、A2、A3为三个信号,则逻辑函数 C 能检测出这三个信号中 是否含有奇数个高电平。 A.A1A2A3 B.A1+A2+A3 C.A1⊕A2⊕A3 D.A1+A2A3 6.以下说法正确的是 C A.TTL门电路和CMOS门电路的输入端都可以悬空

北京邮电大学 数字逻辑期末模拟试题8

本科试卷(八) 一、选择题(每小题2分,共30分) 1.逻辑函数F1=∑m (2,3,4,8,9,10,14,15), 它们之间的关系是________。 A . B . C . D .、互为对偶式 2. 最小项的逻辑相邻项是________。 A .ABCD B. C. D. 3. 逻辑函数F (ABC )=A ⊙C 的最小项标准式为________。 A.F=∑(0,3) B. C.F=m 0+m 2+m 5+m 7 D. F=∑(0,1,6,7) 4. 一个四输入端与非门,使其输出为0的输入变量取值组合有_______种。 A. 15 B. 8 C. 7 D. 1 5. 设计一个四位二进制码的奇偶位发生器(假定采用偶检验码),需要_______个异或门。 A .2 B. 3 C. 4 D. 5 6. 八路数据选择器如图1-1所示,该电路实现的逻辑函数是F=______。 A . B . C . D . 图1-1 7. 下列电路中,不属于时序逻辑电路的是_______。 A .计数器 B .触发器 C .寄存器 D .译码器 8. 对于JK 触发器,输入J=0,K=1,CP 脉冲作用后,触发器的次态应为_____。 A .0 B. 1 C. 保持 D. 翻转 9. Moore 型时序电路的输出_____。 A.与当前输入有关 B. 与当前状态有关 C. 与当前输入和状态都有关 D. 与当前输入和状态都无关 2F ABC ABCD ABC ABC ACD =++++12F F =12F F =12F F =1F 2F ABCD ABCD ABCD ABCD C A C A F +=AB AB +AB AB +A B ⊕A B +

(完整版)数字逻辑期末试卷(B卷)试题及答案

华东师范大学期末试卷(B) 2009 — 2010 学年第 一 学期 课程名称:___数字逻辑________ 学生姓名:___秦宽________________ 学 号:_2013041046__________________ 专 业:____软件工程_______ 年级/班级:13级软件工程 课程性质:公共必修、公共选修、专业必修、专业选修 一、填空题 (20分,每空2分) 1. (2010)D =( )B = ( )H = ( )8421BCD 答案:(111 1101 1010)B = (7DA )H = (0010 0000 0001 0000)8421BCD 2. 仓库门上装了两把暗锁,A 、B 两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。这种逻辑关系为 。 答案:与逻辑 3. 逻辑函数式F=AB+AC 的对偶式为 ,最小项表达式为∑=m F ( )。 答案:))((C A B A F D ++= ∑=m F (5,6,7) 2.逻辑函数D AC CD A C AB D C ABD ABC F ''''''+++++=的最简与或式是 。 答案:'D A + 4. 从结构上看,时序逻辑电路的基本单元是 。 答案:触发器 5. JK 触发器特征方程为 。 答案:Q K JQ ''+ 6.A/D 转换的一般步骤为:取样,保持, ,编码。 答案:量化

二、选择题 (20分,每题2分) 1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。 A) 6 B) 7 C) 8 D) 51 答案:B 2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。 A) 2 B) 4 C) 6 D) 7 答案:D 3. 为实现“线与”逻辑功能,应选用( )。 A) 与非门 B) 与门 C) 集电极开路(OC )门 D) 三态门 答案:C 4. 图1所示逻辑电路为( )。 A) “与非”门 B) “与”门 C)“或”门 D) “或非”门 图1 答案:A 5. 在下列逻辑部件中,属于组合逻辑电路的是( )。 A) 计数器 B) 数据选择器 C) 寄存器 D) 触发器 答案:B 6. 已知某触发器的时钟CP ,异步置0端为R D ,异步置1端为S D ,控制输入端V i 和输出Q 的波形如图2所示,根据波形可判断这个触发器是( )。 B C

数字逻辑北邮期末分析

1.电子电路分为模拟电子电路和数字电子电路。数值的度量采用直流电压或电流的连续值,称模拟量。 2.数字电路比模拟电路有许多优点。如:电路便于集成化、系列化生产,成本低廉,使用方便;抗干扰性强,可靠性高,精度高;处理功能强,不仅能实现数值运算,还可以实现逻辑运算和判断;可编程数字电路可容易地实现各种算法,具有很大的灵活性;数字信号更易于存储、加密、压缩、传输和再现。 3.数字量具有精度高、传输高效、易存储、易处理等优点(上升沿10%—90%) 4.自然码:有权码,每位代码都有固定权值,结构形式与二进制数完全相同,最大计数为2n-1,n为二进制数的位数 5.可靠性代码:(1) 奇偶校验码(2) 格雷码(Gray 码,又称循环码(循环码的一种)<格雷码的特点是任何相邻的两个码组中,仅有一位代码不同,抗干扰能力强,主要用在计数器中> 6.数字电路是传递和处理数字信号的电子电路。它有组合逻辑电路和时序逻辑电路两大类。 7.数字电路的优点:便于高度集成化,工作可靠性强,抗干扰能力强,保密性好等。 8.时序逻辑电路中一定包含:触发器。时序电路中必须有:时钟。从本质上讲,控制器是一种时序电路。时序逻辑电路:逻辑功能特点:任何时刻的输出不仅取决于该时刻的输入信号(输入变量)的状态,而且与电路原有的状态(原来的输出)(Qn+1 = f(Qn, input))有关。即历史状态相关性。时序逻辑电路具有记忆功能(适当的控制) 电路结构特点:由存储电路和组合逻辑电路组成。包含锁存器或触发器它的输出往往反馈到输入端,与输入变量一起决定电路的输出状态。 //时序逻辑电路的类型(都跟触发器或其组合有关)同步时序逻辑电路:所有触发器的时钟端连在一起。所有触发器在同一个时钟脉冲CP 控制下同步工作。 异步时序逻辑电路:时钟脉冲CP 只触发部分触发器,其余触发器由电路内部信号触发。因此,触发器不在同一时钟作用下同步工作。 9.一位十进制计数器至少需要4个触发器 10.锁存器、触发器和门电路是构成数字电路的基本单元。 锁存器、触发器有记忆功能,由它构成的电路在某时刻的输出不仅取决于该时刻的输入,还与电路原来状态有关。而门电路(组合电路)无记忆功能,由它构成的电路在某时刻的输出完全取决于该时刻的输入,与电路原来状态无关 11.布尔代数的三个最重要规则是代入规则,反演规则和对偶规划 12.数字量的特定是数值为离散量,运算结果也是离散量。 13.二进制系统的两个数字0和1是一个开关量,常称比特。用来表示1和0的电平称为逻辑电平。 14.自然二进制有叫有权码。循环码(又叫单位距离码):任何相邻的两个码字中,仅有一位不同。 15.二进制对十进制编码,简称BCD码。8421码(eg:1592是0001 0101 1001 0010)<当相加和大于9时加6修正,无1010~1111>余3码:在8421码的基础上加0011。优点执行十进制相加时,能正确的产生进位信号,而且会给减法运算带来方便。格雷码是使任何两个相邻的代码只有一个二进制状态不同(主要用于计数器)。格雷码是一种循环码。无权码:余 3 码和格雷码。有利于得到更好的译码波形。可靠性代码(奇偶校验码,格雷码) 16.化简的意义:使逻辑式最简,以便设计出最简的逻辑电路,从而节省元器件,优化生产工艺,降低成本和提高系统可靠性。 17.逻辑函数的描述工具:布尔代数{(布尔代数中的变量称为逻辑变量)<0和1代表两种对立的逻辑状态>};真值表(n变量,2^n种可能);逻辑图法();卡诺图法(变量数基本上少于5);波形图;硬件描述语言法。 18.正逻辑,负逻辑,三态门(逻辑1,逻辑0,高阻抗)<使能端有效时(逻辑1)输出状态取决于输入状态> 19.卡诺图

数字逻辑期末试题及答案

西 安 金 戈 技 术 学 校 2008年秋季学期期末考试数字逻辑电路试卷 注意事项 1. 考试时间:120 分钟。 2. 本卷依据2005年颁布的《技工类院校考试要求》命制。 3. 请首先按要求在试卷的规定位置填写您的姓名、准考证号和所在班级。 4. 请仔细阅读各种题目的回答要求,在规定的位置填写您的答案。 5. 不要在试卷上乱写乱画,不要在试卷上填写无关的内容。 一. 判断: 1.数字电路抗干扰能力强的原因是只传递1和0的数字信息.. ( ) 2.BCD 码就是8421BCD 码. ( ) 3.卡诺图是真值表示的另一种形式,具有唯一性. ( ) 4.二极管可组成与门电路,但不能组成或门电路. ( ) 5.三极管非门电路中的三极管主要工作在放大状态. ( ) 6.组合逻辑电路中有具有记忆功能的逻辑部件. ( ) 7.译码是编码的逆过程. ( ) 8.触发器也称为半导体存贮单元. ( ) 9.同步触发器存在空翻现象,而边沿型触发器和主从型触发器克服了空翻. 10.JK 触发器的JK 端相当KS 触发器的SR 端. ( ) 二.选择: 1.若编码器编码输出位数为4位,则最多可对( )个输入信号编码. A.4 B.6 C.16 D.32 2.16选1数据选择器其地址输入至少应有( )位. A.2 B.4 C.8 D.16 3.半加器有( ),全加器有( ) A.2个输入端,2个输出端 B.2个输入端,3个输出端 C.3个输入端,2个输出端 D.3个输入端,3个输出端 4.二极管可组成的电路( ) A.只能是与门 B.只能是或门 C.与门和或门都可以 D.非门 5.通常能实现“线与”功能的门电路是( ) A.OC 门 BTSL.门 C.TTL 与门 6.BCD 码是( ) A.二进制码 B.十进制码 C.二一十进制码 7.下列逻辑函数表示方法中,具有唯一性的是(多选)( ) A.真值表 B.逻辑表达式 C.逻辑图 D.卡诺图 8.下列选项中不属于卡诺图特点的是( ) … … ……… ……考……………生… ……… …答……………题……………不……………准……………超……………过……………此……………线…………………

2013数字逻辑期末试卷试题及答案

一、填空题 (20分,每空2分) 1. (2010)D =( )B = ( )H = ( )8421BCD 2. 仓库门上装了两把暗锁,A 、B 两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。这种逻辑关系为 。 3. 逻辑函数式F=AB+AC 的对偶式为 ,最小项表达式为∑=m F ( )。 2.逻辑函数D AC CD A C AB D C ABD ABC F ''''''+++++=的最简与或式是 。 4. 从结构上看,时序逻辑电路的基本单元是 。 5. JK 触发器特征方程为 。 二、选择题 (20分,每题2分) 1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。 A) 6 B) 7 C) 8 D) 51 2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。 A) 2 B) 4 C) 6 D) 7 4. 图1所示逻辑电路为( )。 A) “与非”门 B) “与”门 C)“或”门 D) “或非”门 图1 +U CC +U CC -U BB R R K R C R B A B C F

5. 在下列逻辑部件中,属于组合逻辑电路的是()。 A) 计数器B) 数据选择器C) 寄存器D) 触发器 6. 已知某触发器的时钟CP,异步置0端为R D,异步置1端为S D,控制输入端V i和输出Q的波形如图2所示,根据波形可判断这个触发器是()。 图2 A) 上升沿D触发器B) 下降沿D触发器 C) 下降沿T触发器D) 上升沿T触发器 7. 寄存器要存放n位二进制数码时,需要( )个触发器。 A) n B) n log C) n2D) n/2 2 8. 下面哪种不是施密特触发器的应用:( ) A) 稳定频率脉冲输出B) 波形变换C) 脉冲整形D) 脉冲鉴幅 9. 下列哪个不能用555电路构成:( ) A)施密特触发器B)单稳态触发器C)多谐振荡器D)晶体振荡器 三、简答题(15分) 1.用公式法化简逻辑函数:Y=A'BC +(A+B')C (7分)

2013《数字逻辑设计》期末考试-试题及参考答案-更新

………密………封………线………以………内………答………题………无………效…… 电子科技大学2012 -2013学年第二学期期末考试 A 卷 课程名称:_数字逻辑设计及应用__ 考试形式:闭卷考试日期: 20 13 年 07 月05 日 考试时长:_120___分钟 课程成绩构成:平时 30 %,期中 30 %,实验0 %,期末 40 % 本试卷试题由___七__部分构成,共__7___页。 题号一二三四五六七八九十合计 得分 I. Fill out your answers in the blanks (3’ X 10=30’) 1. If a 74x138 binary decoder has 110 on its inputs CBA, the active LOW output Y5 should be ( 1 or high ). 2. If the next state of the unused states are marked as “don’t-cares” when designing a finite state machine, this approach is called minimal ( cost ) approach. 3.The RCO_L of 4-bit counter 74x169 is ( 0 or low) when counting to 0000 in decreasing order. 4. To design a "001010" serial sequence generator by shift registers, the shift register should need ( 4 ) bit at least. 5. One state transition equation is Q* = JQ’+K’Q. If we use T flip-flop with enable to complete the equation,the enable input of T flip-flop should have the function EN = ( JQ’+KQ ). (参见课件Flip-flops Transforming Skills.ppt) 6. A 4-bit Binary counter can have ( 16 ) normal states at most, 4-bit Johnson counter with no self-correction can have ( 8 ) normal states, 4-bit linear feedback shift-register (LFSR) counter with self-correction can have ( 16 ) normal states. 7. If we use a ROM, whose capacity is 16 × 4 bits, to construct a 4-bit binary code to gray code converter, when the address inputs are 1001, ( 1101) will be the output. 8. When the input is 10000000 of an 8 bit DAC, the corresponding output voltage is 2V. The output voltage is

2012北邮数字逻辑期中试题-评分及答案

2012北邮数字逻辑期中试题-评分及答案

北京邮电大学 《数字电路与逻辑设计》期中考试试题 2012.3.24 班级姓名班内序号 题号一二三四五六七八九 总成 绩 分 数 20 10 10 10 10 10 10 10 10 注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。 一、(每题1分,共20分)判断(填√或×)、选择(单项选择)题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。)1.组合逻辑电路中不存在记忆单元。(√) 2.晶体管的饱和越深,其对灌电流负载的驱动能力越强,但工作速度越慢。( √ ) 3.TTL门的某输入端通过100KΩ电阻接电源端时,可认为该输入是逻辑“1”。(√) 4.为了增加驱动能力,相同输入时的相同逻辑门输出可以互连在一起使用。 2

3 ( √ ) 5.当两个或两个以上输入信号同时变化,变化前后输出相同,而在输入信号变化时可能出现输出瞬间逻辑错误,称为静态逻辑冒险。( × ) 6.正逻辑的或非门,对应负逻辑的与非门。( √ ) 7.TTL 与非门的关门电平V OFF 越接近阈值电压V T ,其噪声容限越大。( √ ) 8.当i j ≠时,必有两个最大项之积0i j M M ?=。( × ) 9. 用最简与或式表示一个函数时,其表达式可能不是唯一的。( √ ) 10.反相器的拉电流负载电阻过小时,主要对输出的高电平产生影响。( √ ) 11.逻辑项ABCD 的相邻项有: C 。 A.ABCD B.BCD A C.ABC D ? D. C A B D ? 12.判断下列两个函数式中,是否存在逻辑冒险。 B 。 1(,,)Y A B C A BC =+ 2(,,)Y A B C ABC ABC =+ A.不存在,存在 B. 不存在,不存在 C.存在,不存在 D. 存在,存在 13.通过适当连接和控制,可以实现数据双向传输的门电路是 D 。 A. 集电极开路输出的TTL 门电路; B. 互补式输出的TTL 门电路; C. ECL 门电路; D. 三态输出的门电路。 14.若某TTL 门电路的输出端最大灌电流负载能力为16mA ,最大拉电流负载能力为-12mA(流出输出端)。其输入端低电平的输入最大电流为-1mA(流出输入端),输入端高电平时的输入最大电流为0.1mA(流入输入端),该门电路的扇出系数为: A 。 A . 16 B. 120 C. 12 D. 160 15.图1.1中电路为TTL 电路。不能实现对应逻辑功能的电路有 A 。 & A A 1 ≥A A 1 =A A A B 图1.1

《数字电路与数字逻辑》期末考试试卷A卷(1)

广西科技大学2015—2016学年第 1 学期课程考核 试题 考核课程数字电路与数字逻辑( A 卷)考核班级软件141、142 学生数 80 印数 85 考核方式闭卷考核时间 120 分钟 1、 选择题(每题2分,共20分) 1. 数字9的BCD码是1001,那么它的余三码是( A ) A 1100 B 1001 C 0110 D 1111 2. 若输入变量A、B全为1时,输出F为1,其余情况下,F为0,那么F与AB的关系是( B ) A B C D 3. 二进制数1100转换成十六进制数是( C ) A 12H B 0AH C 0BH D 0CH 4. 逻辑表达式( C ) A B C D 5. 组合逻辑电路通常由( A )组合而成。 A 门电路 B 计数器 C 触发器 D 寄存 器 6. 时序逻辑电路中一定包含( C ) A 门电路 B 计数器 C 触发器 D 寄 存器 7. 有2个与非门构成的基本RS触发器,如果要触发器输出保持不变,则( ) A B C D 8. T触发器,如果T端为高电平,那么CP脉冲来的时候,输出Q应( ) A 为0 B 为1 C 保持不变 D 翻

转 9. 时序逻辑电路输出状态的改变( ) A 仅与该时刻输入信号的状态有关 B 仅与时序电路的原状 态有关 C 与时序电路的原状态无关 D 与A、B两项皆有关 10. 以下( B )不是解决组合逻辑电路中竞争冒险现象的方法。 A 增加冗余项 B 使用卡诺图化简 C 增加选通脉冲 D 改变设计方法 2、 使用卡诺图法化简以下逻辑函数(每题5分,共20分) 1. 2. 3. 4. 3、 问答题(每题10分,共40分) 1. 分析下图所示的组合逻辑电路。 1) 写出逻辑表达式。(4分) 2) 画出真值表。(3分) 3) 说明其逻辑功能。(3分) 2. 现有一个T触发器,请使用必要的门电路将其转换成一个JK触发器。 3. 现有5个D触发器连接如下,RST是清零信号,清零之后 5个触

湖大数字逻辑期末试卷(A卷)试题及答案

数字逻辑(A) 2010 — 2011 学年第一学期 课程名称:___数字逻辑________ 学生姓名:___________________ 学号:___________________ 专业:____软件工程_______ 年级/班级:__________________ 课程性质:公共必修、公共选修、专业必修、专业选修 一二三四五六七八总分阅卷人签名 一、填空题(20分,每空2分) 1. (2010)D =()B = ()H = ()8421BCD 答案:(111 1101 1010)B= (7DA)H = (0010 0000 0001 0000)8421BCD 2. 仓库门上装了两把暗锁,A、B两位保管员各管一把锁的钥匙,必须二人同时开锁才能进库。这种逻辑关系为。 答案:与逻辑 3. 逻辑函数式F=AB+AC的对偶式为,最小项表达式为 ∑ F( )。 =m 答案:) F D+ + A =∑ (C B )( A F(5,6,7) =m 2.逻辑函数D ' '+ ' + ' + =的最简与或式 ' + + CD C A AC AB D ABC F' ABD C 是。 答案:'D A+ 4. 从结构上看,时序逻辑电路的基本单元是。 答案:触发器 5. JK触发器特征方程为。 答案:Q '+ K JQ' 6.A/D转换的一般步骤为:取样,保持,,编码。 答案:量化 二、选择题(20分,每题2分)

1. 计算机键盘上有101个键,若用二进制代码进行编码,至少应为( )位。 A) 6 B) 7 C) 8 D) 51 答案:B 2. 在函数F=AB+CD 的真值表中,F=1的状态有( )个。 A) 2 B) 4 C) 6 D) 7 答案:D 3. 为实现“线与”逻辑功能,应选用( )。 A) 与非门 B) 与门 C) 集电极开路(OC )门 D) 三态门 答案:C 4. 图1所示逻辑电路为( )。 A) “与非”门 B) “与”门 C)“或”门 D) “或非”门 图1 答案:A 5. 在下列逻辑部件中,属于组合逻辑电路的是( )。 A) 计数器 B) 数据选择器 C) 寄存器 D) 触发器 答案:B 6. 已知某触发器的时钟CP ,异步置0端为R D ,异步置1端为S D ,控制输入端V i 和输出Q 的波形如图2所示,根据波形可判断这个触发器是( )。 +U CC +U CC -U BB R R K R C R B A B C F

北邮数字逻辑期中试题与参考答案

邮电大学 《数字电路与逻辑设计》期中考试试题 2015.4.11 班级班序号 注意:所有答案(包括选择题和计算题)一律写在试卷纸上,如果卷面位置不够,请写在试卷的背后,否则不计成绩。 一、(每题1分,共20分)判断(填√或×)、单项选择题 (请先在本试卷上答题之后,将全部答案汇总到本题末尾的表格中。)1.ECL逻辑门与TTL门相比,主要优点是抗干扰能力强。(╳)2.CMOS门电路在使用时允许输入端悬空,并且悬空的输入端相当于输入逻辑“1”。( ╳) 3.若对4位二进制码(B3B2B1B0)进行奇校验编码,则校验位C= B3⊕B2⊕B1⊕B0⊕1。(√) 4.根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电平匹配不存在问题(√) 5. 根据表1-1,用CMOS4000系列的逻辑门驱动TTL74系列的逻辑门,驱动门与负载门之间的电流驱动能力不存在问题(╳) 表1-1常用的TTL和CMOS门的典型参数

6.当i j ≠时,必有两个最小项之和+0 m m=。(╳) i j 7. CMOS门电路的静态功耗很低,但在输入信号动态转换时会有较大的电流,工作频率越高,静态功耗越大。(╳) 8. 逻辑函数的表达式是不唯一的,但其标准的最小项之和的表达式是唯一的。(√) 9.用数据分配器加上门电路可以实现任意的逻辑函数。(√) 10.格雷BCD码具有单位距离特性(任意两个相邻的编码之间仅有一位不同)且是无权代码。(√) =++g,下列说法中正确的有 B 。11.关于函数F A C BCD AB C A. 不存在冒险; B. 存在静态逻辑冒险,需要加冗余项ABD和ACD进行消除; C. 存在静态功能冒险,需要加冗余项ABD和ACD进行消除; D. 当输入ABCD从0001→0100变化时存在静态逻辑冒险。 12.逻辑函数F=A⊕B和G=A⊙B满足关系D。