有限状态机分析解析

大作业:有限状态机

姓名:班级:学号:

一、实验目的

有限状态机,实现书上的蚂蚁实例

二、实验仪器

Pc vc6.0

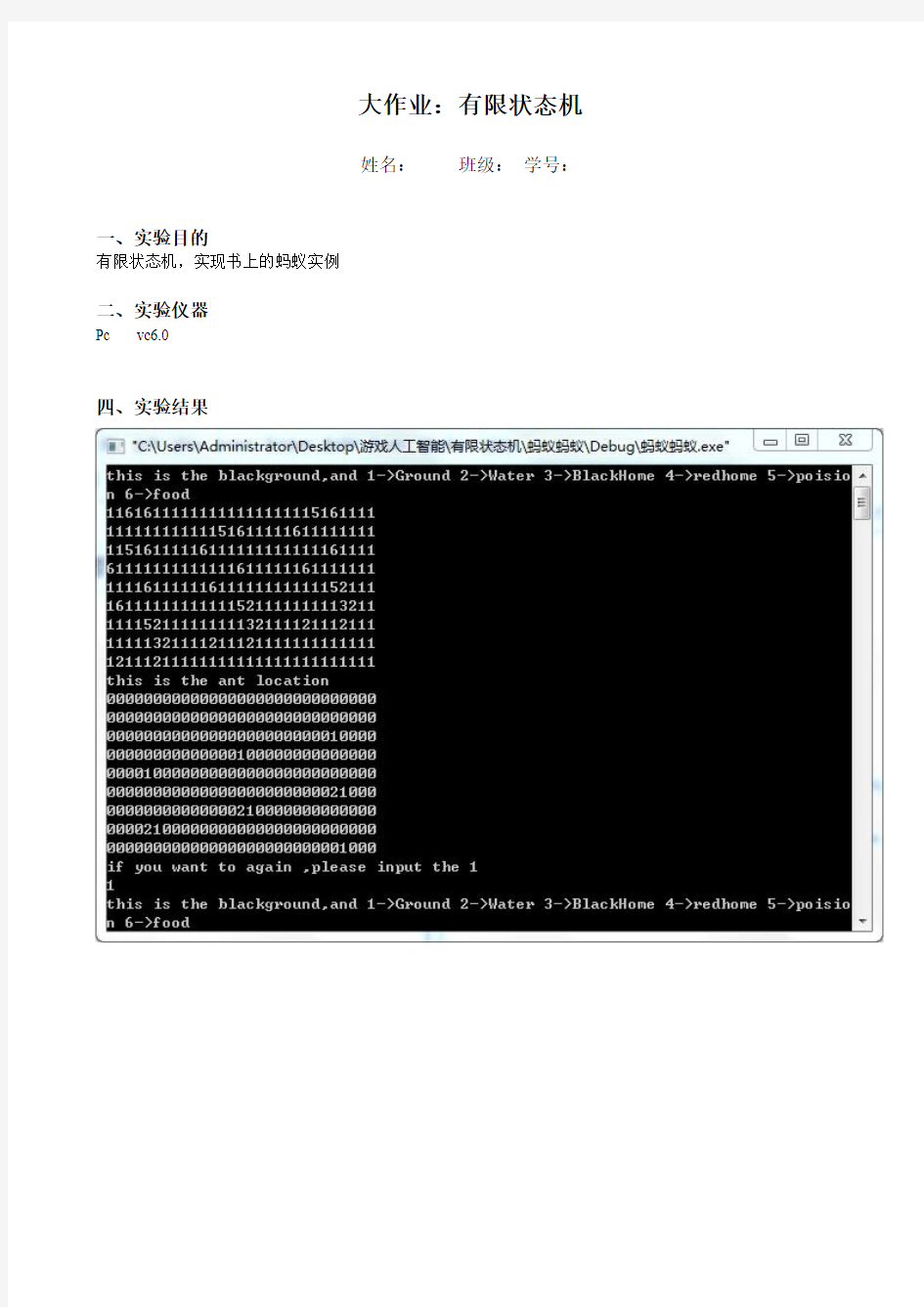

四、实验结果

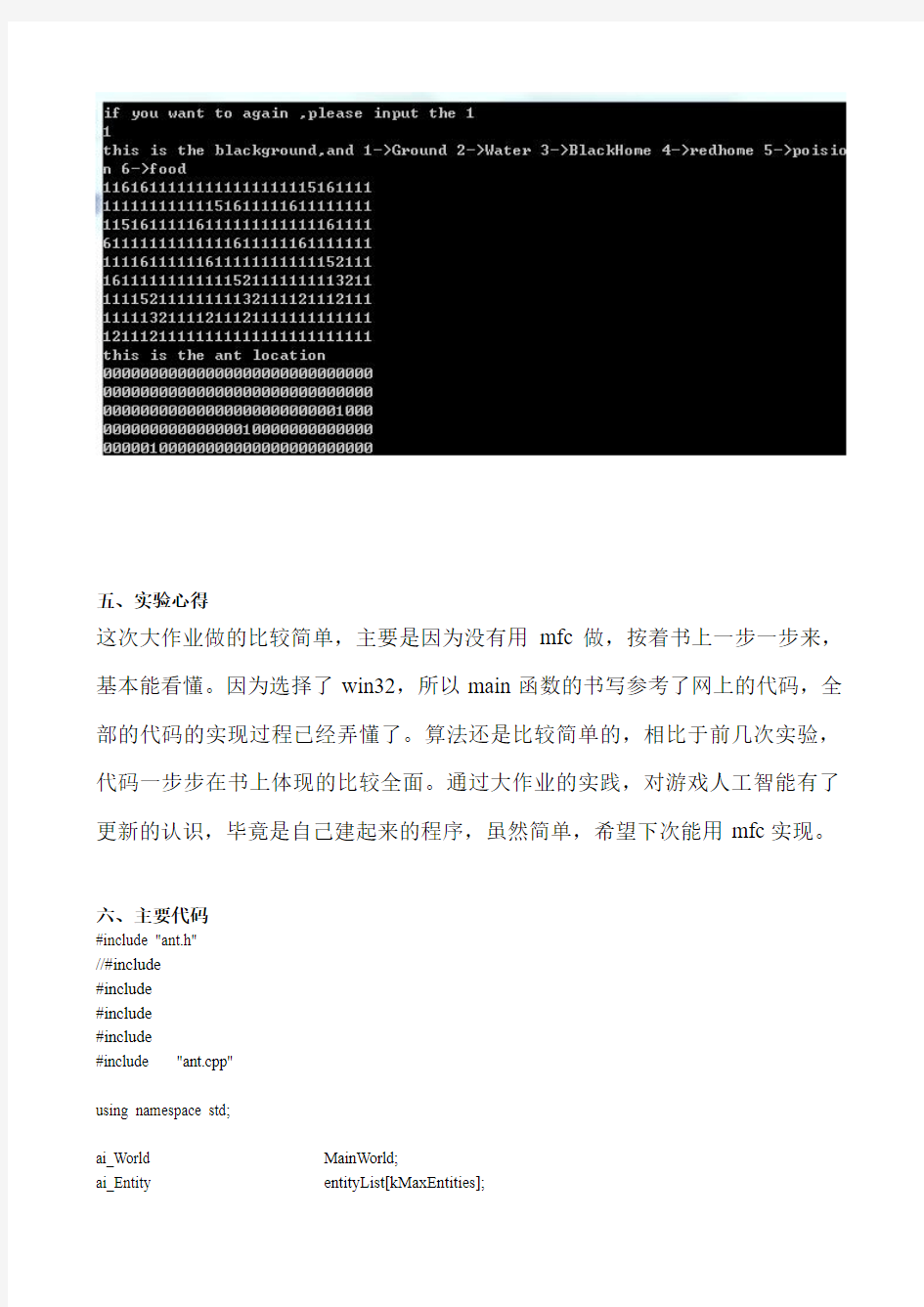

五、实验心得

这次大作业做的比较简单,主要是因为没有用mfc做,按着书上一步一步来,基本能看懂。因为选择了win32,所以main函数的书写参考了网上的代码,全部的代码的实现过程已经弄懂了。算法还是比较简单的,相比于前几次实验,代码一步步在书上体现的比较全面。通过大作业的实践,对游戏人工智能有了更新的认识,毕竟是自己建起来的程序,虽然简单,希望下次能用mfc实现。

六、主要代码

#include "ant.h"

//#include

#include

#include

#include

#include "ant.cpp"

using namespace std;

ai_World MainWorld;

int terrainBackup[kMaxRows][kMaxCols]; int terrain[kMaxRows][kMaxCols];

ai_Entity::ai_Entity()

{

int i;

for (i=0;i { entityList[i].row=0; entityList[i].col=0; entityList[i].type=0; entityList[i].state=0; } /* for (i=0;i { entityList[i].New(kRedAnt,) } */ entityList[0].New(kRedAnt,kForage,5,5); entityList[1].New(kRedAnt,kForage,8,5); entityList[2].New(kBlackAnt,kForage,5,36); entityList[3].New(kBlackAnt,kForage,8,36); } // ----------------------------------------------------------------- // ai_Entity::~ai_Entity() // ----------------------------------------------------------------- // { } void ai_Entity::Forage(void) // ----------------------------------------------------------------- // { int rowMove; int colMove; int newRow; int newCol; int foodRow; int foodCol; int poisonRow; int poisonCol; rowMove=rand()%3-1; colMove=rand()%3-1; newRow=row+rowMove; newCol=col+colMove; if (newRow<1) return; if (newCol<1) return; if (newRow>=kMaxRows-1) return; if (newCol>=kMaxCols-1) return; if ((terrain[newRow][newCol]==kGround) || (terrain[newRow][newCol]==kWater)) { row=newRow; col=newCol; } if (terrain[newRow][newCol]==kFood) { row=newRow; col=newCol; terrain[row][col]=kGround; state=kGoHome; do { /////////////////////please makesure about the begin and the end////////// foodRow=rand()%(kMaxRows-3)+1; foodCol=rand()%(kMaxCols-3)+1; } while (terrain[foodRow][foodCol]!=kGround); terrain[foodRow][foodCol]=kFood; } if (terrain[newRow][newCol]==kPoison) { row=newRow; col=newCol; terrain[row][col]=kGround; state=kDead; do { poisonRow=rand()%(kMaxRows-3)+1; poisonCol=rand()%(kMaxCols-3)+1; } while (terrain[poisonRow][poisonCol]!=kGround); terrain[poisonRow][poisonCol]=kPoison; } } // ----------------------------------------------------------------- // void ai_Entity::Dead(void) // ----------------------------------------------------------------- // { type=0; row=0; col=0; state=0; } // ----------------------------------------------------------------- // void ai_Entity::Thirsty(void) // ----------------------------------------------------------------- // { int rowMove; int colMove; int newRow; int newCol; int foodRow; int foodCol; int poisonRow; int poisonCol; rowMove=rand()%3-1; colMove=rand()%3-1; newRow=row+rowMove; if (newRow<1) return; if (newCol<1) return; if (newRow>=kMaxRows-1) return; if (newCol>=kMaxCols-1) return; if ((terrain[newRow][newCol]==kGround) || (terrain[newRow][newCol]==kFood)) { row=newRow; col=newCol; } if (terrain[newRow][newCol]==kWater) { row=newRow; col=newCol; terrain[row][col]=kGround; state=kForage; do { foodRow=rand()%(kMaxRows-3)+1;; foodCol=rand()%(kMaxCols-3)+1; } while (terrain[foodRow][foodCol]!=kGround); terrain[foodRow][foodCol]=kWater; } if (terrain[newRow][newCol]==kPoison) { row=newRow; col=newCol; terrain[row][col]=kGround; state=kDead; do { poisonRow=rand()%(kMaxRows-3)+1; poisonCol=rand()%(kMaxCols-3)+1; } while (terrain[poisonRow][poisonCol]!=kGround); terrain[poisonRow][poisonCol]=kPoison; } } // ----------------------------------------------------------------- // void ai_Entity::GoHome(void) // ----------------------------------------------------------------- // int rowMove; int colMove; int newRow; int newCol; int homeRow; int homeCol; int i; int poisonRow; int poisonCol; if (type==kRedAnt) { homeRow=kRedHomeRow; homeCol=kRedHomeCol; } else { homeRow=kBlackHomeRow; homeCol=kBlackHomeCol; } if (row rowMove=1; else if (row>homeRow) rowMove=-1; else rowMove=0; if (col colMove=1; else if (col>homeCol) colMove=-1; else colMove=0; newRow=row+rowMove; newCol=col+colMove; if (newRow<1) return; if (newCol<1) return; if (newRow>=kMaxRows-1) return; if (newCol>=kMaxCols-1) return; if (terrain[newRow][newCol]!=kPoison) { row=newRow; col=newCol; } else { row=newRow; col=newCol; terrain[row][col]=kGround; state=kDead; do { poisonRow=rand()%(kMaxRows-3)+1; poisonCol=rand()%(kMaxCols-3)+1; } while (terrain[poisonRow][poisonCol]!=kGround); terrain[poisonRow][poisonCol]=kPoison; } if ((newRow==homeRow) && (newCol==homeCol)) { row=newRow; col=newCol; state=kThirsty; for (i=0;i if (entityList[i].type==0) { entityList[i].row=homeRow; entityList[i].col=homeCol; entityList[i].type=type; entityList[i].state=kForage; break; } } } // ----------------------------------------------------------------- // // ----------------------------------------------------------------- // void ai_Entity::New(int theType, int theState, int theRow, int theCol) // ----------------------------------------------------------------- // { type=theType; row=theRow; col=theCol; state=theState; } // ----------------------------------------------------------------- // ai_World::ai_World() // ----------------------------------------------------------------- // { int i; int j; for (i=0;i for (j=0;j { terrain[i][j]=kGround; } terrain[kRedHomeRow][kRedHomeCol]=kRedHome; terrain[kBlackHomeRow][kBlackHomeCol]=kBlackHome; for (i=0;i terrain[rand()%(kMaxRows-3)+1][rand()%(kMaxCols-3)+1]=kWater; for (i=0;i terrain[rand()%(kMaxRows-3)+1][rand()%(kMaxCols-3)+1]=kPoison; for (i=0;i terrain[rand()%(kMaxRows-3)+1][rand()%(kMaxCols-3)+1]=kFood; //for (i=0;i // for (j=0;j // terrainBackup[i][j]=terrain[i][j]; } // ----------------------------------------------------------------- // ai_World::~ai_World() // ----------------------------------------------------------------- // { // ----------------------------------------------------------------- // void ai_World::UpdateWorld(void) // ----------------------------------------------------------------- // { int i; for (i=0;i { switch (entityList[i].state) { case kForage: entityList[i].Forage(); break; case kGoHome: entityList[i].GoHome(); break; case kThirsty: entityList[i].Thirsty(); break; case kDead: entityList[i].Dead(); break; } } } int main() { int again; do { int row,col; cout<<"this is the blackground,and 1->Ground 2->Water 3->BlackHome 4->redhome 5->poision 6->food"< for(int i=1;i { for(int j=1;j {cout< cout< } cout<<"this is the ant location "< for(int i=0;i { if(entityList[i].state!=kDead) row=entityList[i].row; col=entityList[i].col; terrain2[row][col]++; } for(int f=1;f { for(int j=1;j {cout< cout< } cout<<"if you want to again ,please input the 1"< cin>>again; MainWorld.UpdateWorld(); } while(again==1); } (19)中华人民共和国国家知识产权局 (12)发明专利申请 (10)申请公布号 (43)申请公布日 (21)申请号 201910201771.X (22)申请日 2019.03.18 (71)申请人 信联科技(南京)有限公司 地址 210000 江苏省南京市江宁经济技术 开发区东吉大道1号 (72)发明人 郭涛 李明柱 叶青 (51)Int.Cl. G06F 11/36(2006.01) H04L 12/26(2006.01) (54)发明名称 一种基于协议状态机的模糊测试脚本及测 试引擎 (57)摘要 本发明公开了一种基于协议状态机的模糊 测试脚本及测试引擎,能够实现快速定义状态机 模型,并且测试平台能够自动识别状态机模型生 成状态引导脚本, 在状态机测试模式下,测试引擎首先执行状态引导脚本,将被测设备引导至测 试前的正确状态后开始正式测试流程,状态引导 脚本与主体测试脚本结构、语法一致,新增xml节 点用于定义状态机模型,状态机模型包含状态定 义和状态迁移Action,新增数据库表用于状态定 义和管理状态迁移Action集,状态机模型引用状 态定义表, 便于简化建立状态模型的过程。权利要求书1页 说明书6页 附图1页CN 110532162 A 2019.12.03 C N 110532162 A 权 利 要 求 书1/1页CN 110532162 A 1.一种基于协议状态机的模糊测试脚本及测试引擎,其特征在于,包括以下模块, 状态机模型定义,所述状态机模型定义包括状态机模型定义元素、状态定义表和引用状态定义表; 所述状态机模型定义元素包括 1.#include 11. parent(char* expr); 12.virtual parent* transition() {} 13.}; 14. 15.parent::parent(char* expr) 16.{ 17. expression = new char[strlen(expr)]; 18. strcpy(expression,expr); 19. end_state = 0; 20. doom_state = 0; 21. index = 0; 22.} 23. 24.struct state1:public parent 25.{ 26. parent *ptr2,*ptr3,*ptr4,*ptr5; 27. state1():parent(expression) {} 28. parent* transition(); 29.}; 30. 31.struct state2:public parent 32.{ 33. parent *ptr2; 34. state2():parent(expression) {} 35. parent* transition(); 36.}; 37. 38.struct state3:public parent 39.{ 40. parent *ptr3,*ptr4; 41. state3():parent(expression) {} 42. parent* transition(); 43.}; 44. 45.struct state4:public parent 46.{ 47. parent *ptr4; 48. state4():parent(expression) {} 49. parent* transition(); 50.}; 51. 52.struct state5:public parent 53.{ 54. parent *ptr2,*ptr4,*ptr5; 状态机思路在单片机程序设计中的应用 状态机的概念 状态机是软件编程中的一个重要概念。比这个概念更重要的是对它的灵活应用。在一个思路清晰而且高效的程序中,必然有状态机的身影浮现。 比如说一个按键命令解析程序,就可以被看做状态机:本来在A状态下,触发一个按键后切换到了B状态;再触发另一个键后切换到C状态,或者返回到A状态。这就是最简单的按键状态机例子。实际的按键解析程序会比这更复杂些,但这不影响我们对状态机的认识。 进一步看,击键动作本身也可以看做一个状态机。一个细小的击键动作包含了:释放、抖动、闭合、抖动和重新释放等状态。 同样,一个串行通信的时序(不管它是遵循何种协议,标准串口也好、I2C也好;也不管它是有线的、还是红外的、无线的)也都可以看做由一系列有限的状态构成。 显示扫描程序也是状态机;通信命令解析程序也是状态机;甚至连继电器的吸合/释放控制、发光管(LED)的亮/灭控制又何尝不是个状态机。 当我们打开思路,把状态机作为一种思想导入到程序中去时,就会找到解决问题的一条有效的捷径。有时候用状态机的思维去思考程序该干什么,比用控制流程的思维去思考,可能会更有效。这样一来状态机便有了更实际的功用。 程序其实就是状态机。 也许你还不理解上面这句话。请想想看,计算机的大厦不就是建立在“0”和“1”两个基本状态的地基之上么? 状态机的要素 状态机可归纳为4个要素,即现态、条件、动作、次态。这样的归纳,主要是出于对状态机的内在因果关系的考虑。“现态”和“条件”是因,“动作”和“次态”是果。详解如下: ①现态:是指当前所处的状态。 ②条件:又称为“事件”。当一个条件被满足,将会触发一个动作,或者执行一次状态的迁移。 ③动作:条件满足后执行的动作。动作执行完毕后,可以迁移到新的状态,也可以仍旧保持原状态。动作不是必需的,当条件满足后,也可以不执行任何动作,直接迁移到新状态。 ④次态:条件满足后要迁往的新状态。“次态”是相对于“现态”而言的,“次态”一旦被激活,就转变成新的“现态”了。 实验四有限状态机设计(2学时) 实验内容一: 状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。 根据时序电路输出信号的特点可将时序电路划为Mealy 型和Moore 型两种。Moore型电路中,输出信号仅仅取决于存储电路的状态。Mealy型电路中,输出信号不仅取决于存储电路的状态,而且还取决于输入变量。图1是某Mealy型电路的状态转换图,图中圆圈内的S0、S1等代表电路的状态,状态转换箭头旁斜杠“/”上边的数字代表输入信号,斜杠“/”下边的数字代表输出信号。假设电路的当前状态为S0,当输入信号为0时,电路的下一个状态仍为S0,输出信号为0;当输入信号为1时,电路的下一个状态为S1,输出为1。 图1 Mealy状态机 下面的程序中使用两个进程来描述该状态机。第一个进程负责状态转化,在CP上升沿到达时,当前状态(PresetState)向下一个状态(NextState)的转换;第二个进程负责检测输入信号(DIN)和当前状态(PresetState)的值,并由CASE-WHEN 语句决定输出信号(OP)和下一个状态值(NextState)的值。请补充下图中虚线“…”部分省略掉的程序,然后对完整程序进行编译,并用Tools->Netlist Views->State Machine Viewer和RTL Viewer工具查看该状态机的状态图和RTL顶层图。 … … 实验内容二: 论文《基于VHDL的一个简单Mealy状态机》中设计了一个Mealy状态机用来检测数据流“1101010”,用以验证状态机在数据检测上的应用。请在读懂文中程序的基础上,在Quartus Ⅱ软件中通过编译仿真得到状态图和波形图,仿真中输入波形的设置应能体现该状态机的用途。 实验报告: 本次实验占用两个学时,请于12周周四(5月12日)上课时交实验报告。对于实验内容一,报告的内容应重在程序的完善上,对于实验内容二,报告的内容应重在对论文中源程序的分析和理解,以及仿真的波形图上。 第四章程控数字交换系统的软件 4.1.1 程控交换软件的基本特点 程控交换软件的基本特点是:实时性强、具有并发性、适应性强、可靠性和可维护性要求高。 一、实时性强。 2、在正常的情况下,实时性要求最为严格的是信号接受及信号处理程序。(微秒级) 3、相对而言,对时间要求最不严格的是运行管理功能。(秒级) 二、并发性和多道程序运行 1、并发性就是在同一时间内执行多道程序。 2、采用多道程序运行,可以使处理机在一段时间内同时保持若干进程处于激活状态 3、不同用户启动的呼叫处理进程实例可使用同一个程序代码,各进程实例的差别仅在于它们所处理的数据不同。 4、多个进程实例共用一个程序代码。 三、可靠性要求高 1、可靠性指标是99.98%的正确呼叫处理及40年内系统中断运行时间不超过两小时. 2、提高可靠性的措施有:(1)、对关键设备(如中央处理机、交换网络)采用冗余配置;(2)、采用各种措施及时发现已出现的错误,在交换机软、硬件出现故障时,迅速确定故障性质及其所在,如为硬件故障,则隔离故障部件,调用备用设备重新组成可工作的硬件系统,如为软件故障,则采用程序段的重新执行或再启动,予以恢复。 四、能方便地适应交换机的各种条件 1、为了使交换机能适应不同交换局对交换机的具体要求,在交换机软件的设计中普遍采用参数化技术,使描述处理逻辑大程序部分与给予处理参量的数据部分分离。 2、可用局数据和用户数据来适应不同的局条件。 五、软件的可维护性要求高 采用模块化、结构化设计方法,采用数据驱动程序结构,在编程时尽量采用有意义的标识符常数,建立完备、清晰的文档资料,把易随硬件更新、扩充而变化的软件部分相分离,采用虚拟机层次结构等,都有助于提高软件的可维护性。 4.1.2 程控设计的基本技术 交换机软件的设计中,普遍采用了自顶向下、模块化、层次化、参数化、数据驱动程序、有限状态模型等基本设计技术和概念。 一、自顶向下设计和模块化。 1、系统---子系统----功能块----功能模块 2、自顶向下设计的一个重要特征是对分解中的每一级而言,低一级的设计细节是“隐藏的”,只需确定各模块间的数据接口。 3、一个好的模块设计,应使得模块内部的关联性要强,模块间的关连性要弱,保证各模块的独立性。 二、层次结构和虚拟机概念 1、层次结构中,各层之间只有单向依赖关系。 2、一个硬件模块、被一层或多层软件包围,这些硬件和软件共同组成一个虚拟机。 3、软件层次越多,则虚拟机显示的功能就越强。 三、参数化 1、参数化技术就是在编制程序时对于程序中要用到的半固定数据(如描述交换机容量、硬件配置、路由组织、中继信令方式等方面的数据)暂不赋值,而是用参数来代替它们,仅在为每一台交换机安装时,根据交换局的要求再来确定这些参数的具体数值。 2、一般将这些参数的具体数值称为局数据和用户数据。 四、数据驱动程序 1、数据驱动程序,就是根据一些参数查表来决定需要启动的程序。 详解Qt中的状态机机制(一) ***************************************************************************** 欢迎访问我的博客:https://www.360docs.net/doc/f45323873.html,/u010977122/article/details/52959098 **************************************************************************** 状态机,简写为FSM(Finite State Machine),状态机由状态寄存器和组合逻辑电路构成,能够根据控制信号按照预先设定的状态进行状态转移,是协调相关信号动作、完成特定操作的控制中心。 在GUI开发的时候,界面复杂的逻辑往往令人抓狂,逻辑都不清晰,代码写起来更加费劲。用户界面设计中采用状态驱动,就可以使得GUI 的逻辑更加清晰。根据当前状态的不同,显示不同的界面。程序界面可以被看作显示对应不同场景,或者是通过改变外观响应用户的交互。通常情况下,界面中很多个组件的改变是并发进行的,这样的界面可以看作从一个状态改变到另外一个状态。 今天我们来看看qt中的状态机框架,qt把它作为QtCore中的一个模块,也足见其重要性: Qt状态机框架提供了一些类来创建执行状态图,状态图为一个系统如何对外界激励进行反应提供了一个图形化模型,该模型是通过定义一些系统可能进入的状态以及系统怎样从一个状态切换到另一个状态来实现的。事件驱动的系统的一个关键特性就是它的行为不总是仅仅依赖 于前一个或者当前的事件,而且也依赖于将要执行的事件。通过使用状态图,这些信息会非常容易进行表达。状态机框架提供了一套API以及一种执行模型,可以有效地将状态图的元素和语义嵌入到Qt应用程序中。该框架与Qt的元对象系统结合紧密:例如,不同状态之间的转化可由信号触发,信号驱动,且状态可配置用于QObject的属性和方法。 在进入今天的主题之前,我们先来了解三个概念: 状态(State):是静态的东西,对一系列对象属性的一组静态描述和配置。 过渡(Transition):是一段时间或者空间的描述,状态之间切换的整个过程,或者描述的是不同属性值之间变化的一个过程。 动画(Animation):是动态的一个东西,可以看作是过渡的执行者,通过在属性值上应用动画类型来创建。动画类型会对属性值进行插值,从而创建出平滑的过渡效果。要创建动画,需要为某个属性使用恰当的动画类型;应用的动画也依赖于需要实现的行为类型。 深入分析比较八个信息安全模型 (1)状态机模型: 无论处于什么样的状态,系统始终是安全的,一旦有不安全的事件发生,系统应该会保护自己,而不是是自己变得容易受到攻击。 (2)Bell-LaPadula模型: 多级安全策略的算术模型,用于定于安全状态机的概念、访问模式以及访问规则。主要用于防止未经授权的方式访问到保密信息。 系统中的用户具有不同的访问级(clearance),而且系统处理的数据也有不同的类别(classification)。信息分类决定了应该使用的处理步骤。这些分类合起来构成格(lattice)。BLP是一种状态机模型,模型中用到主体、客体、访问操作(读、写和读/写)以及安全等级。也是一种信息流安全模型,BLP的规则,Simplesecurityrule,一个位于给定安全等级内的主体不能读取位于较高安全等级内的数据。(-propertyrule)为不能往下写。Strongstarpropertyrule,一个主体只能在同一安全登记内读写。 图1-1 Bell-Lapodupa安全模型解析图 基本安全定理,如果一个系统初始处于一个安全状态,而且所有的状态转换都是安全的,那么不管输入是什么,每个后续状态都是安全的。 不足之处:只能处理机密性问题,不能解决访问控制的管理问题,因为没有修改访问权限的机制;这个模型不能防止或者解决隐蔽通道问题;不能解决文件共享问题。 (3)Biba模型: 状态机模型,使用规则为,不能向上写:一个主体不能把数据写入位于较高完整性级别的客体。不能向下读:一个主体不能从较低的完整性级别读取数据。主要用于商业活动中的信息完整性问题。 图1-2 Biba安全模型解析图 (4)Clark-Wilson模型: 主要用于防止授权用户不会在商业应用内对数据进行未经授权的修改,欺骗和错误来保护信息的完整性。在该模型中,用户不能直接访问和操纵客体,而是必须通过一个代理程序来访问客体。从而保护了客体的完整性。使用职责分割来避免授权用户对数据执行未经授权的修改,再次保护数据的完整性。在这个模型中还需要使用审计功能来跟踪系统外部进入系统的信息。完整性的目标,防止未授权的用户进行修改,防止授权用户进行不正确的修改,维护内部和外部的一致性。Biba只能够确认第一个目标。 (5)信息流模型: Bell-LaPadula模型所关注的是能够从高安全级别流到低安全级别的信息。Biba模型关注的是从高完整性级别流到低完整性级别的信息。都使用了信息流模型,信息流模型能够处理任何类型的信息流,而不仅是流的方向。 (6)非干涉模型: 模型自身不关注数据流,而是关注主体对系统的状态有什么样的了解,以避免较高安全等级内的一个实体所引发的一种活动,被低等级的实体感觉到。 有限状态机设计 实验报告 一.实验题目 有机状态机设计 二.实验目的 掌握有机状态机设计的基本方法。 三.实验远离 状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。 四.实验内容 实验内容一: 状态机是指用输入信号和电路状态(状态变量)的逻辑函数去描述时序逻辑电路功能的方法,也叫时序机。有限状态机是指在设计电路中加入一定的限制条件,一般用来实现数字系统设计中的控制部分。 根据时序电路输出信号的特点可将时序电路划为Mealy 型和Moore 型两种。Moore型电路中,输出信号仅仅取决于存储电路的状态。Mealy型电路中,输出信号不仅取决于存储电路的状态,而且还取决于输入变量。图1是某Mealy型电路的状态转换图,图中圆圈内的S0、S1等代表电路的状态,状态转换箭头旁斜杠“/”上边的数字代表输入信号,斜杠“/”下边的数字代表输出信号。假设电路的当前状态为S0,当输入信号为0时,电路的下一个状态仍为S0,输出信号为0;当输入信号为1时,电路的下一个状态为S1,输出为1。 图1 Mealy状态机 下面的程序中使用两个进程来描述该状态机。第一个进程负责状态转化,在CP上升沿到达时,当前状态(PresetState)向下一个状态(NextState)的转换;第二个进程负责检测输入信号(DIN)和当前状态(PresetState)的值,并由CASE-WHEN 语句决定输出信号(OP)和下一个状态值(NextState)的值。请补充下图中虚线“…”部分省略掉的程序,然后对完整程序进行编译,并用Tools->Netlist Views->State Machine Viewer和RTL Viewer工具查看该状态机的状态转移图和RTL原理图。 1、ISE的安装 现以ISE 5.2i为例介绍Xilinx ISE Series的安装过程。 1)系统配置要求 ISE 5.2i推荐的系统配置与设计时选用的芯片有关。因为在综合与实现过程中运算量非常大,所以对系统配置要求很高。为了提高综合、仿真、实现过程的速度,对于计算机的CPU的主频、主板和硬盘的工作速度,尤其是内存大小配置都有非常高的要求。在ISE 5.2i支持的所有Xilinx的FPGA/CPLD中,要求最低的Spartan II和XC9500/XL/XV等系列需要的内存和虚拟内存推荐值均达到128MB,而对于Virtex-II XC2V8000来说,需要的内存和虚拟内存推荐值均高达3GB。 2)ISE 5.2i的安装 以中文版Windows XP操作系统为例加以说明。 (1)启动Windows XP,插入ISE5.2i安装光盘,自动或选择执行Install.exe,安装界面如图4.25所示。 图4.25 ISE5.2i安装界面 (2)单击此时安装界面上的操作选择“下一步”直到出现图示对话框,输入有效的Registration ID。之后单击“下一步”选择安装路径;再之后点击“下一步”,会弹出图4.26的对话框,可以选择器件模型。 图4.26 器件模型选择对话框 (3)点击“下一步”,如图4.27所示,可以选择器件种类。 图4.27 器件种类选择对话框 通过以上步骤后,可根据具体情况来选择,继续“下一步”即可完成安装。 安装完成后,环境变量应作如下描述: 若操作系统是Windows NT/2000/XP,选择开始->控制面板->系统->选项->系统->高级->环境变量,在环境变量中加入: 变量名:Xilinx 变量值:C:Xilinx(即安装路径) 具体设置如图4.28所示。 有限状态机(Finite State Machine ) 1、有限状态机的基本概念 有限状态机是指输出取决于过去输入部分和当前输入部分的时序逻辑电路。在数字电路系统中,有限状态机时一种十分重要的时序逻辑电路模块,它对数字系统的设计具有十分重要的作用。有限状态机一般用来描述数字数字系统的控制单元,是许多数字系统的核心部件。有限状态机由组合逻辑和寄存器逻辑组成。其中,寄存器逻辑的功能是存储有限状态机的内部状态;而组合逻辑有可以分为次态逻辑和输出逻辑两部分,次态逻辑的功能是确定有限状态机的下一个状态,输出逻辑的功能是确定有限状态机的输出。 在实际的应用中,根据有限状态机是否使用输入信号,设计人员经常将其分为Moore型有限状态机和Mealy型有限状态机两种类型。 ⑴Moore型有限状态机其输出信号仅与当前状态有关,即可以把Moore型有限状态的输出看成是当前状态的函数。其结构框图如图1. 图1 Moore型有限状态机的结构 ⑵Mealy型有限状态机其输出信号不仅与当前状态有关,而且还与所有的输入信号有关,即可以把Mealy型有限状态机的输出看成是当前状态和所有输入信号的函数。其结构框图如图2. 图2 Mealy型有限状态机的结构 这两种有限状态机的主要区别在于:Moore型有限状态机仅与当前状态有关,而与输入信号无关。Mealy型有限状态机不但与当前状态有关,还与输入信号有关。 2、为什么要使用有限状态机 ? 有限状态机克服了纯硬件数字系统顺序方式控制不灵活的缺点。 ? 状态机的结构模式相对简单。 ? 状态机容易构成性能良好的同步时序逻辑模块。 ? 状态机的VHDL表述丰富多样。 ? 在高速运算和控制方面,状态机更有其巨大的优势。 ? 就可靠性而言,状态机的优势也是十分明显的。 3、描述有限状态机应该包含的内容 ⑴至少包含一个状态信号,用来指定状态机的状态。 ⑵时钟信号,为有限状态机的状态转换提供时钟信号。 ⑶状态转移指定,用于指定有限状态机的状态之间转换的逻辑关系。 ⑷输出指定,用来指明有限状态机两状态之间转换的结果。 ⑸复位信号,用于有限状态机从任意状态到复位状态的转换。 4、有限状态机的描述方法 一般描述有限状态机应遵循一定的语法规则: 状态机的状态:用枚举类型数据进行定义。 状态机的次态逻辑、输出逻辑和状态寄存器等一般用并行信号赋值语句、IF语句或CASE 语句等语句进行描述。 有限状态机的各种描述风格 描述风格功能划分进程数 A 1、次态逻辑、状态寄存器、输出逻辑1 状态机思路在单片机程序设计中的应用 1,状态机的概念: 状态机是软件编程中的一个重要概念。比这个概念更重要的是对它的灵活应用。在一个思路清晰而且高效的程序中,必然有状态机的身影浮现。 比如说一个按键命令解析程序,就可被看做状态机:本来在A状态下,触发一个按键后切换到了B状态;再触发另一个键后切换到C状态,或者返回到A状态。 最简按键状态机例。实际按键解析程序比这更复杂,但不影响我们对状态机的认识。进一步,击键动作本身也可看做一个状态机。一个细小的击键动作包含了:释放、抖动、闭合、抖动和重新释放等状态。 同样,一个串行通信的时序(不管它是遵循何种协议,标准串口也好、I2C也好;也不管它是有线的、还是红外的、无线的)也都可看做由一系列有限的状态构成。 显示扫描程序也是状态机;通信命令解析程序也是状态机;甚至连继电器的吸合/释放控制、发光管(LED)的亮/灭控制又何尝不是个状态机。 当我们打开思路,把状态机作为一种思想导入到程序中去时,就会找到解决问题的一条有效的捷径。有时候用状态机的思维去思考程序该干什么,比用控制流程的思维去思考,可能会更有效。这样一来状态机便有了更实际的功用。 2,程序其实就是状态机: 也许你还不理解上面这句话。请想想看,计算机的大厦不就是建立在“0”和“1”两个基本状态的地基之上么? 3,状态机的要素: 状态机可归纳为4个要素,即现态、条件、动作、次态。这样的归纳,主要是出于对状态机的内在因果关系的考虑。 “现态”和“条件”是因,“动作”和“次态”是果。详解如下: ①现态:是指当前所处的状态。 ②条件:又称为“事件”。当一条件被满足,将触发一动作,或执行一状态的迁移。 ③动作:条件满足后执行的动作。动作执行完毕后,可迁移到新状态,也可仍旧保持原状。动作非必需的,当条件满足后,也可不执行任何动作,直接迁移到新状态。 ④次态:条件满足后要迁往的新状态。“次态”是相对于“现态”而言的,“次态”一旦被激活,就转变成新的“现态”了。 若我们进一步归纳,把“现态”和“次态”统一起来,而把“动作”忽略(降格处理),则只剩下两个最关键的要素,即:状态、迁移条件。 状态机的表示方法有多种,可用文字、图形或表格的形式来表示一个状态机。 纯粹用文字描述是很低效的,所以就不介绍了。接下来先介绍图形的方式。 4,状态迁移图(STD): 实验七有限状态机设计 一、实验目的 1、掌握利用有限状态机实现一般时序逻辑分析的方法; 2、掌握用VHDL或Verilog编写可综合的有限状态机的标准模板; 3、掌握用VHDL或Verilog编写序列检测器以及其他复杂逻辑电路的设计; 二、实验内容 1、用MOORE型状态机设计一个具有双向步进电动机控制实验:该控制电路有三个输入信号:clk时钟信号,clr复位信号,dir方向控制信号。输出信号为phase[3..0]用来控制步进电机的动作。当dir=1时要求phase[3..0]按照“0001”,“0010”,“0100”,“1000”的顺序变化;当dir=0时要求phase[3..0]按照“0001”,“1000”,“0100”,“0010”的顺序变化。 2、设计一个简单的状态机,功能是检测一个5位的二进制序列“10010”。 3、设计一个串行数据检测器,要求是:连续4个或4个以上为1时输出为1,其他输入情况为0。(选做) 4、根据状态图,写出对应于结构图b,分别由主控组合进程和主控时序进程组成的VERILOG 有限状态机描述。(选做) 三、实验步骤 实验一: 1、建立工程 2、创建Verilog HDL文件 3、输入程序代码并保存 module moore1(clk,clr,dir,phase); input clk,clr,dir; output[3:0] phase; reg[3:0] phase; reg[1:0] state; parameter s0='b00,s1='b01,s2='b10,s3='b11; always@(posedge clk) begin if(clr)begin phase<='b0000;state<=s0;end else begin case(state) s0:if(dir) begin phase<='b0010;state<=s1;end else begin phase<='b1000;state<=s3;end s1:if(dir) begin phase<='b0100;state<=s2;end else begin phase<='b0001;state<=s0;end s2:if(dir) begin phase<='b1000;state<=s3;end 单片机通信协议处理 现在大部分的仪器设备都要求能过通过上位机软件来操作,这样方便调试,利于操作。其中就涉及到通信的过程。在实际制作的几个设备中,笔者总结出了通信程序的通用写法,包括上位机端和下位机端等 1. 自定义数据通信协议 这里所说的数据协议是建立在物理层之上的通信数据包格式。所谓通信的物理层就是指我们通常所用到的 RS232、 RS485、红外、光纤、无线等等通信方式。在这个层面上,底层软件提供两个基本的操作函数:发送一个字节数据、接收一个字节数据。所有的数据协议全部建立在这两个操作方法之上。 通信中的数据往往以数据包的形式进行传送的,我们把这样的一个数据包称作为一帧数据。类似于网络通信中的 TCPIP 协议一般,比较可靠的通信协议往往包含有以下几个组成部分:帧头、地址信息、数据类型、数据长度、数据块、校验码、帧尾。 帧头和帧尾用于数据包完整性的判别,通常选择一定长度的固定字节组成,要求是在整个数据链中判别数据包的误码率越低越好。减小固定字节数据的匹配机会,也就是说使帧头和帧尾的特征字节在整个数据链中能够匹配的机会最小。通常有两种做法,一、减小特征字节的匹配几率。二、增加特征字节的长度。通常选取第一种方法的情况是整个数据链路中的数据不具有随即性,数据可预测,可以通过人为选择帧头和帧尾的特征字来避开,从而减小特征字节的匹配几率。使用第二种方法的情况更加通用,适合于数据随即的场合。通过增加特征字节的长度减小匹配几率,虽然不能够完全的避免匹配的情况,但可以使匹配几率大大减小,如果碰到匹配的情况也可以由校验码来进行检测,因此这种情况在绝大多说情况下比较可靠。 地址信息主要用于多机通信中,通过地址信息的不同来识别不同的通信终端。在一对多的通信系统中,可以只包含目的地址信息。同时包含源地址和目的地址则适用于多对多的通信系统。 Digital System Design 大部分数字系统都可以划分为控制单元和数据单元(存储单元)两个组成部分,通常,控制单元的主体是一个状态机,它接收外部信号以及数据单元产生的状态信息,产生控制信号序列。 1 2011/6/21Computer Faculty of Guangdong University of Technology Digital System Design 有限状态机特别适合描述那些发生有先后顺序或者有逻辑规律的事情(其实这就是状态机的本质)。状态机的本质就是对具有逻辑顺序或时序规律事件的一种描述方法,即“逻辑顺序”和“时序规律”就是状态机所要描述的核心和强项,换言之,所有具有逻辑顺序和时序规律的事情都适合用状态机来描述。 2 2011/6/21Computer Faculty of Guangdong University of Technology Digital System Design 1、基本概念 有限状态机(Finite State Machine,FSM)是表示实现有限个离散状态及其状态之间的转移等行为动作的数学模型。(关注Matlab的Stateflow) (1)状态:也叫状态变量。在逻辑设计中,使用状态划分逻辑顺序和时序规律。 状态名称、状态编码、进入/退出操作、内部转移、子状态、延迟事件 3 2011/6/21Computer Faculty of Guangdong University of Technology Digital System Design (2)转移:指两个状态之间的关系,表示当发生指定事件且满足指定条件时,第一个状态中的对象将执行某些操作并进入第二个状态,即“触发”了转移。将触发转移之前的状态定义为“源”状态(初始状态),而触发转移之后的状态定义为“目标”状态(次态)。 初始状态、转移条件、警戒条件、转移操作、目标状态 4 2011/6/21Computer Faculty of Guangdong University of Technology 北大青鸟中关村 解析技术–解析XML文件 在千禧年左右,当XML 第一次出现在很多Java 开发人员面前时,有两种基本的解析XML 文件的方法。SAX 解析器实际是由程序员对事件调用一系列回调方法的大型状态机。DOM 解析器将整个XML 文档加入内存,并切割成离散的对象,它们连接在一起形成一个树。该树描述了文档的整个XML Infoset 表示法。这两个解析器都有缺点:SAX 太低级,无法使用,DOM 代价太大,尤其对于大的XML 文件—整个树成了一个庞然大物。幸运的是,Java 开发人员找到第三种方法来解析XML 文件,通过对文档建模成“节点”,它们可以从文档流中一次取出一个,检查,然后处理或丢弃。这些“节点”的“流”提供了SAX 和DOM 的中间地带,名为“Streaming API for XML”,或者叫做StAX。(此缩写用于区分新的API 与原来的SAX 解析器,它与此同名。)StAX 解析器后来包装到了JDK 中,在javax.xml.stream 包。使用StAX 相当简单:实例化XMLEventReader,将它指向一个格式良好的XML 文件,然后一次“拉出”一个节点(通常用while 循环),查看。例如,在清单1 中,列举出了Ant 构造脚本中的所有目标:清单1. 只是让StAX 指向目标import java.io.*; import https://www.360docs.net/doc/f45323873.html,space.QName; import javax.xml.stream.*; import javax.xml.stream.events.*; import javax.xml.stream.util.*; public class Targets { public static void main(String[] args) throws Exception { for (String arg : args) { XMLEventReader xsr = XMLInputFactory.newInstance() .createXMLEventReader(new FileReader(arg)); while (xsr.hasNext()) { XMLEvent evt = xsr.nextEvent(); switch (evt.getEventType()) { case XMLEvent.START_ELEMENT: { StartElement se = evt.asStartElement(); if (se.getName().getLocalPart().equals("target")) { Attribute targetName = se.getAttributeByName(new QName("name")); // Found a target! System.out.println(targetName.getValue()); } break; } // Ignore everything else } } } } } StAX 解析器不会替换所有的SAX 和DOM 代码。但肯定会让某些任务容易些。尤其对完成不需要知道XML 文档整个树结构的任务相当方便。 请注意,如果事件对象级别太高,无法使用,StAX 也有一个低级API 在XMLStreamReader 中。尽管也许没有阅读器有用,StAX 还有一个XMLEventWriter,同样,还有一个XMLStreamWriter 类用于XML 输出。 本文和大家重点讨论一下UML活动图和状态图的概念,这两种图都有各自的特点和作用,那么他们之间有什么区别和联系呢,请看本文详细介绍。 UML活动图和状态图 一、UML活动图: ◆流程图常被用来建立算法模型 ◆UML活动图与流程图类似,不同在于它支持并行活动. ◆缺点:不能清楚的表示 二、作用: 1、描述一个操作的执行过程中所完成的工作或者动作 2、描述对象内部的工作 3、描述用例的执行 4、处理多线程 5、显示如何执行一组相关的动作,以及这些动作如何影响周围对象 三、以下情况不用UML活动图 1、显示对象之间的合作 2、显示对象在其生命周期内的运转情况。 这两点是通过序列图和协作图完成的。 四、UML活动图的基本要素: ◆活动状态 ◆活动状态之间的转移(箭头) ◆判断(决策点) ◆保证条件 ◆同步条:活动之间的同步 ◆起点和终点 --起点有且只有一个,终点可以有n个。 五、泳道: 用于对UML活动图中的活动进行分组,用于描述对象之间的合作关系。 ----所谓泳道技术,就是将活动用线分成一些纵向区域,这些纵向区域称为泳道。 UML状态图 一、状态图: ◆描述一个特定对象的所有可能状态以及由于各种事件的发生而引起的状态之间的转换。例如呼叫中心系统。 ◆状态图符 --状态:矩形(四角圆弧) --转移 --起点 --终点 1、状态机: ◆一种行为:描述了一个对象或一个交互在生命周期内响应事件所经历的状态序列。 ◆单个类或者一组类之间协作的行为可以用状态机来描述 ◆一个状态机涉及到一些其他元素,包括状态、转换、事件 2、状态: 在对象的生命周期中满足某些条件、执行某些活动或等待某些事件的一个条件活状况。1)名称 2)进入协作和退出动作 3)内部转换 4)子状态 5)延迟事件 3、转换:两个状态之间的一种关系,表示对象将在第一个状态中执行一定的动作并在某个特定事件发生而某个特定条件满足时进入第二个状态。 1)源状态 2)事件触发 3)监护条件 4)动作 5)目标状态 例子:电话机状态图 二、UML活动图与状态图的区别: 状态:行为的结果 活动:行为的动作 在uml中图符不一样。 注意:实际项目中,UML活动图不是必须的。 用到UML活动图的情况: --描述并行的过程或这行为 --描述一个算法 --描述一个跨越多个用例的活动 状态图描述了一个具体对象的可能状态以及他们之间的转换。 单独的说UML活动图很抽象,但是当把UML活动图与流程图进行简单的比较之后就 实验三利用有限状态机进行时序逻辑的设计 1.实验目的: (1)掌握利用有限状态机实现一般时序逻辑分析的方法; (2)掌握用Verilog编写可综合的有限状态机的标准模板; (3)掌握用Verilog编写状态机模块的测试文件的一般方法。 (4)在数字电路中已经学习过通过建立有限状态机来进行数字逻辑的设计,而在VerilogHDL硬件描述语言中,这种设计方法得到进一步的发展。通过Verilog HDL提供的语句,可以直观的设计出更为复杂的时序逻辑的电路。关于有限状态机的设计方法在教材中已经作了较为详细的阐述。 2.实验环境 PC机一台,安装有quartusII13.0软件以及modulsim软件 3.实验内容 设计一个简单的状态机,功能是检测一个5位二进制序列“10010”。考虑到序列重叠的可能。有限状态机共提供8个状态(包括初始状态IDLE). 4.实验步骤 1)源程序: module seqdet(x,z,clk,rst,state); input x,clk ,rst ; output z; output [2:0] state ; reg[2:0] state ; wire z; parameter IDLE='d0, A='d1, B='d2, C='d3, D='d4, E='d5, F='d6, G='d7; assign z=(state == E && x==0)?1:0; always @(posedge clk) if(!rst) begin state <= IDLE; end else casex(state) IDLE:if(x==1) begin state <= A; end A: if(x==0) begin state <= B; end B: if(x==0) begin state <= C; end else begin state <= F; end C: if(x==1) begin state <= D; end else begin 集成电路实验 状态机设计实验报告 专业:电子信息工程 姓名:江燕婷 学号:2011301200025 状态机设计(实验五)实验报告 一.实验目的 1. 掌握状态机设计的基本方法 2.学习利用状态机的方法实现控制电路 二.实验原理 有限状态机(Finite State Machine FSM)是时序电路设计中经常采用的一种方式,尤其适合设计数字系统的控制模块,在一些需要控制高速器件的场合,用状态机进行设计是一种很好的解决问题的方案,具有速度快、结构简单、可靠性高等优点。有限状态机非常适合用FPGA器件实现,用Verilog HDL的case 语句能很好地描述基于状态机的设计,再通过EDA工具软件的综合,一般可以生成性能极优的状态机电路,从而使其在执行时间、运行速度和占用资源等方面优于用CPU实现的方案。 有限状态机一般包括组合逻辑和寄存器逻辑两部分,寄存器逻辑用于存储状态,组合逻辑用于状态译码和产生输出信号。根据输出信号产生方法的不同,状态机可分为两类:米里型(Mealy)和摩尔型(Moore)。摩尔型状态机的输出只是当前状态的函数,如图1-1所示;米里型状态机的输出则是当前状态和当前输入的函数,如图1-2所示。米里型状态机的输出是在输入变化后立即变化的,不依赖时钟信号的同步,摩尔型状态机的输入发生变化时还需要等待时钟的到来,必须在状态发生变化时才会导致输出的变化,因此比米里型状态机要多等待一个时钟周期。 图1-1 摩尔型状态机图1-2 米里型状态机 状态机在硬件描述语言实现上,可使用单过程、双过程或三过程等不同的结构实现。状态机的状态实现上,可采用符号编码或显式数字编码。编码方式有顺序编码(自然二进制编码),一位热码(one-hot encoding),格雷(gray code)码等。顺序编码,简单状态寄存器占用少;一位热码输出译码电路简单;在状态顺序变化时,格雷码每次只有一位变化,避免产生输出信号毛刺。【CN110532162A】一种基于协议状态机的模糊测试脚本及测试引擎【专利】

有限状态机(FSM)

状态机思路在单片机程序设计中的应用

实验四 有限状态机设计(2学时)

第四章程控数字交换系统的软件复习要点2003

详解Qt中的状态机机制

深入分析比较8个安全模型

有限状态机设计

ISE学习教程解析

有限状态机(moore mealy)

状态机在单片机C程序中的应用

有限状态机设计

单片机通信协议处理解析

状态机讲义

解析技术

解析UML活动图和状态图的作用和区别

利用有限状态机进行时序逻辑的设计

状态机设计