高速电路设计中时序计算方法与应用实例

高速电路设计中时序计算方法与应用实例

来源:互联网

1满足接收端芯片的建立,保持时间的必要性

在高速数字电路设计中,由于趋肤效应、临近干扰、电流高速变化等因素,

设计者不能

单纯地从数字电路的角度来审查自己的产品,

而要把信号看作不稳定的模拟信号。

采用频谱

分析仪对信号分析,可以发现,信号的高频谱线主要来自于信号的变化沿而不是信号频率。 例如一个1MHz 的信号,虽然时钟周期为 1微秒,但是如果其变化沿上升或下降时间为纳秒 级,则在频谱仪上可以观察到频率高达数百兆赫兹的谱线。

信号的边沿,因为边沿往往也就是信号频谱最高、最容易受到干扰的地方。

在同步设计中,数据的读取需要基于时钟采样,根据以上分析,为了得到稳定的数据, 时钟的采样点应该远离数据的变化沿。

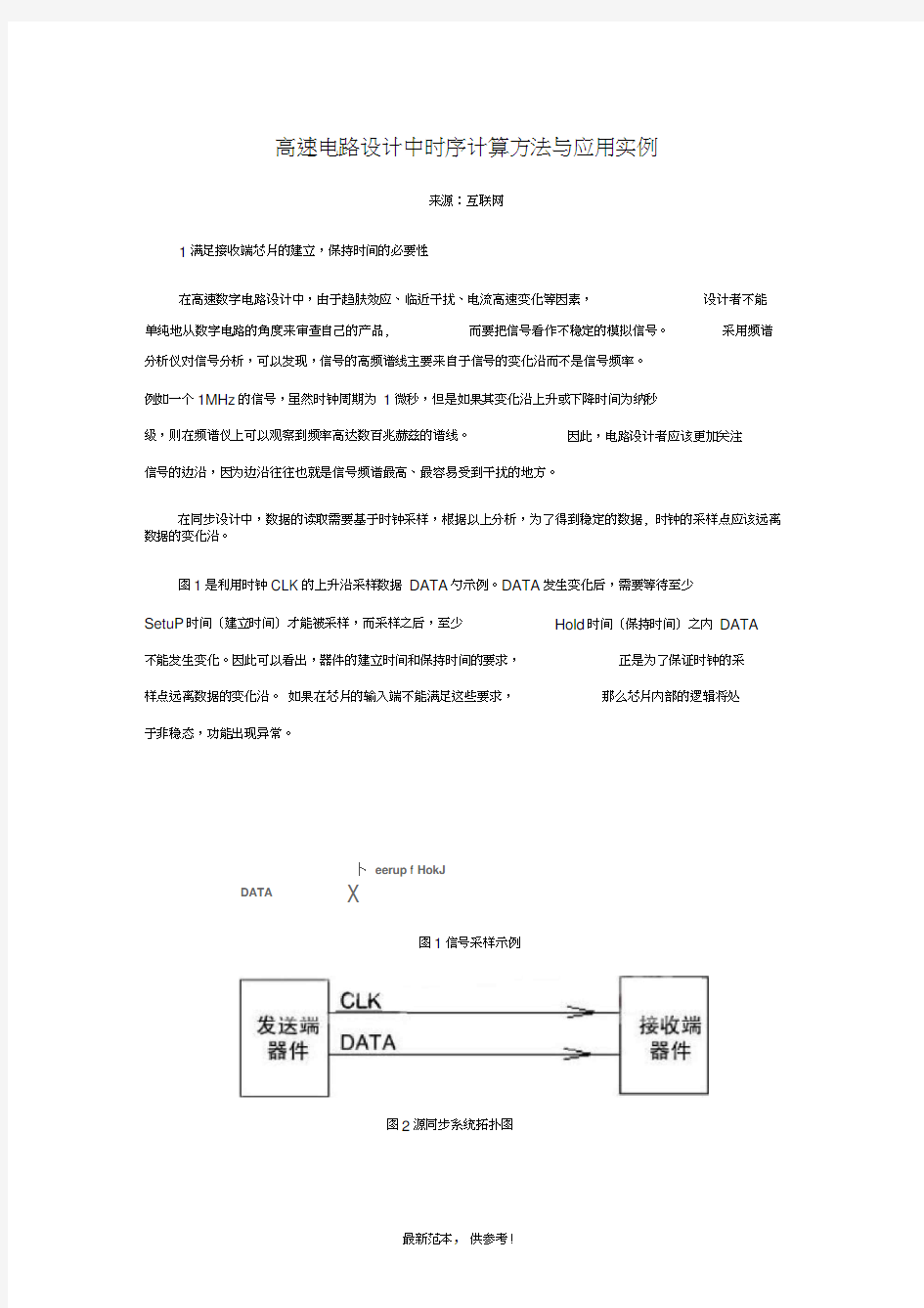

图1是利用时钟CLK 的上升沿采样数据 DATA 勺示例。DATA 发生变化后,需要等待至少

SetuP 时间(建立时间)才能被采样,而采样之后,至少

不能发生变化。因此可以看出,器件的建立时间和保持时间的要求, 正是为了保证时钟的采 样点远离数据的变化沿。 如果在芯片的输入端不能满足这些要求, 那么芯片内部的逻辑将处

于非稳态,功能出现异常。

因此,电路设计者应该更加关注

Hold 时间(保持时间)之内 DATA

DATA

卜 eerup f HokJ

X

图1信号采样示例

图2源同步系统拓扑图

2时序分析中的关键参数

为了进行时序分析,需要从

datasheet (芯片手册)中提取以下关键参数:

? Freq :时钟频率,该参数取决于对芯片工作速率的要求。

? Tcycle :时钟周期,根据时钟频率 Freq 的倒数求得。Tcycle=1/Freq.

? Teo :时钟到数据输出的延时。上文提到,输入数据需要采用时钟采样,而输出数据

同样也需要参考时钟,不过一般而言,相比时钟,输出的数据需要在芯片内延迟一段时间, 这个时间就称为Teo.该参数取决于芯片制造工艺。

? TsetuP (min ):最小输入建立时间要求。

? Thold ( min ):最小输入保持时间要求。

除以上五个参数外,时序分析中还需要如下经验参数:

? Vsig :信号传输速度。信号在电路上传输,传输速度约为

时序计算的目标是得到以下两个参数之间的关系:

? Tflight-data :数据信号在电路板上的走线延时。

? Tflight-clk :时钟信号在电路板上的走线延时。

以上参数是进行时序分析的关键参数,对于普通的时序分析已经足够。

源同步系统的时序计算

源同步系统指数据和时钟是由同一个器件驱动发出的情况, 扑结构:

该系统的特点是,时钟和数据均由发送端器件发出, 在接收端,利用接收到的时钟信号

CLK 采样输入数据信号 DATA.

源同步系统的时序计算公式为:

(式 2)

6英寸/纳秒。

F 图是常见的源同步系统拓

TCO ( max ) + ( Tflight-data - Tflight-clk

)MAX + Tsetup ( min )Thold ( min )

时序计算的最终目标是获得Tflight-data - T flight-clk 的允许区间,再基于该区间,通过Vsig参数,推算出时钟信号和数据信号的走线长度关系。

4 SP 14.2接口时序分析

SP 14.2 (System P acket In terface Level4 ,P hase 2 )接口是国际组织OIF 制定的针

对OC192( 10Gbps)速率的接口。目前广泛应用在高速芯片上,作为物理层芯片和链路层芯

片之间的接口。SP 14.2的接口定义如下:

SP 14.2接口信号按照收、发方向分为两组,如图3中,以T开头的发送信号组和以R 开头的接收信号组。每组又分为两类,以发送信号组为例, 有数据类和状态类,其中数据类

包含TDCLK TDAT[15: 0],TCTL,状态类包含TSCLK TSTAT[1: 0].

transmil ^SCLK

Link

TSTAT1101 .ayer

Device WCLK TDAT[15:0]| TCTL

算

XLK;Receive RCTL

Jnk

jyer

Device RSTAT(I:Q]

RSCLK TSCLK

TSTAT[1:

O]

RSTATIIQJ RSCLK

TDCLK

TDAT115:O3 TCTL PH Y

De/ice

'FE 啊'

RCTt

图3 SP 14.2接口信号

其中,状态类信号是单端LVTTL信号,接收端利用TSCLK的上升沿对TSTAT[1: 0]采样,

方向为从物理层芯片发往链路层芯片;数据类信号是差分LVDS信号,接收端利用TDCLK的上升沿与下降沿对TDAT[15:0]和TCTL采样,即一个时钟周期进行两次采样,方向为从链

路层芯片发往物理层芯片。

由于接收信号组与发送信号组的时序分析类似,因此本文仅对发送信号组进行时序分

析

。

在本设计中,采用Vitesee公司的VSC9128作为链路层芯片,VSC7323作为物理层芯片,

以下参数分别从这两个芯片的Datasheet中提取出来。

?状态类信号的时序分析

对状态类信号,信号的流向是从物理层芯片发送到链路层芯片。

第一步,确定信号工作频率,对状态类信号,本设计设定其工作频率和时钟周期为:

Freq=78.125MHz ; Tcycle = 1/ Freq = 12.8ns

第二步,从发送端,即物理层芯片手册提取以下参数:

-1ns < Tco < 2.5ns;

第三步,从接收端,即链路层芯片手册提取建立时间和保持时间的要求:

Tsetup(min) = 2ns; Thold(min) = 0.5ns;

将以上数据代入式 1 和式 2:

2.5ns + (Tflight-data - Tflight-clk)MAX + 2ns < 12.8ns -1ns + (Tflight-data - Tflight-clk)MIN > 0.5ns 1.5ns < (Tflight-data - Tflight-clk) < 8.3ns

基于以上结论,同时考虑到 Vsig = 6inch/ns ,可以得到如下结论,当数据信号和时钟 信号走线长度关系满足以下关系时,状态类信号的时序要求将得到满足: 度比TSCLK 长9英寸,但最多不能超过

49.8英寸。

? 数据类信号的时序分析

对数据类信号,信号的流向是从链路层芯片发送到物理层芯片。

第一步,确定信号工作频率,对数据类信号,本设计设定其工作频率为:

Freq=414.72MHz;

与状态类信号不同的是,数据类信号是双边沿采样,即,一个时钟周期对应两次采样, 因此采样周期为时钟周期的一半。采样周期计算方法为:

整理得到:

TSTAT 信号走线长

Tsa mp le = 1/2*Tcycle = 1.2

ns;

第二步,从发送端,即链路层芯片手册提取以下参数:

-0.28 ns < Tco < 0.28

ns;

第三步,从接收端,即物理层芯片资料可以提取如下需求:

Tset up(min) = 0.17

ns;

Thold(mi n) = 0.21

ns;

将以上数据代入式1和式2,需特别注意的是,对数据类信号,由于是双边沿采样,应

采用Tsample代替式1中的Tcycle :

0.28 ns + (Tflight-data- Tflight-clk)MAX + 0.17 ns < 1.2

ns

-0.28 ns + (Tflight-data- Tflight-clk)MIN> 0.21

ns

整理得到:

0.49 ns < (Tflight-data - Tflight-clk) < 0.75

ns

基于以上结论,同时考虑到Vsig = 6in ch/ns ,可以得到如下结论, 当数据信号和时钟

信号走线长度关系满足以下关系时,数据类信号的时序要求将得到满足: TDAT TCTL 信号走线长度比TDCLK长2.94英寸,但最多不能超过4.5英寸。

5结论

高速电路中的时序设计,虽然看似复杂,然而只要明晰其分析方法, 问题可以迎刃而解。

【本文档内容可以自由复制内容或自由编辑修改内容期待

你的好评和关注,我们将会做得更好】

ADS2009射频电路仿真实验实验报告

低通滤波器的设计与仿真报告 一、实验目的 (1)熟悉ADS2009的使用及操作; (2)运用此软件设计一低通录波器,通过改变C2.L1的值,使低通录波器达到预定的要求(dB值以大于—3.0以上为宜); (3)画出输出仿真曲线并标明截止频率的位置与大小。 二、低通滤波器简介 (1)定义:让某一频率以下的信号分量通过,而对该频率以上的信号分量大大抑制的电容、电感与电阻等器件的组合装置。低通滤波器是容许低于截止频率的信号通过,但高于截止频率的信号不能通过的电子滤波装置。 (2)特点与用途 特点:低损耗高抑制;分割点准确;双铜管保护;频蔽好,防水功能强。 用途:产品用途广泛,使用于很多通讯系统,如 CATV EOC 等系统。并能有效的除掉通频带以外的信号和多余的频段、频率的干扰。 低通滤波器在信号处理中的作用等同于其它领域如金融领域中移动平均数所起的作用;低通滤波器有很多种,其中,最通用的就是巴特沃斯滤波器和切比雪夫滤波器。 三、设计步骤 1,建立新项目 (1)在界面主窗口执行菜单命令【File】/【New Project...】,创建

新项目。在选择保存路径时,在“Name”栏中输入项目的名称“lab1”; (2)单击按钮“确认”,出现电路原理图设计及仿真向导对话框,按照要求进行选择选项。 2,建立一个低通录波器设计 (1)在主界面窗口,单击“New Schematic Window”图标,弹出原理图设计窗口; (2)单击“保存”图标,保存原理图,命名为“lpf1”; (3)在元件模型列表窗口中选择“Lumped-Components”集总参数元件类; (4)在左侧面板中选择电容图标,将其放置到电路图设计窗口中,并进行旋转; (5)用类似的方法将电感放置到电路图设计窗口中,并利用接地图标,把电容器的一端接地,将各个器件连接起来; (6)在元件库列表窗口选择“Simulation-S-Param”项,在该面板中选择S-parameter模拟控制器和端口Term,将其放到原理图中。双击电容“C2”并修改其参数。 低通滤波器原理图如下图1所示: 3,电路仿真 1)设置S参数控件参数 (1)双击S参数控件,打开参数设置窗口,将“Step-size”设置为0.5GHz; (2)选中【Display】选项卡,在此列出了所有可以显示在原理

实验五--时序逻辑电路实验报告

实验五时序逻辑电路(计数器和寄存器)-实验报告 一、实验目的 1.掌握同步计数器设计方法与测试方法。 2.掌握常用中规模集成计数器的逻辑功能和使用方法。 二、实验设备 设备:THHD-2型数字电子计数实验箱、示波器、信号源 器件:74LS163、74LS00、74LS20等。 三、实验原理和实验电路 1.计数器 计数器不仅可用来计数,也可用于分频、定时和数字运算。在实际工程应用中,一般很少使用小规模的触发器组成计数器,而是直接选用中规模集成计数器。 2.(1) 四位二进制(十六进制)计数器74LS161(74LS163) 74LSl61是同步置数、异步清零的4位二进制加法计数器,其功能表见表5.1。 74LSl63是同步置数、同步清零的4位二进制加法计数器。除清零为同步外,其他功能与74LSl61相同。二者的外部引脚图也相同,如图5.1所示。 表5.1 74LSl61(74LS163)的功能表 清零预置使能时钟预置数据输入输出 工作模式R D LD EP ET CP A B C D Q A Q B Q C Q D 0 ××××()××××0 0 0 0 异步清零 1 0 ××D A D B D C D D D A D B D C D D同步置数 1 1 0 ××××××保持数据保持 1 1 ×0 ×××××保持数据保持 1 1 1 1 ××××计数加1计数3.集成计数器的应用——实现任意M进制计数器 一般情况任意M进制计数器的结构分为3类,第一类是由触发器构成的简单计数器。第二类是由集成二进制计数器构成计数器。第三类是由移位寄存器构成的移位寄存型计数器。第一类,可利用时序逻辑电路的设计方法步骤进行设计。第二类,当计数器的模M较小时用一片集成计数器即可以实现,当M较大时,可通过多片计数器级联实现。两种实现方法:反馈置数法和反馈清零法。第三类,是由移位寄存器构成的移位寄存型计数器。 4.实验电路: 十进制计数器 同步清零法 同步置数法

同步时序电路的设计步骤

同步时序电路的设计步骤 同步时序电路的设计步骤 同步时序电路的分析是根据给定的时序逻辑电路,求出能反映该电路功能的状态图。状态图清楚地表明了电路在不同的输入、输出原状态时,在时钟作用下次态状态的变化情况。同步时序电路的设计的设计是分析的反过程,其是根据给定的状态图或通过对设计要求的分析得到的状态图,设计出同步时序电路的过程。 这里主要讨论给定状态图的情况下的同步时序电路的设计,对于具体的要求得到状态图的过程一般是一个较复杂的问题,这是暂不讲。根据已知状态图设计同步时序电路的过程一般分为以下几步: 1.确定触发器的个数。首先根据状态的个数来确定所需要触发器的个数,如给定的状态个数为n,由应满足 n≤2K,K为实现这来状态所需要的触发器的个数。(实际使用时可能给定的状态中存在冗余项,这时一般还须对状态进行化简。) 2.列出状态转移真值表。根据状态列出状态转移真值表,也称状态表、状态转移表。 3.触发器选型。选择合适的触发器,通常可选的触发器有:JK-FF,D-FF,T-FF,一般使用较广的为JK-FF。根据状态图和给出的触发器的型号写出其输入方程,通常在写输入方程时须对其进行化简,以使电路更简单。 4.求出输出方程。根据状态表,求出输出逻辑函数Z的输出方程,还过有些电路没有独立的输出,这一步就省了。 5.画出逻辑图。根据输入方程、输出方程画出逻辑电路图。 6.讨论设计的电路能否自启动。在设计的电路中可能出现一些无关的状态,这些状态能否经过若干个时钟脉冲后进行有效的状态。 同步时序电路设计举例 例按下图状态图设计同步时序电路。 1.根据状态数确定触发器的数目:由状态图可以看出,其每个状态由两个状态,故可用两个触发器。其变量可 用Q 1,Q 表示; 2.根据状态图列出状态表:状态表的自变量为输入变量x和触发器当前状态Q 1 n,Q n,而应变量为触发器的次态 Q 1n+1Q n+1、及输出z,列表时将自变量的所有组合全部列出来,其中当Q 1 n Q n=01的状态为不出现,其输出可看作任意 项处理。

射频实验报告一

电子科技大学通信射频电路实验报告 学生姓名: 学号: 指导教师:

实验一选频回路 一、实验内容: 1.测试发放的滤波器实验板的通带。记录在不同频率的输入下输出信号的 幅度,并绘出幅频响应曲线。 2.设计带宽为5MHz,中心频率为39MHz,特征阻抗为50欧姆的5阶带 通滤波器。 3.在ADS软件上对设计出的带通滤波器进行仿真。 二、实验结果: (一)低通滤波器数据记录及幅频响应曲线 频率 1.0k 500k 1M 1.5M 2.0M 2.5M 3.0M 3.5M 4..0M 4.5M 5.0M /Hz Vpp/mv 1000 1010 1020 1020 1020 1050 952 890 832 776 736 频率/Hz 5.5M 6.0M 6.2M 6.4M 6.6M 6.8M 7.0M 7.2M 7.4M 7.6M 7.8M Vpp/mv 704 672 656 640 624 592 568 544 512 480 448 频率/Hz 8.0M 8.2M 8.4M 8.6M 8.8M 9.0M 9.2M 9.4M 9.6M 9.8M 10.0M Vpp/mv 416 400 368 376 320 288 272 256 224 208 192

(二)带通滤波器数据记录及幅频响应曲线 频率 /MHz 0.5 1.0 1.5 2.0 2.5 3.0 3.5 4.0 4.5 5.0 5.5 6.0 6.5 Vpp/mv 0.4 0.8 0.4 0.6 0.8 0.6 0.8 0.8 1.4 1.1 6.0 4.0 23. 8 频率 /MHz 7.0 7.2 7.4 7.6 7.8 8.0 8.2 8.4 8.6 8.8 9.0 9.2 9.4 Vpp/mv 79. 2 72. 8 66. 4 69. 6 77. 6 90. 4 108. 8 137. 6 183. 2 260 364 442 440 频率/MHz 9.6 9.8 10. 10. 2 10. 4 10. 6 10.8 11.0 11.2 11. 4 11. 6 11. 8 12. Vpp/mv 440 403 378 378 406 468 468 548 548 484 412 356 324 频率/MHz 12. 2 12. 4 12. 6 12. 8 13. 13. 2 13.4 13.6 13.8 14.

时序逻辑电路实验报告

时序逻辑电路实验报告 一、实验目的 1. 加深理解时序逻辑电路的工作原理。 2. 掌握时序逻辑电路的设计方法。 3. 掌握时序逻辑电路的功能测试方法。 二、实验环境 1、PC机 2、Multisim软件工具 三、实验任务及要求 1、设计要求: 要求设计一个计数器完成1→3→5→7→9→0→2→4→6→8→1→…的循环计数(设初值为1),并用一个数码管显示计数值(时钟脉冲频率为约1Hz)。 2、实验内容: (1)按要求完成上述电路的功能。 (2)验证其功能是否正确。 四、实验设计说明(简述所用器件的逻辑功能,详细说明电路的设计思路和过程) 首先根据题目要求(即要完成1到9的奇数循环然后再0到8的偶数循环)画出真值表,如下图。画出真值表后,根据真值表画出各次态对应的卡诺图,如下图。然后通过化简卡诺图,得到对应的次态的状态方 程;

然后开始选择想要用于实现的该电路的器件,由于老师上课时所用的例题是用jk触发器完成的,我觉得蛮不错的,也就选择了同款的jk触发器;选好器件之后,根据状态方程列出jk触发器的驱动方程。然后根据驱动方程连接好线路图,为了连接方便,我也在纸上预先画好了连接图,以方便照着连接。接下来的工作就是在multisim上根据画好的草图连接器件了,然后再接上需要的显示电路,即可完成。

五、实验电路(画出完整的逻辑电路图和器件接线图)

六、总结调试过程所遇到的问题及解决方法,实验体会 1、设计过程中遇到过哪些问题?是如何解决的? 在设计过程中最大的问题还是忘记设计的步骤吧,因为老师是提前将实验内容已经例题讲解给我们听的,而我开始实验与上课的时间相隔了不短的时间,导致上课记下来的设计步骤忘得七七八八,不过好在是在腾讯课堂上得网课,有回放,看着回放跟着老师的思路走一遍后,问题也就迎刃而解了,后面的设计也就是将思路步骤走一遍而已,没再遇到什么困难。 2、通过此次时序逻辑电路实验,你对时序逻辑电路的设计是否有更清楚的认识?若没有,请分析原因;若有,请说明在哪些方面更加清楚。 通过这次时序逻辑电路实验,我最大的感触就是实验设计的思路与步骤一定要清晰,思路与步骤的清晰与否真的是造成实验设计是否困难的最重要的因素。清晰的话,做起实验来如同顺水推舟,毫不费力,不清晰的话则如入泥潭,寸步难行。

彩灯控制器电路设计报告

西安科技大学高新学院 毕业设计(论文) 题目彩灯控制器电路设计 院(系、部) 机电信息学院 专业及班级电专1202班 姓名张森 指导教师田晓萍 日期 2015年5月28日

摘要 随着微电子技术的发展,人民的生活水平不断提高,人们对周围环境的美化和照明已不仅限于单调的白炽灯,彩灯已成为时尚的潮流。彩灯控制器的实用价值在日常生产实践,日常生活中的作用也日益突出。基于各种器件的彩灯也都出现,单片机因其价格低廉、使用方便、控制简单而成为控制彩灯的主要器件。 目前市场上更多用全硬件电路实现,电路结构复杂,结构单一,一旦制成成品就只能按固定模式,不能根据不同场合,不同时段调节亮度时间,模式和闪烁频率等动态参数,而且一些电路存在芯片过多,电路复杂,功率损耗大,亮灯样式单调缺乏可操作性等缺点,设计一种新型彩灯已迫不及待。 近年来,彩灯对于美化、亮化城市有着不可轻视的重要作用。因此作为城市装饰的彩灯需求量越来越大,对于彩灯的技术和花样也越来越高。目前市场上各种式样的LED彩灯多半是采用全硬件电路实现,存在电路结构复杂、功能单一等局限性,因此有必要对现有的彩灯控制器进行改进。 关键词:LED彩灯;STC-89C52单片机;彩灯控制器。

目录 1前言 (1) 1.1设计目的 (1) 1.2设计要求 (1) 1.3总体方案设计与选择的论证 (2) 2节日彩灯控制器的设计 (4) 2.1核心芯片及主要元件功能介绍 (4) 2.1.1 AT89S52芯片 (4) 表1 (5) 2.1.2 74HC377芯片 (5) 2.1.3 74HC138芯片 (6) 2.2硬件设计 (7) 2.2.1直流电源电路 (7) 2.2.2按键电路 (8) 2.2.3时钟复位电路 (8) 2.2.4 LED显示电路 (9) 2.2.5硬件调试 (9) 2.3软件设计 (10) 3 总结 (15) 3.1实验方案设计的可行性、有效性 (15) 3.2设计内容的实用性 (15) 3.3心得 (16) 附录 (16) 参考文献 (18) 致谢 (19)

数字电路与系统设计实验报告

数字电路与系统设计实验报告 学院: 班级: 姓名:

实验一基本逻辑门电路实验 一、实验目的 1、掌握TTL与非门、与或非门和异或门输入与输出之间的逻辑关系。 2、熟悉TTL中、小规模集成电路的外型、管脚和使用方法。 二、实验设备 1、二输入四与非门74LS00 1片 2、二输入四或非门74LS02 1片 3、二输入四异或门74LS86 1片 三、实验内容 1、测试二输入四与非门74LS00一个与非门的输入和输出之间的逻辑关系。 2、测试二输入四或非门74LS02一个或非门的输入和输出之间的逻辑关系。 3、测试二输入四异或门74LS86一个异或门的输入和输出之间的逻辑关系。 四、实验方法 1、将器件的引脚7与实验台的“地(GND)”连接,将器件的引脚14与实验台的十5V连接。 2、用实验台的电平开关输出作为被测器件的输入。拨动开关,则改变器件的输入电平。 3、将被测器件的输出引脚与实验台上的电平指示灯(LED)连接。指示灯亮表示输出低电平(逻辑为0),指示灯灭表示输出高电平(逻辑为1)。 五、实验过程 1、测试74LS00逻辑关系 (1)接线图(图中K1、K2接电平开关输出端,LED0是电平指示灯) (2)真值表 2、测试74LS02逻辑关系

(1)接线图 (2)真值表 3、测试74LS86逻辑关系接线图 (1)接线图 (2)真值表 六、实验结论与体会 实验是要求实践能力的。在做实验的整个过程中,我们首先要学会独立思考,出现问题按照老师所给的步骤逐步检查,一般会检查处问题所在。实在检查不出来,可以请老师和同学帮忙。

实验二逻辑门控制电路实验 一、实验目的 1、掌握基本逻辑门的功能及验证方法。 2、掌握逻辑门多余输入端的处理方法。 3、学习分析基本的逻辑门电路的工作原理。 二、实验设备 1、基于CPLD的数字电路实验系统。 2、计算机。 三、实验内容 1、用与非门和异或门安装给定的电路。 2、检验它的真值表,说明其功能。 四、实验方法 按电路图在Quartus II上搭建电路,编译,下载到实验板上进行验证。 五、实验过程 1、用3个三输入端与非门IC芯片74LS10安装如图所示的电路。 从实验台上的时钟脉冲输出端口选择两个不同频率(约7khz和14khz)的脉冲信号分别加到X0和X1端。对应B和S端数字信号的所有可能组合,观察并画出输出端的波形,并由此得出S和B(及/B)的功能。 2、实验得真值表

《单片机系统设计》实验报告

短学期实验报告 (单片机系统设计) 题目: 专业: 指导教师: 学生姓名: 学号: 完成时间: 成绩:

基于单片机的交流电压表设计 目录 1系统的设计要求 (2) 2系统的硬件要求 (2) 2.1真有效值转换电路的分析 (2) 2.2放大电路的设计 (3) 2.3A/D转换电路的设计 (3) 2.4单片机电路的分析 (4) 2.5显示电路 (4) 3 软件设计 (5) 3.1 软件的总流程图 (5) 3.2 初始化定义与定时器初始化流程图 (5) 3.3 A/D转换流程图 (6) 3.4 数据处理流程图 (6) 3.5 数据显示流程图 (7) 4 调试 (7) 4.1 调试准备 (7) 4.2 关键点调试 (7) 4.3 测试结果 (8) 4.4 误差分析 (8) 5结束语 (8) 5.1 总结 (9) 5.2 展望 (9) 附录1 总原理图 (10) 附录2 程序 (10) 附录3 实物图 (14)

基于单片机的交流电压表设计 ****学院 ****专业 姓名 指导老师:******* 1 设计要求 (1)运用单片机实现真有效值的检测和显示。 (2)数据采集使用中断方式,显示内容为有效值与峰值交替进行。 2 硬件设计 本系统是完成一个真有效值的测量和显示,利用AD737将交流电转换成交流电压的有效值,用ADC0804实现模数转换,再通过单片机用数码管来显示。系统原理框图如图2-1所示。系统框图由真有效值转换电路、放大电路、A/D 转换电路、单片机电路、数码管显示电路五部分。 图2-1 原理框图 2.1 真有效值转换电路 真有效值转换电路主要是利用AD737芯片来实现真有效值直流变换的,即将输入的交流信号转换成直流信号的有效值,其原理图如图2-2所示。 图2-2 真有效值转换电路 由于AD737最大输入电压为200mV, 所以需要接两个二极管来限制输入电压,起到限幅的作用。如图中D1、D2,由IN4148构成,电容C6是耦合电容,电阻R1是限流电阻。 2.2 放大电路设计 放大电路主要是利用运放uA741来进行放大,电路原理图如图2-3所示。 A/D 转换 单片机 电路 显示 电路 转换 电路 交流 信号 放大 电路

同步时序逻辑电路的习题 数字逻辑

第五章 同步时序逻辑电路的习题 一、基本知识点 1、时序逻辑电路的一般结构 特点:a 、有存储电路(记忆元件);有组合电路(特殊时可没有) b 、包含反馈电路,电路功能与“时序”相关 c 、输出不仅与输入(X )有关,而且与存储状态(Y )有关 分类:(1)Mealy 型 Z =F (X ,Q ) 输出是电路的输入和现态的函数(注意输出与输入有直接关系) (2)Moore 型 Z =F (Q ) 输出仅仅是电路现态的函数(注意输出与输入没有直接关系) 同步时序逻辑电路:各触发器共用同一时钟信号,即电路中各触发器状态的转换时刻在统一时钟信号控制下同步发生。 异步时序逻辑电路:电路没有统一的时钟信号对状态变化进行同步控制,输入信号的变化将直接引起电路状态的变化。 //本课程将较少讨论异步时序逻辑电路 2、同步时序逻辑电路的描述 注意:任一个同步时序逻辑电路的结构和功能可用3组函数表达式完整地描述。 (1)激励函数表达式:存储电路输入Y 与电路输入X 和现态Q 之间的关系 Y =F (X ,Q ) //现态Q 就是上图存储电路原始的输出y k (2)次态函数表达式:电路的次态Q n+1与激励函数Y 和现态Q 之间关系 Q n+1=F (Y ,Q ) //次态Q n+1就是上图存储电路再次触发后的输出y k n+1 (3)输出函数表达式:电路的输出Z 和输入X 和当前现态Q 的关系 Mealy 型 Z =F (X ,Q ) Moore 型 Z =F (Q ) 输入信号 输出信号 X 1 X 2 X n Z 1 Z 2 Z m y s 过去输入 现态 现在输入 } 输出 输出 所有输入 现态

RLC串联谐振电路(Multisim仿真实训)

新疆大学 实习(实训)报告 实习(实训)名称: __________ 电工电子实习(EDA __________ 学院: __________________ 专业班级_________________________________ 指导教师______________________ 报告人____________________________ 学号 ______ 时间: 实习主要内容: 1. 运用Multisim仿真软件自行设计一个RLC串联电路,并自选合适的参数。 2. 用调节频率法测量RLC串联谐振电路的谐振频率f 0 ,观测谐振现象。 3. 用波特图示仪观察幅频特性。 4?得出结论并思考本次实验的收获与体会。 主要收获体会与存在的问题: 本次实验用Multisim 仿真软件对RLC串联谐振电路进行分析,设计出了准确的电路模型,也仿真出了正确的结果。通过本次实验加深了自己对RLC振荡电路的理解与应用,更学习熟悉了Multisim 仿真软件,达到了实验的目

的。存在的问题主要表现在一些测量仪器不熟悉,连接时会出现一些错误,但最终都实验成功了。 指导教师意见: 指导教师签字: 年月日 备注: 绪论 Multisim仿真软件的简要介绍 Multisim是In terctive Image Tech no logies公司推出的一个专门用于电子电 路仿真和设计的软件,目前在电路分析、仿真与设计等应用中较为广泛。该软件以图形界面为主,采用菜单栏、工具栏和热键相结合的方式,具有一般Windows 应用软件的界面风格,用户可以根据自己的习惯和熟练程度自如使用。尤其是多种可放置到设计电路中的虚拟仪表,使电路的仿真分析操作更符合工程技术人员的工作习惯。下面主要针对Multisim11.0软件中基本的仿真与分析方法做简单介绍。 EDA就是“ Electronic Design Automation ”的缩写技术已经在电子设计领 域得到广泛应用。发达国家目前已经基本上不存在电子产品的手工设计。一台电子产品的设计过程,从概念的确立,到包括电路原理、PCB版图、单片 机程序、机内结构、FPGA的构建及仿真、外观界面、热稳定分析、电磁兼容分析在内的物理级设计再到PCB钻孔图、自动贴片、焊膏漏印、元器件清 单、总装配图等生产所需资料等等全部在计算机上完成。EDA已经成为集成 电路、印制电路板、电子整机系统设计的主要技术手段。 功能: 1. 直观的图形界面 整个操作界面就像一个电子实验工作台,绘制电路所需的元器件和仿真所需的测试仪器均可直接拖放到屏幕上,轻点鼠标可用导线将它们连接起来,软件仪器的控制面板和操作方式都与实物相似,测量数据、波形和特性曲线如同在真实仪器上看到的;

单元15-时序逻辑电路

第十六单元时序逻辑电路 (8学时——第49~56学时) 主要容:时序逻辑电路的分析与设计 教学重点:时序逻辑电路的分析与设计方法 教学难点:时序逻辑电路的设计 教学方法:启发式教学、探究式教学 教学手段:实验、理论、实际应用相结合 第一部分知识点 一、时序电路概述 时序电路的状态及输出是与时间顺序有关的,由组合电路和存储电路(多为触发器)组成,1、特点 任意时刻的输出,不仅与该时刻的输入有关、还与电路原来的状态有关。 2、分类 按逻辑功能分为计数器、寄存器等,按触发器工作分为同步电路和异步电路,按电路输出信号特性分为Mealy型(输出与输入及电路现态有关)和Moore型(输出仅与电路现态有关)电路。 二、时序电路的分析 1、分析步骤 (1)写出电路的时钟方程(各触发器的CP表达式)、输出方程(各输出端表达式)及驱动方程(各触发器的触发信号表达式)。 (2)求出电路的状态方程(各触发器的状态表达式) (3)计算得出电路工作状态表 (4)画状态图及时序图 (5)分析电路功能 2、分析举例 分析时序电路

(1)时钟方程CP0=CP1=CP2=CP 输出方程n n n Q Q Q Y 1 2 = 驱动方程n Q J 2 =、n Q K 2 =,n Q J 1 =、n Q K 1 =,n Q J 1 2 =、n Q K 1 2 =(2)状态方程 将J、K代入JK触发器特征方程n n n Q K Q J Q+ = +1得各触发器状态方程: n n Q Q 2 1 = +、n n Q Q 1 1 = +、n n Q Q 1 1 2 = + (3)计算得到状态表 现态次态输出 n Q 2 n Q 1 n Q 1 2 | n Q+1 1 + n Q1 + n Q Y 0 0 0 0 0 1 0 1 0 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 0 0 1 0 1 1 1 0 1 1 1 1 0 0 0 0 1 0 1 0 0 1 1 0 1 1 1 1 1 1 1 (4)画状态图及时序图 (5)逻辑功能 这是一个有六个工作状态的同步工作电路,属Moore型电路。 (6)有效态和无效态

实验五时序逻辑电路实验报告

实验五时序逻辑电路(计数器和寄存器)-实验报告一、实验目的 1掌握同步计数器设计方法与测试方法。 2 ?掌握常用中规模集成计数器的逻辑功能和使用方法。 二、实验设备 设备:THHD-2型数字电子计数实验箱、示波器、信号源 器件:74LS163、74LS00、74LS20 等。 三、实验原理和实验电路 1计数器 计数器不仅可用来计数,也可用于分频、定时和数字运算。在实际工程应用中,一般很少使用小规模的触发器组成计数器,而是直接选用中规模集成计数器。 2. (1)四位二进制(十六进制)计数器74LS161 (74LS163) 74LS161是同步置数、异步清零的4位二进制加法计数器,其功能表见表。 74LS163是同步置数、同步清零的4位二进制加法计数器。除清零为同步外,其他功能与74LS161相同。二者的外部引脚图也相同,如图所示。 3.集成计数器的应用一一实现任意M进制计数器

Eft CR IK rh th Ih ET 7-I1A C1M /( 制扭环计数 同步清零法器 同步置数法 般情况任意M 进制计数器的结构分为 3类,第一类是由触发器构成的简单计数器。 第 二类是 由集成二进制计数器构成计数器。第三类是由移位寄存器构成的移位寄存型计数器。 第一类,可利用时序逻辑电路的设计方法步骤进行设计。 第二类,当计数器的模 M 较小时用 一片集成计数器即可以实现,当 M 较大时,可通过多片计数器级联实现。两种实现方法:反 馈置数法和反馈清零法。第三类,是由移位寄存器构成的移位寄存型计数器。 4?实验电路: 十进制计数器 1

图74LS161 (74LS163)外部引脚图 四、实验内容及步骤 1 .集成计数器实验 (1)按电路原理图使用中规模集成计数器74LS163和与非门74LS00,连接成一个同步置数或同步清零十进制计数器,并将输出连接至数码管或发光二极管。然后使用单次脉冲作为触发输入,观察数码管或发光二极管的变化,记录得到电路计数过程和状态的转换规律。 (2)根据电路图,首先用D触发器74LS7474构成一个不能自启的六进制扭环形计数器,同样将输出连接至数码管或发光二极管。然后使用单次脉冲作为触发输入,观察数码管或发光二 极管的变化,记录得到电路计数过程和状态的转换规律。注意观察电路是否能自启,若不能自启,则将电路置位有效状态。接下来再用D触发器74LS7474构成一个能自启的六进制扭环 形计数器,重复上述操作。 2?分频实验 依据实验原理图用74LS163及74LS00组成一个具有方波输出的六分频电路。选择适当时钟输入方式及频率(CP接连续波脉冲),用双踪示波器观察并记录时钟与分频输出信号的时序波形。 五、实验结果及数据分析 1 .集成计数实验同步清零和同步置数的十进制加一计数器状态转换过程分别如下所示: 0000 : 0001 : 0010 : 0011 ; 0100 爲00*卄庇爲爲卄yh 六进制扭环形计数器的状态转换过程如下:

收音机实验报告..

《高频电子线路》课程设计报告 题目SD-105 七管半导体收音机 学院(部)信息学院 专业通信工程 班级2011240401 学生姓名张静 学号33 指导教师宋蓓蓓,利骏

目录 一、概括……………………………………页码 二、收音机工作原理……………………………………页码 三、各部分设计及原理分析……………………页码 四、实验仿真及结果……………………………页码 五、结论…………………………………………页码 六、心得体会……………………………………页码 七、参考文献……………………………………页码

调幅半导体收音机原理及其调试 一概述:收音机的发明人类自从发现能利用电波传递信息以来,就不断研究出不同的方法来增加通信的可靠性、通信的距离、设备的微形化、省电化、轻巧化等。接收信息所用的接收机,俗称为收音机。目前的无线电接收机不单只能收音,且还有可以接收影像的电视机、数字信息的电报机等。 随着广播技术的发展,收音机也在不断更新换代。自1920年开发了无线电广播的半个多世纪中,收音机经历了电子管收音机、晶体管收音机、集成电路收音机的三代变化,功能日趋增多,质量日益提高。20世纪80年代开始,收音机又朝着电路集成化、显示数字化、声音立体化、功能电脑化、结构小型化等方向发展。 1947年、美国贝尔实验室发明了世界上第一个晶体管,从此以后.开始了收音机的晶体管时代.并且逐步结束了以矿石收音机、电子管收音机为代表的收音机的初级阶段。 调幅收音机:由输入回路、本振回路、混频电路、检波电路、自动增益控制电路(AGC)及音频功率放大电路组成输入回路由天线线圈和可变电容构成,本振回路由本振线圈和可变电容构成,本振信号经内部混频器,与输入信号相混合。混频信号经中周和455kHz陶瓷滤波器构成的中频选择回路得到中频信号。至此,电台的信号就变成了以

Moore型同步时序逻辑电路的设计与分析

实验九Moore型同步时序逻辑电路的分析与设计 22920132203686 薛清文周2下午实验 一.实验目的: 1.同步时序逻辑电路的分析与设计方法 2.D,JK触发器的特性机器检测方法。 2.掌握时序逻辑电路的测试方法。 3.了解时序电路自启动设计方法。 4.了解同步时序电路状态编码对电路优化作用。 二.实验原理: 二、 1.Moore同步时序逻辑电路的分析方法: 时序逻辑电路的分析,按照电路图(逻辑图),选择芯片,根据芯片管脚,在逻辑图上标明管脚号;搭接电路后,根据电路要求输入时钟信号(单脉冲信号或连续脉冲信号),求出电路的状态转换图或时序图(工作波形),从中分析出电路的功能。 2.Moore同步时序逻辑电路的设计方法: (1)分析题意,求出状态转换图。 (2)状态分析化简:确定等价状态,电路中的等价状态可合并为一个状态。(3)重新确定电路状态数N,求出触发器数n,触发器数按下列公式求:2n-1 实验一 典型环节的模拟研究及阶跃响应分析 1、比例环节 可知比例环节的传递函数为一个常数: 当Kp 分别为0.5,1,2时,输入幅值为1.84的 正向阶跃信号,理论上依次输出幅值为0.92,1.84,3.68的反向阶跃信号。实验中,输出信号依次为幅值为0.94,1.88,3.70的反向阶跃信号, 相对误差分别为1.8%,2.2%,0.2%. 在误差允许范围内可认为实际输出满足理论值。 2、 积分环节 积分环节传递函数为: (1)T=0.1(0.033)时,C=1μf(0.33μf),利用MATLAB ,模拟阶跃信号输入下的输出信号如图: T=0.1 T=0.033 与实验测得波形比较可知,实际与理论值较为吻合,理论上T=0.033时的波形斜率近似为T=0.1时的三倍,实际上为8/2.6=3.08,在误差允许范围内可认为满足理论条件。 3、 惯性环节 i f i o R R U U -=TS 1 CS R 1Z Z U U i i f i 0-=-=-= 惯性环节传递函数为: K = R f /R 1,T = R f C, (1) 保持K = R f /R 1 = 1不变,观测T = 0.1秒,0.01秒(既R 1 = 100K,C = 1μf , 0.1μf )时的输出波形。利用matlab 仿真得到理论波形如下: T=0.1时 t s (5%)理论值为300ms,实际测得t s =400ms 相对误差为:(400-300)/300=33.3%,读数误差较大。 K 理论值为1,实验值2.12/2.28, 相对误差为(2.28-2.12)/2.28=7%与理论值较 为接近。 T=0.01时 t s (5%)理论值为30ms,实际测得t s =40ms 相对误差为:(40-30)/30=33.3% 由于ts 较小,所以读数时误差较大。 K 理论值为1,实验值2.12/2.28, 相对误差为(2.28-2.12)/2.28=7%与理论值 较为接近 (2) 保持T = R f C = 0.1s 不变,分别观测K = 1,2时的输出波形。 K=1时波形即为(1)中T0.1时波形 K=2时,利用matlab 仿真得到如下结果: 1 TS K )s (R )s (C +-= 时序电路设计 实验目的: 1.掌握条件语句在简单时序模块设计中的使用。 2.学习在Verilog模块中应用计数器。 实验环境: Windows 7、MAX+PlusⅡ10等。 实验内容: 1.模为60的8421BCD码加法计数器的文本设计及仿真。 2.BCD码—七段数码管显示译码器的文本设计及仿真。 3.用For语句设计和仿真七人投票表决器。 4.1/20分频器的文本设计及仿真。 实验过程: 一、模为60的8421BCD码加法计数器的文本设计及仿真: (1)新建文本:选择菜单File下的New,出现如图5.1所示的对话框,在框中选中“Text Editor file”,按“OK”按钮,即选中了文本编辑方式。 图5.1 新建文本 (2)另存为Verilog编辑文件,命名为“count60.v”如图5.2所示。 (3)在编辑窗口中输入程序,如图5.3所示。 图5.2 另存为.V编辑文件图5.4 设置当前仿真的文本设计 图5.3 模为60的8421BCD码加法计数器的设计代码 (4)设置当前文本:在MAX+PLUS II中,在编译一个项目前,必须确定一个设计文件作为当前项目。按下列步骤确定项目名:在File菜单中选择Project 中的Name选项,将出现Project Name 对话框:在Files 框内,选择当前的设计文件。选择“OK”。如图5.4所示。 (5)打开编译器窗口:在MAX—plusⅡ菜单内选择Compiler 项,即出现如图5.5的编译器窗口。 图5.5 编译器窗口 选择Start即可开始编译,MAX+PLUS II编译器将检查项目是否有错,并对项目进行逻辑综合,然后配置到一个Altera 器件中,同时将产生报告文件、编程文件和用于时间仿真用的输出文件。 (6)建立波形编辑文件:选择菜单File下的New选项,在出现的New对话框中选择“Waveform Editor File”,单击OK后将出现波形编辑器子窗口。 (7)仿真节点插入:选择菜单Node下的Enter Nodes from SNF选项,出现如图5.6所示的选择信号结点对话框。按右上侧的“List”按钮,在左边的列表框选择需要的信号结点,然后按中间的“=>”按钮,单击“OK”,选中的信号将出现在波形编辑器中。 图5.6 仿真节点插入 时序逻辑电路分析例题 1、分析下图时序逻辑电路。 解: 1、列出驱动方程:111==K J 1//122Q A AQ K J +== 2、列出状态方程: 将驱动方程代入JK 触发器的特性方程Q K JQ Q //*+=得: /1*1Q Q = 212/1//21//2/1*2Q AQ Q Q A Q Q A Q AQ Q +++= 3、列出输出方程: 21//2/1Q Q A Q AQ Y += 4、列出状态转换表: (1)当A=1时: 根据:/1*1Q Q =;21/2/1*2Q Q Q Q Q +=;/2/1Q Q Y =得: (2)当A=0时: 根据:/1*1Q Q =;2/1/21*2 Q Q Q Q Q +=;21Q Q Y =得 : 5、画状态转换图: 6、说明电路实现的逻辑功能: 此电路就是一个可逆4进制(二位二进制)计数器,CLK 就是计数脉冲输入端,A 就是加减控制端,Y 就是进位与借位输出端。当控制输入端A 为低电平0时,对输入的脉冲进行加法计数,计满4个脉冲,Y 输出端输出一个高电平进位信号。当控制输入端A 为高电平1时,对输入的脉冲进行减法计数,计满4个脉冲,Y 输出端输出一个高电平借位信号。 2、如图所示时序逻辑电路,试写出驱动方程、状态方程,画出状态图,说明该电路的功能。 解:驱动方程 ?? ?=⊕=1010K Q X J n ???=⊕=11 1K Q X J n 状态方程 ()()n n n n n n n n n n n n n n Q XQ Q Q X Q Q X Q Q Q X Q Q X Q Q X Q 0 1 1 1 1 010110 11+=⊕=+=⊕=++ 1J 1K C1 1J 1K C1 1 Q 0 Q CP X Z =1 =1 =1 & FF 1 FF 0 1 1 数字电子技术实验报告 实验名称:时序逻辑电路 班级姓名学号 实验日期年月日交报告日期年月日 时序逻辑电路 一、设计要求 1.设计一个秒脉冲发生器,用LED指示秒脉冲的发送。 2.设计一个带有异步清零和同步置数信号的4位寄存器,并在开发板上验证。 二、实验内容 任务1:秒脉冲发生器 (1)源文件——ge.v module ge( input clr, input clk, output LED ); parameter T1s = 26'b10_1111_1010_1111_0000_1000_0000; reg [26:0] Count1; always @ (posedge clk or posedge clr) begin if(clr==1) Count1<=0; else if(Count1==T1s) Count1<=0; else Count1<=Count1 + 1; end reg rled; always @ (posedge clk or posedge clr) begin if(clr==1) rled<=0; else if(Count1==T1s) rled<=~rled; end assign LED=rled; endmodule (2)约束文件——ge.ucf NET"clk"LOC="B8"; //时钟 NET"clr"LOC="N3"; //SW7 NET"LED"LOC="G1"; //LED7 (3)开发板验证 当将开关SW7拨到1,LED7每隔1s闪烁一次。 任务2:四位寄存器(异步清零,同步置数) (1)源文件——ge1.v module ge1(clr,clk,d,load,q); input clr,clk,load; input[3:0] d; output[3:0] q; reg[3:0] q; always@(posedge clk or posedge clr) if(clr) q<=0; //异步清零 else if(!clr && load) //同步置数 begin q[0]<=1;q[1]<=1;q[2]<=1;q[3]<=1; end else q<=d; endmodule (2)约束文件——ge1.ucf NET"clk"LOC="B8"; //MCLK NET"clr"LOC="P11"; //SW0 NET"load"LOC="L3"; //SW1 NET"d[3]"LOC="G3"; //SW4 NET"d[2]"LOC="F3"; //SW5 NET"d[1]"LOC="E2"; //SW6 NET"d[0]"LOC="N3"; //SW7 NET"q[3]"LOC="N5"; //LD4 NET"q[2]"LOC="N4"; //LD5 NET"q[1]"LOC="P4"; //LD6 NET"q[0]"LOC="G1"; //LD7 (3)仿真文件——test_ge1.v #100; clr=1; #200; clr=0;clk=1;d=0100; #200; clk=0;d=1100; #200; clk=1;d=1001; #200; clk=0;d=0011; 实验十Moore型同步时序逻辑电路的分析与设计 一.实验目的: 1.同步时序逻辑电路的分析与设计方法 2.掌握时序逻辑电路的测试方法。 二.实验原理: 1.Moore同步时序逻辑电路的分析方法: 时序逻辑电路的分析,按照电路图(逻辑图),选择芯片,根据芯片管脚,在逻辑图上标明管脚号;搭接电路后,根据电路要求输入时钟信号(单脉冲信号或连续脉冲信号),求出电路的状态转换图或时序图(工作波形),从中分析出电路的功能。 2.Moore同步时序逻辑电路的设计方法: (1)分析题意,求出状态转换图。 (2)状态分析化简:确定等价状态,电路中的等价状态可合并为一个状态。(3)重新确定电路状态数N,求出触发器数n,触发器数按下列公式求:2n-1 (7)利用卡诺图如图2,求状态方程、驱动方程。 (8)自启动检验:将各无效状态代入状态方程,分析状态转换情况,画出完整的 状态转换图,如图3所示,检查是否能自启动。自动控制原理实验报告31418

[VIP专享]EDA 实验2简单分频时序逻辑电路设计 实验报告

时序逻辑电路分析举例

时序逻辑电路实验报告

实验十 Moore型同步时序逻辑电路的分析与设计