EDA实验报告1_8位全加器

EDA技术与应用实验报告

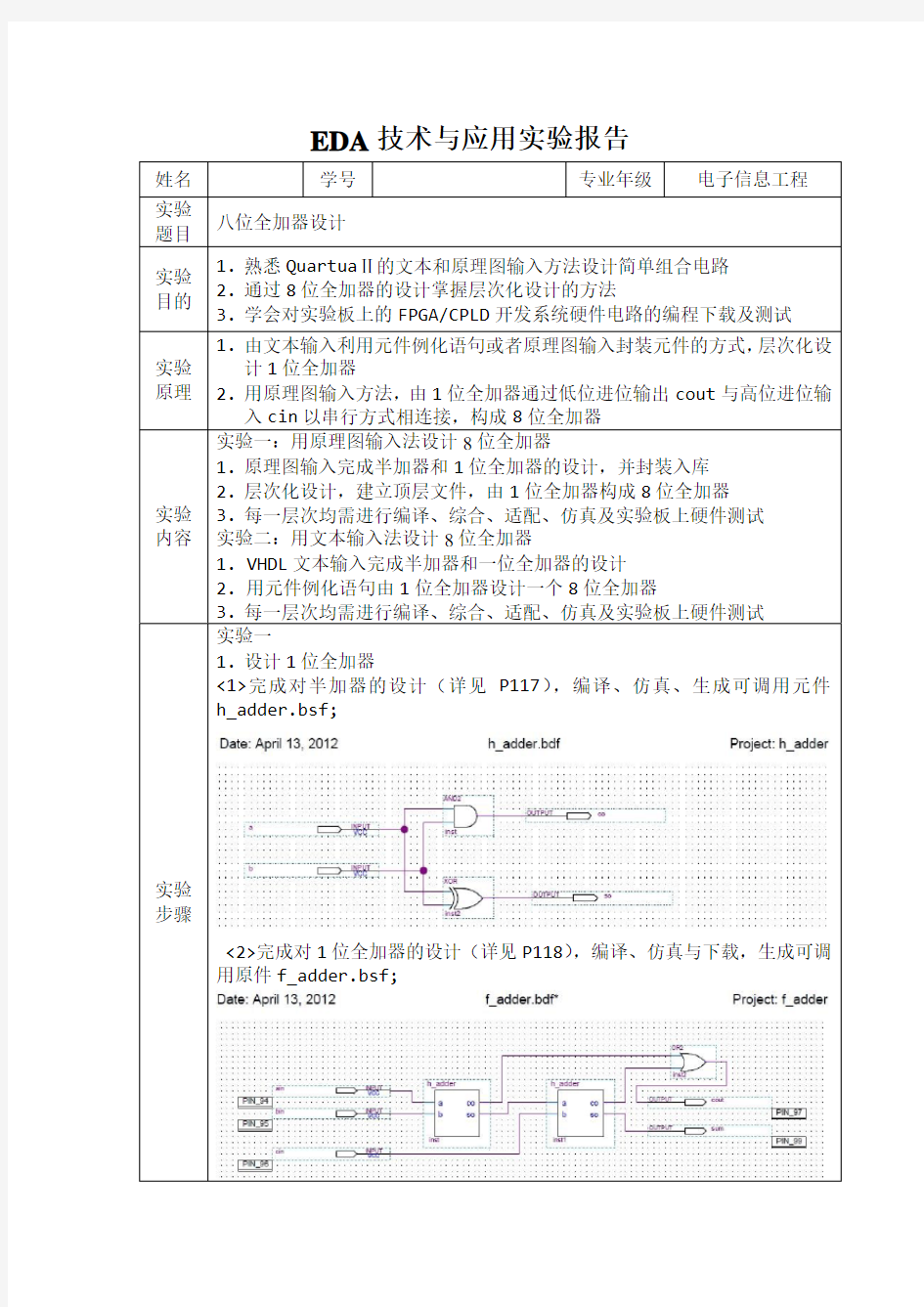

<2>完成对1位全加器的设计(详见P118),编译、仿真与下载,生成可调用原件f_adder.bsf;

<3>选择芯片EP1K100QC208-3,引脚锁定并再次编译,编程下载,分析实验结果。

实验二

1.设计1位全加器

<1>分别新建子文件夹,用来保存底层文件或门or2a.VHDL、半加器h_adder.VHDL的设计,并分别建立相应的project,进行编译、综合、适配、

实验一 八位全加器的设计

电子科技大学电子工程学院标准实验报告(实验)课程名称EDA技术与应用 姓名:孙远 学号:2010021030002 指导教师:窦衡 电子科技大学教务处制表

实验一八位全加器的设计 一、预习内容 1.结合教材中的介绍熟悉QuartusⅡ软件的使用及设计流程; 2.八位全加器设计原理。 二、实验目的 1.掌握图形设计方法; 2.熟悉QuartusⅡ软件的使用及设计流程; 3.掌握全加器原理,能进行多位加法器的设计。 三、实验器材 PC机一台、EDA教学实验系统一台、下载电缆一根(已接好)、导线若干 四、实验要求 1、用VHDL设计一个四位并行全加器; 2、用图形方式构成一个八位全加器的顶层文件; 3、完成八位全加器的时序仿真。 五、实验原理与内容 1、原理: 加法器是数字系统中的基本逻辑器件。例如:为了节省资源,减法器和硬件乘法器都可由加法器来构成。但宽位加法器的设计是很耗费资源的,因此在实际的设计和相关系统的开发中需要注意资源的利用率和进位速度等两方面的问题。多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。 实验表明,4 位二进制并行加法器和串行级联加法器占用几乎相同的资源。这样,多位数加法器由4 位二进制并行加法器级联构成是较好的折中选择。因此本实验中的8 位加法器采用两个4位二进制并行加法器级联而成。

2、实现框图: 1)四位加法器 四位加法器可以采用四个一位全加器级连成串行进位加法器,实现框图如下图所示,其中CSA为一位全加器。显然,对于这种方式,因高位运算必须要等低位进位来到后才能进行,因此它的延迟非常可观,高速运算肯定无法胜任。 通过对串行进位加法器研究可得:运算的延迟是由于进位的延迟。因此,减小进位的延迟对提高运算速度非常有效。下图是减少了进位延迟的一种实现方法。可见,将迭代关系去掉,则各位彼此独立,进位传播不复存在。因此,总的延迟是两级门的延迟,其高速也就自不待言。 2)八位加法器 用两个并行四位加法器实现一个八位加法器的框图如下:

数字电子钟课程设计实验报告

中北大学 信息与通信工程学院 通信工程专业 《电子线路及系统》课程设计任务书2016/2017 学年第一学期 学生姓名:张涛学号: 李子鹏学号: 课程设计题目:数字电子钟的设计 起迄日期:2017年1月4日~2017年7月10日 课程设计地点:科学楼 指导教师:姚爱琴 2017年月日 课程设计任务书

中北大学 信息与通信工程学院 通信工程专业 《电子线路及系统》课程设计开题报告2016/2017 学年第一学期 题目:数字电子钟的设计 学生姓名:张涛学号: 李子鹏学号:

指导教师:姚爱琴 2017 年 1 月 6 日 中北大学 信息与通信工程学院 通信工程专业 《电子线路及系统》课程设计说明书2016/2017 学年第二学期 题目:数字电子钟的设计 学生姓名:张涛学号: 李子鹏学号: 指导教师:姚爱琴 2017 年月日

目录 1 引言 (6) 2 数字电子钟设计方案 (6) 2.1 数字计时器的设计思想 (6) 2.2数字电路设计及元器件参数选择 (6) 2.2.2 时、分、秒计数器 (7) 2.2.3 计数显示电路 (8) 2.2.5 整点报时电路 (10) 2.2.6 总体电路 (10) 2.3 安装与调试 (11) 2.3.1 数字电子钟PCB图 (11) 3 设计单元原理说明 (11) 3.1 555定时器原理 (12) 3.2 计数器原理 (12) 3.3 译码和数码显示电路原理 (12) 3.4 校时电路原理 (12) 4 心得与体会 (12) 1 引言 数字钟是一种用数字电子技术实现时,分,秒计时的装置,具有较高的准确性和直观性等各方面的优势,而得到广泛的应用。此次设计数字电子钟是为了了解数字钟的原理,在设计数字电子钟的过程中,用数字电子技术的理论和制作实践相结合,进一步加深数字电子技术课程知识的理解和应用,同时学会使用Multisim电子设计软件。 2数字电子钟设计方案 2.1 数字计时器的设计思想 要想构成数字钟,首先应选择一个脉冲源——能自动地产生稳定的标准时间脉冲信号。而脉冲源产生的脉冲信号地频率较高,因此,需要进行分频,使得高频脉冲信号变成适合于计时的低频脉冲信号,即“秒脉冲信号”(频率为1Hz)。经过分频器输出的秒脉冲信号到计数器中进行计数。由于计时的规律是:60秒=1分,60分=1小时,24小时=1天,就需要分别设计60进制,24进制计数器,并发出驱动信号。各计数器输出信号经译码器、驱动器到数字显示器,是“时”、“分”、“秒”得以数字显示出来。 值得注意的是:任何记时装置都有误差,因此应考虑校准时间电路。校时电路一般

8位全加器实验报告

实验1 原理图输入设计8位全加器 一、实验目的: 熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA软件进行电子线路设计的详细流程。 二、原理说明: 一个8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现。即将低位加法器的进位输出cout与其相邻的高位加法器的最低进位输入信号cin相接。而一个1位全加器可以按照本章第一节介绍的方法来完成。 三、实验内容: 1:完全按照本章第1节介绍的方法与流程,完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真。 2:建立一个更高的原理图设计层次,利用以上获得的1位全加器构成8位全加器,并完成编译、综合、适配、仿真和硬件测试。 四、实验环境: 计算机、QuartusII软件。 五、实验流程: 实验流程: 根据半加器工作原 理,建立电路并仿 真,并将元件封装。 ↓ 利用半加器构成一位 全加器,建立电路并 仿真,并将元件封 装。 ↓ 利用全加器构成8位全 加器,并完成编译、综 合、适配、仿真。 图1.1 实验流程图

六、实验步骤: 1.根据半加器工作原理建立电路并仿真,并将元件打包。(1)半加器原理图: 图1.2 半加器原理图(2)综合报告: 图1.3 综合报告: (3)功能仿真波形图4: 图1.4 功能仿真波形图

时序仿真波形图: 图1.5 时序仿真波形图 仿真结果分析:sout为和信号,当a=1,b=0或a=0,b=1时,和信号sout为1,否则为0.当a=b=1时,产生进位信号,及cout=1。 (4)时序仿真的延时情况: 图1.6 时序仿真的延时情况 (5)封装元件: 图1.7 元件封装图 2. 利用半加器构成一位全加器,建立电路并仿真,并将元件封装。 (1)全加器原理图如图: 图2.1 全加器原理图

8位全加器的设计

课程设计报告 课程名称数字逻辑课程设计 课题8位全加器的设计 专业计算机科学与技术 班级1202 学号34 姓名贺义君 指导教师刘洞波陈淑红陈多 2013年12月13日

课程设计任务书 课程名称数字逻辑课程设计 课题8位全加器的设计 专业班级计算机科学与技术1202 学生姓名贺义君 学号34 指导老师刘洞波陈淑红陈多审批刘洞波 任务书下达日期:2013年12月13日 任务完成日期:2014年01月21日

一、设计内容与设计要求 1.设计内容: 本课程是一门专业实践课程,学生必修的课程。其目的和作用是使学生能将已学过的数字电子系统设计、VHDL程序设计等知识综合运用于电子系统的设计中,掌握运用VHDL或者Verilog HDL设计电子系统的流程和方法,采用Quartus II等工具独立应该完成1个设计题目的设计、仿真与测试。加强和培养学生对电子系统的设计能力,培养学生理论联系实际的设计思想,训练学生综合运用数字逻辑课程的理论知识的能力,训练学生应用Quartus II进行实际数字系统设计与验证工作的能力,同时训练学生进行芯片编程和硬件试验的能力。 题目一4线-16线译码器电路设计; 题目二16选1选择器电路设计; 题目三4位输入数据的一般数值比较器电路设计 题目四10线-4线优先编码器的设计 题目五8位全加器的设计 题目六RS触发器的设计; 题目七JK触发器的设计; 题目八D触发器的设计; 题目九十进制同步计数器的设计; 题目十T触发器的设计; 每位同学根据自己学号除以10所得的余数加一,选择相应题号的课题。 参考书目 1 EDA技术与VHDL程 序开发基础教程 雷伏容,李俊,尹 霞 清华大学出版 社 978-7-302-22 416-7 201 TP312VH/ 36 2 VHDL电路设计雷伏容清华大学出版 社 7-302-14226-2 2006 TN702/185 3 VHDL电路设计技术王道宪贺名臣? 刘伟 国防工业出版 社 7-118-03352-9 2004 TN702/62 4 VHDL 实用技术潘松,王国栋7-8106 5 7-81065-290-7 2000 TP312VH/1 5 VHDL语言100 例详解 北京理工大学A SIC研究所 7-900625 7-900625-02-X 19 99 TP312VH/3 6 VHDL编程与仿真王毅平等人民邮电出版 社 7-115-08641-9 20 00 7 3.9621/W38V 7 VHDL程序设计教程邢建平?曾繁泰清华大学出版 社 7-302-11652-0 200 5 TP312VH/27 /3

EDA设计II实验报告——多功能数字钟

『EDA设计II』 课程实验报告 姓名 学号 学院 指导教师 时间 2011年 05月

多功能数字钟 摘要:本实验利用Quartus II软件设计多功能数字钟并下载到Smart SOPC实验系统,实现校分、校时、清零、保持和整点报时等多种基本功能,以及闹钟等附加功能。本实验首先通过Quartus II 软件对各模块进行原理图设计,并进行仿真调试,最后下载至实验平台验证其功能。 关键词:多功能数字钟Quartus II软件仿真封装校分校时清零保持整点报时闹钟 Abstract:The experiment is to design a multi-purpose digital clock by Quartus II and then download to the test system of Smart SOPC. It can realize many functions such as minute adjusting, hour adjusting, resetting, keeping and reporting time on integral hour. Apart from this, it can also be used as a alarm clock. First of all, we design the schematic diagram of every part. In addition, we simulate through Quartus II. At last, we download it to the tests platform and test the function. Key words:multi-purpose digital clock Quartus II simulate seal minute- adjusting hour adjusting resetting keeping reporting time on integral hour alarm clock

EDA 1位全加器实验报告

南华大学 船山学院 实验报告 (2009 ~2010 学年度第二学期) 课程名称EDA 实验名称1位全加器 姓名学号200994401 专业计算机科学与 班级01 技术 地点8-212 教师

一、实验目的: 熟悉MAX+plus 10.2的VHDL 文本设计流程全过程 二、实验原理图: ain cout cout ain bin sum cin bin sum cin f_adder or2a f e d u3 u2u1b a c co so B co so B h_adder A h_adder A 三、实验代码: (1)LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; ENTITY f_adder IS PORT (ain ,bin ,cin : IN STD_LOGIC; cout ,sum : OUT STD_LOGIC ); END ENTITY f_adder; ARCHITECTURE fd1 OF f_adder IS COMPONENT h_adder PORT ( a ,b : IN STD_LOGIC; co ,so : OUT STD_LOGIC); END COMPONENT ; COMPONENT or2a PORT (a ,b : IN STD_LOGIC; c : OUT STD_LOGIC); END COMPONENT ; SIGNAL d ,e ,f : STD_LOGIC; BEGIN u1 : h_adder PORT MAP(a=>ain ,b=>bin ,co=>d ,so=>e); u2 : h_adder PORT MAP(a=>e , b=>cin , co=>f ,so=>sum); u3 : or2a PORT MAP(a=>d , b=>f , c=>cout);

eda数字时钟实验报告

EDA数字时钟电工电子实习 实验报告 姓名 班级 学号20

一、实验目的: 1、掌握多位计数器相连的设计方法。 2、掌握十进制、六十进制和二十四进制计数器的设计方法。 3、巩固数码管的驱动原理及编程方法。 4、掌握CPLD技术的层次化设计方法。 二、实验要求: 基本要求:具有时、分、秒计数显示功能,以二十四小时循环计时。 扩展要求:具有整点报时功能。 三、实验原理: 计数时钟由模60秒计数器、模60分计数器、模24小时计数器、蜂鸣器(用于整点报时)、分/时设定模块、输出显示模块构成,秒计数模块的进位输出为分钟计数模块的进位输入,分钟计数模块的进位输出为小时计数模块的进位输入。 74163功能简介:

图1 图2 由图1可知,74163的脉冲上升沿的时候工作。 四、实验过程

1.模60计数器(如图3) 图3 由74163实现计数功能,第一片74163实现10进制,即做0-9的循环,9即二进制的1001,化简可得当q[0]与q[3]同时为1的时候进行清零。第二片74163实现6进制,即做0-5的循环,5即二进制的111,化简可得当q[4]与q[6]同时为1的时候进行清零,同时第一片74163的进位端作为第二片的脉冲端。这样就可实现60进制。60进制计数器用于秒计数器和分计数器,秒个位的进位端作为秒十位的脉冲端秒十位的进位端作为分个位的脉冲端,分个位的进位端作为分十位的脉冲端。 2.模24计数器(如图4) 图4 分十位的进位端作为时个位的脉冲端,时个位的进位端作为时十位的脉冲端。因为24进制的特殊性,当十位是0和1的时候,个位做十进制循环,即0-9,9的二进制为1001;当十位是2的时候,个位做0-3的循环。而十位做0-2的循环。2的二进制为0010,3的二进制为0011。所以第一片74163不仅要在q[14]与q[17]同时为1的时候清零,还要在第二片74163的q[19]、第一片的q[14]、q[15]同时为1(即23时)做清零。第二片是3进制,在q[19]=1的时候进行清零。

EDA设计实验报告

摘要 通过实验学习和训练,掌握基于计算机和信息技术的电路系统设计和仿真方法。要求: 1. 熟悉multisim软件的使用,包括电路图编辑、虚拟仪器仪表的使用和掌握常见电路分析 方法。2. 能够运用multisim软件对模拟电路进行设计和性能分析,掌握eda设计的基本方 法和步骤。multisim常用分析方法:直流工作点分析、直流扫描分析、交流分析。掌握设计 电路参数的方法。复习巩固单级放大电路的工作原理,掌握静态工作点的选择对电路的影响。 了解负反馈对两级放大电路的影响,掌握阶梯波的产生原理及产生过程。 关键字:电路仿真 multisim 负反馈阶梯波 目次 实验一 (1) 实验二............................................................................................. 11 实验三 (17) 实验一单级放大电路的设计与仿真 一、实验目的 1. 设计一个分压偏置的单管电压放大电路,要求信号源频率5khz(峰值10mv) , 负载电阻5.1kω,电压增益大于50。 2. 调节电路静态工作点(调节电位计),观察电路出现饱和失真和截止失真的输出 信号波形,并测试对应的静态工作点值。 3. 调节电路静态工作点(调节电位计),使电路输出信号不失真,并且幅度尽可能 大。在此状态下测试: ①电路静态工作点值; ②三极管的输入、输出特性曲线和? 、 rbe 、rce值;③电路的输入电阻、输出电 阻和电压增益;④电路的频率响应曲线和fl、fh值。 二、实验要求 1. 给出单级放大电路原理图。 2. 给出电路饱和失真、截止失真和不失真且信号幅度尽可能大时的输出信号波形 图,并给出三种状态下电路静态工作点值。 3. 给出测试三极管输入、输出特性曲线和? 、 rbe 、rce值的实验图,并给出 测试结果。 4. 给出正常放大时测量输入电阻、输出电阻和电压增益的实验图,给出测试结果 并和理论计算值进行比较。 5. 给出电路的幅频和相频特性曲线,并给出电路的fl、fh值。 6. 分析实验结果。 三、实验步骤 实验原理图: 饱和失真时波形: 此时静态工作点为: 所以,i(bq)=4.76685ua i(cq)=958.06700ua u(beq)=0.62676v u(ceq)=0.31402v 截止失真时波形: 此时静态工作点为: 所以,i(bq)=2.07543ua i(cq)=440.85400ua u(beq)=0.60519v u(ceq)=5.54322v 最大不失真时波形:篇二:eda课程设计实验报告电子电工实习 华北电力大学

用原理图输入方法设计8位全加器

实验一 用原理图输入方法设计8位全加器 1.实验目的和要求 本实验为综合性实验,综合了简单组合电路逻辑,MAX+plus 10.2的原理图输入方法, 层次化设计的方法等内容。其目的是通过一个8位全加器的设计熟悉EDA 软件进行电子线路设计的详细流程。学会对实验板上的FPGA/CPLD 进行编程下载,硬件验证自己的设计项目。 2.实验原理 1位全加器可以用两个半加器及一个或门连接而成,半加器原理图的设计方法很多,我们用一个与门、一个非门和同或门(xnor 为同或符合,相同为1,不同为0)来实现。先设计底层文件:半加器,再设计顶层文件全加器。 (1) 半加器的设计: 半加器表达式:进位:co=a and b 和:so=a xnor ( not b ) 半加器原理图如下: (2) 全加器的设计: 全加器原理图如下: 3.主要仪器设备(实验用的软硬件环境) 实验的硬件环境是: 微机 I113co a so b 1 0101 0110001 10 0co so b a not xnor2 and2 I113ain cout cout ain bin sum cin bin sum cin f_adder or2a f e d u3 u2 u1 b a c co so B co so B h_adder A h_adder A

EDA实验开发系统 ZY11EDA13BE 并口延长线,JTAG延长线 实验的软件环境是: MAX+plus 10.2 4.操作方法与实验步骤 ●按照4.1 节介绍的方法与流程,完成半加器和全加器的设计,包括原理图输入、编译、综合、适配、仿真、实验板上的硬件测试,并将此全加器电路设置成一个硬件符号入库。 ●建立一个更高的原理图设计层次,利用以上获得的1位全加器构成8位全加器,并完成编译、综合、适配、仿真、硬件测试。 5.实验内容及实验数据记录 1.设计半加器: 用原理图输入的方法输入一个半加器的逻辑图,如图所示: 然后在assign里头的device里头根据试验箱的芯片设置Decices,接着就设置输入输出荧脚的输入端和输出端,设置如表1所示: 表1.半加器引脚端口设置 引脚名称设置端口 ain input Pin=45 bin input Pin=46 co output Pin=19 so output Pin=24 然后Save,名称为h_add.gdf,再save & Compile。 结果如图所示:

EDA实验实验报告

数字eda实验实验报告 学院:计算机科学与工程学院专业:通信工程学 号: 0941903207 姓名:薛蕾指导老 师:钱强 实验一四选一数据选择器的设计 一、实验目的 1、熟悉quartus ii软件的使用。 2、了解数据选择器的工作原理。 3、熟悉eda开发 的基本流程。 二、实验原理及内容 实验原理 数据选择器在实际中得到了广泛的应用,尤其是在通信中为了利用多路信号中的一路, 可以采用数据选择器进行选择再对该路信号加以利用。从多路输入信号中选择其中一路进行 输出的电路称为数据选择器。或:在地址信号控制下,从多路输入信息中选择其中的某一路 信息作为输出的电路称为数据选择器。数据选择器又叫多路选择器,简称mux。 4选1数据 选择器: (1)原理框图:如右图。 d0 、d1、d2、d3 :输入数据 a1 、a0 :地址变量 由地址码决定从4路输入中选择哪1路输出。 (2)真值表如下图: (3)逻辑图 数据选择器的原理比较简单,首先必须设置一个选择标志信号,目的就是为了从多路信 号中选择所需要的一路信号,选择标志信号的一种状态对应着一路信号。在应用中,设置一 定的选择标志信号状态即可得到相应的某一路信号。这就是数据选择器的实现原理。 三.实验内容 1、分别采用原理图和vhdl语言的形式设计4选1数据选择器 2、对所涉及的电路进行 编译及正确的仿真。电路图: 四、实验程序 library ieee; use ieee.std_logic_1164.all; entity mux4 is port( a0, a1, a2, a3 :in std_logic; s :in std_logic_vector (1 downto 0); y :out std_logic ); end mux4; architecture archmux of mux4 is begin y <= a0 when s = 00 else --当s=00时,y=a0 a1 when s = 01 else --当s=01时,y=a1 a2 when s = 10 else --当s=10时,y=a2 a3; --当s取其它值时,y=a2 end archmux; 五、运行结果 六.实验总结 真值表分析: 当js=0时,a1,a0取00,01,10,11时,分别可取d0,d1,d2,d3. 篇二:eda实验报告模版 《eda技术》实验报告

EDA课程设计----八位二进制全加器

EDA设计说明书 课程名称:EDA技术实用教程 设计题目:八位二进制全加器 院系:电子信息与电气工程学院学生姓名: 学号: 专业班级: 指导教师:李响 2011 年6 月1

1. 设计目的 熟悉利用QuartusⅡ的原理图输入法设计简单的组合电路,掌握层次化设计的方法,并通过一个八位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。 2. 设计原理 2.1 一位全加器的原理 一位全加器可以用两个半加器及一个或门连接而成,因此需要首先完成半加器的设计。在本设计中,将采用原理图输入法来完成设计。 一位全加器的设计步骤: ①为本项工程设计建立文件夹; ②输入设计项目和存盘; ③将设计项目设计成可调用的元件; ④设计全加器顶层文件; ⑤将设计项日设置成工程和时序仿真。 2.2 八位全加器的原理 一个八位全加器可以由八个一位全加器构成,加法器之间的进位可以用串行方式实现,即将低位加法器的进位输出cout 与相邻的高位加法器的最低进位输入信号cin 相接。 3. 设计方案与仿真 3.1 一位全加器的设计与仿真 全加器的实现是以半加器的实现为基础的,因此,要设计全加器应首先设计一个一位的半加器。半加器的实现方案为: ①为此项工程建立文件夹; ②在基本元件库中,选中需要的元件,将元件(包含元件and2、not 、xnor 和输 入输出引脚input、output)调入原理图编辑窗口中;

③将己设计好的原理图文件存盘; ④将所设计的半加器设置成可调用的元件。 用原理图输入法所设计的半加器原理图如图3-1所示,利用QuartusⅡ软件平台,根据图3-1所示电路,可生成一个半加器元件符号,如图3-2所示。在半加器的基础上,为了建立全加器的顶层文件,必须再打开一个原理图编辑窗口,方法同上。其中,所选择的元件包含半加器、或门和输入输出引脚,由此可得到如图3-3所示的全加器原理图;进而可生成个全加器元件符号,如图3-4所示。 图3-1 半加器原理图图3-2 半加器元件符号 图3-3 全加器原理图图3-4 全加器元件符号按照一位全加器原理图连接电路,通过编译、仿真所得的波形图如图3-5所示: 图3-5 一位全加器时序仿真波形 根据图3-5可知,当输入信号ain 、bin 、cin 全是低电平时,输出信号sum 和cout 全是低电平;当输入信号ain 、bin 、cin 中有且只有一个为高电平时,输出信号sum 为高电平,输出信号cout 为低电平;当输入信号ain 、bin 、cin 中有两个为

EDA数字钟实验报告

目录 1.设计思路—————————————————————(3) 1.1总体结构——————————————————(3) 2.方案论证与选择——————————————————(3) 3.单元模块设计部分—————————————————(3)3.1 CNT10 模块的设计———————————————(4)3.2 CNT6 模块的设计———————————————(5)3.3 CNT101模块的设计———————————————(6)3.4 CNT61模块的设计———————————————(7) 3.5 CNT23模块的设计———————————————(8) 4.系统仿真—————————————————————(9) 4.1数字钟的引脚锁定———————————————(9) 4.2数字钟原理图————————————————(12) 4.3数字钟仿真图————————————————(10) 4.4数字钟编译报告———————————————(11) 5.参考文献————————————————————(13)

EDA数字钟设计 中文摘要: 数字钟学习的目的是掌握各类计数器及它们相连的设计方法;掌握多个数码管显示的原理与方法;掌握FPGA技术的层次化设计方法;掌握用VHDL语言的设计思想以及整个数字系统的设计。此数字钟具有时,分,秒计数显示功能,以24小时为计数循环;能实现清零,调节小时,分钟以及整点报时的功能。 关键词:数字钟,计数器,,FPGA,VHDL 1.设计思路 基于VHDL语言,用Top—To--Down的思想进行设计。 1.1 确定总体结构,如图1-1所示。 图1-1 2. 方案论证与选择 方案:设置小时和分,输出整点报时信号和时,分,秒信号。方案采用自顶向下的设计方法,它由秒计数模块,分计数模块,小时计数模块和顶层模块四部分组成。 3. 单元模块设计部分 RES是整个系统的复位键,低电平有效,复位时,各个输出都为零,时间显示0时0分0秒;clk是输入时钟,提供秒信号,上升沿触发,每出发一次,时间增加一秒;HRTMP,MIN10TMP,MINTMPKEYI可以分别设置小时位,10分位,分位,起到调时的作用,高电平有效,有效时,每来一个CLK时钟(1s),所对应的位都将以各自的计数循环; RING是整点报时。

8位全加器设计

基于原理图的8位全加器设计 实验目的:熟悉利用Quartus II的原理图输入方法设计简单的组合电路,掌握层次化设 计的方法,并通过一个8位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。 实验原理:一个8位全加器可以由8个1位全加器串行构成,即将低位加法器的进位输 出cout与相临的高位加法器的最低位输入信号cin相接。 试验任务:1.完成半加器和全加器的设计。 2.建立一个更高层次的原理图设计,利用以上获得的1位全加器构成8位全加器,完成编译、综合、适配、仿真和硬件测试。 实验步骤: 一、1位全加器设计 1.建立工程文件夹adder,路径d:\adder。 2.输入设计项目和存盘 原理图编辑输入流程如下: (1)打开Quartus II,选择file—>new命令,在弹出的窗口中选择block diagram/schematic file 选项,单击ok按钮后将打开原理图编辑窗口。 (2)在编辑窗口中的任何一个位置上右击,将弹出快捷菜单,选择inset—>symbol命令,将弹出元件输入对话框。 (3)单击“…”按钮,找到基本元件库路径d:/altera/90/quartus/libraries/primitives/logic项(假设软件安装在D盘),选中需要的元件,单击“打开”按钮,此元件即显示在窗口中,然后单击symbol窗口中的ok按钮,即可将元件调入原理图编辑窗口中。也可以在name栏输入需要的元件名。调入好元件和引脚后,连接好电路,再输入各引脚名。 (4)选择file—>save as命令,选择刚才为自己的工程建立的目录d:\adder,将已设计好的原理图取名为h_adder.bdf,并存盘此文件夹内。 3.将设计好的项目设置成可调用的元件 为了构成全加器的顶层设计,必须将以上设计的半加器h_adder.bdf设置成可调用的元件。在打开半加器原理图文件的情况下,选择file—>create/update—>create symbol file for current file命令,即可将当前文件h_adder.bdf变成一个元件符号存盘,以待高层次设计中调用。4.设计全加器顶层文件 打开一个原理图编辑窗口,方法同前。在新打开的原理图窗口中双击,在弹出的窗口中选择project选项,选择h_adder.bdf,并调入其他元件,连接好电路。以f_adder.bdf名存在同一路径d:\adder中。 二、8位全加器设计 1.将刚设计好的1位全加器设置成可调用的元件,方法同上。 2.调入元件,连接电路图,以8f_adder.bdf保存于同一路径d:\adder中的文件夹中。 3.将顶层文件8f_adder.bdf设置为工程。 4.编译与仿真 原理图与仿真波形分析:

数字钟实验报告

EDA技术课程设计 ——多功能数字钟 学院:城市学院 专业、班级:电子C154 姓名:高阳夏岩 学号:158102 58128 指导老师:安亚军 2017年12月

一实验目的 1、具有时、分、秒记数显示功能,以24小时循环计时。 2、要求数字钟具有清零、调节小时、分钟功能。 3、具有整点报时,整点报时的同时LED灯花样显示 二实验原理 1时钟计数:完成时、分、秒的正确计时并且显示所计的数字;对秒、分——60进制计数,即从0到59循环计数,时钟——24进制计数,即从0到23循环计数,并且在数码管上显示数值。 2时间设置:手动调节分钟、小时,可以对所设计的时钟任意调时间,这样使数字钟真正具有使用功能。我们可以通过实验板上的键7和键4进行任意的调整,因为我们用的时钟信号均是1HZ的,所以每LED灯变化一次就来一个脉冲,即计数一次。 3清零功能:reset为复位键,低电平时实现清零功能,高电平时正常计数。可以根据我们自己任意时间的复位。 4蜂鸣器在整点时有报时信号产生,蜂鸣器报警。产生“滴答.滴答”的报警声音。 5LED灯在时钟显示时有花样显示信号产生。即根据进位情况,LED不停的闪烁,从而产生“花样”信号 三实验内容 1时钟记数部分 1)小时部分 其VHDL描述如下 编译,无误。 经仿真,其波形如下

2)分钟部分 其VHDL描述如下 编译,无误。 经仿真,其波形如下 3)秒部分 其VHDL描述如下

编译,无误。 经仿真,其波形如下 2整点报时部分,其VHDL描述如下 编译,无误。

经仿真,其波形如下 3驱动8位八段共阴扫描数码管的片选驱动信号输出部分 其VHDL描述如下 编译,无误。 经仿真,其波形如下 4驱动八段字形译码输出部分 该模块功能:信号输入后,模块驱动八段字形译码输出,A,B,C,D,E,F,G分别接八段共阴级数码管7个接口,即有字形输出。

4位全加器实验报告.doc

四位全加器 11微电子黄跃1117426021 【实验目的】 采用modelsim集成开发环境,利用verilog硬件描述语言中行为描述模式、结构描述模式或数据流描述模式设计四位进位加法器。 【实验内容】 加法器是数字系统中的基本逻辑器件。多位加法器的构成有两种方式:并行进位和串行进位方式。并行进位加法器设有并行进位产生逻辑,运算速度快;串行进位方式是将全加器级联构成多位加法器。通常,并行加法器比串行级联加法器占用更多的资源,并且随着位数的增加,相同位数的并行加法器比串行加法器的资源占用差距也会越来越大。 实现多位二进制数相加的电路称为加法器,它能解决二进制中1+1=10的功能(当然还有 0+0、0+1、1+0). 【实验原理】 全加器 除本位两个数相加外,还要加上从低位来的进位数,称为全加器。图4为全 加器的方框图。图5全加器原理图。被加数A i 、加数B i 从低位向本位进位C i-1 作 为电路的输入,全加和S i 与向高位的进位C i 作为电路的输出。能实现全加运算 功能的电路称为全加电路。全加器的逻辑功能真值表如表2中所列。 信号输入端信号输出端 A i B i C i S i C i 0 0 0 0 0 0 0 1 1 0 0 1 0 1 0 0 1 1 0 1 1 0 0 1 0 1 0 1 0 1 1 1 0 0 1 1 1 1 1 1

表2 全加器逻辑功能真值表 图4 全加器方框图 图5 全加器原理图 多位全加器连接可以是逐位进位,也可以是超前进位。逐位进位也称串行进位,其逻辑电路简单,但速度也较低。 四位全加器 如图9所示,四位全加器是由半加器和一位全加器组建而成: 图9 四位全加器原理图 【实验步骤】 (1)建立新工程项目: 打开modelsim软件,进入集成开发环境,点击File→New project建立一

eda实验报告

一位全加器 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; -- Uncomment the following lines to use the declarations that are -- provided for instantiating Xilinx primitive components. --library UNISIM; --use UNISIM.VComponents.all; entity adder is port(a,b,cin:in std_logic; co,so:out std_logic); end adder; architecture Behavioral of adder is signal temp1,temp2:std_logic; begin temp1<= a xor b; temp2<= temp1 and cin; so<= temp1 xor cin; co<= temp2 OR (a AND b); end Behavioral; 四位全加器 library IEEE; use IEEE.STD_LOGIC_1164.ALL; use IEEE.STD_LOGIC_ARITH.ALL; use IEEE.STD_LOGIC_UNSIGNED.ALL; -- Uncomment the following lines to use the declarations that are -- provided for instantiating Xilinx primitive components. --library UNISIM; --use UNISIM.VComponents.all; entity counter10 is

FPGA 8位全加器的原理图设计

3-8. 在QuartusII中用原理图输入法设计8位全加器 1、实验目的:熟悉利用QuartusⅡ的原理图输入方法设计简单组合电路,掌握层次化设计的方法,并通过一个8位全加器的设计把握利用EDA软件进行原理图输入方式的电子线路设计的详细流程。 2、实验原理:先由一个半加器构成一个全加器,8位全加器可以由8个1位全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相临的高位加法器的最低进位输入信号cin 相接。 3、实验内容及过程: 在D盘下建立一个新的文件夹为ADDER8。 本设计的思路是先设计1个1位半加器,因此建立新建文件夹D:/ ADDER8/h_adder;要利用1位的半加器构造1位的全加器,因此建立新建文件夹D:/ADDER8/f_adder;要利用1位的全加器构造8位的全加器,因此建立新建文件夹D:/ADDER8/adder8; (1)、用原理图输入法构造1位半加器 打开QuartusII软件,选择菜单File-New,在弹出的New对话框中选择原理图文件编辑输入项Block Diagram/Schematic File(如图4-1所示),按ok按钮后将打开原理图编辑窗口。 (2)建立一个初始原理图。在编辑窗口中的任何一个位置上右击鼠标,选择输入原件项Insert-Symbol,或者直接双击原理图编辑窗口,于是将弹出如图4-2所示原件对话框。在坐下的Name栏键入输入引脚符号input。然后单击ok按钮。即可将元件调入原理图编辑窗口。 图4-1 图4-2 (3)原理图文件存盘。选择菜单File-Save As,将此原理图文件存于刚才建立的目录D:/ ADDER8/h_adder 中,取文件名为:h_adder.bdf。然后将h_adder.bdf设定为工程,创建工程。 (4)绘制半加器原理图。在工程管理窗口,双击工程名,再次进入原理图编辑窗。双击原理图任何位置,再次弹出4-2的对话框。分别在Name栏键入原件名and2、not、xnor和输出引脚output,并用单击拖动的方法连接电路。然后分别在input和output引脚的PIN NAME上双击使其变为黑色,再用键盘输入各引脚名:a、b、co和so。最后作为本工程的顶层原理设计图如4-3。 图4-3 (5)仿真测试半加器。全程编译后,对此半加器工程进行方针测试,仿真波形如下图所示4-4。

数字时钟设计实验报

电子课程设计题目:数字时钟

数字时钟设计实验报告 一、设计要求: 设计一个24小时制的数字时钟。 要求:计时、显示精度到秒;有校时功能。采用中小规模集成电路设计。 发挥:增加闹钟功能。 二、设计方案: 由秒时钟信号发生器、计时电路和校时电路构成电路。 秒时钟信号发生器可由振荡器和分频器构成。 计时电路中采用两个60进制计数器分别完成秒计时和分计时;24进制计数器完成时计时;采用译码器将计数器的输出译码后送七段数码管显示。 校时电路采用开关控制时、分、秒计数器的时钟信号为校时脉冲以完成校时。 三、电路框图: 图一 数字时钟电路框图 四、电路原理图: (一)秒脉冲信号发生器 秒脉冲信号发生器是数字电子钟的核心部分,它的精度和稳定度决定了数字钟的质量。由振荡器与分频器组合产生秒脉冲信号。 ? 振荡器: 通常用555定时器与RC 构成的多谐振荡器,经过调整输出1000Hz 脉冲。 ? 分频器: 分频器功能主要有两个,一是产生标准秒脉冲信号,一是提供功能 扩展电路所需要的信号,选用三片74LS290进行级联,因为每片为1/10分频器,三片级联好获得1Hz 标准秒脉冲。其电路图如下: 译码器 译码器 译码器 时计数器 (24进制) 分计数器 (60进制) 秒计数器 (60进制) 校 时 电 路 秒信号发生器

图二秒脉冲信号发生器 (二)秒、分、时计时器电路设计 秒、分计数器为60进制计数器,小时计数器为24进制计数器。 ?60进制——秒计数器 秒的个位部分为逢十进一,十位部分为逢六进一,从而共同完成60进制计数器。当计数到59时清零并重新开始计数。秒的个位部分的设计:利用十进制计数器CD40110设计10进制计数器显示秒的个位。个位计数器由0增加到9时产生进位,连在十位部计数器脉冲输入端CP,从而实现10进制计数和进位功能。利用74LS161和74LS11设计6进制计数器显示秒的十位,当十位计数器由0增加到5时利用74LS11与门产生一个高电平接到个位、十位的CD40110的清零端,同时产生一个脉冲给分的个位。其电路图如下: 图三60进制--秒计数电路

八位加法器设计实验报告

实验四:8位加法器设计实验 1.实验目的:熟悉利用quartus原理图输入方法设计简单组合电路,掌握层次化设计方法。 2.实验原理:一个八位加法器可以由八个全加器构成,加法器间的进位可以串行方式实现,即将低位加法器的进位输出cout与相邻的高位加法器的最低进位输入信号cin相接。 3.实验任务:完成半加器,全加器,八位加法器设计,使用例化语句,并将其设计成一个原件符号入库,做好程序设计,编译,程序仿真。 1)编译成功的半加器程序: module h_adder(a,b,so,co); input a,b; output so,co; assign so=a^b; assign co=a&b; endmodule 2)编译成功的全加器程序: module f_adder(ain,bin,cin,cout,sum); output cout,sum;input ain,bin,cin; wire net1,net2,net3; h_adder u1(ain,bin,net1,net2); h_adder u2(.a(net1),.so(sum),.b(cin),.co(net3));

or u3(cout,net2,net3); endmodule 3)编译成功的八位加法器程序: module f_adder8(ain,bin,cin,cout,sum); output [7:0]sum; output cout;input [7:0]ain,bin;input cin; wire cout0, cout1, cout2 ,cout3, cout4,cout5,cout6; f_adder u0(.ain(ain[0]),.bin(bin[0]),.cin(cin),.sum(sum[0]),.cout(cout0)); f_adder u1(.ain(ain[1]),.bin(bin[1]),.cin(cout0),.sum(sum[1]),.cout(cout1 )); f_adder u2(.ain(ain[2]),.bin(bin[2]),.cin(cout1),.sum(sum[2]),.cout(cout2 )); f_adder u3(.ain(ain[3]),.bin(bin[3]),.cin(cout2),.sum(sum[3]),.cout(cout3 )); f_adder u4(.ain(ain[4]),.bin(bin[4]),.cin(cout3),.sum(sum[4]),.cout(cout4 )); f_adder