六层板pcb布线经验-飞思卡尔工程师

Freescale Semiconductor

Application Note

This application note is a design guide to assist the customer in creating a low-layer, low-cost, PCB design when using the MPC8544E device. Key items of discussion include assumed PCB stackup, power delivery, and proper signal referencing. Additionally, layout plots for the device fan-out are also included.

NOTE

The schematic and Gerber data shown within

this application note are intended merely to

demonstrate the fan-out and power delivery

strategy necessary to achieve a six-layer

PCB. The schematic and Gerber data does not

include all the decoupling, nor do they show

all the necessary pull-ups and AC caps

required outside the BGA fan-out area. This

level of detail is captured as part of the

MPC8544E development system.

Document Number:AN3535

Rev. 0, 2/2008

Contents

1.References . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2

2.Ballmap Organization . . . . . . . . . . . . . . . . . . . . . . . . . 2

3.Interface Support in Six Layers . . . . . . . . . . . . . . . . . 3

4.Board Stackup Considerations . . . . . . . . . . . . . . . . . . 4

5.Signal Breakout . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 6

6.Via Usage . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 9

7.Power and Ground Strategy . . . . . . . . . . . . . . . . . . . 10

8.Signal Layer Gerber Plot . . . . . . . . . . . . . . . . . . . . . 20

9.Fan-Out Schematics . . . . . . . . . . . . . . . . . . . . . . . . . 24

10.Current Delivery in the BGA Field . . . . . . . . . . . . . . 39

11.Revision History . . . . . . . . . . . . . . . . . . . . . . . . . . . . 43

A Strategy for Routing the MPC8544E in a Six-Layer PCB

by Michael George

NMG Applications

Freescale Semiconductor, Inc.

Austin, Texas

References

1References

Table 1 lists references mentioned in this application note, as well as useful resources for further reading.

2Ballmap Organization

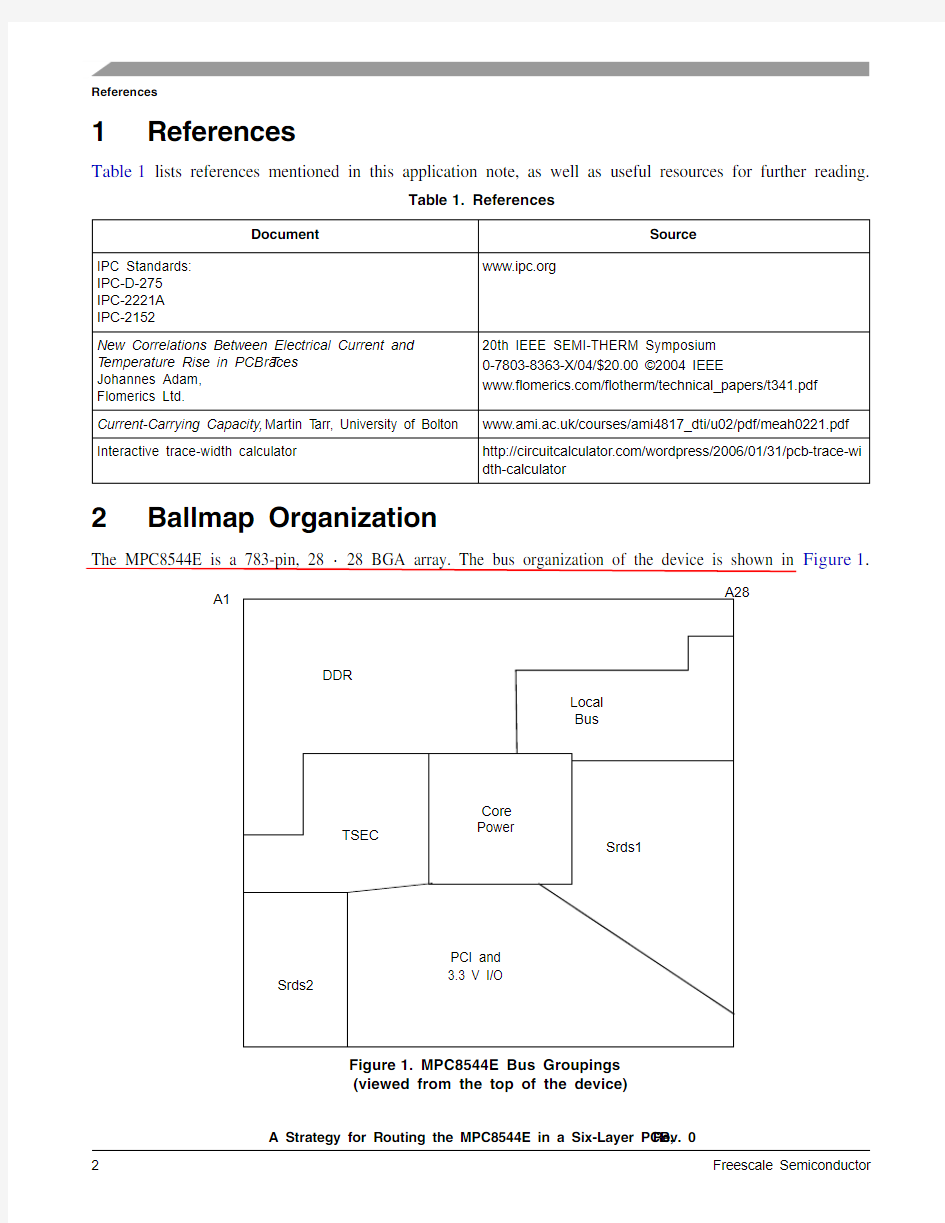

The MPC8544E is a 783-pin, 28 × 28 BGA array. The bus organization of the device is shown in Figure 1.

Figure 1. MPC8544E Bus Groupings (viewed from the top of the device)

Table 1. References

Document

Source

IPC Standards:IPC-D-275IPC-2221A IPC-2152

https://www.360docs.net/doc/cb18481152.html,

New Correlations Between Electrical Current and T emperature Rise in PCB T races Johannes Adam,Flomerics Ltd.

20th IEEE SEMI-THERM Symposium 0-7803-8363-X/04/$20.00 ?2004 IEEE

https://www.360docs.net/doc/cb18481152.html,/flotherm/technical_papers/t341.pdf Current-Carrying Capacity, Martin T arr, University of Bolton https://www.360docs.net/doc/cb18481152.html,/courses/ami4817_dti/u02/pdf/meah0221.pdf Interactive trace-width calculator

https://www.360docs.net/doc/cb18481152.html,/wordpress/2006/01/31/pcb-trace-wi dth-calculator

TSEC

Srds2

PCI and 3.3 V I/O

Srds1

Local Bus

DDR

A1

A28

Power

Core

Interface Support in Six Layers 3Interface Support in Six Layers

Though the MPC8544E device can be fully broken out in six layers, there are a handful of signals that are not necessarily optimal from a signal integrity perspective, mainly due to splits in the reference plane. Such cases are very limited and are, therefore, manageable. Table2 enumerates the MPC8544E interfaces and indicates whether there is proper signal referencing in the six-layer PCB fan-out example.

Table2. Interface Support in Six Layers

Board Stackup Considerations

4Board Stackup Considerations

This section presents the considerations associated with the PCB and its stackup. Table 3 lists the target impedances needed in a six-layer design.

Additional considerations for the stackup include

?Must utilize high-volume, low-cost, PCB technology ?Routing density

?Aspect ratio less than 10:1?Drill size set at 10 mil

?Common core construction

?Proper signal referencing for all critical signals

4.1Stackup Proposal

Figure 2 shows a viable stackup for achieving the target impedances noted in Table 3. The target card thickness used is 62 mils (±7 mils). All signal routing is done on the inner two signal layers, or on the top and bottom signal layers. No signal routing is performed on the power and ground layers.

Table 3. Target Impedance for a Typical MPC8544E Design

Interface

Connection

Target Impedance

DDR2

MPC8544E-to-DDR2 memory

Single-ended impedance = 55–60 ΩDifferential impedance = 100 Ω ± 10%

SERDES1 (PCIe)

MPC8544E-to-PCIe connector or device Microstrip

Single-ended impedance = 60 ± 15% Differential impedance = 100 Ω ± 20%Stripline

Single-ended impedance = 60 ± 15%Differential impedance = 100 Ω ± 15%SERDES2 (SGMII/PCIe)

MPC8544E-to-connector or device

Microstrip

Single-ended impedance = 60 ± 15% Differential impedance = 100 Ω ± 20%Stripline

Single-ended impedance = 60 ± 15%Differential impedance = 100 Ω ± 15%All other MPC8544E signals

MPC8544E-to-connector or device

Single-ended interface = 55–60 Ω

Other system Items:Ethernet differential

Ethernet Phy to connector Differential impedance = 100 Ω ± 15%

Board Stackup Considerations

Figure2. Example Six-Layer PCB Stackup (Provided by Sanmina-SCI;https://www.360docs.net/doc/cb18481152.html,) Table4. Impedance Information (Provided by Sanmina-SCI; https://www.360docs.net/doc/cb18481152.html,)

Layer Type Line Width Center-to-Center

tpd

(ps/in.)

Impedance

(Ω)

1Single-ended

microstrip

5 mil n/a15355.15

1Differential

microstrip

4 mil8 mil15493.28

1Differential

microstrip

5 mil12 mil15496.54

3Single-ended

stripline

4 mil n/a17956.0

3Differential

stripline

4 mil10 mil18196.38

4Single-ended

stripline

4 mil n/a17956.0

Signal Breakout

5

Signal Breakout

5.1

Inside the BGA area

The key strategy used in breaking out the MPC8544E is centered on the use of inexpensive through-hole vias and two-track routing for the inner and bottom layers (see Figure 4). For all mainstream PCB fabrication shops, this approach is considered “production-level” technology and is capable of being produced in high volumes. Additionally, this approach produces a cheaper overall PCB design, avoiding the additional cost associated with blind- and buried-type approaches.The key items of the strategy are as follows:

?1-mm (39.3 mil) ball pitch ?Plastic substrate

?22-mil attach pad on top layer ?19-mil via pad

?28-mil anti-pad ?Single-track routing on top layer (between attach pads)?Two-track routing on inner layers and on the bottom layer —Using 4-mil traces and 4-mil space

4Differential stripline 4 mil 10 mil 18196.386Single-ended microstrip 5 mil n/a 15355.15 6Differential microstrip 4 mil 8 mil 15493.286

Differential microstrip

5 mil

12 mil

154

96.54

Table 4. Impedance Information (Provided by Sanmina-SCI; https://www.360docs.net/doc/cb18481152.html, ) (continued)

Layer Type Line Width

Center-to-Center

tpd (ps/in.)Impedance

(Ω)阻焊盘

Signal Breakout Figure3 and Figure4 show the track routing strategy used for each of the signal layers.

Figure3. Signal Routing (Top and Layer #2)

Signal Breakout

Figure4. Signal Routing (Signal Layer 3 and Bottom)

5.2Outside the BGA Area

Inside the BGA area, two-track routing limits the minimum trace width to 4 mils and the minimum spacing to 4 mils. Outside the BGA area, this is not the case. Since wider traces have less dielectric loss, the designer may find it useful to use larger trace widths once outside the via array. Similarly, in the cases of differential pairs, the air gaps can be adjusted as needed in order to hit desired impedance targets.

5.3Trace Spacing Outside the BGA Area

To minimize crosstalk opportunities once outside the BGA area, the spacing between differing signal groups must be observed. This spacing, denoted as ‘S,’ is based on the dielectric thickness ‘H’ (shown in Figure5). For the stackup shown in Figure2, the dielectric thickness is 4.0. Using a 3:1 spacing rule, the air gap between differing signal groups should be at least 12 mil.

Via Usage

Figure 5. Trace Spacing Outside the BGA Area

6Via Usage

For the six-layer PCB a 10-mil drill is used. A 10-mil drill has favorable cost advantages because smaller drill sizes incur additional cost. During fabrication, the drill tolerance is specified as +0/–3 mil, giving a finished hole size (FHS) of approximately 7–7.5 mil.

Using a 10-mil drill, an aspect ratio of ~ 6:1 is realized. This aspect ratio is based on an 0.062-inch board thickness and is well within the high-volume production capabilities of all mainstream PCB vendors. Figure 6 depicts the via model used for the six-layer PCB.

Figure

6. Cross Section of PCB

T race 1

T race 2

H

= Section of power plane flowing between vias = Outer layer signal tracks = Inner layer signal tracks = Via barrel/via pad copper = PCB

Legend

Power and Ground Strategy

7Power and Ground Strategy

The MPC8544E requires several power supplies for each subsystem (DDR, Ethernet, SerDes, and so forth) as well as the core itself. The total number of supplies a system needs depends on the interfaces, the interface voltages required to connect with external peripherals, and the number of those voltages that are common and sharable.

Consult the MPC8544E PowerQUICC? III Integrated Processor Hardware Specifications for accurate voltage and current requirements. For convenience, Table 5 provides a snapshot of the MPC8544E power requirements at the date of this application note. The table also reflects the unique power splits constructed in the six-layer PCB example (refer to the Power Rails column). In short, a total of six unique power rails are used.

Note that Table 5 lists the power requirements for the MPC8544E only; it does not include requirements for external devices, memory, and so forth. At the very least, additional power is needed to drive connected I/O pins, and the internal logic of the other devices often shared with the MPC8544E supplies.

7.1Power Planes

The following pictures, Figure 7 through Figure 8, highlight the power strategy used for the six-layer PCB. The ground reference for the PCB is a solid ground plane at layer 2. Since it is a solid plane with no splits, the ground layer is not shown.

Table 5. MPC8544E Power Requirements 1

1 These figures are subject to change without notice. Consult the latest

version of the MPC8544E PowerQUICC? III Integrated Processor Hardware Specifications.

Power Rails Symbol Typical Voltage Tolerance P MAX Core power

V DD_CORE AV DD_CORE AV DD_PLAT AV DD_PCI AV DD_LBIU AV DD_SRDS AV DD_SRDS2

1.0 V

±50 mV

7.8 W

SerDes SV DD XV DD 1.0 V ±50 mV 0.71W DDR2 bus

GV DD

1.8 V ±90 mV

2.5 W E

thernet LV DD

TV DD 2.5 V ±125 mV 0.24 W Local bus BV DD 3.3 V ±125 mV 0.33 W Misc/PCI

OV DD

3.3 V

±125 mV

0.33 W

Power and Ground Strategy

Figure7. Power Plane (Layer 5 of 6)

Figure8. SV DD, XV DD(Layer 6 of 6—Bottom)

Power and Ground Strategy

For sensitive supplies (such as XV DD and SV DD), a key requirement for power sharing is that the planes be relatively isolated. One effective strategy is to route the power planes separately and tie them together at the power source. See Figure9.

Figure9. Common Source Split Planes

Another strategy is to use a low-pass filter to eliminate coupled noise, as long as there is sufficient current capacity in the components and connections. In either case, once separated, treat the two as independent power planes and route and bypass them separately.

7.2Current Delivery

An important consideration in the six-layer PCB is ensuring all power rails have sufficient copper for proper current delivery. The highest power on the MPC8544E is V DD_CORE

for V DD_CORE is 7.8W.

Within a congested BGA array, the current travels down multiple 11-mil trace segments as it travels to the power pins, assuming the via stackup referenced in Figure6 is used. The current-carrying capacity of these 11-mil traces is highly dependent on the current model chosen, either IPC2221A or the newer research performed by Johannes Adam of Flomerics Ltd. For greater detail on these two approaches see Section10, “Current Delivery in the BGA Field.”

Power and Ground Strategy

In short, Table 6 depicts the current capacity differences between the two approaches assuming a

maximum temperature rise of 20°C. Additionally, the last column highlights the current capacity assumed for the MPC8544E six-layer PCB.

Table 6. Current Capacity of an 11-mil Trace Adam’s Model vs. IPC

Taking the last column from Table 6 and the number of 11-mil channels achieved in the six-layer PCB, Table 7 highlights the current capacity for V DD_CORE .

7.3PLL Filters

The MPC8544E has six PLLs which each require a filter circuit. The PLL pins are placed on the package in order to minimize noise and to allow ease during layout. An example layout for the filters are shown in Figure 10. This figure shows example layout for an A VDD filter. For the exact filter values refer to the MPC8544E PowerQUICC? III Integrated Processor Hardware Specifications.To ensure a high quality filter is realized, use the following rules:

?Place the components of the filter as close a possible to their respective pin ?Keep the traces as short as possible

?Use a 10-mil trace width or larger. An area fill is also a possibility.

Location

Copper Plating

(oz.)

11-mil Trace: Adam’s Model (A)

11-mil Trace:

IPC2221A

(A)11-mil Trace:

Capacity Assumed for the MPC8544E Six-Layer PCB

(A)

Outer

0.5 1.2100.777 1.01.0 1.711 1.285 1.51.5 2.420 1.730N/A 2.0

3.422 2.130N/A Inner

0.5 1.1490.3900.751.0 1.6250.582 1.11.5 2.2990.865N/A 2.0

3.251

1.065

N/A

Table 7. Current C a pacity Achieved in the Six-Layer PCB

Power Rail Copper Weight

Used

(oz.)

No. of 11-mil Traces

Supplying Power

Current per Trace (A)Total Current Supplied

in Six-Layer PCB

(A)

Assumed Worst Case Current (A)V DD_CORE

1.0

10

1.1

11

7.8 (7.8 W/1.0 V)

Power and Ground Strategy

?

Maintain at least 20-mil clearance between the filter and other signals.

Figure10. Example Layout for AV DD Filters

7.4Sharing Power Supplies

The six-layer design referenced in this application note assumes all processor powers referenced in Table5 are supplied by unique power supplies. If the customer chooses, further sharing of power supplies can be achieved to reduce the number of supplies needed at the board level. Table8 shows some acceptable options for sharing MPC8544E power rails.

Table8. MPC8544E Power Requirements

Power Source Symbol Voltage Comments

Core power + PLL filter

V DD_CORE

AV DD_CORE

AV DD_PCI

AV DD_PLAT

AV DD_LBIU

AV DD_SRDS

AV DD_SRDS2

1.0 V PLLs are sourced from RC filter circuit derived from 1.0-V rail.

SerDes SV DD

XV DD

Separate filtered plane but derived from the same 1.0-V power regulator.

Memory GV DD 1.8 V Unique rail on the MPC8544E device. Could possibly be shared with another

1.8-V device on the board.

Ethernet LV DD

TV DD 2.5 V 2.5 V is readily usable by most PHYs; however, 3.3 V is not suitable for RGMII

mode.

Local bus BV DD 2.5 V requires low-voltage flash memory and so forth

Or alternatively

Filters

Power and Ground Strategy

7.5Bypass Capacitor Placement

Because of the high current transients on the V DD_CORE power pins, take care to bypass these power pins and to provide a good connection between the BGA pads and the power and ground planes. In particular, the SMD capacitors should have pads directly attached to the via ring (or even better, within it using via-in-pad methods).

Ethernet LV DD TV DD 3.3 V

3.3 V is not suitable for RGMII mode

Local bus BV DD PCI/Misc

OV DD

Table 8. MPC8544E Power Requirements (continued)

Power Source Symbol Voltage Comments

Power and Ground Strategy

Figure 11 shows the dispersion of V DD_CORE power pins along with the ground pattern. This is a bottom view of the center portion of interest within the BGA array.

Figure 11. MPC8544E V DD_CORE and Ground Pattern (Bottom View)

Ground

L M N P R T U 111213141516V W Y

171819202122

23V DD_CORE

24

Power and Ground Strategy

After the power and grounds are escaped, the SMD 0402 capacitors can be placed so that the capacitor pads attach directly to the power vias on the side. Minimize or eliminate the trace between the via and the capacitor pad. Figure 12 shows three possible attachment methods.

Figure 12. MPC8544E SMD Capacitor Via Placement

Vias Embedded in Pads

Vias to the Side of Pads

All are SMD0402

Vias Offset From Pads

Best

Good

OK

Power and Ground Strategy

Figure 13 shows the relative attachment of the SMD 0402 capacitors using any of the methods shown in Figure 12. This is a view through the top of the board.

Figure 13. MPC8544E CORE and Ground SMD 0402 Capacitor Placement (Bottom View)

Other capacitors, such as those required for the other power rails, are not shown but can be attached in the same manner. If the PCB is not permitted to use via-in-pad connections, the capacitors can be shifted to attach to a pad in the area between the BGA pads. In that case, use the same relative pattern, but each capacitor shifts a little.

V DD_PLA T

GROUND

L

M

N

P

R

T

U

111213

1415

16V

W

Y

17

1819202122

23V DD_CORE

24

Power and Ground Strategy

7.6Bulk Capacitors

Bulk capacitors can be placed outside the periphery of the MPC8544E die, as close as reasonably possible. Systems with heatsinks and/or sockets probably need some additional spacing, but the high-frequency capacitors handle the fastest transients, allowing the bulk capacitors to be spaced a little further away. Keep them within 2 cm. Figure 14 shows the MPC8544E V DD_CORE bulk capacitor placement.

Figure 14. MPC8544E Bulk Capacitor Placement (Top View)

MPC8544E

0.46 mils

Low-ESR

Bulk Capacitors

0.46 mils

V CORE Power Split

A28

A1

Signal Layer Gerber Plot

8Signal Layer Gerber Plot

Figure15 through Figure18 show the signal layers for the six-layer PCB example. The intent is to demonstrate that the MPC8544E signals can be broken in a six-layer PCB; the figure does not include all the decoupling, nor does it show all the necessary pull-ups, AC caps, and other circuitry that would be required outside the BGA fan-out area. This level of detail is captured as part of the MPC8544E development system.

Figure15. Top Gerber Plot (Layer 1 of 6)

PCB板布线技巧

PCB板布线技巧 在PCB设计中,布线是完成产品设计的重要步骤,可以说前面的准备工作都是为它而做的,在整个PCB中,以布线的设计过程限定最高,技巧最细、工作量最大。PCB布线有单面布线、双面布线及多层布线。布线的方式也有两种:自动布线及交互式布线,在自动布线之前,可以用交互式预先对要求比较严格的线进行布线,输入端与输出端的边线应避免相邻平行,以免产生反射干扰。必要时应加地线隔离,两相邻层的布线要互相垂直,平行容易产生寄生耦合。 自动布线的布通率,依赖于良好的布局,布线规则可以预先设定,包括走线的弯曲次数、导通孔的数目、步进的数目等。一般先进行探索式布经线,快速地把短线连通,然后进行迷宫式布线,先把要布的连线进行全局的布线路径优化,它可以根据需要断开已布的线。并试着重新再布线,以改进总体效果。 对目前高密度的PCB设计已感觉到贯通孔不太适应了,它浪费了许多宝贵的布线通道,为解决这一矛盾,出现了盲孔和埋孔技术,它不仅完成了导通孔的作用,还省出许多布线通道使布线过程完成得更加方便,更加流畅,更为完善,PCB 板的设计过程是一个复杂而又简单的过程,要想很好地掌握它,还需广大电子工程设计人员去自已体会,才能得到其中的真谛。 1 电源、地线的处理 既使在整个PCB板中的布线完成得都很好,但由于电源、地线的考虑不周到而引起的干扰,会使产品的性能下降,有时甚至影响到产品的成功率。所以对电、地线的布线要认真对待,把电、地线所产生的噪音干扰降到最低限度,以保证产品的质量。 对每个从事电子产品设计的工程人员来说都明白地线与电源线之间噪音所产生的原因,现只对降低式抑制噪音作以表述: 众所周知的是在电源、地线之间加上去耦电容。 尽量加宽电源、地线宽度,最好是地线比电源线宽,它们的关系是:地线>电源线>信号线,通常信号线宽为:0.2~0.3mm,最经细宽度可达0.05~0.07mm,电源线为1.2~2.5 mm 对数字电路的PCB可用宽的地导线组成一个回路, 即构成一个地网来使用(模拟电路的地不能这样使用) 用大面积铜层作地线用,在印制板上把没被用上的地方都与地相连接作为地线用。或是做成多层板,电源,地线各占用一层。 2 数字电路与模拟电路的共地处理 现在有许多PCB不再是单一功能电路(数字或模拟电路),而是由数字电路和模拟电路混合构成的。因此在布线时就需要考虑它们之间互相干扰问题,特别是地线上的噪音干扰。 数字电路的频率高,模拟电路的敏感度强,对信号线来说,高频的信号线尽可能远离敏感的模拟电路器件,对地线来说,整人PCB对外界只有一个结点,所以必须在PCB内部进行处理数、模共地的问题,而在板内部数字地和模拟地实际上是分开的它们之间互不相连,只是在PCB与外界连接的接口处(如插头等)。数字地与模拟地有一点短接,请注意,只有一个连接点。也有在PCB上不共地的,这由系统设计来决定。 3 信号线布在电(地)层上 在多层印制板布线时,由于在信号线层没有布完的线剩下已经不多,再多加层数就会造成浪费也会给生产增加一定的工作量,成本也相应增加了,为解决这个矛盾,可以考虑在电(地)层上进行布线。首先应考虑用电源层,其次才是地层。因为最好是保留地层的完整性。 4 大面积导体中连接腿的处理

PCB布线的技巧及注意事项

PCB布线的技巧及注意事项 PCB布线的技巧及注意事项对于硬件电子产品设计者,面临的PCB设计越来越复杂。管脚越来越密的高级封装器件被使用,单位面积的网络密度不断提高,给布线带来更大的压力。同时,更多的工程师已经不满足自动布线器100%布通率的要求,希望能够进行电气规则约束布线,满足信号完整性要求。 70%以上的工程师关心的与信号完整性有关,包括了传输线分析、信号回流路径、匹配、串扰、拓朴和EMI/EMC等问题。此外,还问到可制造性、软件使用方面的问题。看来工程师门对高速还是非常关注的,相反,对于高密度布线好像并不是很关注。 这个好像和当前国内设计状况类似。很多高速设计还处在方案讨论阶段,或原型样机阶段。工程师预见或者已经观察到一些问题,如过冲、欠冲、振荡、串扰等问题。但是对整个高速问题的起因,对高速分析仿真方法不太了解,往往把高速数字电路设计和射频设计当做同样问题对待。我感觉实际高速分析中,时序分析也是数字电路设计中的一个关键却往往被忽略。除了分析外,为了减小传输线效应,缩小PCB面积,高密度设计实现也是一个问题。但在国内,由于担心串扰,开发周期或者调测方面的问题,往往采用多个单板,将设计密度降低。 作高速PCB设计,前仿真分析很关键,这些包括器件选择、模型编辑、信号分配、匹配策略和层叠设计等。前仿真分析不能仅仅在原理图阶段,使用拓朴结构编辑,还必须使用PCB LAYOUT工具进行布局探测和预布线分析,估计实现难度和布线方法。同时对于分配好的平面层先作电源分割,安排好布线层的优先级,最大限度避免关键信号的跨分割。 完成原理图,一般工程师就迫不及待的开始PCB设计。我建议可以花一天或两天的时间检查一下原理图。因为到了后期,如果发现原理图设计有误,更改的代价就太大了。开始PCB设计,不要忙着布线,先好好布局。根据经验,PCB设计时间一般按照三三制分配,布局占1/3时间,布线占1/3,检查1/3。布局相当关键,有经验的工程师在布局同时,已经有了关键布线的规划。布局一般本着先大后小,先关键后次要,先放置有定位要求的器件,布局时,除了考虑布线质量,对测试,加工等问题也要考虑,权衡各方面因素。 手工布线现在还是大部分工程师的选择,因为很多人对自动布线的结果不是很满意。其实现在一些高级EDA工具,自动布线已经相当智能化。自动布线,并不意味着全部交给工具去做,还有很多需要人干预的地方。我个人经验认为,网络分类(class),布线优先级设置,布线规则是影响布通率和布线效果的主要因素。 有人也称PCB设计是从抽象概念到实际产品的转化。PCB设计实际是一项混合技术。要求设计者对电路原理、电磁场、布线算法、生产加工、测试等各方面知识都要有所了解,所以一名优秀的PCB工程师应当注意学习这些知识

飞思卡尔智能车比赛细则

2016

目录

第十一届竞赛规则导读 参加过往届比赛的队员可以通过下面内容了解第十一届规则主要变化。如果第一次参加比赛,则建议对于本文进行全文阅读。 相对于前几届比赛规则,本届的规则主要变化包括有以下内容: 1.本届比赛新增了比赛组别,详细请参见正文中的图1和第四章的“比赛任务” 中的描述; 2.第十届电磁双车组对应今年的A1组:双车追逐组。其它组别与新组别的对应 关系请参见图2; 3.为了提高车模出界判罚的客观性,规则提出了两种方法:路肩法和感应铁丝 法,详细请见赛道边界判定”; 4.改变了原有的光电计时系统,所有赛题组均采用磁感应方法计时,详细请参 见“计时裁判系统”; 5.取消了第十届的发车灯塔控制的方式; 6.赛道元素进行了简化,详细请参见“赛道元素”; 7.赛道材质仍然为PVC耐磨塑胶地板,但赛题组A2不再需要赛道。 8.对于车模所使用的飞思卡尔公司MCU的种类、数量不再限制。 9.比赛时,每支参赛队伍的赛前准备时间仍然为20分钟,没有现场修车环节。

一、前言 智能车竞赛是从2006开始,由教育部高等教育司委托高等学校自动化类教学指导委员会举办的旨在加强学生实践、创新能力和培养团队精神的一项创意性科技竞赛。至今已经成功举办了十届。在继承和总结前十届比赛实践的基础上,竞赛组委会努力拓展新的竞赛内涵,设计新的竞赛内容,创造新的比赛模式,使得围绕该比赛所产生的竞赛生态环境得到进一步的发展。 为了实现竞赛的“立足培养、重在参与、鼓励探索、追求卓越”的指导思想,竞赛内容设置需要能够面向大学本科阶段的学生和教学内容,同时又能够兼顾当今时代科技发展的新趋势。 第十一届比赛的题目在沿用原来根据车模识别赛道传感器种类进行划分的基础类组别之上,同时增加了以竞赛内容进行划分的提高类组别,并按照“分赛区普及,全国总决赛提高”的方式,将其中一个类别拓展出创意类组别。第十一届比赛的题目各组别分别如下: ●基础类包括B1光电组、B2摄像头组、B3电磁直立组、B4电轨组; ●提高类包括A1双车追逐组、A2信标越野组; ●创意类包括I1 电轨节能组。 图 1 不同组别,不同挑战度 每个组别在选用的车模、赛道识别方法、完成任务等方面存在差别,对于参赛选手不同学科知识和能力要求也不同,制作的挑战度也有较大的区别。相比较而言,

二十年经验浓缩:PCB布线设计经验谈附原理图

二十年经验浓缩:PCB布线设计经验谈附原理图 在当今激烈竞争的电池供电市场中,由于成本指标限制,设计人员常常使用双面板。尽管多层板(4层、6层及8层)方案在尺寸、噪声和性能方面具有明显优势,成本压力却促使工程师们重新考虑其布线策略,采用双面板。在本文中,我们将讨论自动布线功能的正确使用和错误使用,有无地平面时电流回路的设计策略,以及对双面板元件布局的建议。 自动布线的优缺点以及模拟电路布线的注意事项 设计PCB时,往往很想使用自动布线。通常,纯数字的电路板(尤其信号电平比较低,电路密度比较小时)采用自动布线是没有问题的。但是,在设计模拟、混合信号或高速电路板时,如果采用布线软件的自动布线工具,可能会出现一些问题,甚至很可能带来严重的电路性能问题。 例如,图1中显示了一个采用自动布线设计的双面板的顶层。此双面板的底层如图2所示,这些布线层的电路原理图如图3a和图3b所示。设计此混合信号电路板时,经仔细考虑,将器件手工放在板上,以便将数字和模拟器件分开放置。采用这种布线方案时,有几个方面需要注意,但最麻烦的是接地。如果在顶层布地线,则顶层的器件都通过走线接地。器件还在底层接地,顶层和底层的地线通过电路板最右侧的过孔连接。当检查这种布线策略时,首先发现的弊端是存在多个地环路。另外,还会发现底层的地线返回路径被水平信号线隔断了。这种接地方案的可取之处是,模拟器件(12位A/D转换器MCP3202和2.5V参考电压源MCP4125)放在电路板的最右侧,这种布局确保了这些模拟芯片下面不会有数字地信号经过。 图3a和图3b所示电路的手工布线如图4、图5所示。在手工布线时,为确保正确实现电路,需要遵循一些通用的设计准则:尽量采用地平面作为电流回路;将模拟地平面和数字地平面分开;如果地平面被信号走线隔断,为降低对地电流回路的干扰,应使信号走线与地平面垂直;模拟电路尽量靠近电路板边缘放置,数字电路尽量靠近电源连接端放置,这样做可以降低由数字开关引起的di/dt效应。 这两种双面板都在底层布有地平面,这种做法是为了方便工程师解决问题,使其可快速明了电路板的布线。厂商的演示板和评估板通常采用这种布线策略。但是,更为普遍的做法是将地平面布在电路板顶层,以降低电磁干扰。

飞思卡尔智能车经验

RT,留下一点不算成功的经验吧。 先说说个人认为要取得好成绩的两个最重要的先决条件。 1. 人,这个是大前提,对于一个好的队伍,判别标准其实很简单,就是队员3个人是玩伴关系还是领导和下属关系。前者,大家都是来玩这个智能车的,自然主观能动性就会很高,能自主学习。不会总是“等着所谓队长分配任务”。这样效率就会很高。成绩自然不会低,后者,如果“队长”个人能力很强的话,就会出现到最后只有“队长”一个人在干。其他的队员就会因为自己技术不行,渐渐退出。而不会因为自己不会而去主动的学习。如果“队长”能力一般,再没有一些强力指导老师的情况下,这样的队伍一般会悲剧掉。所以,新人在参加这个智能车比赛的时就要明确动机。参加智能车确实是来学习知识的,但不会有人真正的来教你。一切都靠自己。 2.跑道,这个是客观条件中最重要的,一条污浊、破损、不符合规则的跑道,是不可能出成绩的。我们学校的赛道就是因为当初制作和后期保养不到位,导致赛道诸多永久性污浊、破损。一开始车刚能爬的时候,问题还不明显,后来在测试让车能平滑过S弯时问题就来了,由于赛道污浊,远处的跑道在CCD看了是错误,导致S弯和普通弯看起来一样,致使S弯策略根本没有启用,当时一直到修改S弯策略,到后来调出图像来看才发现是采集的问题。至于赛道污浊破损带来的干扰要不要处理,答案是肯定的,因为就算是比赛用的跑道也会有擦不掉,补不了的地方。但处理这些问题,应该是放在车辆原先行驶策略都调试正确的情况下,再人为的加入这些干扰。这样修改程序起来就有的放矢。 下面再以个人的观点介绍一下3个组别的特点,给新人选择做一个参考。 摄像头:有点像开卷考试,能得到的东西很多,但是如何把这些东西用好就是一个学问。摄像头的关键就是如何从采集回来的图像所包含的诸多信息中,选出一些高效方便的信息来控制车辆。至于控制策略,个人觉得一个能根据不同赛道类型而变化比例系数的比例控制器就能很好的满足控制需要。 光电组:想象起来很容易,其实很累的一个组,原理最简单,但是为了能有30CM以上的前瞻,和比较连续的偏差变化,就要下大功夫,先不说别的,让你装15个激光管,而且要保证不焊烧并要把光点打在一条线上,就是很繁琐的事情。总得来说,光电组拼的就是电路和传感器结构。不过对于看客来说,光电组是最好“看”的组,一排壮观的激光加上摆头的机械~ 电磁组:听起来有点复杂,其实比前两个组都轻松的组,电磁组又可分为数字和模拟两个类别。数字传感器就是和光电一样弄一排的传感器,看看哪个传感器接收到的信号最强以判断中线位置。模拟的就是比较两个传感器之间信号强度的差值来判断。电磁组好处就是不容易受到干扰,比赛上也见的,电磁车跑完的成功率是很高的,而且很容易判别起跑线。基本不用懂脑筋。而且如果选用是模拟传感器的话,能得到比较平滑的控制。 先说这些,想到再继续 关于摇头激光车的一点个人理解:为什么光电的车,要多花一个舵机去让传感器摇头呢?因为。为了能获得赛道上一个比较宽范围的信息,就必须把传感器做的很长。这样的后果 就是重量。折中的办法就是摇头,通过摇头,可以使一个小尺寸的传感器检测到大范围 DEMOK工作室淘宝小店

飞思卡尔智能车竞赛新手入门建议

每年都会有很多新人怀着满腔热情来做智能车,但其中的很多人很快就被耗光了热情和耐心而放弃。很多新人都不知道如何入手,总有些有劲无处使的感觉,觉得自己什么都不会,却又不知道该干什么。新人中存在的主要问题我总结了以下几点: l缺乏自信,有畏难情绪 作为新人,一切都是新的。没有设计过电路,没有接触过单片机,几乎什么都不会。有些新人听了两次课,看了两篇技术报告,就发现无数不懂不会的东西,于是热情在消退,信心在减弱。这些都是放弃的前兆。殊不知,高手都是从新人过来的,没有谁天生什么都会做。一件事件,如果还没开始做,就自己否定自己,认为自己做不到,那么肯定是做不到的。 l习惯了被动接收知识,丧失了主动学习的能力。 现在的学生大多从小习惯了被灌输知识,只学老师教的,只学老师考的。殊不知一旦走向社会,将不再有老师来教,不再有应付不完的考试。做智能车和传统的教学不同,学生将从被动学习的地位转变为主动学习。就算有指导老师,有指导的学长,但也都处于被动地位,往往都不会主动来教。有的学生一开始就没有转变思想,还希望就像实验课一样,老师安排好步骤1,2,3……,然后自己按照老师安排好的步骤按部就班的完成。这样的学生,往往都丧失了提出问题和分析问题的能力,只是一个应付考试的机器。要知道,解决问题的第一步是提出问题,如果总等着别人来教,那么问题永远会挡在你面前。 l缺乏团队精神和合作意识 智能车比赛是以团队的形式参赛,只依靠个人能力单兵作战就能取得好成绩的是很少很少的。当今社会,任何人的成功都离不开身后的团队的支撑。智能车是一个很复杂的系统,电路、机械、传感器、单片机、底层驱动、控制算法……。如果所有的任务都是一个人去完成,固然锻炼了自己,但想做的很好却很不现实。很多新人,来到实验室,来到一个陌生的环境和团队,连向学长请教,和同学交流的勇气都没有,又如何融入团队呢。除了要主动融入团队,还要培养自己的团队意识。团队精神往往表现为一种责任感,如果团队遇到问题,每个人都只顾自己,出了错误,不想着解决问题,而是互相推诿埋怨。这样的团队,肯定是无法取得好成绩的。 l缺乏耐心和细心的精神 其实把一件事做好很简单,细心加上耐心。不细心就想不到,没有耐心,即使想到了也做不到。做事怕麻烦,将就,说白了就是惰性在作祟。明明可以把支架做的更轻更漂亮,明明可以把程序写的更简洁,明明可以把电路设计得更完善……。其实,每个人都有很大潜力,如果不逼自己一次,你永远不知道自己的潜力有多

PCB布线设计详介

PCB布线设计 在当今激烈竞争的电池供电市场中,由于成本指标限制,设计人员常常使用双面板。尽管多层板(4层、6层及8层)方案在尺寸、噪声和性能方面具有明显优势,成本压力却促使工程师们重新考虑其布线策略,采用双面板。在本文中,我们将讨论自动布线功能的正确使用和错误使用,有无地平面时电流回路的设计策略,以及对双面板元件布局的建议。 自动布线的优缺点以及模拟电路布线的注意事项 设计PCB时,往往很想使用自动布线。通常,纯数字的电路板(尤其信号电平比较低,电路密度比较小时)采用自动布线是没有问题的。但是,在设计模拟、混合信号或高速电路板时,如果采用布线软件的自动布线工具,可能会出现一些问题,甚至很可能带来严重的电路性能问题。 例如,图1中显示了一个采用自动布线设计的双面板的顶层。此双面板的底层如图2所示,这些布线层的电路原理图如图3a和图3b所示。设计此混合信号电路板时,经仔细考虑,将器件手工放在板上,以便将数字和模拟器件分开放置。 采用这种布线方案时,有几个方面需要注意,但最麻烦的是接地。如果在顶层布地线,则顶层的器件都通过走线接地。器件还在底层接地,顶层和底层的地线通过电路板最右侧的过孔连接。当检查这种布线策略时,首先发现的弊端是存在多个地环路。另外,还会发现底层的地线返回路径被水平信号线隔断了。这种接地方案的可取之处是,模拟器件(12位A/D转换器MCP3202和2.5V参考电压源MCP4125)放在电路板的最右侧,这种布局确保了这些模拟芯片下面不会有数字地信号经过。 图3a和图3b所示电路的手工布线如图4、图5所示。在手工布线时,为确保正确实现电路,需要遵循一些通用的设计准则:尽量采用地平面作为电流回路;将模拟地平面和数字地平面分开;如果地平面被信号走线隔断,为降低对地电流回路的干扰,应使信号走线与地平面垂直;模拟电路尽量靠近电路板边缘放置,数字电路尽量靠近电源连接端放置,这样做可以降低由数字开关引起的di/dt效应。 这两种双面板都在底层布有地平面,这种做法是为了方便工程师解决问题,使其可快速明了电路板的布线。厂商的演示板和评估板通常采用这种布线策略。但是,更为普遍的做法是将地平面布在电路板顶层,以降低电磁干扰。

飞思卡尔智能车竞赛光电组技术报告

第九届“飞思卡尔”杯全国大学生智能车竞赛光电组技术报告 学校:中北大学 伍名称:ARES 赛队员:贺彦兴 王志强 雷鸿 队教师:闫晓燕甄国涌

关于技术报告和研究论文使用授权的说明书本人完全了解第八届“飞思卡尔”杯全国大学生智能汽车竞赛关保留、使用技术报告和研究论文的规定,即:参赛作品著作权归参赛者本人,比赛组委会和飞思卡尔半导体公司可以在相关主页上收录并公开参赛作品的设计方案、技术报告以及参赛模型车的视频、图像资料,并将相关内容编纂收录在组委会出版论文集中。 参赛队员签名: 带队教师签名: 日期:2014-09-15日

摘要 本文介绍了第九届“飞思卡尔杯全国大学生智能车大赛光电组中北大学参赛队伍整个系统核心采用飞思卡尔单片机MC9S12XS128MAA ,利用TSL1401线性CCD 对赛道的行扫描采集信息来引导智能小车的前进方向。机械系统设计包括前轮定位、方向转角调整,重心设计器件布局设计等。硬件系统设计包括线性CCD传感器安装调整,电机驱动电路,电源管理等模块的设计。软件上以经典的PID算法为主,辅以小规Bang-Bang 算法来控制智能车的转向和速度。在智能车系统设计开发过程中使用Altium Designer设计制作pcb电路板,CodeWarriorIDE作为软件开发平台,Nokia5110屏用来显示各实时参数信息并利用蓝牙通信模块和串口模块辅 助调试。关键字:智能车摄像头控制器算法。

目录 1绪论 (1) 1.1 竞赛背景 (1) 1.2国内外智能车辆发展状况 (1) 1.3 智能车大赛简介 (2) 1.4 第九届比赛规则简介 (2) 2智能车系统设计总述 (2) 2.1机械系统概述 (3) 2.2硬件系统概述 (5) 2.3软件系统概述 (6) 3智能车机械系统设计 (7) 3.1智能车的整体结构 (7) 3.2前轮定位 (7) 3.3智能车后轮减速齿轮机构调整 (8) 3.4传感器的安装 (8) 4智能车硬件系统设计 (8) 4.1XS128芯片介绍 (8) 4.2传感器板设计 (8) 4.2.1电磁传感器方案选择 (8) 4.2.2电源管理模 (9) 4.2.3电机驱动模块 (10) 4.2.4编码器 (11) 5智能车软件系统设 (11) 5.1程序概述 (11) 5.2采集传感器信息及处理 (11) 5.3计算赛道信息 (13) 5.4转向控制策略 (17) 5.5速度控制策略 (19) 6总结 (19)

飞思卡尔杯智能车竞赛报告总结

1.1. 系统分析 智能车竞赛要求设计一辆以组委会提供车模为主体的可以自主寻线的模型车,最后成绩取决于单圈最快时间。因此智能车主要由三大系统组成:检测系统,控制系统,执行系统。其中检测系统用于检测道路信息及小车的运行状况。控制系统采用大赛组委会提供的16位单片机MC9S12XS128作为主控芯片,根据检测系统反馈的信息新局决定各控制量——速度与转角,执行系统根据单片机的命令控制舵机的转角和直流电机的转速。整体的流程如图1.1,检测系统采集路径信息,经过控制决策系统分析和判断,由执行系统控制直流电机给出合适的转速,同时控制舵机给出合适的转角,从而控制智能车稳定、快速地行驶。 图2.1 1.2. 系统设计 参赛小车将电感采集到的电压信号,经滤波,整流后输入到XS128单片机,用光电编码器获得实时车速,反馈到单片机,实现完全闭环控制。速度电机采用模糊控制,舵机采用PD控制,具体的参数由多次调试中获得。考滤到小车设计的综合性很强,涵盖了控制、传感、电子、电气、计算机和机械等多个学科领域,因此我们采用了模块化设计方法,小车的系统框图如图2.2。

第五届全国大学生智能汽车竞赛技术报告 图2.2 1.3. 整车外观 图2.3

1.4. 赛车的基本参数 智能车竞赛所使用的车模是东莞市博思公司生产的G768型车模,由大赛组委会统一提供,是一款带有摩擦式差速器后轮驱动的电动模型车。车模外观如图3.1。车模基本参数如表3.1。 图3.1 表3.1车模基本参数 1.5. 赛车前轮定位参数的选定

第五届全国大学生智能汽车竞赛技术报告 现代汽车在正常行驶过程中,为了使汽车直线行驶稳定,转向轻便,转向后能自动回正,减少轮胎和转向系零件的磨损等,在转向轮、转向节和前轴之间须形成一定的相对安装位置,叫车轮定位,其主要的参数有:主销后倾、主销内倾、车轮外倾和前束。模型车的前轮定位参数都允许作适当调整,故此我们将自身专业课所学的理论知识与实际调车中的赛车状况相结合,最终得出赛车匹配后的前轮参数[6]。 1.5.1. 主销后倾角 主销后倾角是指在纵向平面内主销轴线与地面垂直线之间的夹角γ,如图3-2。模型车的主销后倾角可以设置为0、 2°?3°、 4°?6°,可以通过改变上横臂轴上的黄色垫片来调整,一共有四个垫片,前二后二时为0°,前一后三为2°?3°,四个全装后面时为4°?6°。 由于主销后倾角过大时会引起转向沉重,又因为比赛所用舵机特性偏软,所以不宜采用大的主销后倾角,以接近0°为好,即垫片宜安装采用前二后二的方式,以便增加其转向的灵活性。如图3.3。 图3.2 图3.3 1.5. 2. 主销内倾角 主销内倾角是指在横向平面内主销轴线与地面垂直线之间的夹角β,如图3.4,它的作用也是使前轮自动回正。对于模型车,通过调整前桥的螺杆的长度可以改变主销内倾角的大小,由于前轴与主销近似垂直的关系,故主销内倾角

PCB布线技巧

.信号完整性(Signal Integrity):就是指电路系统中信号的质量,如果在要求的时间内,信号能不失真地从源端传送到接收端,我们就称该信号是完整的。 2.传输线(Transmission Line):由两个具有一定长度的导体组成回路的连接线,我们称之为传输线,有时也被称为延迟线。 3.集总电路(Lumped circuit):在一般的电路分析中,电路的所有参数,如阻抗、容抗、感抗都集中于空间的各个点上,各个元件上,各点之间的信号是瞬间传递的,这种理想化的电路模型称为集总电路。 4.分布式系统(Distributed System):实际的电路情况是各种参数分布于电路所在空间的各处,当这种分散性造成的信号延迟时间与信号本身的变化时间相比已不能忽略的时侯,整个信号通道是带有电阻、电容、电感的复杂网络,这就是一个典型的分布参数系统。 5.上升/下降时间(Rise/Fall Time):信号从低电平跳变为高电平所需要的时间,通常是量度上升/下降沿在10%-90%电压幅值之间的持续时间,记为Tr。 6.截止频率(Knee Frequency):这是表征数字电路中集中了大部分能量的频率范围(0.5/Tr),记为Fknee,一般认为超过这个频率的能量对数字信号的传输没有任何影响。 7.特征阻抗(Characteristic Impedance):交流信号在传输线上传播中的每一步遇到不变的瞬间阻抗就被称为特征阻抗,也称为浪涌阻抗,记为Z0。可以通过传输线上输入电压对输入电流的比率值(V/I)来表示。 8.传输延迟(Propagation delay):指信号在传输线上的传播延时,与线长和信号传播速度有关,记为tPD。 9.微带线(Micro-Strip):指只有一边存在参考平面的传输线。 10.带状线(Strip-Line):指两边都有参考平面的传输线。 11.趋肤效应(Skin effect):指当信号频率提高时,流动电荷会渐渐向传输线的边缘靠近,甚至中间将没有电流通过。与此类似的还有集束效应,现象是电流密集区域集中在导体的内侧。 12.反射(Reflection):指由于阻抗不匹配而造成的信号能量的不完全吸收,发射的程度可以有反射系数ρ表示。 13.过冲/下冲(Over shoot/under shoot):过冲就是指接收信号的第一个峰值或谷值超过设定电压——对于上升沿是指第一个峰值超过最高电压;对于下降沿是指第一个谷值超过最低电压,而下冲就是指第二个谷值或峰值。 14.振荡:在一个时钟周期中,反复的出现过冲和下冲,我们就称之为振荡。振荡根据表现形式可分为振铃(Ringing)和环绕振荡,振铃为欠阻尼振荡,而环绕振荡为过阻尼振荡。 匹配(Termination):指为了消除反射而通过添加电阻或电容器件来达到阻抗一致的效果。因为通常采用在源端或终端,所以也称为端接。 15.串扰:串扰是指当信号在传输线上传播时,因电磁耦合对相邻的传输线产生的不期望的电压噪声干扰,这种干扰是由于传输线之间的互感和互容引起的。 信号回流(Return current):指伴随信号传播的返回电流。 16.自屏蔽(Self shielding):信号在传输线上传播时,靠大电容耦合抑制电场,靠小电感耦合抑制磁场来维持低电抗的方法称为自屏蔽。 17.前向串扰(Forward Crosstalk):指干扰源对牺牲源的接收端产生的第一次干扰,也称为远端干扰(Far-end crosstalk)。 18.后向串扰(Forward Crosstalk):指干扰源对牺牲源的发送端产生的第一次干

飞思卡尔智能车黑线识别算法及控制策略研究

智能车黑线识别算法及控制策略研究 时间:2009-05-1811:23:07来源:电子技术作者:北京信息科技大学,机电工程学院张淑 谦王国权 0引言 “飞思卡尔”杯全国大学生智能车大赛是由摩托罗拉旗下飞思卡尔公司赞助由高等学校自动化专业教学指导委员会负责主办的全国性的赛事,旨在加强大学生的创新意识、团队合作精神和培养学生的创新能力。此项赛事专业知识涉及控制、模式识别、传感技术、汽车电子、电气、计算机、机械等多个学科,对学生的知识融合和动手能力的培养,对高等学校控制及汽车电子学科学术水平的提高,具有良好的推动作用。 智能车竞赛所使用的车模是一款带有差速器的后轮驱动模型赛车,它由大赛组委会统一提供。自动控制器是以飞思卡尔16位微控制器MC9S12DGl28(S12)为核心控制单元,配合有传感器、电机、舵机、电池以及相应的驱动电路,它能够自主识别路径,控制车高速稳定运行在跑道上。比赛要求自己设计控制系统及自行确定控制策略,在规定的赛道上以比赛完成的时间短者为优胜者。赛道由白色底板和黑色的指引线组成。根据赛道的特点,比赛组委会确定了两种寻线方案:1.光电传感器。2.摄像头。 两种寻线方案的特点如下: (1)光电传感器方案。通过红外发射管发射红外线光照射跑道,跑道表面与中心指引线具有不同的反射强度,利用红外接收管可以检测到这些信息。此方案简单易行程序调试也简单且成本低廉,但是它受到竞赛规则的一些限制(组委会要求传感器数量不超过16个(红外传感器的每对发射与接收单元计为一个传感器,CCD传感器计为1个传感器)),传感器的数量不可能安放的太多,因而道路检测的精度较低,能得到指引线的信息量也较少。若采用此方案容易引起舵机的回摆走蛇形路线。 (2)摄像头方案。根据赛道的特点斯用黑白图像传感器即可满足要求。CCD摄像头有面阵和线阵两种类型,它们在接口电路、输出信号以及检测信息等方面有着较大的区别,面阵摄像头可以获取前方赛道的图像信息,而线阵CCD只能获取赛道一条直线上的图像信息。摄像头方案的所能探测的道路信息量远大于光电传感器方案,而且摄像头也可以探测足够远的距离以方便控制器对前方道路进行预判。虽然此方案对控制器的要求比较高,但组委会提供的MC9S12DGl28(S12)的运算能力以及自身AD口的采样速度完全能够满足摄像头的视频采样和大量图像数据的处理的要求。 本文就是在摄像头方案的前提下,在实时的图像数据获取的基础上对图像信息进行数据处理,从而提取赛道中心的黑色指引线,再以此来作为舵机和驱动电机的控制依据。 1摄像头采样数据的特点 采用的黑白摄像头的主要工作原理为:按一定的分辨率,以隔行扫描的方式采集图像上的点,当扫描到某点时,就通过图像传感芯片将该点处图像的灰度转换成与灰度一一对应的电压值,然后将此电压值通过视频信号端输出,见图1。摄像头连续地扫描图像上的一行,则输出就是一段连续的电压信号,该电压信号的高低起伏反映了该行图像的灰度变化。当扫描完一行,视频信号端就输出一个低于最低视频信号电压的电平(如O.3V),并保持一段时间。这样相当于紧接着每行图像信号之后会有一个电压“凹槽”,此“凹槽”叫做行同步脉

PCB自动布线之谈

CB自动布线之谈 PROTEL 2008-11-11 16:11 阅读98 评论0 字号:大中小 现在PCB设计的时间越来越短,越来越小的电路板空间,越来越高的器件密度,极其苛刻的布局规则和大尺寸的元件使得设计师的工作更加困难。为了解决设计上的困难,加快产品的上市,现在很多厂家倾向于采用专用EDA工具来实现PCB的设计。但专用的EDA工具并不能产生理想的结果,也不能达到100%的布通率,而且很乱,通常还需花很多时间完成余下的工作。 现在市面上流行的EDA工具软件很多,但除了使用的术语和功能键的位置不一样外都大同小异,如何用这些工具更好地实现PCB的设计呢?在开始布线之前对设计进行认真的分析以及对工具软件进行认真的设置将使设计更加符合要求。下面是一般的设计过程和步骤。 确定PCB的层数 电路板尺寸和布线层数需要在设计初期确定。如果设计要求使用高密度球栅阵列(BGA)组件,就必须考虑这些器件布线所需要的最少布线层数。布线层的数量以及层叠(stack-up)方式会直接影响到印制线的布线和阻抗。板的大小有助于确定层叠方式和印制线宽度,实现期望的设计效果。 多年来,人们总是认为电路板层数越少成本就越低,但是影响电路板的制造成本还有许多其他因素。近几年来,多层板之间的成本差别已经大大减小。在开始设计时最好采用较多的电路层并使敷铜均匀分布,以避免在设计临近结束时才发现有少量信号不符合已定义的规则以及空间要求,从而被迫添加新层。在设计 之前认真的规划将减少布线中很多的麻烦。 设计规则和限制 自动布线工具本身并不知道应该做些什么。为完成布线任务,布线工具需要在正确的规则和限制条件下工作。不同的信号线有不同的布线要求,要对所有特殊要求的信号线进行分类,不同的设计分类也不一样。每个信号类都应该有优先级,优先级越高,规则也越严格。规则涉及印制线宽度、过孔的最大数量、平行度、信号线之间的相互影响以及层的限制,这些规则对布线工具的性能有很大影响。认真考虑设计要求是 成功布线的重要一步。 元件的布局 为最优化装配过程,可制造性设计(DFM)规则会对元件布局产生限制。如果装配部门允许元件移动,可以对电路适当优化,更便于自动布线。所定义的规则和约束条件会影响布局设计。 在布局时需考虑布线路径(routing channel)和过孔区域,如图1所示。这些路径和区域对设计人员而言是显而易见的,但自动布线工具一次只会考虑一个信号,通过设置布线约束条件以及设定可布信号线的层, 可以使布线工具能像设计师所设想的那样完成布线。 扇出设计 在扇出设计阶段,要使自动布线工具能对元件引脚进行连接,表面贴装器件的每一个引脚至少应有一个过孔,以便在需要更多的连接时,电路板能够进行内层连接、在线测试(ICT)和电路再处理。

飞思卡尔项目书

飞思卡尔智能车比赛项目 参赛时间:2011.7.16 — 2011.7.20 赛前准备时间:2010.7 ---2011.7 飞思卡尔智能车比赛简介: 为加强大学生实践、创新能力和团队精神的培养,促进高等教育教学改革,受教育部高等教育司委托(教高司函[2005]201号文,附件1),由教育部高等学校自动化专业教学指导分委员会(以下简称自动化分教指委)主办全国大学生智能汽车竞赛。该竞赛是以智能汽车为研究对象的创意性科技竞赛,是面向全国大学生的一种具有探索性工程实践活动,是教育部倡导的大学生科技竞赛之一。该竞赛以“立足培养,重在参与,鼓励探索,追求卓越”为指导思想,旨在促进高等学校素质教育,培养大学生的综合知识运用能力、基本工程实践能力和创新意识,激发大学生从事科学研究与探索的兴趣和潜能,倡导理论联系实际、求真务实的学风和团队协作的人文精神,为优秀人才的脱颖而出创造条件。 该竞赛由竞赛秘书处设计、规范标准硬软件技术平台,竞赛过程包括理论设计、实际制作、整车调试、现场比赛等环节,要求学生组成团队,协同工作,初步体会一个工程性的研究开发项目从设计到实现的全过程。该竞赛融科学性、趣味性和观赏性为一体,是以迅猛发展、前景广阔的汽车电子为背景,涵盖自动控制、模式识别、传感技术、电子、电气、计算机、机械与汽车等多学科专业的创意性比赛。该竞赛规则透明,评价标准客观,坚持公开、公平、公正的原则,力求向健康、普及、持续的方向发展。 该竞赛以飞思卡尔半导体公司为协办方,得到了教育部相关领导、飞思卡尔公司领导与各高校师生的高度评价,已发展成全国30个省市自治区近300所高校广泛参与的全国大学生智能汽车竞赛。2008年起被教育部批准列入国家教学质量与教学改革工程资助项目中科技人文竞赛之一(教高函[2007]30号文)。 全国大学生智能汽车竞赛原则上由全国有自动化专业的高等学校(包括港、澳地区的高校)参赛。竞赛首先在各个分赛区进行报名、预赛,各分赛区的优胜队将参加全国总决赛。每届比赛根据参赛队伍和队员情况,分别设立光电组、摄像头组、电磁组、创意组等多个赛题组别。每个学校可以根据竞赛规则选报不同组别的参赛队伍。全国大学生智能汽车竞赛组织运行模式贯彻“政府倡导、专家主办、学生主体、社会参与”的16字方针,充分调动各方面参与的积极性。 全国大学生智能汽车竞赛一般在每年的10月份公布次年竞赛的题目和组织方式,并开始接受报名,次年的3月份进行相关技术培训,7月份进行分赛区竞赛,8月份进行全国总决赛。 飞思卡尔智能车比赛技术要求:

飞思卡尔智能车比赛个人经验总结

先静下心来看几篇技术报告,可以是几个人一起看,边看边讨论,大致了解智能车制作的过程及所要完成的任务。 看完报告之后,对智能车也有了大概的了解,其实总结起来,要完成的任务也很简单,即输入模块——控制——输出。 (1)输入模块:各种传感器(光电,电磁,摄像头),原理不同,但功能都一样,都是用来采集赛道的信息。这里面就包含各种传感器的原理,选用,传感器电路的连接,还有传感器的安装、传感器的抗干扰等等需要大家去解决的问题。 (2)控制模块:传感器得到了我们想要的信息,进行相应的AD转换后,就把它输入到单片机中,单片机负责对信息的处理,如除噪,筛选合适的点等等,然后对不同的赛道信息做出相应的控制,这也是智能车制作过程中最为艰难的过程,要想出一个可行而又高效的算法,确实不是一件容易的事。这里面就涉及到单片机的知识、C语言知识和一定的控制算法,有时为了更直观地动态控制,还得加入串口发送和接收程序等等。 (3)输出模块:好的算法,只有通过实验证明才能算是真正的好算法。经过分析控制,单片机做出了相应的判断,就得把控制信号输出给电机(控制速度)和舵机(控制方向),所以就得对电机和舵机模块进行学习和掌握,还有实现精确有效地控制,又得加入闭环控制,PID算法。 明确了任务后,也有了较为清晰的控制思路,接下来就着手弄懂每一个模块。虽然看似简单,但实现起来非常得不容易,这里面要求掌握电路的知识,基本的机械硬件结构知识和单片机、编程等计算机知识。最最困难的是,在做的过程中会遇到很多想得到以及想不到的事情发生,一定得细心地发现问题,并想办法解决这些问题。 兴趣是首要的,除此之外,一定要花充足的时间和精力在上面,毕竟,有付出就会有收获,最后要明确分工和规划好进度。

PCB图布线的经验总结

PCB图布线的经验总结 1.组件布置 组件布置合理是设计出优质的PCB图的基本前提。关于组件布置的要求主要有安装、受力、受热、信号、美观六方面的要求。 1.1.安装 指在具体的应用场合下,为了将电路板顺利安装进机箱、外壳、插槽,不致发生空间干涉、短路等事故,并使指定接插件处于机箱或外壳上的指定位置而提出的一系列基本要求。这里不再赘述。 1.2.受力 电路板应能承受安装和工作中所受的各种外力和震动。为此电路板应具有合理的形状,板上的各种孔(螺钉孔、异型孔)的位置要合理安排。一般孔与板边距离至少要大于孔的直径。同时还要注意异型孔造成的板的最薄弱截面也应具有足够的抗弯强度。板上直接"伸"出设备外壳的接插件尤其要合理固定,保证长期使用的可靠性。 1.3.受热 对于大功率的、发热严重的器件,除保证散热条件外,还要注意放置在适当的位置。尤其在精密的模拟系统中,要格外注意这些器件产生的温度场对脆弱的前级放大电路的不利影响。一般功率非常大的部分应单独做成一个模块,并与信号处理电路间采取一定的热隔离措施。 1.4.信号 信号的干扰PCB版图设计中所要考虑的最重要的因素。几个最基本的方面是:弱信号电路与强信号电路分开甚至隔离;交流部分与直流部分分开;高频部分与低频部分分开;注意信号线的走向;地线的布置;适当的屏蔽、滤波等措施。这些都是大量的论着反复强调过的,这里不再重复。 1.5.美观 不仅要考虑组件放置的整齐有序,更要考虑走线的优美流畅。由于一般外行人有时更强调前者,以此来片面评价电路设计的优劣,为了产品的形象,在性能要求不苛刻时要优先考虑前者。但是,在高性能的场合,如果不得不采用双面板,而且电路板也封装在里面,平时看不见,就应该优先强调走线的美观。下一小节将会具体讨论布线的"美学"。 2.布线原则 下面详细介绍一些文献中不常见的抗干扰措施。考虑到实际应用中,尤其是产品试制中,仍大量采用双面板,以下内容主要针对双面板。 2.1.布线"美学" 转弯时要避免直角,尽量用斜线或圆弧过渡。 走线要整齐有序,分门别类集中排列,不仅可以避免不同性质信号的相互干扰,也便于检查和修改。对于数字系统,同一阵营的信号线(如数据线、地址线)之间不必担心干扰的问题,但类似读、写、时钟这样的控制性信号,就应该独来独往,最好用地线保护起来。 大面积铺地(下面会进一步论述)时,地线(其实应该是地"面")与信号线

飞思卡尔智能车技术报告

第六届“飞思卡尔”杯全国大学生智能汽车邀请赛技术报告 学校: 队伍名称: 参赛队员: 带队教师:

关于技术报告和研究论文使用授权的说明 本人完全了解第六届“飞思卡尔”杯全国大学生智能汽车邀请赛关保留、使用技术报告和研究论文的规定,即:参赛作品著作权归参赛者本人,比赛组委会和飞思卡尔半导体公司可以在相关主页上收录并公开参赛作品的设计方案、技术报告以及参赛模型车的视频、图像资料,并将相关内容编纂收录在组委会出版论文集中。 参赛队员签名: 带队教师签名: 日期: 摘要 随着现代科技的飞速发展,人们对智能化的要求已越来越高,而智能化在汽车相关产业上的应用最典型的例子就是汽车电子行业,

汽车的电子化程度则被看作是衡量现代汽车水平的重要标志。同时,汽车生产商推出越来越智能的汽车,来满足各种各样的市场需求。本文以第六届全国大学生智能车竞赛为背景,主要介绍了智能车控制系统的机械及硬软件结构和开发流程。 机械硬件方面,采用组委会规定的标准 A 车模,以飞思卡尔半导体公司生产的80管脚16 位单片机MC9S12XS128MAA 为控制核心,其他功能模块进行辅助,包括:摄像头数据采集模块、电源管理模块、电机驱动模块、测速模块以及无线调试模块等,来完成智能车的硬件设计。 软件方面,我们在CodeWarrior IDE 开发环境中进行系统编程,使用增量式PD 算法控制舵机,使用位置式PID 算法控制电机,从而达到控制小车自主行驶的目的。 另外文章对滤波去噪算法,黑线提取算法,起止线识别等也进行了介绍。 关键字:智能车摄像头图像处理简单算法闭环控制无线调试 第一章引言 飞思卡尔公司作为全球最大的汽车电子半导体供应商,一直致力于为汽车电子系统提供全范围应用的单片机、模拟器件和传感器等器件产品和解决方案。飞思卡尔公司在汽车电子的半导体器件市场拥有领先的地位并不断赢得客户的

PID改进飞思卡尔智能车算法

PID改进飞思卡尔智能车算法 PID改进飞思卡尔智能车算法:智能车系统是一个时变且非线性的系统,采用传统PID算法的单一的反馈控制会使系统存在不同程度的超调和振荡现象,无法得到理想的控制效果。将前馈控制引入到了智能车系统的控制中,有效地改善了系统的实时性,提高了系统的反应速度;并且根据智能车系统的特点,对数字PID算法进行了改进,引入了微分先行和不完全微分环节,改善了系统的动态特性;同时,利用模糊控制具有对参数变化不敏感和鲁棒性强的特点,将模糊算法与PID算法相结合,有效地提高了智能车的适应性和鲁棒性,改善了系统的控制性能。 改进PID算法 智能车的控制是由飞思卡尔公司的S12芯片完成,所以对智能车的控制要采用计算机控制方法。本文针对智能车控制的特殊性,对传统数字PID算法做了一些改进,这样可以更好地满足智能车控制的需要。 不完全微分PID 将微分环节引入智能车的方向和速度控制,明显地改善了系统的动态性能,但对于误差干扰突变也特别敏感,对系统的稳定性有一定的不良影响。为了克服上述缺点,本文在PID算法中加入了一阶惯性环节,不完全微分PID算法结构如图1所示。 将一阶惯性环节直接加到微分环节上,可得到系统的传递函数为: 将(1)式的微分项推导并整理,得到方程如下: 式中,,由系统的时间常数和一阶惯性环节时间常数决定的一个常数。 为了编程方便,可以将2-2式写成如下形式:

分析式(3)可知,引入不完全微分以后,微分输出在第一个采样周期内被减少了,此后又按照一定比例衰减[3][4]。实验表明,不完全微分有效克服了智能车的偏差干扰给速度控制带来的不良影响,具有较好的控制效果。图2为不完全微分PID算法的程序流程图。 微分先行PID 由于智能车在跑道上行驶时,经常会遇到转弯的情况,所以智能车的速度设定值和方向设定值都会发生频繁的变化,从而造成系统的振荡。为了解决设定值的频繁变化给系统带来的不良影响,本文在智能车的速度和方向控制上引入了微分先行PID算法,其特点是只对输出量进行微分,即只对速度测量值和舵机偏转量进行微分,而不对速度和方向的设定值进行微分。这样,在设定值发生变化时,输出量并不会改变,而被控量的变化相对是比较缓和的,这就很好地避免了设定值的频繁变化给系统造成的振荡,明显地改善了系统的动态性能。 图3是微分先行PID控制的结构图,微分先行的增量控制算式如下。