《VHDL语言与数字逻辑电路设计》——第2讲 VHDL程序结构

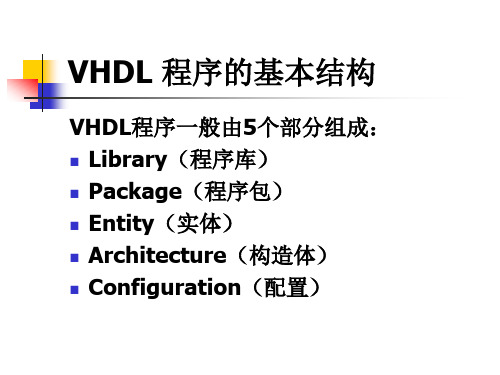

vhdl程序的基本结构vhdl程序一般由5个部分组成

块语句

块标号:BLOCK[保护表达式] [类属子句;] [端口子句;] [块说明部分;] BEGIN

<块语句部分;>

; END BLOCK 块标号

类属子句用于参数的定义;端口子句用于信号的定义; 块说明部分对该块要用到的信号、常数、元件和子程序 等进行说明;块语句部分对该块的功能进行描述,块语 句部分的语句是并行执行的,和书写顺序无关。

缺省说明: library std; use std.standard.all;

常用库及其程序包

IEEE: IEEE认可的标准库 std_logic_1164:定义了 std_logic, std_logic_vector, std_ulogic, std_ulogic_vector 等数据类型

VHDL 程序的基本结构

设计实体

实体说明

构造体

设计实体的组成

实体说明

Entity <实体名> is

[类属说明;] [端口说明;]

[实体说明部分;] [实体语句部分;] End [entity]<实体名>;

最简单的例: entity nothing is end nothing;

实体说明--类属说明

类属为设计实体和外部环境通讯的静态通信提供通道。可以定

实体说明--实体语句部分

是设计实体接口的共同部分。只能由并行断 言语句、并行过程调用语句、被动进程语 句组成,且不能在语句中给信号赋值。

设计实体

实体说明

构造体

设计实体的组成

构造体

architecture <构造体名> of <实体名> is

[构造体说明语句;]

Begin

<功能描述语句;>

第二讲_VHDL代码结构

默认库) 2)STD 库(默认库) VHDL的标准资源库,包括数据类型和 输入/输出文本等内容。库中包集有: standard和textio。 3)WORK库(默认库) WORK库 默认库) 当前工作库,当前设计的所有代码 都存放在work库中,无需声明。

5

1.2、 1.2、库的声明 在使用库之前,首先需要对库进行声明。 用关健字library说明要使用的库,用关健 字 use 说明要使用的库中的程序包。 LIBRARY library_name; USE library_name.package_name.package_parts; 库的声明总是放在实体单元前面,默认库可 不作说明。 库的作用范围:仅限于所说明的设计实体。 每一个设计实体都必须有自已完整的库说明 6 语句。

& std_ulogic(9值逻辑)) • std_logic_arith (signed、unsigned数据 类 型的算术、比较运算函数) • std_logic_signed (std_logic_vector类型 数据的一些signed运算操作函数) • std_logic_unsigned (std_logic_vector类 4 型数据的一些unsigned运算操作函数)

A EN

1

G1 EN 1 0

工作原理 G1 工作 高阻态 G2 传输结果 高阻态 B=A 工作

EN

1

B EN

G2 EN

A=B

out和 buffer 的典型结构: 用法如P112页out1/out2 的使用

10

信号的类型:BIT、STD_LOGIC、INTEGER 等; 实体ENTITY的命名:不要与VHDL关键字 冲突。 例子: 基本的与非门---纯组合逻辑

vhdl硬件描述语言与数字逻辑电路设计

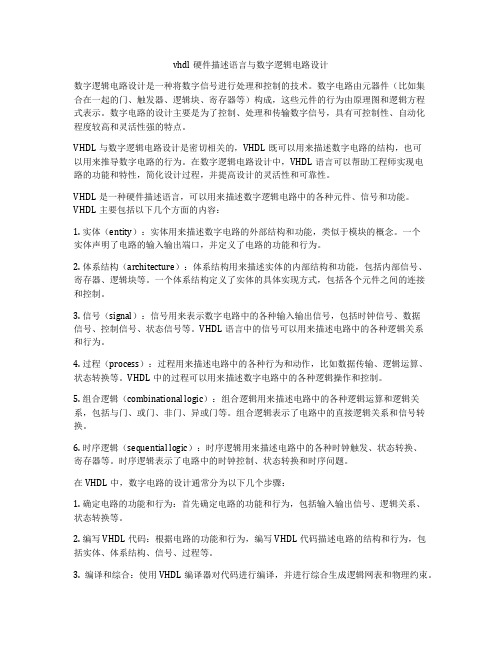

vhdl硬件描述语言与数字逻辑电路设计数字逻辑电路设计是一种将数字信号进行处理和控制的技术。

数字电路由元器件(比如集合在一起的门、触发器、逻辑块、寄存器等)构成,这些元件的行为由原理图和逻辑方程式表示。

数字电路的设计主要是为了控制、处理和传输数字信号,具有可控制性、自动化程度较高和灵活性强的特点。

VHDL与数字逻辑电路设计是密切相关的,VHDL既可以用来描述数字电路的结构,也可以用来推导数字电路的行为。

在数字逻辑电路设计中,VHDL语言可以帮助工程师实现电路的功能和特性,简化设计过程,并提高设计的灵活性和可靠性。

VHDL是一种硬件描述语言,可以用来描述数字逻辑电路中的各种元件、信号和功能。

VHDL主要包括以下几个方面的内容:1. 实体(entity):实体用来描述数字电路的外部结构和功能,类似于模块的概念。

一个实体声明了电路的输入输出端口,并定义了电路的功能和行为。

2. 体系结构(architecture):体系结构用来描述实体的内部结构和功能,包括内部信号、寄存器、逻辑块等。

一个体系结构定义了实体的具体实现方式,包括各个元件之间的连接和控制。

3. 信号(signal):信号用来表示数字电路中的各种输入输出信号,包括时钟信号、数据信号、控制信号、状态信号等。

VHDL语言中的信号可以用来描述电路中的各种逻辑关系和行为。

4. 过程(process):过程用来描述电路中的各种行为和动作,比如数据传输、逻辑运算、状态转换等。

VHDL中的过程可以用来描述数字电路中的各种逻辑操作和控制。

5. 组合逻辑(combinational logic):组合逻辑用来描述电路中的各种逻辑运算和逻辑关系,包括与门、或门、非门、异或门等。

组合逻辑表示了电路中的直接逻辑关系和信号转换。

6. 时序逻辑(sequential logic):时序逻辑用来描述电路中的各种时钟触发、状态转换、寄存器等。

时序逻辑表示了电路中的时钟控制、状态转换和时序问题。

VHDL语言的基本结构

4

一、VHDL语言设计的基本单元及其构成

3)端口说明 PORT(端口名{,端口名}:方向 数据类型; 是对设计实体与外部接口 的描述,即对元件引脚、 ┇ 数据类型和I/O方向的描述 端口名{,端口名}:方向 数据类型); 1端口名

设计实体

进程 或其它并行结构 结构体 n (ARCHITECTURE 进程 或其它并行结构

配置(CONFIGURATION)

VHDL程序设计实体的一般结构

2

VHDL语言的基本结构

主要内容

一、 VHDL语言设计的基本单元及其构成 二、 VHDL语言构造体的子结构描述 三、 包集合、库及配置

3

一、VHDL语言设计的基本单元及其构成

VHDL语言

15

二、VHDL语言构造体的子结构描述

【例】4位二进制加法计数器构造体逻辑描述。

SIGNAL cnt4:INTEGER RANGE O TO 15; ... PROCESS(clk,clear,Stop) BEGIN IF clear='0' THEN cnt4<=0; ELSIF clk'EVENT AND clk='1' THEN IF stop='0' THEN cnt4<=cnt4+1; END IF; END IF; END PROCESS; --注意cnt4的数据类型

存盘文件 为 bpac.vhd

VHDL程序的基本结构

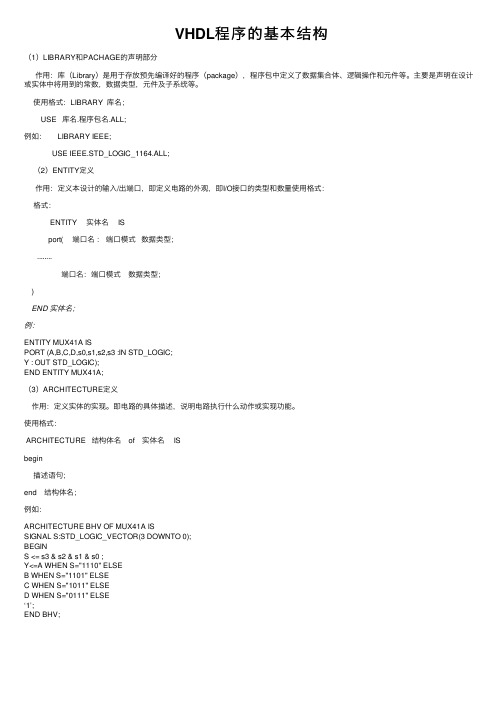

VHDL程序的基本结构(1)LIBRARY和PACHAGE的声明部分作⽤:库(Library)是⽤于存放预先编译好的程序(package),程序包中定义了数据集合体、逻辑操作和元件等。

主要是声明在设计或实体中将⽤到的常数,数据类型,元件及⼦系统等。

使⽤格式:LIBRARY 库名;USE 库名.程序包名.ALL;例如: LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;(2)ENTITY定义作⽤:定义本设计的输⼊/出端⼝,即定义电路的外观,即I/O接⼝的类型和数量使⽤格式:格式:ENTITY 实体名 ISport( 端⼝名:端⼝模式数据类型;........端⼝名:端⼝模式数据类型;)END 实体名;例:ENTITY MUX41A ISPORT (A,B,C,D,s0,s1,s2,s3 :IN STD_LOGIC;Y : OUT STD_LOGIC);END ENTITY MUX41A;(3)ARCHITECTURE定义作⽤:定义实体的实现。

即电路的具体描述,说明电路执⾏什么动作或实现功能。

使⽤格式:ARCHITECTURE 结构体名 of 实体名 ISbegin描述语句;end 结构体名;例如:ARCHITECTURE BHV OF MUX41A ISSIGNAL S:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINS <= s3 & s2 & s1 & s0 ;Y<=A WHEN S="1110" ELSEB WHEN S="1101" ELSEC WHEN S="1011" ELSED WHEN S="0111" ELSE‘1’;END BHV;。

VHDL第二章课件

(6)Character(字符)。

是用单引号括起来的一个字母(A~Z, a~z) 、数字( 0~ 9 )、空格或一些特殊字符(如$、@、%等)。

VHDL语言对大小写英文字母不敏感, 但区分字符量中的大小写。 (‘7A)’S,tr‘inag’(,字‘符串B’),。‘是b用’双, 引都号认括为起是来不的同一的个字字符符。序字列。符 字‘符1’串,区‘分2’大仅、是小符写号字。母。常用于程序的提示和结果说明等。例 如“VHDL”, “STRING”, “MULTI_SCREEN COMPUTER”等。 (8)Time(时间)。时间的取值范围从 -(231-1)~(231 -1)。时间由整数值和时间单位组成。常用的时间单位有: fs、 ns、μs、ms、s、min、hr等。时间类型一般用于仿真,而不用 逻辑综合。时间常用于指定时间延时和标记仿真时刻。

(4) 扩展标识符的界定符两个斜杠之间可以用数字打头。 如:

2.2 数据对象

在VHDL中,凡是可以赋予一个值的客体称为数据对象。常 用的数据对象为常量、变量 、信号和文件,其中文件类型是 VHDL’93标准中新通过的。

对象说明的一般书写格式为:

对象类别 标识符表: 子类型标识[:= 初值];

对象说明举例: CONSTANT T1,T2: time :=30ns,--常量说明 VARIABLE SUM: read; --变量说明

• VHDL语言有两个标准版: VHDL’87版和 VHDL’93版。VHDL’87版的标识符语法规则经 过扩展后,形成了VHDL’93版的标识符语法规则。 前一部分称为短标识符,扩展部分称为扩展标识符。 VHDL’93版含有短标识符和扩展标识符两部分。

2.1.1 短标识符

短标识符规则: 短标识符由字母、数字以及下划线字符组成,且具

第2章 VHDL语言程序的基本结构

第2章

VHDL语言程序的基本结构

1.设计思路

根据数字电子技术的知识,我们知道,74LS00是 一个四—2输入与非门,亦即该芯片由四个2输入与非门 组成,因此我们设计时可先设计一个2输入与非门(如 图2.1(a)所示),再由四个2输入与非门构成一个整体—— MY74LS00(如图2.1(b)所示)。

也就是说我们实际做的程序,并不象开始所 列的那样必须包含5部分,通常下面结构才是基 本的和必需的

Use定义区

Entity定义区

Architecture定义区

我们以一个实际的例子来看一下 VHDL语言基本语法结构 Use定义区应写成

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; USE IEEE.STD_LOGIC_ARITH.ALL; USE IEEE.STD_LOGIC_UNSIGNED.ALL;

48

7

Entity定义区写成

ENTITY example IS PORT( Pin48 : IN STD_LOGIC; Pin7 : OUT STD_LOGIC ); END example;

Architecture 定义区写成

ARCHITECTURE BEHAV OF example IS BEGIN Pin7<=Pin48; END BEHAV;

--元件连接说明

第2章

VHDL语言程序的基本结构

BEGIN

U1:NAND2 PORT MAP(A=>A1,B=>B1,Y=>Y1); U2:NAND2 PORT MAP(A=>A2,B=>B2,Y=>Y2); U3:NAND2 PORT MAP(A3, B3, Y3); U4:NAND2 PORT MAP(A4, B4, Y4);

简要写出vhdl程序的设计结构

简要写出vhdl程序的设计结构下载提示:该文档是本店铺精心编制而成的,希望大家下载后,能够帮助大家解决实际问题。

文档下载后可定制修改,请根据实际需要进行调整和使用,谢谢!本店铺为大家提供各种类型的实用资料,如教育随笔、日记赏析、句子摘抄、古诗大全、经典美文、话题作文、工作总结、词语解析、文案摘录、其他资料等等,想了解不同资料格式和写法,敬请关注!Download tips: This document is carefully compiled by this editor. I hope that after you download it, it can help you solve practical problems. The document can be customized and modified after downloading, please adjust and use it according to actual needs, thank you! In addition, this shop provides you with various types of practical materials, such as educational essays, diary appreciation, sentence excerpts, ancient poems, classic articles, topic composition, work summary, word parsing, copy excerpts, other materials and so on, want to know different data formats and writing methods, please pay attention!好的,根据您的要求,我将为您撰写一篇关于VHDL程序设计结构的中文演示文章。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

许钢

2011-2-13

《VHDL语言与数字逻辑电路设计》

11

第2讲 VHDL程序结构

2.5 MaxPlus II、Quartus II使用指南 、 使用指南

• • • • • 安装; License.dat文件的管理; VHDL源文件编辑; 仿真; 编程下载。

许钢

2011-2-13

《VHDL语言与数字逻辑电路设计》

许钢

2011-2-13

《VHDL语言与数字逻辑电路设计》

6

第2讲 VHDL程序结构

2.2 结构体 结构体

VHDL把一个电路模块看作一个单元,对任何一个单元的描述包括 接口描述和内部特性描述 内部特性描述两个部分。接口描述称为设计实体,它提供该 接口描述 内部特性描述 单元的公共信息,如名称、端口等;内部特性描述称为结构体,它定义 单元的内部操作特性,描述实体端口间的逻辑关系。 结构体的语句格式: 结构体的语句格式: ARCHITECTURE 结构体名 OF 实体名 IS [ 说明语句 ] BEGIN [ 功能描述语句 ] END ARCHITECTURE 结构体名 结构体名;

许钢

2011-2-13

《VHDL语言与数字逻辑电路设计》

10

第2讲 VHDL程序结构

2.4 库、程序包

常用的程序包: 常用的程序包: Std_logic_1164 属于IEEE库,包含常用的数据类型。 属于 库 包含常用的数据类型。 Std_logic_arith Std_logic_unsigned Std_logic_signed 属于IEEE库,由Synopsys公司开发,扩展了一些数据类型和算术 公司开发, 属于 库 公司开发 运算符。 运算符。 例:USE IEEE.std_logic_arith.all

许钢

2011-2-13

第2讲 VHDL程序结构

2.4 库、程序包

库的调用说明: •库的调用说明: 库的调用说明 LIBRARY 库名; 库名; •例: 例 LIBRARY IEEE; --使用 使用IEEE库 使用 库

•库的使用: 库的使用: 库的使用 USE 库名 程序包名 项目名; USE IEEE.STD_LOGIC_1164.ALL; 库名.程序包名 项目名; 程序包名.项目名 --使用 使用IEEE库中 库中STD_LOGIC_1164程序包 使用 库中 程序包 --的所有项目 的所有项目 库的种类: 库的种类: •IEEE库:使用时必须声明。 库 使用时必须声明。 •STD库:VHDL的标准库,可以不声明(由具体开发环境决定)。 的标准库, 库 的标准库 可以不声明(由具体开发环境决定)。 •WORK库:用户设计的现行工作库,可以不声明(由具体开发环境决定) 。 库 用户设计的现行工作库,可以不声明(由具体开发环境决定)

"00" =>o<="0001"; "01" =>o<="0010"; "10" =>o<="0100"; "11" =>o<="1000"; others =>o<="XXXX";

许钢

2011-2-13

《VHDL语言与数字逻辑电路设计》

2

第2讲 VHDL程序结构

例2-1:文件 文件d24_conc.vhd

12

第2讲 VHDL程序结构

第二讲 (完)

许钢

2011-2-13

《VHDL语言与数字逻辑电路设计》

13

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; --使用 使用IEEE库 使用 库 --使用程序包 使用程序包

ENTITY d24_conc IS PORT ( i: in std_logic_vector(1 downto 0); o: out std_logic_vector(3 downto 0)); END ENTITY d24_conc; ARCHITECTURE a of d24_conc is begin process(i) begin case i is when when when when when end case; end process; END ARCHITECTURE a;

"00" =>o<="0001"; "01" =>o<="0010"; "10" =>o<="0100"; "11" =>o<="1000"; others =>o<="XXXX";

许钢

2011-2-13

《VHDL语言与数字逻辑电路设计》

3

第2讲 VHDL程序结构

2.1 实体

VHDL把一个电路模块看作一个单元,对任何一个单元的描述包括 接口描述和内部特性描述 内部特性描述两个部分。接口描述称为设计实体,它提供该 接口描述 内部特性描述 单元的公共信息,如名称、端口等;内部特性描述称为结构体,它定义 单元的内部操作特性,描述实体端口间的逻辑关系。 实体说明单元: 实体说明单元: ENTITY 实体名 IS [ GENERIC(类属表 ;] 类属表); 类属表 [ PORT(端口表 端口表); ] 端口表 END ENTITY 实体名 实体名; 要求: 源程序文件名必须与实体名一致! 要求:VHDL源程序文件名必须与实体名一致! 源程序文件名必须与实体名一致

许钢

2011-2-13

《VHDL语言与数字逻辑电路设计》

4

第2讲 VHDL程序结构

2.1 实体

类属说明语句: 类属说明语句: GENERIC(常数名: 数据类型: 设定值; 常数名: 数据类型: 设定值; 常数名 常数名: 数据类型: 设定值; 常数名: 数据类型: 设定值;……

例:GENERIC ( width1: INTEGER:=8; width2: INTEGER:=15); 在MaxPlus II环境下,对输入信号的位宽谨慎使用! 例如: 例如: ENTITY d24_conc IS GENERIC(width1: INTEGER:=3); PORT (i: in std_logic_vector(width1-2 downto 0); o: out std_logic_vector(width1 downto 0)); END ENTITY d24_conc; ARCHITECTURE a of d24_conc is begin process(i) --编译将会出错! 编译将会出错! 编译将会出错 ………… END ARCHITECTURE a;

ENTITY d24_conc IS PORT ( i: in std_logic_vector(1 downto 0); o: out std_logic_vector(3 downto 0)); END ENTITY d24_conc; ARCHITECTURE a of d24_conc is begin process(i) begin case i is when when when when when end case; end process; END ARCHITECTURE a;

许钢

2011-2-13

《VHDL语言与数字逻辑电路设计》

7

第2讲 VHDL程序结构

2.2 结构体 结构体

并行执行! 并行执行!

许钢

2011-2-13

《VHDL语言与数字逻辑电路设计》

8

第2讲 VHDL程序结构

2.3 配置

每个实体可以有多个结构体,配置(configuration)可以为实 体指定一个特定的结构体。此外还有元件配置、块配置等。

VHDL语言 与数字逻辑电路设计

主讲:许钢 2010.9

许钢 《VHDL语言与数字逻辑电路设计》 1

2011-2-13

第2讲 VHDL程序结构

例2-1:文件 文件d24_conc.vhd

LIBRARY IEEE; USE IEEE.STD_LOGIC_1164.ALL; --使用 使用IEEE库 使用 库 --使用程序包 使用程序包

许钢

2011-2-13

); ;

《VHDL语言与数字逻辑电路设计》

5

第2讲 VHDL程序结构

2.1 实体

端口说明语句: 端口说明语句: PORT(端口名: 端口模式 数据类型; 端口名: 数据类型; 端口名 端口名: 数据类型; ); 端口名: 端口模式 数据类型; …… ; 端口相当于这个实体元件的管脚或与其它模块联系的信号线。 端口相当于这个实体元件的管脚或与其它模块联系的信号线。 端口模式: 端口模式:

例: ENTITY d24_conc IS PORT ( i: in std_logic_vector(1 downto 0); o: out std_logic_vector(3 downto 0)); END ENTITY d24_conc; ARCHITECTURE a of d24_conc is …… END ARCHITECTURE a; ARCHITECTURE b of d24_conc is …… END ARCHITECTURE b; CONFIGURATION conf1 OF d24_conc IS FOR a END FOR; END conf1; 《VHDL语言与数字逻辑电路设计》 9