计算机组成与设计(王诚)课后答案第二章

计算机组成课后习题答案

闪存可以分为NOR Flash和NAND Flash两种类型。

工作原理

闪存的主要功能是可擦写、非易失性存储数据。NOR Flash读取速度快,适用于代码存储;NAND Flash容量大 、成本低,适用于大量数据的存储。闪存的擦除和编程操作需要特定的电压和时序。

04

输入输出设备

键盘的工作原理与分类

THANKS

感谢观看

成字符或汉字。

05

数据传输方式

并行传输与串行传

并行传输

指数据以多个通道同时传输,适用于近距离、高速传输,如 CPU与内存之间的数据交换。

串行传输

指数据一位一位地顺序传输,适用于远距离、低速传输,如 网络通信。

数据传输速率

数据传输速率

指单位时间内传输的数据量,通常以比特率(bit per second)表示。

影响数据传输速率的因素

包括信号带宽、信噪比、误码率等。

数据传输过程中的同步与异步问题

同步传输

指发送方和接收方的时钟信号保持同 步,适用于高速数据传输。

异步传输

指发送方和接收方的时钟信号不需同 步,适用于低速数据传输。

06

操作系统基础知识

操作系统的功能与分类

要点一

功能

操作系统是计算机系统的核心软件,负责管理计算机硬件 和软件资源,提供用户与计算机交互的界面。

硬盘的分类与工作原理

分类

硬盘可以分为机械硬盘(HDD)和固态硬盘(SSD)。

工作原理

硬盘的主要功能是永久存储数据。HDD采用磁记录技术,将数据以磁道的形式存 储在旋转的盘片上;SSD则采用闪存技术,通过电子方式存储数据。HDD的读取 速度较慢,但价格较低;SSD的读取速度较快,但价格较高。

大学计算机第二章习题答案教学教材

大学计算机第二章习题答案1.简述冯诺依曼体系结构。

采用“存储程序”,即程序和数据一起存储在内存中,计算机按照程序顺序执行,采用二进制表示数据,且计算机由5部分组成:运算器、控制器、存储器、输入设备、输出设备。

2.简述计算机的五大组成部分。

运算器、控制器、存储器、输入设备、输出设备。

3.简述计算机的基本工作原理。

计算机的工作过程是程序执行的过程。

程序是为实现特定目标而用程序设计语言描述的指令序列。

计算机在运行时,先从内存中取出第一条指令,通过控制器的译码分析,并按指令要求从存储器中取出数据进行指定的运算或逻辑操作,然后再按地址把结果送到内存中,接着按照程序的逻辑结构有序地取出第二条指令,在控制器的控制下完成规定操作。

4.什么是流水线技术?作用是什么?流水线技术:将不同指令的各个步骤通过多个硬件处理单元进行重叠操作作用:实现几条指令的并行处理,以加速程序运行进程。

5.ROM和RAM的作用和区别是什么?ROM:只读存储器,主要用于存放计算机的启动程序。

RAM:随机存取储存器,通常所说的内存,RAM里的内容可按其地址随时进行存取。

区别:RAM的特点是数据存取速度较快,但是掉电后数据不能保存。

ROM的数据只能被读取而不能写入,如果要更改,就需要紫外线来擦除。

6.系统软件和应用软件各自的作用是什么?系统软件:控制和维护计算机的正常运行,管理计算机的各种资源,以满足应用软件的需要。

应用软件:完成一个特定的任务,在系统软件的支持下才能运行。

7.总线的概念是什么?简述总线类型。

概念:总线是各部件(或设备)之间传输数据的公用通道。

类型:按功能和规范:数据总线、地址总线、控制总线、扩展总线、局部总线按传输数据的方式:串行总线、并行总线按时钟信号是否独立:同步总线、异步总线8.什么是主板?它主要有哪些部件?各部件之间如何连接?主板:即母板,是微型计算机中最大的一块集成电路板,也是其它部件和各种外部设备的连接载体。

部件:芯片:芯片组、BIOS芯片、集成芯片等插槽/接口:CPU插座、内存条插槽、PCI插槽、PCI-E插槽、SATA接口、键盘/鼠标接口、USB接口、音频接口、HDMI接口。

计算机组成与设计答案

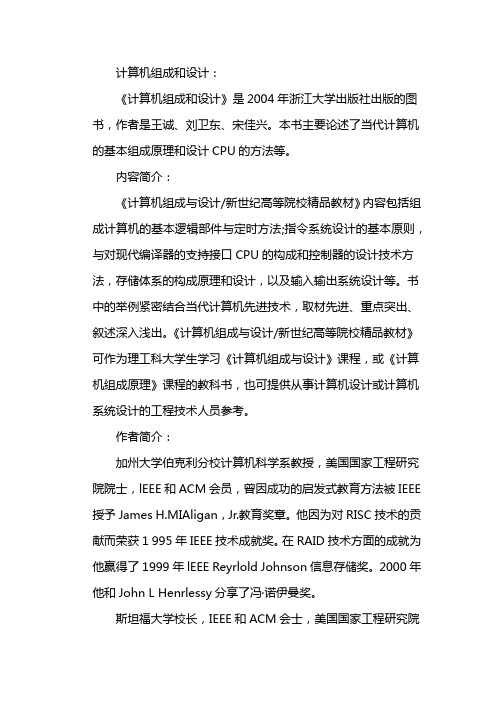

计算机组成和设计:

《计算机组成和设计》是2004年浙江大学出版社出版的图书,作者是王诚、刘卫东、宋佳兴。

本书主要论述了当代计算机的基本组成原理和设计CPU的方法等。

内容简介:

《计算机组成与设计/新世纪高等院校精品教材》内容包括组成计算机的基本逻辑部件与定时方法;指令系统设计的基本原则,与对现代编译器的支持接口CPU的构成和控制器的设计技术方法,存储体系的构成原理和设计,以及输入输出系统设计等。

书中的举例紧密结合当代计算机先进技术,取材先进、重点突出、叙述深入浅出。

《计算机组成与设计/新世纪高等院校精品教材》可作为理工科大学生学习《计算机组成与设计》课程,或《计算机组成原理》课程的教科书,也可提供从事计算机设计或计算机系统设计的工程技术人员参考。

作者简介:

加州大学伯克利分校计算机科学系教授,美国国家工程研究院院士,lEEE和ACM会员,曾因成功的启发式教育方法被IEEE 授予James H.MIAligan,Jr.教育奖章。

他因为对RISC技术的贡献而荣获1 995年IEEE技术成就奖。

在RAID技术方面的成就为他赢得了1999年lEEE Reyrlold Johnson信息存储奖。

2000年他和John L Henrlessy分享了冯·诺伊曼奖。

斯坦福大学校长,IEEE和ACM会士,美国国家工程研究院

院士及美国科学艺术研究院院士。

Hen rlessy教授因为在RISC 技术方面做出了突出贡献而荣获2001年的Eckert—MatJchly 奖章,他也是2001年SeymIour Cray计算机工程奖得主,并且和David A.Pattersorl分享了2000年的冯·诺伊曼奖。

计算机组成与设计课后答案

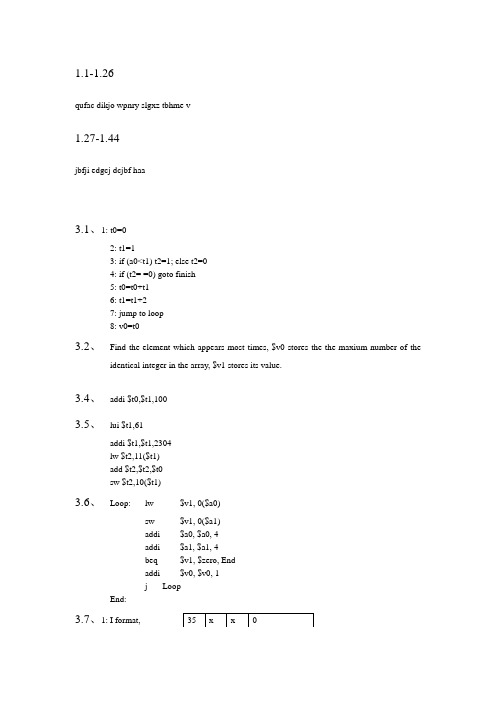

1.1-1.26qufac dikjo wpnry slgxz tbhme v1.27-1.44jbfji edgcj dcjbf haa3.1、1: t0=02: t1=13: if (a0<t1) t2=1; else t2=04: if (t2= =0) goto finish5: t0=t0+t16: t1=t1+27: jump to loop8: v0=t03.2、Find the element which appears most times, $v0 stores the the maxium number of theidentical integer in the array, $v1 stores its value.3.4、addi $t0,$t1,1003.5、lui $t1,61addi $t1,$t1,2304lw $t2,11($t1)add $t2,$t2,$t0sw $t2,10($t1)3.6、Loop: lw $v1, 0($a0)sw $v1, 0($a1)addi $a0, $a0, 4addi $a1, $a1, 4beq $v1, $zero, Endaddi $v0, $v0, 1j LoopEnd:3.7、1: I format,3: I format,4: I format,5: I format,6: I format,3.8、v0=0;v1=a0;v0++;a1=v1;a0++;a1++;if(v1= =0) goto loop;v0--;3.9、bne $t0,$s5,exitloop: add $t1,$s3,$s3add $t1,$t1,$t1add $s3,$s3,$s6lw $t0,0(t1)beq $t0,$s5,loop exit:3.11、slti $t5,$t0,1bne $t0,1,exitloop: addi $t0,$zero,0add $t4,$t0,$t0add $t4,$t4,$t4lw $t1,0($a0)add $t2,$t4,$t1add $t3,$a1,$t1sw $t2,0($t3)addi $t0,$t0,1slti $t5,$t0,101beq $t5,1,loopexit:3.23、loop: addi $t0,$zero,98lb $t1,0($a0)addi $a0,$a0,1beq $t1,$zero,exitbne $t1,$t0,loopbeq $t1,$t0,nextsub $v0,$a0,1exit: add $v0,$zero,$zeronext:3.24、bcount: addi $sp,$sp,-12sw $ra,8($sp)sw $a0,4($sp)sw $s0,0($sp)add $s0,$zero,$zeroNext: jal bfindadd $a0,$v0,$zerolb $t0,0($a0)beq $t0,$zero,End #encounter nulladdi $s0,$s0,1addi $v0,$v0,1j NextEnd: add $v0,$s0,$zerolw $s0,0($sp)lw $a0,4($sp)lw $ra,8($sp)addi $sp,$sp,12jr $ra4.1、000000000000000000000010000000004.2、111111111111111111111100000000014.4、-5004.5、-14.6、21474836474.10、loop: sub $t3,$zero,$t3slt $t0,$t3,$zerobeq $t0,$zero,loopadd $t2,$t3,$zero how to use 3 instructions?4.13、If A_lower is positive, A_upper_adjusted equals to A_upper.If A_lower is negative, A_upper_adjusted equals to A_upper+1.4.17、addu $t0, $t3,$t4sltu $t2,$t0,$t34.22、srl $t0,$s0,8andi $s1,$t0,40954.23、when it overflew , set should be converted .4.40、xor $s0,$s0,$s1xor $s1,$s1,$s0xor $s0,$s0,$s14.46、ripple carry c1=a0*c0+b0*c0+a0*b0 2Tc2=a1*c1+b1*c1+a1*b1 4Tc3=a2*c2+b2*c2+a2*b2 6TThe worst case : c4=a3*c3+b3*c3+a3*b3 8TCarry look ahead : gi=ai*bi T pi=ai+bi Tc1=c2=c3=c4=3T4.53、4.54、step1 6.42*101=0.642*102step2 9.51*102+0.642*102=10.152*102step3 10.152*102=1.0152*102step4 1.0152*103 is rounded to three significant digits 1.015*1034.55、6.42X101=0.642X1020.642+9.51=10.1526.42X101+9.51X102=10.152X102=1.0152X103so the answer is 1.02X1035.1、RegDst=0 lw sw and branchAluSrc=0 R-format beqMemtoReg=0 R-format sw and beqZero=0 R-format sw and lw5.2、RegDst=1 R-format sw and beqAluSrc=1 lw and swMemtoReg=1 lw sw and beqZero=1 R-format lw and sw5.6、修改两个信号:MemtoReg: 00 :Alu result01 :From Mem data10 :PC+4RegDst: 00 : Instruction[20-16]01 :Instruction[15-11]10 :$ra寄存器5.8、lw $t0 ,$t1,$t25.14、P374页图Instruction a b cR-formatlwswbeqjlongest8 10 10time5.165.17、5.22、jr rsIt is an R-type instruction.So the changes can be made like following .5.24、M1=5*22%+4*11%+4*49%+3*16%+3*2%=4.04M2=4*22%+4*11%+3*49%+3*16%+3*2%=3.33M3=3*22%+3*11%+3*49%+3*16%+3*2%=3So the CPU excution time isT1=CPI*Clockcycletime=4.04/(500*106 )=8.08nsT2=3.33/(400*106 )=8.325nsT3=3/(250*106 )=12nsHence M1 is the fastest machine.5.26、beq $t3,$zero,Exitadd $t3,$t3,$t3add $t3,$t3,$t3 #get 4*$t3add $t3,$t3,$t2 #caculate the address of destination[$t3] loop: lw $t4,0($t1)sw $t4,0($t2)addi $t1,$t1,4addi $t2,$t2,4bne $t2,$t3,loopExit:branch 3 lw 5 and the rest are 4The number of executed instructions is 4+5*100=504The nmber of cycles is3+3*4+(5+4*3+3)*100=20155.27、1. According to the figure above there will be two changes.1>Extend the multiplexor for ALUSrcA by adding ALUout to it .We mark it with 102> We add a multiplexor between B and Memory write data ,connect memory dataregister with the multiplexor and mark it with 1.The multi is controled by the ]signal bcp.2. By making these changes ,we can directly increase the address $t1,$t2,in ALUout by 4When the memory data loading from $t1is read into memory data register, we canquickly write it into memory by setting bcp to 0.3. By estination ,we can cut down clock cycles distinctively by implementing theinstruction in hardware above .The performance increase comes from adding internal registers.7.7、7.8、7.9、212*(32*4+16+1)=580Kb7.11、a. 1+16*10+16*1=177 clock cyclesb. 1+4*10+4*1=45 clock cyclesc. 1+4*10+16*1=57 clock cycles7.12、The CPI of a is 1.2+0.5%*177=2.085The CPI of b is 1.2+0.5%*45=1.425The CPI of c is 1.2+0.5%*57=1.485The processor using wide memory is 2.085/1,425=1.46 times faster than using nerrowand 1.04 times faster than the one using interleaved memories.7.15、AMAT=(1+0.05*20)*2ns=4ns7.20、7.22、7.24、The number of sets in the cache: S/ABThe number of index bits in the address: log2(S/AB)The number of bits needed to implement the cache : Tag =k- log2(S/AB)-log2B7.27、Cache1: X+(4%+0.5*8%)*7=2So,X=1.44Cache2: 1.44+(2%+0.5*5%)*10=1.85Cache3: 1.44+(2%+0.5*4%)*10=1.84Thus,machine1spemds the most cycles on cache mises.7.32、Page size is 16-KB=214B240/214=226Total size of bits 226*(36-14+4)=208MB7.33、Virtual addressCache hit8.1 A 200 1000/5B 150 750/58.2 (1)n*5*(1/1000)+n*(1/10)*(20/1000)=1 n=142(2)5*n*(1/750)+500/5*(1/10)*18*(1/1000)+(5n-500)/5/5/10*25/1000 =1 n=1168.3 7和8距离近的那张图,原因是路程短8.10 a=1+19.7ms/5ns+2+2=3.9*10^6 cyclesb=3.94*10^6*128/4=1.26*10^8cycles) 32/b=50.798/a=12.750.79 12.78.18 17.84。

计算机组成与系统结构第二章课后作业参考答案

该浮点数真值 1.101×2-1 十进制表示形式 0.8125

• The following numbers use the 32-bit IEEE 754 format. What is the equivalent decimal value? c. 00000000010000000000000000000000 阶码真值 = 00000000 - 01111111= -01111111 尾数真值 = 1.1 该浮点数真值 1.1×2-01111111

= 2.3ቤተ መጻሕፍቲ ባይዱ6

效率 E

n t i

i 1

m

m[ t i (n 1)t j ]

i 1

m

=

50×(6+9+7) 3×[(6+9+7)+49×9]

= 79%

(2)对阶,尾数加 - y的尾数S-y右移1位,阶码加1 S-y = 00.1010000000 Sx + S-y = 01.0010000000 (3)规格化 00.0101000000

尾数溢出,右移1位,阶码加1 Sx + S-y = 00.1001000000 阶码[E ]移 = [Ex ]移 + [1]补 = 0,101 + 0,001 = 0,110

计算机组成与设计第四版第二章答案

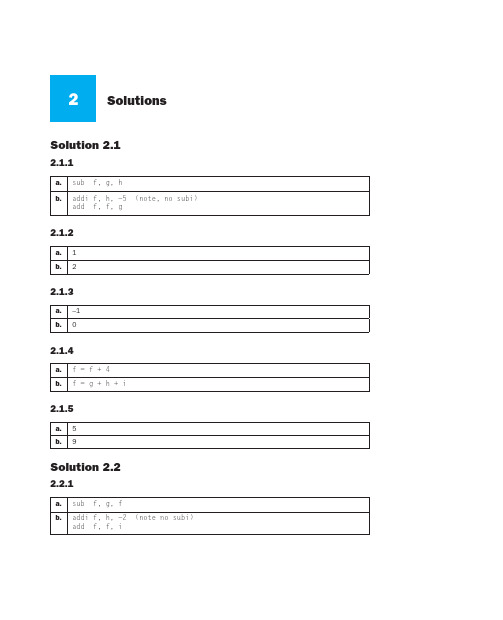

2 SolutionsSolution 2.12.1.1a.sub f, g, hb.addi f, h, −5 (note, no subi)add f, f, g2.1.2a.1b.22.1.3a.−1b.02.1.4a. f = f + 4b. f = g + h + i2.1.5a.5b.9Solution 2.22.2.1a.sub f, g, fb.addi f, h, −2 (note no subi)add f, f, iS2 ChapterSolutions22.2.2a.1b.22.2.3a.1b.22.2.4a. f += 4;b. f = i − (g + h);2.2.5a.5b.−1Solution 2.32.3.1a.sub f, $0, fsub f, f, gb.sub f, $0, faddi f, f, −5 (note, no subi)add f, f, g2.3.2a.2b.32.3.3a.−3b.−3Chapter 2 Solutions S32.3.4a. f += −4b. f += (g + h);2.3.5a.−3b.6Solution 2.42.4.1a.lw $s0, 16($s6)sub $s0, $0, $s0sub $s0, $s0, $s1b.sub $t0, $s3, $s4add $t0, $s6, $t0lw $t1, 16($t0)sw $t1, 32($s7)2.4.2a.3b.42.4.3a.3b.62.4.4a. f = 2j + i + g;b.B[g] = A[f] + A[1+f];S4 Chapter2Solutions2.4.5a.slli $s2, $s4, 1add $s0, $s2, $s3add $s0, $s0, $s1b.add $t0, $s6, $s0add $t1, $s7, $s1lw $s0, 0($t0)lw $t0, 4($t0)add $t0, $t0, $s0sw $t0, 0($t1)2.4.6a. 5 as written, 5 minimallyb.7 as written, 6 minimallySolution 2.52.5.1a. Address Data20 424 528 332 234 1temp = Array[0]; temp2 = Array[1]; Array[0] = Array[4]; Array[1] = Array[3]; Array[3] = temp; Array[4] = temp2;b. Address Data24 238 432 336 640 1temp = Array[0]; temp2 = Array[1]; Array[0] = Array[4]; Array[1] = temp; Array[4] = Array[3]; Array[3] = temp2;2.5.2a. Address Data20 424 528 332 234 1temp = Array[0];temp2 = Array[1];Array[0] = Array[4];Array[1] = Array[3];Array[3] = temp;Array[4] = temp2;lw $t0, 0($s6)lw $t1, 4($s6)lw $t2, 16($s6)sw $t2, 0($s6)lw $t2, 12($s6)sw $t2, 4($s6)sw $t0, 12($s6)sw $t1, 16($s6)Chapter 2 Solutions S5b. Address Data24 238 432 336 640 1temp = Array[0];temp2 = Array[1];Array[0] = Array[4];Array[1] = temp;Array[4] = Array[3];Array[3] = temp2;lw $t0, 0($s6)lw $t1, 4($s6)lw $t2, 16($s6)sw $t2, 0($s6)sw $t0, 4($s6)lw $t0, 12($s6)sw $t0, 16($s6)sw $t1, 12($s6)2.5.3a. Address Data20 424 528 332 234 1temp = Array[1];Array[1] = Array[5];Array[5] = temp;temp = Array[2];Array[2] = Array[4];temp2 = Array[3];Array[3] = temp;Array[4] = temp2;lw $t0, 0($s6)lw $t1, 4($s6)lw $t2, 16($s6)sw $t2, 0($s6)lw $t2, 12($s6)sw $t2, 4($s6)sw $t0, 12($s6)sw $t1, 16($s6)8 MIPS instructions,+1 MIPS inst. for everynon-zero offset lw/swpair (11 MIPS inst.)b. Address Data24 238 432 336 640 1temp = Array[3];Array[3] = Array[2];Array[2] = Array[1];Array[1] = Array[0];Array[0] = temp;lw $t0, 0($s6)lw $t1, 4($s6)lw $t2, 16($s6)sw $t2, 0($s6)sw $t0, 4($s6)lw $t0, 12($s6)sw $t0, 16($s6)sw $t1, 12($s6)8 MIPS instructions, +1MIPS inst. for every non-zero offset lw/sw pair(11 MIPS inst.)2.5.4a.2882400018b.2705449602.5.5a. Address Data12 ab8 cd4 ef0 12 Address Data 12 12 8 ef 4 cf 0 abb. Address Data12 108 204 300 40 Address Data 12 40 8 30 4 20 010S6 ChapterSolutions2Solution 2.62.6.1a.lw $t0, 4($s7) # $t0 <-- B[1]sub $t0, $t0, $s1 # $t0 <-- B[1] − gadd $s0, $t0, $s2 # f <-- B[1] −g + hb.sll $t0, $s1, 2 # $t0 <-- 4*gadd $t0, $t0, $s7 # $t0 <-- Addr(B[g])lw $t0, 0($t0) # $t0 <-- B[g]addi $t0, $t0, 1 # $t0 <-- B[g]+1sll $t0, $t0, 2 # $t0 <-- 4*(B[g]+1) = Addr(A[B[g]+1])lw $s0, 0($t0) # f <-- A[B[g]+1]2.6.2a.3b.62.6.3a.5b.42.6.4a. f = f – i;b. f = 2 * (&A);2.6.5a.$s0 = −30b.$s0 = 5122.6.6a.Chapter 2 Solutions S7 b.addi $t0, $s6, 4I-type82284add $t1, $s6, $0R-type02209sw $t1, 0($t0)I-type43890lw $t0, 0($t0)I-type35880add $s0, $t1, $t0R-type09816Solution 2.72.7.1a.613566756b.16063037442.7.2a.613566756b.16063037442.7.3a.24924924b.5FBE40002.7.4a.11111111111111111111111111111111b.100000000002.7.5a.FFFFFFFFb.4002.7.6a.1b.FFFFFC00S8 ChapterSolutions2Solution 2.82.8.1a.50000000, overflowb.0, no overflow2.8.2a.B0000000, no overflowb.2, no overflow2.8.3a.D0000000, overflowb.000000001, no overflow2.8.4a.overfl owb.overfl ow2.8.5a.overfl owb.overfl ow2.8.6a.overfl owb.overfl owSolution 2.92.9.1a.no overfl owb.overfl owChapter 2 Solutions S92.9.2a.no overfl owb.no overfl ow2.9.3a.no overfl owb.no overfl ow2.9.4a.overfl owb.overfl ow2.9.5a.94924924b.CFBE40002.9.6a.2492614948b.−809615360Solution 2.102.10.1a.add $s0, $s0, $s0b.sub $t1, $t2, $t32.10.2a.r-typeb.r-type2.10.3a.2108020b.14B4822S10 ChapterSolutions22.10.4a.0x21080001b.0xAD4900202.10.5a.i-typeb.i-type2.10.6a.op=0x8, rs=0x8, rs=0x8, imm=0x0b.op=0x2B, rs=0xA, rt=0x9, imm=0x20Solution 2.112.11.1a.0000 0001 0000 1000 0100 0000 0010 0000twob.0000 0010 0101 0011 1000 1000 0010 0010two2.11.2a.17317920b.390287702.11.3a.add $t0, $t0, $t0b.sub $s1, $s2, $s32.11.4a.r-typeb.i-type2.11.5a.sub $v1, $v1, $v0b.lw $v0, 4($at)2.11.6a.0x00621822b.0x8C220004Solution 2.122.12.12.12.2a.i-type67716total bits = 36b.i-type85516total bits = 342.12.3a.more registers → more bits per instruction → could increase code sizemore registers → less register spills → less instructionsb.more instructions → more appropriate instruction → decrease code sizemore instructions → larger opcodes → larger code size2.12.4a.17367058b.29030482102.12.5a.sub $t0, $t1, $0b.sw $t1, 12($t0)2.12.6a.r-type, op=0x0, rt=0x9b.i-type, op=0x2B, rt=0x8Solution 2.132.13.1a.0xBABEFEF8b.0x11D111D12.13.2a.0xAAAAAAA0b.0x00DD00D02.13.3a.0x00005545b.0x0000BA012.13.4a.0x00014B4Ab.0x000000012.13.5a.0x4b4a0000b.0x000000002.13.6a.0x4b4bfffeb.0x0000003CSolution 2.142.14.1a.lui $t1, 0x003fori $t1, $t0, 0xffe0and $t1, $t0, $t1srl $t1, $t1, 5b.lui $t1, 0x003fori $t1, $t0, 0xffe0and $t1, $t0, $t1sll $t1, $t1, 92.14.2a.add $t1, $t0, $0sll $t1, $t1, 28b.andi $t0, $t0, 0x000fsll $t0, $t0, 14ori $t1, $t1, 0x3fffsll $t1, $t1, 18ori $t1, $t1, 0x3fffor $t1, $t1, $t0 2.14.3a.srl $t1, $t0, 28sll $t1, $t1, 29b.srl $t0, $t0, 28andi $t0, $t0, 0x0007sll $t0, $t0, 14ori $t1, $t1, 0x7fffsll $t1, $t1, 17ori $t1, $t1, 0x3fffor $t1, $t1, $t02.14.4a.srl $t0, $t0, 11sll $t0, $t0, 26ori $t2, $0, 0x03ffsll $t2, $t2, 16ori $t2, $t2, 0xffffand $t1, $t1, $t2or $t1, $t1, $t0b.srl $t0, $t0, 11sll $t0, $t0, 26srl $t0, $t0, 12ori $t2, $0, 0xfff0sll $t2, $t2, 16ori $t2, $t2, 0x3fffand $t1, $t1, $t2or $t1, $t1, $t02.14.5a.sll $t0, $t0, 27ori $t2, $0, 0x07ffsll $t2, $t2, 16ori $t2, $t2, 0xffffand $t1, $t1, $t2or $t1, $t1, $t0b.sll $t0, $t0, 27srl $t0, $t0, 13ori $t2, $0, 0xfff8sll $t2, $t2, 16ori $t2, $t2, 0x3fffand $t1, $t1, $t2or $t1, $t1, $t02.14.6a.srl $t0, $t0, 29sll $t0, $t0, 30ori $t2, $0, 0x3fffsll $t2, $t2, 16ori $t2, $t2, 0xffffand $t1, $t1, $t2or $t1, $t1, $t0b.srl $t0, $t0, 29sll $t0, $t0, 30srl $t0, $t0, 16ori $t2, $0, 0xffffsll $t2, $t2, 16ori $t2, $t2, 0x3fffand $t1, $t1, $t2or $t1, $t1, $t0Solution 2.152.15.1a.0xff005a5ab.0x00ffffe72.15.2a.nor $t1, $t2, $t2b.nor $t1, $t3, $t3or $t1, $t2, $t12.15.3a.nor $t1, $t2, $t2000000 01010 01010 01001 00000 100111b.nor $t1, $t3, $t3or $t1, $t2, $t1000000 01011 01011 01001 00000 100111 000000 01010 01001 01001 00000 1001012.15.4a.0xFFFFFFFFb.0x000123402.15.5 Assuming $t1 = A, $t2 = B, $s1 = base of Array Ca. nor $t3, $t1, $t1or $t1, $t2, $t3b. lw $t3, 0($s1)sll $t1, $t3, 42.15.6a. nor $t3, $t1, $t1or $t1, $t2, $t3000000 01001 01001 01011 00000 100111 000000 01010 01011 01001 00000 100101b. lw $t3, 0($s1)sll $t1, $t3, 4100011 10001 01011 0000000000000000 000000 00000 01011 01001 00100 000000Solution 2.16 2.16.1a.$t2 = 1b.$t2 = 12.16.2a.noneb.none2.16.3a.Jump – No, Beq - Nob.Jump – No, Beq - No2.16.4a.$t2 = 2b.$t2 = 12.16.5a.$t2 = 0b.$t2 = 02.16.6a.jump – Yes, beq - nob.jump – no, beq - noSolution 2.172.17.1 The answer is really the same for all. All of these instructions are either supported by an existing instruction or sequence of existing instructions. Looking for an answer along the lines of, “these instructions are not common, and we are only making the common case fast.”2.17.2a.i-typeb.i-type2.17.3a.addi $t2, $t3, −5b.addi $t2, $t2, −1beq $t2, $0, loop2.17.4a.20b.202.17.5a.i = 10;do {B += 2;i = i – 1;} while ( i > 0)b.Same as part a.2.17.6a. 3 ´ Nb. 5 ´ N2.18.2a.addi $t0, $0, 0 beq $0, $0, TEST LOOP: add $s0, $s0, $s1 addi $t0, $t0, 1 TEST: slt $t2, $t0, $s0 bne $t2, $0, LOOPSolution 2.182.18.1b. addi $t0, $0, 0beq $0, $0, TEST1LOOP1:addi $t1, $0, 0beq $0, $0, TEST2LOOP2:add $t3, $t0, $t1sll $t2, $t1, 4add $t2, $t2, $s2sw $t3, ($t2)addi $t1, $t1, 1TEST2:slt $t2, $t1, $s1bne $t2, $0, LOOP2addi $t0, $t0, 1TEST1:slt $t2, $t0, $s0bne $t2, $0, LOOP12.18.3a. 6 instructions to implement and infi nite instructions executedb.14 instructions to implement and 158 instructions executed2.18.4a.351b.6012.18.5a.for(i=50; i>0; i--){result += MemArray[s0];result += MemArray[s0+1];s0 += 2;}b.for (i=0; i<100; i++) {result += MemArray[s0];s0 = s0 + 4;}2.18.6a. addi $t1, $s0, 400LOOP: lw $s1, 0($s0)add $s2, $s2, $s1lw $s1, 4($s0)add $s2, $s2, $s1addi $s0, $s0, 8bne $s0, $t1, LOOPb. addi $t1, $s0, 400LOOP: lw $s1, 0($t1)add $s2, $s2, $s1addi $t1, $t1, −4bne $t1, $s0, LOOPSolution 2.192.19.1a.fib: addi $sp, $sp, −12 # make room on stacksw $ra, 8($sp) # push $rasw $s0, 4($sp) # push $s0sw $a0, 0($sp) # push $a0 (N)bgt $a0, $0, test2 # if n>0, test if n=1 add $v0, $0, $0 # else fib(0) = 0j rtn #test2: addi $t0, $0, 1 #bne $t0, $a0, gen # if n>1, genadd $v0, $0, $t0 # else fib(1) = 1j rtngen: subi $a0, $a0,1 # n−1jal fib # call fib(n−1)add $s0, $v0, $0 # copy fib(n−1)sub $a0, $a0,1 # n−2jal fib # call fib(n−2)add $v0, $v0, $s0 # fib(n−1)+fib(n−2)rtn: lw $a0, 0($sp) # pop $a0lw $s0, 4($sp) # pop $s0lw $ra, 8($sp) # pop $raaddi $sp, $sp, 12 # restore spjr $ra# fib(0) = 12 instructions, fib(1) = 14 instructions,# fib(N) = 26 + 18N instructions for N >=2b.positive:addi $sp, $sp, −4sw $ra, 0($sp)jal additaddi $t1, $0, 1slt $t2, $0, $v0bne $t2, $0, exitaddi $t1, $0, $0exit:add $v0, $t1, $0lw $ra, 0($sp)addi $sp, $sp, 4jr $raaddit:add $v0, $a0, $a1jr $ra# 13 instructions worst-case2.19.2a.Due to the recursive nature of the code, not possible for thecompiler to in-line the function call.b.positive:add $t0, $a0, $a1addi $v0, $0, 1slt $t2, $0, $t0bne $t2, $0, exitaddi $v0, $0, $0exit:jr $ra# 6 instructions worst-case2.19.3a.after calling function fib:old $sp -> 0x7ffffffc−4 contents of register $ra for fib(N)−8 contents of register $s0 for fib(N)$sp-> −12 contents of register $a0 for fib(N)there will be N−1 copies of $ra, $s0, and $a0b.after calling function positive:old $sp -> 0x7ffffffc$sp-> −4 contents of register $raafter calling function addit:old $sp -> 0x7ffffffc−4 contents of register $ra$sp-> −8 contents of register $ra #return to positive2.19.4a.f: addi $sp,$sp,−12sw $ra,8($sp)sw $s1,4($sp)sw $s0,0($sp)move $s1,$a2move $s0,$a3jal funcmove $a0,$v0add $a1,$s0,$s1jal funclw $ra,8($sp)lw $s1,4($sp)lw $s0,0($sp)addi $sp,$sp,12jr $rab.f: addi $sp,$sp,−4sw $ra,0($sp)add $t0,$a1,$a0add $a1,$a3,$a2slt $t1,$a1,$t0beqz $t1,Lmove $a0,$t0jal funclw $ra,0($sp)addi $sp,$sp,4jr raL: move $a0,$a1move $a1,$t0jal funclw $ra,0($sp)addi $sp,$sp,4jr $ra2.19.5a.We can use the tail-call optimization for the second call to func, but then we must restore $ra,$s0, $s1, and $sp before that call. We save only one instruction (jr $ra).b.We can use the tail-call optimization for either call to func (when the condition for the if istrue or false). This eliminates the need to save $ra and move the stack pointer, so we execute5 fewer instructions (regardless of whether the if condition is true or not). The code of thefunction is 8 instructions shorter because we can eliminate both instances of the code thatrestores $ra and returns.2.19.6 Register $ra is equal to the return address in the caller function, registers $sp and $s3 have the same values they had when function f was called, and register $t5 can have an arbitrary value. For register $t5, note that although our function f does not modify it, function func is allowed to modify it so we cannot assume anything about the value of $t5 after function func has been called.Solution 2.202.20.1a.FACT: addi $sp, $sp, −8 # make room in stack for 2 more itemssw $ra, 4($sp) # save the return addresssw $a0, 0($sp) # save the argument nslti $t0, $a0, 1 # $t0 = $a0 x 2beq, $t0, $0, L1 # if $t0 = 0, goto L1add $v0, $0, 1 # return 1add $sp, $sp, 8 # pop two items from the stackjr $ra # return to the instruction after jalL1: addi $a0, $a0, −1 # subtract 1 from argumentjal FACT # call fact(n−1)lw $a0, 0($sp) # just returned from jal: restore nlw $ra, 4($sp) # restore the return addressadd $sp, $sp, 8 # pop two items from the stackmul $v0, $a0, $v0 # return n*fact(n−1)jr $ra # return to the callerb.FACT: addi $sp, $sp, −8 # make room in stack for 2 more itemssw $ra, 4($sp) # save the return addresssw $a0, 0($sp) # save the argument nslti $t0, $a0, 1 # $t0 = $a0 x 2beq, $t0, $0, L1 # if $t0 = 0, goto L1add $v0, $0, 1 # return 1add $sp, $sp, 8 # pop two items from the stackjr $ra # return to the instruction after jalL1: addi $a0, $a0, −1 # subtract 1 from argumentjal FACT # call fact(n−1)lw $a0, 0($sp) # just returned from jal: restore nlw $ra, 4($sp) # restore the return addressadd $sp, $sp, 8 # pop two items from the stackmul $v0, $a0, $v0 # return n*fact(n−1)jr $ra # return to the caller2.20.2a.25 MIPS instructions to execute non-recursive vs. 45 instructions to execute (corrected versionof) recursionNon-recursive version:FACT: addi $sp, $sp, −4sw $ra, 4($sp)add $s0, $0, $a0add $s2, $0, $1LOOP: slti $t0, $s0, 2bne $t0, $0, DONEmul $s2, $s0, $s2addi $s0, $s0, −1j LOOPDONE: add $v0, $0, $s2lw $ra, 4($sp)addi $sp, $sp, 4jr $rab.25 MIPS instructions to execute non-recursive vs. 45 instructions to execute (corrected versionof) recursionNon-recursive version:FACT: addi $sp, $sp, −4sw $ra, 4($sp)add $s0, $0, $a0add $s2, $0, $1LOOP: slti $t0, $s0, 2bne $t0, $0, DONEmul $s2, $s0, $s2addi $s0, $s0, −1j LOOPDONE: add $v0, $0, $s2lw $ra, 4($sp)addi $sp, $sp, 4jr $ra2.20.3a.Recursive versionFACT: addi $sp, $sp, −8sw $ra, 4($sp)sw $a0, 0($sp)add $s0, $0, $a0HERE: slti $t0, $a0, 2beq $t0, $0, L1addi $v0, $0, 1addi $sp, $sp, 8jr $raL1: addi $a0, $a0, −1jal FACTmul $v0, $s0, $v0lw $a0, 0($sp)lw $ra, 4($sp)addi $sp, $sp, 8jr $raat label HERE, after calling function FACT with input of 4: old $sp -> 0xnnnnnnnn−4 contents of register $ra$sp-> −8 contents of register $a0at label HERE, after calling function FACT with input of 3: old $sp -> 0xnnnnnnnn−4 contents of register $ra−8 contents of register $a0−12 contents of register $ra$sp-> −16 contents of register $a0at label HERE, after calling function FACT with input of 2: old $sp -> 0xnnnnnnnn−4 contents of register $ra−8 contents of register $a0−12 contents of register $ra−16 contents of register $a0−20 contents of register $ra$sp-> −24 contents of register $a0at label HERE, after calling function FACT with input of 1: old $sp -> 0xnnnnnnnn−4 contents of register $ra−8 contents of register $a0−12 contents of register $ra−16 contents of register $a0−20 contents of register $ra−24 contents of register $a0−28 contents of register $ra$sp-> −32 contents of register $a0b.Recursive versionFACT: addi $sp, $sp, −8sw $ra, 4($sp)sw $a0, 0($sp)add $s0, $0, $a0HERE: slti $t0, $a0, 2beq $t0, $0, L1addi $v0, $0, 1addi $sp, $sp, 8jr $raL1: addi $a0, $a0, −1jal FACTmul $v0, $s0, $v0lw $a0, 0($sp)lw $ra, 4($sp)addi $sp, $sp, 8jr $raat label HERE, after calling function FACT with input of 4: old $sp -> 0xnnnnnnnn−4 contents of register $ra$sp-> −8 contents of register $a0at label HERE, after calling function FACT with input of 3: old $sp -> 0xnnnnnnnn−4 contents of register $ra−8 contents of register $a0−12 contents of register $ra$sp-> −16 contents of register $a0at label HERE, after calling function FACT with input of 2: old $sp -> 0xnnnnnnnn−4 contents of register $ra−8 contents of register $a0−12 contents of register $ra−16 contents of register $a0−20 contents of register $ra$sp-> −24 contents of register $a0at label HERE, after calling function FACT with input of 1: old $sp -> 0xnnnnnnnn−4 contents of register $ra−8 contents of register $a0−12 contents of register $ra−16 contents of register $a0−20 contents of register $ra−24 contents of register $a0−28 contents of register $ra$sp-> −32 contents of register $a02.20.4a.FIB: addi $sp, $sp, −12sw $ra, 8($sp)sw $s1, 4($sp)sw $a0, 0($sp)slti $t0, $a0, 3beq $t0, $0, L1addi $v0, $0, 1j EXITL1: addi $a0, $a0, −1jal FIBaddi $s1, $v0, $0addi $a0, $a0, −1jal FIBadd $v0, $v0, $s1EXIT: lw $a0, 0($sp)lw $s1, 4($sp)lw $ra, 8($sp)addi $sp, $sp, 12jr $rab.FIB: addi $sp, $sp, −12sw $ra, 8($sp)sw $s1, 4($sp)sw $a0, 0($sp)slti $t0, $a0, 3beq $t0, $0, L1addi $v0, $0, 1j EXITL1: addi $a0, $a0, −1jal FIBaddi $s1, $v0, $0addi $a0, $a0, −1jal FIBadd $v0, $v0, $s1EXIT: lw $a0, 0($sp)lw $s1, 4($sp)lw $ra, 8($sp)addi $sp, $sp, 12jr $ra2.20.5a.23 MIPS instructions to execute non-recursive vs. 73 instructions to execute (corrected versionof) recursionNon-recursive version:FIB: addi $sp, $sp, −4sw $ra, ($sp)addi $s1, $0, 1addi $s2, $0, 1LOOP: slti $t0, $a0, 3bne $t0, $0, EXITadd $s3, $s1, $0add $s1, $s1, $s2add $s2, $s3, $0addi $a0, $a0, −1j LOOPEXIT: add $v0, s1, $0lw $ra, ($sp)addi $sp, $sp, 4jr $rab.23 MIPS instructions to execute non-recursive vs. 73 instructions to execute (corrected versionof) recursionNon-recursive version:FIB: addi $sp, $sp, −4sw $ra, ($sp)addi $s1, $0, 1addi $s2, $0, 1LOOP: slti $t0, $a0, 3bne $t0, $0, EXITadd $s3, $s1, $0add $s1, $s1, $s2add $s2, $s3, $0addi $a0, $a0, −1j LOOPEXIT: add $v0, s1, $0lw $ra, ($sp)addi $sp, $sp, 4jr $ra2.20.6a.Recursive versionFIB: addi $sp, $sp, −12sw $ra, 8($sp)sw $s1, 4($sp)sw $a0, 0($sp)HERE: slti $t0, $a0, 3beq $t0, $0, L1addi $v0, $0, 1j EXITL1: addi $a0, $a0, −1jal FIBaddi $s1, $v0, $0addi $a0, $a0, −1jal FIBadd $v0, $v0, $s1EXIT: lw $a0, 0($sp)lw $s1, 4($sp)lw $ra, 8($sp)addi $sp, $sp, 12jr $raat label HERE, after calling function FIB with input of 4: old $sp -> 0xnnnnnnnn−4 contents of register $ra−8 contents of register $s1$sp-> −12 contents of register $a0 b.Recursive versionFIB: addi $sp, $sp, −12sw $ra, 8($sp)sw $s1, 4($sp)sw $a0, 0($sp)HERE: slti $t0, $a0, 3beq $t0, $0, L1addi $v0, $0, 1j EXITL1: addi $a0, $a0, −1jal FIBaddi $s1, $v0, $0addi $a0, $a0, −1jal FIBadd $v0, $v0, $s1EXIT: lw $a0, 0($sp)lw $s1, 4($sp)lw $ra, 8($sp)addi $sp, $sp, 12jr $raat label HERE, after calling function FIB with input of 4: old $sp -> 0xnnnnnnnn−4 contents of register $ra−8 contents of register $s1$sp-> −12 contents of register $a0Solution 2.212.21.1a.MAIN: addi $sp, $sp, −4sw $ra, ($sp)addi $a0, $0, 10addi $a1, $0, 20jal FUNCadd $t2, $v0 $0lw $ra, ($sp)addi $sp, $sp, 4jr $raFUNC: lw $t1, ($s0) #assume $s0 has global variable basesub $t0, $v0, $v1addi $v0, $t0, $t1jr $rab.MAIN: addi $sp, $sp, −4sw $ra, ($sp)lw $t1, ($s0) #assume $s0 has global variable baseaddi $a0, $t1, 1jal LEAFadd $t2, $v0 $0lw $ra, ($sp)addi $sp, $sp, 4jr $raLEAF: addi $v0, $a0, 1jr $ra2.21.2a.after entering function main:old $sp -> 0x7ffffffc$sp-> −4 contents of register $raafter entering function my_function:old $sp -> 0x7ffffffc−4 contents of register $ra$sp-> −8 c ontents of register $ra (return to main) global pointers:0x10008000 100 my_globalb.after entering function main:old $sp -> 0x7ffffffc$sp-> −4 contents of register $raglobal pointers:0x10008000 100 my_globalafter entering function leaf_function:old $sp -> 0x7ffffffc−4 contents of register $ra$sp-> −8 c ontents of register $ra (return to main) global pointers:0x10008000 101 my_global2.21.3a.MAIN: addi $sp, $sp, −4sw $ra, ($sp)addi $a0, $0, 10addi $a1, $0, 20jal FUNCadd $t2, $v0 $0lw $ra, ($sp)addi $sp, $sp, 4jr $raFUNC: lw $t1, ($s0) #assume $s0 has global variable basesub $t0, $v0, $v1addi $v0, $t0, $t1jr $rab.MAIN: addi $sp, $sp, −4sw $ra, ($sp)lw $t1, ($s0) #assume $s0 has global variable baseaddi $a0, $t1, 1jal LEAFadd $t2, $v0 $0lw $ra, ($sp)addi $sp, $sp, 4jr $raLEAF: addi $v0, $a0, 1jr $ra2.21.4a.The return address of the function is in $ra, so the last instruction should be “jr $ra.”b.The tail call to g must use jr, not jal. If jal is used, it overwrites the return address so function greturns back to f, not to the original caller of f as intended.2.21.5a.int f(int a, int b, int c){if(c)return (a+b);return (a−b);}b.int f(int a, int b, int c, int d){if(a>c+d)return b;return g(b);}2.21.6a.The function returns 101 (1000 is nonzero, so it returns 1+100).b.The function returns 500 (c+d is 1030, which is larger than 1, so the function returns g(b),which according to the problem statement is 500).Solution 2.222.22.1a.68 65 6C 6C 6F 20 77 6F 72 6C 64b.48 49 50 51 52 53 54 55 56 572.22.2a.U+0038, U+0020, U+0062, U+0069, U+0074, U+0073b.U+0030, U+0031, U+0032, U+0033, U+0034, U+0035, U+0036, U+0037,U+0038, U+00392.22.3a.ADDb.MIPSSolution 2.232.23.1a.MAIN: addi $sp, $sp, −4sw $ra, ($sp)add $t6, $0, 0x30 # ‘0’add $t7, $0, 0x39 # ‘9’add $s0, $0, $0add $t0, $a0, $0LOOP: lb $t1, ($t0)slt $t2, $t1, $t6bne $t2, $0, DONEslt $t2, $t7, $t1bne $t2, $0, DONEsub $t1, $t1, $t6beq $s0, $0, FIRSTmul $s0, $s0, 10FIRST: add $s0, $s0, $t1addi $t0, $t0, 1j LOOPDONE: add $v0, $s0, $0lw $ra, ($sp)addi $sp, $sp, 4jr $rab.MAIN: addi $sp, $sp, −4sw $ra, ($sp)add $t4, $0, 0x41 # ‘A’add $t5, $0, 0x46 # ‘F’add $t6, $0, 0x30 # ‘0’add $t7, $0, 0x39 # ‘9’add $s0, $0, $0add $t0, $a0, $0LOOP: lb $t1, ($t0)slt $t2, $t1, $t6bne $t2, $0, DONEslt $t2, $t7, $t1bne $t2, $0, HEXsub $t1, $t1, $t6j DECHEX: slt $t2, $t1, $t4bne $t2, $0, DONEslt $t2, $t5, $t1bne $t2, $0, DONEsub $t1, $t1, $t4addi $t1, $t1, 10DEC: beq $s0, $0, FIRSTmul $s0, $s0, 10FIRST: add $s0, $s0, $t1addi $t0, $t0, 1j LOOPDONE: add $v0, $s0, $0lw $ra, ($sp)addi $sp, $sp, 4jr $raSolution 2.242.24.1a.0x00000012b.0x0012ffff2.24.2a.0x00000080b.0x008000002.24.3a.0x00000011b.0x00115555Solution 2.252.25.1 Generally, all solutions are similar:lui $t1, top_16_bitsori $t1, $t1, bottom_16_bits2.25.2 Jump can go up to 0x0FFFFFFC.a.nob.yes2.25.3 Range is 0x604 + 0x1FFFC = 0x0002 0600 to 0x604 – 0x20000 = 0xFFFE 0604.a.nob.no2.25.4 Range is 0x1FFFF004 + 0x1FFFC = 0x2001F000 to 0x1FFFF004 – 0x20000 = 1FFDF004a.yesb.no2.25.5 Generally, all solutions are similar:add $t1, $0, $0 #clear $t1addi $t2, $0, top_8_bits #set top 8bsll $t2, $t2, 24 #shift left 24 spotsor $t1, $t1, $t2 #place top 8b into $t1 addi $t2, $0, nxt1_8_bits #set next 8bsll $t2, $t2, 16 #shift left 16 spotsor $t1, $t1, $t2 #place next 8b into $t1 addi $t2, $0, nxt2_8_bits #set next 8bsll $t2, $t2, 24 #shift left 8 spotsor $t1, $t1, $t2 #place next 8b into $t1 ori $t1, $t1, bot_8_bits #or in bottom 8b2.25.6a.0x12345678b.0x000000002.25.7a.t0 = (0x1234 << 16) + 0x5678;b.t0 = (0x1234 << 16) && 0x5678;Solution 2.262.26.1 Branch range is 0x00020000 to 0xFFFE0004.a.one branchb.one branch2.26.2a.oneb.can’t be done2.26.3 Branch range is 0x00000200 to 0xFFFFFE04.a.256 branchesb.one branch2.26.4a.branch range is 16× smallerb.branch range is 4× smaller2.26.5a.no changeb.jump to addresses 0 to 226 instead of 0 to 228, assuming the PC<0x080000002.26.6a.rs fi eld now 7 bitsb.no changeSolution 2.272.27.1a.MIPS lw/sw instructions: lw $t0, 8($t1)b.jump2.27.2a.i-typeb.j-type2.27.3a.+ allows memory from (base +/– 215) addresses to be loaded without changing the base– max size of 64 kB memory array without having to use multiple base addressesb.+ large jump range– jump range not as large as jump-register– can only access 1/16th of the total addressable space2.27.4a.0x00400000 beq $s0, $0, FAR...0x00403100 FAR: addi $s0, $s0, 10x12000c3c 0x22100001b.0x00000100 j AWAY...0x04000010 AWAY: addi $s0, $s0, 10x09000004 0x221000012.27.5a. addi $t0, $0, 0x31sll $t0, $t0, 8beq $s0, $0, TEMP...TEMP: jr $t0b. addi $s0, $0, 0x4sll $s0, $s0, 24ori $s0, $s0, 0x10jr $s0...addi $s0, $s0, 12.27.6a.2b.3Solution 2.282.28.1a. 3 instructions2.28.2a.The location specifi ed by the LL instruction is different than the SC instruction; hence, the operation of the store conditional is undefi ned.2.28.3a.try: MOV R3,R4LL R2,0(R1)ADDI R2, R2, 1SC R3,0(R1)BEQZ R3,tryMOV R4,R2。

计算机系统结构 第二章(习题解答)

1. 数据类型、数据表示和数据结构之间是什么关系?在设计一个计算机系统时,确定数据表示的原则主要有哪几个? 答:略2. 假设有A 和B 两种不同类型的处理机,A 处理机中的数据不带标志位,其指令字长和数据字长均为32位。

B 处理机的数据带有标志位,每个数据的字长增加至36位,其中有4位是标志符,它的指令条数由最多256条减少至不到64条。

如果每执行一条指令平均要访问两个操作数,每个存放在存储器中的操作数平均要被访问8次。

对于一个由1000条指令组成的程序,分别计算这个程序在A 处理机和B 处理机中所占用的存储空间大小(包括指令和数据),从中得到什么启发? 答:我们可以计算出数据的总数量:∵ 程序有1000条指令组成,且每条指令平均要访问两个操作数 ∴ 程序访问的数据总数为:1000×2=2000个 ∵ 每个数据平均访问8次∴ 程序访问的不同数据个数为:2000÷8=250对于A 处理机,所用的存储空间的大小为:bit 4000032250321000Mem Mem Mem data n instructio A =⨯+⨯=+=对于B 处理机,指令字长由32位变为了30位(条数由256减少到64),这样,所用的存储空间的大小为:bit 3900036250301000Mem Mem Mem data n instructio B =⨯+⨯=+=由此我们可以看出,由于数据的平均访问次数要大于指令,所以,采用带标志符的数据表示不会增加总的存储空间大小。

3. 对于一个字长为64位的存储器,访问这个存储器的地址按字节编址。

假设存放在这个存储器中的数据中有20%是独立的字节数据(指与这个字节数据相邻的不是一个字节数据),有30%是独立的16位数据,有20%是独立的32位数据,另外30%是独立的64位数据;并且规定只能从一个存储字的起始位置开始存放数据。

⑴计算这种存储器的存储空间利用率。

⑵给出提高存储空间利用率的方法,画出新方法的逻辑框图,并计算这种方法的存储空间利用率。

计算机组成原理课后答案

计算机组成原理课后答案1. 什么是计算机组成原理?计算机组成原理是研究计算机硬件的基本组成和工作原理的学科,主要包括处理器、内存、输入输出设备等方面的内容。

它研究计算机硬件的组成结构和各部件之间的组织、连接和控制方式,以及计算机如何运行和进行数据处理的原理和方法。

2. 计算机的五大基本部件是什么?计算机的五大基本部件是:•中央处理器(CPU):负责执行计算机指令,控制和协调计算机的各部件工作。

•主存储器(Memory):用于存储计算机处理数据和指令时所需要的数据。

•输入设备:用户通过输入设备向计算机输入数据和指令。

•输出设备:计算机将处理结果输出给用户。

•外部存储器:用于长期存储数据和程序的设备,例如硬盘和光盘等。

3. 简述冯·诺依曼体系结构的特点。

冯·诺依曼体系结构是计算机组成原理中最重要的概念之一,其特点包括:•存储程序:指令和数据以二进制形式存储在同一存储器中,计算机可以根据指令的地址自动取指令执行。

•以运算器和控制器为核心:运算器负责执行算术和逻辑运算,控制器负责控制计算机的运行和各部件的协调工作。

•输入输出分离:计算机的输入设备和输出设备与运算器和控制器分离,通过输入输出设备和外存进行数据交互。

•指令执行顺序:指令按照程序设计者指定的顺序执行,依次从存储器中取出指令并执行。

4. 什么是指令集架构?指令集架构是计算机体系结构的一种分类方式,它定义了计算机硬件与软件之间的接口和指令集的编码规则。

指令集架构决定了计算机的指令集和寻址方式,是软硬件协同工作的重要基础。

常见的指令集架构有精简指令集(RISC)和复杂指令集(CISC)两种。

精简指令集架构主张指令集简单、指令执行速度快,执行周期短,例如ARM架构;而复杂指令集架构主张指令集功能丰富、指令执行效率高,例如x86架构。

5. 计算机中的字长是什么意思?计算机中的字长是指计算机中最基本的数据单位的长度,决定了计算机的数据处理能力和寻址能力。

计算机组成原理第二章参考答案

计算机组成原理第二章参考答案计算机组成原理第二章主要介绍了计算机的层次结构和性能指标。

以下是第二章的参考答案,详细介绍了计算机层次结构的各个层次和性能指标。

第二章:计算机的层次结构和性能指标1. 什么是计算机的层次结构?计算机的层次结构是指计算机系统中各个层次之间的相互关系和功能划分。

计算机的层次结构从上到下分为五个层次:应用层、操作系统层、汇编和机器语言层、微程序层和硬件层。

2. 请介绍计算机的五个层次结构。

- 应用层:计算机的最顶层,负责处理用户的应用程序和数据。

- 操作系统层:负责管理计算机系统的资源和控制计算机的运行。

- 汇编和机器语言层:负责将高级语言转化为机器语言,供计算机硬件执行。

- 微程序层:负责实现计算机指令的具体执行过程。

- 硬件层:计算机的最底层,包括处理器、内存、输入输出设备等硬件组件。

3. 什么是计算机的性能指标?计算机的性能指标是指衡量计算机性能优劣的指标,主要包括速度、存储容量、可靠性和成本四个方面。

4. 请介绍计算机的速度性能指标。

- 响应时间:指从用户发出请求到计算机给出响应的时间。

- 时钟周期:指计算机内部处理器的时钟周期时间。

- 主频:指处理器的时钟频率,单位为赫兹。

- MIPS:指每秒执行百万条指令数,是衡量计算机运算速度的指标。

5. 请介绍计算机的存储容量性能指标。

- 主存容量:指计算机中用于存储程序和数据的主存容量。

- 硬盘容量:指计算机中用于存储大容量数据的硬盘容量。

- 缓存容量:指计算机中用于提高数据访问速度的高速缓存容量。

6. 请介绍计算机的可靠性性能指标。

- 故障率:指计算机发生故障的概率。

- 可用性:指计算机正常工作的时间占总时间的比例。

- 容错能力:指计算机在部分组件故障时仍然可以正常工作的能力。

7. 请介绍计算机的成本性能指标。

- 硬件成本:指计算机硬件的购买和维护成本。

- 能耗成本:指计算机在运行过程中消耗的能源成本。

- 人工成本:指计算机的使用和维护所需的人力成本。

计算机组成原理第二章课后习题答案

第二章运算方法和运算器练习一、填空题1. 补码加减法中,(符号位)作为数的一部分参加运算,(符号位产生的进位)要丢掉。

2. 为判断溢出,可采用双符号位补码,此时正数的符号用(00)表示,负数的符号用(11)表示。

3. 采用双符号位的方法进行溢出检测时,若运算结果中两个符号位(不相同),则表明发生了溢出。

若结果的符号位为(01),表示发生正溢出;若为(10),表示发生负溢出。

4. 采用单符号位进行溢出检测时,若加数与被加数符号相同,而运算结果的符号与操作数的符号(不一致),则表示溢出;当加数与被加数符号不同时,相加运算的结果(不会产生溢出)。

5. 利用数据的数值位最高位进位C和符号位进位Cf的状况来判断溢出,则其表达式为over=(C⊕Cf)。

6. 在减法运算中,正数减(负数)可能产生溢出,此时的溢出为(正)溢出;负数减(正数)可能产生溢出,此时的溢出为(负)溢出。

7. 补码一位乘法运算法则通过判断乘数最末位Yi和Yi-1的值决定下步操作,当YiYi-1=(10)时,执行部分积加【-x】补,再右移一位;当YiYi-1=(01)时,执行部分积加【x】补,再右移一位。

8. 浮点加减运算在(阶码运算溢出)情况下会发生溢出。

9. 原码一位乘法中,符号位与数值位(分开运算),运算结果的符号位等于(两操作数符号的异或值)。

10. 一个浮点数,当其补码尾数右移一位时,为使其值不变,阶码应该(加1)。

11. 左规的规则为:尾数(左移一位),阶码(减1)。

12. 右规的规则是:尾数(右移一位),阶码(加1)。

13. 影响进位加法器速度的关键因素是(进位信号的传递问题)。

14. 当运算结果的补码尾数部分不是(11.0×××××或00.1×××××)的形式时,则应进行规格化处理。

当尾数符号位为(01)或(10)时,需要右规。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

电平触发是在高电平或是低电平的时候触发, 电平触发是在高电平或是低电平的时候触发, 边沿触发仅仅在上升沿下降沿触发。 边沿触发仅仅在上升沿下降沿触发。抗干扰能 力强多了。 力强多了。

2.14 PLD器件和 器件和FPGA器件在内部组成和使用方法等方面 器件和 器件在内部组成和使用方法等方面 有什么区别? 有什么区别?

布尔代数又称为“二值代数”和“开关代数”,与电路 中的“通”,“断”两种状态对应,是适合数字逻辑设 计的一种代数。 为了与“数字系统逻辑设计”相适应,我们习惯于又称 之为“逻辑代数” 逻辑代数有“五个公理”,“三个基本运算”,“八个 定理”,“三个规则”。运用这些,可以根据需要选择 各种“门电路”来实现特定逻辑功能,可以得到最简的 逻辑电路,降低设计成本,可以可以设计出任何复杂功能的组 只用与, 只用与 合逻辑,时序逻辑电路吗? 合逻辑,时序逻辑电路吗?

答:是的,因为用这三种基本的逻辑门电路可以 实现任何的组合逻辑电路,而时序逻辑电路的基 本触发器也都可以用这三种基本的逻辑门电路实 现

2.11 电平触发的触发器和边沿触发的触发器有什么异同? 电平触发的触发器和边沿触发的触发器有什么异同?

第二章习题

2.1 数字逻辑电路和半导体材料的关系

我们将半导体用于数字逻辑电路中,是因为半导 体的一个什么样的导电特性? 答:半导体器件的单向导电性。 我们在数字逻辑中常用的半导体器件有哪些? 答:二极管,三极管,MOS管等

2.3简单说明布尔代数在数字电路中的 简单说明布尔代数在数字电路中的 作用。 作用。

PLD是采用与,或两级逻辑陈列加上输出逻辑单 元的内部结构,而FPGA的内部结构则是采用许 多个独立的可编程的逻辑模块,输入输出模块和 互连资源3部分组成的