计算机组成与设计第五版答案

计算机组成原理第五版 白中英(详细)第4章习题参考答案

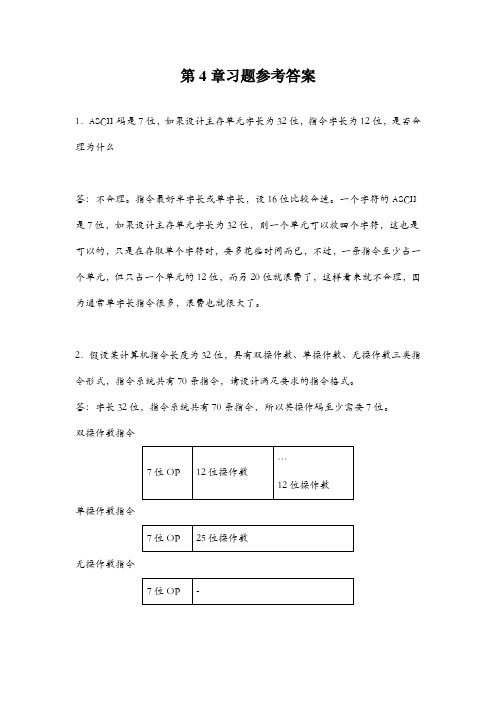

第4章习题参考答案1.ASCII码是7位,如果设计主存单元字长为32位,指令字长为12位,是否合理?为什么?答:不合理。

指令最好半字长或单字长,设16位比较合适。

一个字符的ASCII 是7位,如果设计主存单元字长为32位,则一个单元可以放四个字符,这也是可以的,只是在存取单个字符时,要多花些时间而已,不过,一条指令至少占一个单元,但只占一个单元的12位,而另20位就浪费了,这样看来就不合理,因为通常单字长指令很多,浪费也就很大了。

2.假设某计算机指令长度为32位,具有双操作数、单操作数、无操作数三类指令形式,指令系统共有70条指令,请设计满足要求的指令格式。

答:字长32位,指令系统共有70条指令,所以其操作码至少需要7位。

双操作数指令单操作数指令无操作数指令3.指令格式结构如下所示,试分析指令格式及寻址方式特点。

答:该指令格式及寻址方式特点如下:(1) 单字长二地址指令。

(2) 操作码字段OP可以指定26=64种操作。

(3) 源和目标都是通用寄存器(可分指向16个寄存器)所以是RR型指令,即两个操作数均在寄存器中。

(4) 这种指令结构常用于RR之间的数据传送及算术逻辑运算类指令。

4.指令格式结构如下所示,试分析指令格式及寻址方式特点。

15 10 9 8 7 4 3 0答:该指令格式及寻址方式特点如下:(1)双字长二地址指令,用于访问存储器。

(2)操作码字段OP可以指定26=64种操作。

(3)RS型指令,一个操作数在通用寄存器(选择16个之一),另一个操作数在主存中。

有效地址可通过变址寻址求得,即有效地址等于变址寄存器(选择16个之一)内容加上位移量。

5.指令格式结构如下所示,试分析指令格式及寻址方式特点。

答:该指令格式及寻址方式特点如下:(1)该指令为单字长双操作数指令,源操作数和目的操作数均由寻址方式和寄存器构成,寄存器均有8个,寻址方式均有8种。

根据寻址方式的不同,指令可以是RR型、RS型、也可以是SS型;(2)因为OP为4位,所以最多可以有16种操作。

计算机组装与维护第五版课后习题参考答案(工业)

计算机组装与维护第五版课后习题参考答案(工业)第一章:计算机基础知识1. 什么是计算机硬件?计算机硬件又可以分为哪几类?计算机硬件是指构成计算机实体的各个部件,包括处理器、内存、硬盘、显示器、键盘等。

计算机硬件可以分为以下几类:1.中央处理器(CPU):负责处理计算机的指令和数据。

2.主存储器(内存):用于存储程序和数据。

3.输入设备:用于将外部信息输入到计算机中,如键盘、鼠标等。

4.输出设备:用于将计算机处理的结果输出,如显示器、打印机等。

5.辅助存储设备:用于长期保存数据和程序,如硬盘、光盘等。

6.扩展设备:如网络设备、声卡、显卡等。

2. 什么是计算机软件?计算机软件又可以分为哪几类?计算机软件是指计算机系统中的各种程序和数据,可以分为以下几类:1.系统软件:包括操作系统、编译器、数据库管理系统等,用于管理和控制计算机硬件资源。

2.应用软件:包括办公软件、图形图像处理软件、娱乐软件等,用于满足用户的各种需求。

3.开发工具软件:包括编程语言、集成开发环境等,用于开发其他软件。

3. 简述计算机系统的五大组成部分。

计算机系统的五大组成部分分别是:输入设备、输出设备、存储设备、中央处理器(CPU)和控制器/调度器。

•输入设备用于将外部信息输入到计算机中,如键盘、鼠标等。

•输出设备用于将计算机处理的结果输出,如显示器、打印机等。

•存储设备用于长期保存数据和程序,如硬盘、光盘等。

•中央处理器(CPU)负责处理计算机的指令和数据。

•控制器/调度器用于控制计算机系统的各个部件的协调工作。

4. 什么是计算机的位数?计算机位数的提升对计算机性能有什么影响?计算机的位数是指计算机中用于表示数据的二进制位的位数。

常见的计算机位数有8位、16位、32位和64位等。

计算机位数的提升对计算机性能有以下几个方面的影响:1.内存容量:位数的提升可以扩大计算机内存的寻址范围,使计算机能够处理更大容量的数据。

2.计算速度:位数的提升可以增加计算机的计算能力,提高运算速度。

白中英《计算机组成原理》(第5版)笔记和课后习题详解复习答案

白中英《计算机组成原理》(第5版)笔记和课后习题详解完整版>精研学习网>无偿试用20%资料

全国547所院校视频及题库全收集

考研全套>视频资料>课后答案>往年真题>职称考试

第1章计算机系统概论

1.1复习笔记

1.2课后习题详解

第2章运算方法和运算器

2.1复习笔记

2.2课后习题详解

第3章多层次的存储器

3.1复习笔记

3.2课后习题详解

第4章指令系统

4.1复习笔记

4.2课后习题详解

第5章中央处理器

5.1复习笔记

5.2课后习题详解

第6章总线系统

6.1复习笔记

6.2课后习题详解

第7章外存与I/O设备

7.1复习笔记

7.2课后习题详解

第8章输入输出系统

8.1复习笔记

8.2课后习题详解

第9章并行组织与结构

9.1复习笔记

9.2课后习题详解

第10章课程教学实验设计

第11章课程综合设计。

计算机组成原理课后答案(白中英主编_第五版_立体化教材)_2

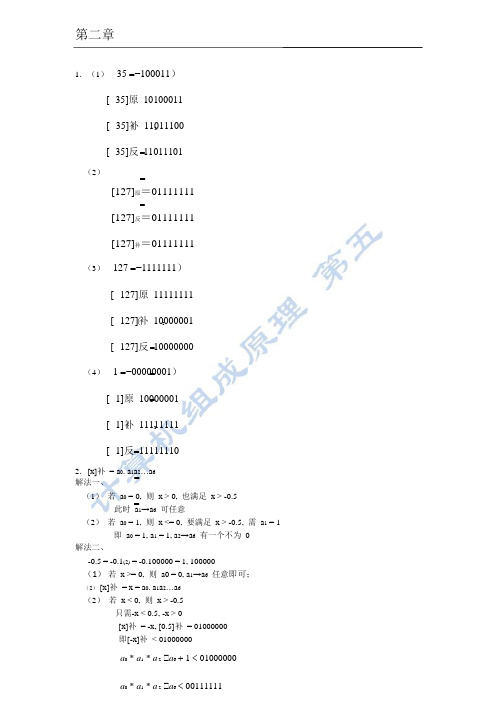

( 2= ==( 2= = =( 2===第二章1.(1) 35 =−100011)[ 35]原 10100011[ 35]补 11011100 [ 35]反 11011101(2)[127]原=01111111[127]反=01111111[127]补=01111111(3) 127 =−1111111)[ 127]原 11111111[ 127]补 10000001[ 127]反 10000000(4) 1 =−00000001)[ 1]原 10000001[ 1]补 11111111 [ 1]反 111111102.[x]补 = a 0. a 1a 2…a 6解法一、(1) 若 a 0 = 0, 则 x > 0, 也满足 x > -0.5此时 a 1→a 6 可任意(2) 若 a 0 = 1, 则 x <= 0, 要满足 x > -0.5, 需 a 1 = 1 即 a 0 = 1, a 1 = 1, a 2→a 6 有一个不为 0解法二、-0.5 = -0.1(2) = -0.100000 = 1, 100000(1) 若 x >= 0, 则 a0 = 0, a 1→a 6 任意即可;(2) [x]补= x = a 0. a 1a 2…a 6(2) 若 x < 0, 则 x > -0.5只需-x < 0.5, -x > 0[x]补 = -x, [0.5]补 = 01000000 即[-x]补 < 01000000a 0 * a 1 * a 2 a 6 + 1 < 01000000⋅ (1 2 ) 即: 2 2 ⋅ 2(最接近 0 的负数)即: 2 2 ⋅ (2 + 2[ 2 2 ⋅ 2 ⋅ (1 2 ) ] [ 22 1 ⋅ ( 1) , 2 2 ⋅ (2 1 + 2 ) ]a 0 a 1a 2 a 6 > 11000000即 a 0a 1 = 11, a 2→a 6 不全为 0 或至少有一个为 1(但不是“其余取 0”)3.字长 32 位浮点数,阶码 8 位,用移码表示,尾数 23 位,用补码表示,基为 2EsE 1→E 8MsM 21M 0(1) 最大的数的二进制表示E = 11111111Ms = 0, M = 11…1(全 1)1 11111111 01111111111111111111111(2) 最小的二进制数E = 11111111Ms = 1, M = 00…0(全 0) 1 11111111 1000000000000000000000(3) 规格化范围正最大E = 11…1, M = 11…1, Ms = 08 个22 个即: 227 122正最小E = 00…0, M = 100…0, Ms = 08 个7121 个负最大E = 00…0, M = 011…1, Ms = 18 个 21 个负最小7 1E = 11…1, M = 00…0, Ms =18 个22 个22 )即: 22⋅ ( 1) 规格化所表示的范围用集合表示为:71, 227122 7 7 2244.在 IEEE754 标准中,一个规格化的 32 位浮点数 x 的真值表示为:X=( 1)s ×(1.M )× 2 E 127(1)27/64=0.011011=1.1011× 22E= -2+127 = 125= 0111 1101 S= 0M= 1011 0000 0000 0000 0000 000最后表示为:0 01111101 10110000000000000000000 (2)-27/64=-0.011011=1.1011× 22E= -2+127 = 125= 0111 1101 S= 1M= 1011 0000 0000 0000 0000 000最后表示为:1 01111101 10110000000000000000000 5.(1)用变形补码进行计算:[x]补=00 11011 [y]补=00 00011[x]补 = [y]补 = [x+y]补00 11011 + 00 00011 00 11110结果没有溢出,x+y=11110(2) [x]补=00 11011 [y]补=11 01011[x]补 = [y]补 = [x+y]补=00 11011 + 11 01011 00 00110结果没有溢出,x+y=00110(3)[x]补=11 01010 [y]补=11 111111[x]补 = [y]补 = [x+y]补=00 01010 + 00 11111 11 01001结果没有溢出,x+y=−101116.[x-y]补=[x]补+[-y]补 (1)[x]补=00 11011[-y]补=00 11111[x]补 =00 11011 [-y]补 = + 00 11111 [x-y]补= 01 11010结果有正溢出,x−y=11010(2)[x]补=00 10111[-y]补=11 00101[x]补 =00 10111 [-y]补 = + 11 00101 [x-y]补结果没有溢出,x−y=−00100(3)[x]补=00 11011 [-y]补=00 10011[x]补= 00 11011[-y]补= + 00 10011[x-y]补= 01 01110结果有正溢出,x−y=100107.(1)用原码阵列乘法器:[x]原=0 11011 [y]原=1 11111因符号位单独考虑,|x|=11011 |y|=111111 1 0 1 1×) 1 1 1 1 1——————————————————————————1 1 0 1 11 1 0 1 11 1 0 1 11 1 0 1 11 1 0 1 11 1 0 1 0 0 0 1 0 1[x×y]原=1 1101000101用补码阵列乘法器:[x]补=0 11011 [y]补=1 00001乘积符号位为:1|x|=11011 |y|=111111 1 0 1 1×) 1 1 1 1 1——————————————————————————1 1 0 1 11 1 0 1 11 1 0 1 11 1 0 1 11 1 0 1 0 0 0 1 0 1[x×y]补=1 0010111011(2) 用原码阵列乘法器:[x]原=1 11111 [y]原=1 11011因符号位单独考虑,|x|=11111 |y|=110111 1 1 1 1×) 1 1 0 1 1——————————————————————————1 1 1 1 11 1 1 1 10 0 0 0 01 1 1 1 11 1 1 1 11 1 0 1 0 0 0 1 0 1[x×y]原=0 1101000101用补码阵列乘法器:[x]补=1 00001 [y]补=1 00101乘积符号位为:1|x|=11111 |y|=110111 1 1 1 1×) 1 1 0 1 1——————————————————————————1 1 1 1 11 1 1 1 10 0 0 0 01 1 1 1 111111[x×y]补=0 11010001018.(1) [x]原=[x]补=0 11000[-∣y ∣]补=1 00001被除数 X 0 11000 +[-|y|]补 1 00001----------------------------------------------------余数为负 1 11001 →q0=0左移 1 10010 +[|y|]补0 11111----------------------------------------------------余数为正 0 10001 →q1=1左移 1 00010 +[-|y|]补1 00001----------------------------------------------------余数为正 0 00011 →q2=1左移 0 00110 +[-|y|]补1 00001----------------------------------------------------余数为负 1 00111 →q3=0左移 0 01110 +[|y|]补0 11111----------------------------------------------------余数为负 1 01101 →q4=0左移 0 11010 +[|y|]补0 11111----------------------------------------------------余数为负 1 11001 →q5=0+[|y|]补0 11111 ----------------------------------------------------余数 0 11000故 [x÷y]原=1.11000 即 x÷y= −0.11000 余数为 0 11000(2)[∣x ∣]补=0 01011[-∣y ∣]补=1 00111被除数 X 0 01011 +[-|y|]补 1 00111----------------------------------------------------余数为负 1 10010 →q0=0x+y= 1.010010*2 = 2 *-0.101110左移 1 00100 +[|y|]补 0 11001----------------------------------------------------余数为负 1 11101 →q1=0左移 1 11010 +[|y|]补0 11001----------------------------------------------------余数为正 0 10011 →q2=1左移 1 00110 +[-|y|]补1 00111----------------------------------------------------余数为正 0 01101 →q3=1左移 0 11010 +[-|y|]补1 00111----------------------------------------------------余数为正 0 00001 →q4=1左移 0 00010 +[-|y|]补1 00111----------------------------------------------------余数为负 1 01001 →q5=0 +[|y|]补0 11001----------------------------------------------------余数 0 00010x÷y= −0.01110余数为 0 000109.(1) x = 2-011*0.100101, y = 2-010*(-0.011110)[x]浮 = 11101,0.100101 [y]浮 = 11110,-0.011110 Ex-Ey = 11101+00010=11111 [x]浮 = 11110,0.010010(1)x+y 0 0. 0 1 0 0 1 0 (1)+ 1 1. 1 0 0 0 1 01 1. 1 1 0 1 0 0 (1)规格化处理: 1.010010 阶码11100-4 -4x-y0 0. 0 1 0 0 1 0 (1) + 0 0. 0 1 1 1 1 00 0 1 1 0 0 0 0 (1) 规格化处理:0.110000阶码11110x-y=2-2*0.110001(2) x = 2-101*(-0.010110), y = 2-100*0.010110[x]浮= 11011,-0.010110 [y]浮= 11100,0.0101109Ex-Ey = 11011+00100 = 11111 [x]浮= 11100,1.110101(0) x+y 1 1. 1 1 0 1 0 1+ 0 0. 0 1 0 1 1 00 0. 0 0 1 0 1 1规格化处理: 0.101100 x+y= 0.101100*2阶码-611010x-y1 1.1 1 0 1 0 1 + 1 1.1 0 1 0 1 01 1.0 1 1 1 1 1规格化处理: 1.011111 阶码11100x-y=-0.100001*2-410.(1) Ex = 0011, Mx = 0.110100Ey = 0100, My = 0.100100 Ez = Ex+Ey = 0111 Mx*My 0. 1 1 0 1* 0.1 0 0 101101 00000 00000 01101 00000 001110101规格化:26*0.111011(2) Ex = 1110, Mx = 0.011010Ey = 0011, My = 0.111100 Ez = Ex-Ey = 1110+1101 = 1011 [Mx]补 = 00.011010[My]补 = 00.111100, [-My]补 = 11.00010010计算机组成原理第五版习题答案00011010 +[-My]11000100 11011110 10111100+[My]00111100 11111000 111100000.0 +[My]00111100 00101100 010110000.01 +[-My]11000100 00011100 001110000.011 +[-My]11000100 11111100 111110000.0110 +[My]00111100 00110100 011010000.01101 +[-My]1 1 0 00 1 0 0 0 0 1 0 1 10 00.01101 商 = 0.110110*2-6, 11.4 位加法器如上图,C i = A i B i + A i C i 1 + B i C i 1 = A i B i + ( A i + B i )C i 1 = A i B i + ( A i B i )C i 1(1)串行进位方式余数=0.101100*2-6C 1 = G 1+P 1C 0 C 2 = G 2+P 2C 1 C 3 = G 3+P 3C 2 C 4 = G 4+P 4C 3 其中:G 1 = A 1B 1G 2 = A 2B 2G 3 = A 3B 3 G 4 = A 4B 4P1 = A 1⊕B 1(A 1+B 1 也对) P 2 = A 2⊕B 2 P 3 = A 3⊕B 3 P 4 = A 4⊕B 4(2)并行进位方式 C 1 = G 1+P 1C 0C 2 = G 2+P 2G 1+P 2P 1C 0C 3 = G 3+P 3G 2+P 3P 2G 1+P 3P 2P 1C 0C 4 = G 4+P 4G 3+P 4P 3G 2+P 4P 3P 2G 1+P 4P 3P 2P 1C 0“计算机组成原理第五版习题答案12.(1)组成最低四位的74181 进位输出为:C4 = C n+4 = G+PC n = G+PC0,C0为向第0 位进位其中,G = y3+y2x3+y1x2x3+y0x1x2x3,P = x0x1x2x3,所以C5 = y4+x4C4C6 = y5+x5C5 = y5+x5y4+x5x4C4(2)设标准门延迟时间为T,与或非”门延迟时间为1.5T,则进位信号C0,由最低位传送至C6需经一个反相器、两级“与或非”门,故产生C0的最长延迟时间为T+2*1.5T = 4T(3)最长求和时间应从施加操作数到ALU 算起:第一片74181 有3 级“与或非”门(产生控制参数x0, y0, C n+4),第二、三片74181 共 2 级反相器和 2 级“与或非”门(进位链),第四片74181 求和逻辑(1 级与或非门和 1 级半加器,设其延迟时间为3T),故总的加法时间为:t0 = 3*1.5T+2T+2*1.5T+1.5T+3T = 14T13.设余三码编码的两个运算数为X i和Y i,第一次用二进制加法求和运算的和数为S i’,进位为C i+1’,校正后所得的余三码和数为S i,进位为C i+1,则有:X i = X i3X i2X i1X i0Y i = Y i3Y i2Y i1Y i0S i’ = S i3’S i2’S i1’S i0’s i3 s i2 s i1 s i0Ci+1FA FA FA FA十进校正+3VFA s i3'FAs i2'FAs i1'FAs i0'二进加法X i3 Y i3 X i2 Y i2 X i1 Y i1 X i0 Y i0当C i+1’ = 1时,S i = S i’+0011并产生C i+1当C i+1’ = 0时,S i = S i’+1101根据以上分析,可画出余三码编码的十进制加法器单元电路如图所示。

计算机组成与设计第五版(Chapter2)

计算机组成与设计第五版(Chapter2)Chapter 2 Solutions S-3 2.1 addi f, h, -5 (note, no subi) add f, f, g2.2 f = g + h + i2.3 sub $t0, $s3, $s4add $t0, $s6, $t0lw $t1, 16($t0)sw $t1, 32($s7)2.4 B[g] = A[f] + A[1+f];2.5 add $t0, $s6, $s0add $t1, $s7, $s1lw $s0, 0($t0)lw $t0, 4($t0)add $t0, $t0, $s0sw $t0, 0($t1)2.62.6.1 temp = Array[0];temp2 = Array[1];Array[0] = Array[4];Array[1] = temp;Array[4] = Array[3];Array[3] = temp2;2.6.2 lw $t0, 0($s6)lw $t1, 4($s6)lw $t2, 16($s6)sw $t2, 0($s6)sw $t0, 4($s6)lw $t0, 12($s6)sw $t0, 16($s6)sw $t1, 12($s6)S-4 ChapterSolutions22.712ab12128cd8ef4ef4cd0120ab2.8 28824000182.9 sll $t0, $s1, 2 # $t0 <-- 4*gadd $t0, $t0, $s7 # $t0 <-- Addr(B[g])lw $t0, 0($t0) # $t0 <-- B[g]addi $t0, $t0, 1 # $t0 <-- B[g]+1sll $t0, $t0, 2 # $t0 <-- 4*(B[g]+1) = Addr(A[B[g]+1]) lw $s0, 0($t0) # f <-- A[B[g]+1]2.10 f = 2*(&A);2.11addi $t0, $s6, 4I-type82284add $t1, $s6, $0R-type02209sw $t1, 0($t0)I-type43890lw $t0, 0($t0)I-type35880add $s0, $t1, $t0R-type098162.122.12.1 500000002.12.2 overflow2.12.3 B00000002.12.4 no overflow2.12.5 D00000002.12.6 overflow2.132.13.1 128 231?1, x ? 231?129 and 128 ? x ??231, x ??231? 128(impossible)2.13.2 128? x ? 231?1, x ??231?129 and 128 ? x ??231, x ? 231? 128(impossible)2.13.3 x? 128 ??231, x ??231? 128 and x ? 128 ? 231? 1, x ? 231? 127(impossible)Chapter 2 Solutions S-52.14 r-type, add $s0, $s0, $s02.15 i-type, 0xAD4900202.16 r-type, sub $v1, $v1, $v0, 0x006218222.17 i-type, lw $v0, 4($at), 0x8C2200042.182.18.1 opcode would be 8 bits, rs, rt, rd fi elds would be 7 bits each2.18.2 opcode would be 8 bits, rs and rt fi elds would be 7 bits each2.18.3 more registers →more bits per instruction → could increase code sizemore registers → less register spills → less instructionsmore instructions → more appropriate instruction → decrease code sizemore instructions → larger opcodes → larger code size2.192.19.1 0xBABEFEF82.19.2 0xAAAAAAA02.19.3 0x000055452.20 srl $t0, $t0, 11sll $t0, $t0, 26ori $t2, $0, 0x03ffsll $t2, $t2, 16ori $t2, $t2, 0xffffand $t1, $t1, $t2or $t1, $t1, $t02.21 nor $t1, $t2, $t22.22 lw $t3, 0($s1)sll $t1, $t3, 42.23 $t2 = 32.24 jump: no, beq: noS-6 ChapterSolutions22.252.25.1 i-type2.25.2 addi $t2, $t2, –1beq $t2, $0, loop2.262.26.1 202.26.2 i = 10;do {B += 2;i = i – 1;} while ( i > 0)2.26.3 5*N2.27addi $t0, $0, 0beq $0, $0, TEST1LOOP1: addi $t1, $0, 0beq $0, $0, TEST2LOOP2: add $t3, $t0, $t1sll $t2, $t1, 4add $t2, $t2, $s2sw $t3, ($t2)addi $t1, $t1, 1TEST2: slt $t2, $t1, $s1bne $t2, $0, LOOP2addi $t0, $t0, 1TEST1: slt $t2, $t0, $s0bne $t2, $0, LOOP12.28 14 instructions to implement and 158 instructions executed2.29 for (i=0; i<100; i++) {result += MemArray[s0];s0 = s0 + 4;}Chapter 2 Solutions S-7 2.30 addi $t1, $s0, 400LOOP: lw $s1, 0($t1)add $s2, $s2, $s1addi $t1, $t1, -4bne $t1, $s0, LOOP2.31 fib: addi $sp, $sp, -12 # make room on stacksw $ra, 8($sp) # push $rasw $s0, 4($sp) # push $s0sw $a0, 0($sp) # push $a0 (N)bgt $a0, $0, test2 # if n>0, test if n=1add $v0, $0, $0 # else fib(0) = 0rtn #jtest2: addi $t0, $0, 1 #bne $t0, $a0, gen # if n>1, genadd $v0, $0, $t0 # else fib(1) = 1rtnjgen: subi $a0, $a0,1 # n-1jal fib # call fib(n-1)add $s0, $v0, $0 # copy fib(n-1)sub $a0, $a0,1 # n-2jal fib # call fib(n-2)add $v0, $v0, $s0 # fib(n-1)+fib(n-2)rtn: lw $a0, 0($sp) # pop $a0lw $s0, 4($sp) # pop $s0lw $ra, 8($sp) # pop $raaddi $sp, $sp, 12 # restore spjr $ra# fib(0) = 12 instructions, fib(1) = 14 instructions,# fib(N) = 26 + 18N instructions for N >=22.32 D ue to the recursive nature of the code, it is not possible for the compiler toin-line the function call.2.33 after calling function fib:old $sp -> 0x7ffffffcc ontents of register $ra for-4fib(N)c ontents of register $s0 for-8fib(N)$sp-> -12 c ontents of register $a0 forfib(N)there will be N-1 copies of $ra, $s0 and $a0 S-8 ChapterSolutions22.34 f: addi $sp,$sp,-12$ra,8($sp)sw$s1,4($sp)sw$s0,0($sp)sw$s1,$a2move$s0,$a3movefuncjal$a0,$v0moveadd$a1,$s0,$s1funcjallw$ra,8($sp)$s1,4($sp)lw$s0,0($sp)lw$sp,$sp,12addi$rajr2.35 W e can use the tail-call optimization for the second call to func, but thenwe must restore $ra, $s0, $s1, and $sp before that call. We save only oneinstruction (jr $ra).2.36 R egister $ra is equal to the return address in the caller function, registers$sp and $s3 have the same values they had when function f was called, andregister $t5 can have an arbitrary value. For register $t5, note that althoughour function f does not modify it, function func is allowed to modify it sowe cannot assume anything about the of $t5 aft er function func has beencalled.2.37 MAIN: addi $sp, $sp, -4sw $ra, ($sp)add $t6, $0, 0x30 # ‘0’add $t7, $0, 0x39 # ‘9’add $s0, $0, $0add $t0, $a0, $0LOOP: lb $t1, ($t0)slt $t2, $t1, $t6bne $t2, $0, DONEslt $t2, $t7, $t1bne $t2, $0, DONEsub $t1, $t1, $t6beq $s0, $0, FIRSTmul $s0, $s0, 10FIRST: add $s0, $s0, $t1addi $t0, $t0, 1LOOPjChapter 2 Solutions S-9DONE: add $v0, $s0, $0lw $ra, ($sp)addi $sp, $sp, 4jr $ra2.38 0x000000112.39 Generally, all solutions are similar:lui $t1, top_16_bitsori $t1, $t1, bottom_16_bits2.40 No, jump can go up to 0x0FFFFFFC.2.41 N o, range is 0x604 + 0x1FFFC = 0x0002 0600 to 0x604 – 0x20000= 0xFFFE 0604.2.42 Y es, range is 0x1FFFF004 + 0x1FFFC = 0x2001F000 to 0x1FFFF004- 0x20000 = 1FFDF0042.43 trylk: li $t1,1ll $t0,0($a0)$t0,trylkbnezsc $t1,0($a0)$t1,trylkbeqzlw $t2,0($a1)slt $t3,$t2,$a2$t3,skipbnezsw $a2,0($a1)skip: sw $0,0($a0)2.44 try: ll $t0,0($a1)slt $t1,$t0,$a2$t1,skipbnezmov $t0,$a2sc $t0,0($a1)$t0,trybeqzskip:2.45 It is possible for one or both processors to complete this code without everreaching the SC instruction. If only one executes SC, it completes successfully. Ifboth reach SC, they do so in the same cycle, but one SCcompletes fi rst and thenthe other detects this and fails.S-10 ChapterSolutions22.462.46.1 Answer is no in all cases. Slows down the computer.CCT ? clock cycle timeICa ? instruction count (arithmetic)ICls ? instruction count (load/store)ICb ? instruction count (branch)new CPU time ? 0.75*old ICa*CPIa*1.1*oldCCToldICls*CPIls*1.1*oldCCToldICb*CPIb*1.1*oldCCTTh e extra clock cycle time adds suffi ciently to the new CPU time such thatit is not quicker than the old execution time in all cases.2.46.2 107.04%, 113.43%2.472.47.1 2.62.47.2 0.882.47.3 0.533333333。

计算机组成原理第五版-白中英(详细)第4章习题参考答案

第4章习题参考答案1.ASCII码是7位,如果设计主存单元字长为32位,指令字长为12位,是否合理为什么答:不合理。

指令最好半字长或单字长,设16位比较合适。

一个字符的ASCII 是7位,如果设计主存单元字长为32位,则一个单元可以放四个字符,这也是可以的,只是在存取单个字符时,要多花些时间而已,不过,一条指令至少占一个单元,但只占一个单元的12位,而另20位就浪费了,这样看来就不合理,因为通常单字长指令很多,浪费也就很大了。

2.假设某计算机指令长度为32位,具有双操作数、单操作数、无操作数三类指令形式,指令系统共有70条指令,请设计满足要求的指令格式。

答:字长32位,指令系统共有70条指令,所以其操作码至少需要7位。

双操作数指令单操作数指令无操作数指令3.指令格式结构如下所示,试分析指令格式及寻址方式特点。

15 10 !9 8 7 4 3 0答:该指令格式及寻址方式特点如下:(1) 单字长二地址指令。

》(2) 操作码字段OP可以指定26=64种操作。

(3) 源和目标都是通用寄存器(可分指向16个寄存器)所以是RR型指令,即两个操作数均在寄存器中。

(4) 这种指令结构常用于RR之间的数据传送及算术逻辑运算类指令。

4.指令格式结构如下所示,试分析指令格式及寻址方式特点。

15 10 9 8 7 4 3 015 10 9 8 7 4 3 0答:该指令格式及寻址方式特点如下:(1)双字长二地址指令,用于访问存储器。

(2)操作码字段OP可以指定26=64种操作。

(3)RS型指令,一个操作数在通用寄存器(选择16个之一),另一个操作数在主存中。

有效地址可通过变址寻址求得,即有效地址等于变址寄存器(选择16个之一)内容加上位移量。

|5.指令格式结构如下所示,试分析指令格式及寻址方式特点。

15 12 11 9 8 6 5 3 2 0答:该指令格式及寻址方式特点如下:(1)该指令为单字长双操作数指令,源操作数和目的操作数均由寻址方式和寄存器构成,寄存器均有8个,寻址方式均有8种。

计算机组成原理第五版白中英(详细)第3章习题答案

第3章习题答案1、设有一个具有20位地址和32位字长的存储器,问 (1) 该存储器能存储多少字节的信息? (2) 如果存储器由512K ×8位SRA M 芯片组成,需要多少片? (3) 需要多少位地址作芯片选择? 解:(1) 该存储器能存储:字节4M 832220=⨯(2) 需要片8823228512322192020=⨯⨯=⨯⨯K(3) 用512K ⨯8位的芯片构成字长为32位的存储器,则需要每4片为一组进行字长的位数扩展,然后再由2组进行存储器容量的扩展。

所以只需一位最高位地址进行芯片选择。

2、已知某64位机主存采用半导体存储器,其地址码为26位,若使用4M ×8位的DR A M 芯片组成该机所允许的最大主存空间,并选用内存条结构形式,问; (1) 若每个内存条为16M ×64位,共需几个内存条? (2) 每个内存条内共有多少D RAM 芯片? (3) 主存共需多少DRAM 芯片? CPU 如何选择各内存条? 解:(1) 共需内存条条4641664226=⨯⨯M (2) 每个内存条内共有个芯32846416=⨯⨯M M 片 (3) 主存共需多少个RAM 1288464648464226=⨯⨯=⨯⨯M M M 芯片, 共有4个内存条,故CPU 选择内存条用最高两位地址A 24和A 25通过2:4译码器实现;其余的24根地址线用于内存条内部单元的选择。

3、用16K ×8位的DR A M 芯片构成64K ×32位存储器,要求: (1) 画出该存储器的组成逻辑框图。

(2) 设存储器读/写周期为0.5μS ,CPU 在1μS 内至少要访问一次。

试问采用哪种刷新方式比较合理?两次刷新的最大时间间隔是多少?对全部存储单元刷新一遍所需的实际刷新时间是多少? 解:(1) 用16K ×8位的DR A M 芯片构成64K ×32位存储器,需要用个芯16448163264=⨯=⨯⨯K K 片,其中每4片为一组构成16K ×32位——进行字长位数扩展(一组内的4个芯片只有数据信号线不互连——分别接D0~D 7、D 8~D 15、D 16~D23和D 24~D 31,其余同名引脚互连),需要低14位地址(A 0~A 13)作为模块内各个芯片的内部单元地址——分成行、列地址两次由A 0~A6引脚输入;然后再由4组进行存储器容量扩展,用高两位地址A 14、A15通过2:4译码器实现4组中选择一组。

计算机组成与设计第五版答案

解决方案4第4章解决方案S-34.1 4.1.1信号值如下:RegWrite MemReadALUMux MemWrite aloop RegMux Branch 0 0 1(Imm)1 ADD X 0 ALUMux是控制ALU输入处Mux 的控制信号,0(Reg)选择寄存器文件的输出,1(Imm)从指令字中选择立即数作为第二个输入。

以铝合金为控制信号,控制Mux输入寄存器文件,0(ALU)选择ALU的输出,1(Mem)选择存储器的输出。

X值表示“不关心”(不管信号是0还是1)4.1.2除了未使用的寄存器4.1.3分支添加单元和写入端口:分支添加,寄存器写入端口没有输出:无(所有单元都生成输出)4.2 4.2.1第四条指令使用指令存储器、两个寄存器读取端口、添加Rd和Rs的ALU,寄存器中的数据存储器和写入端口。

4.2.2无。

可以使用此指令实现现有的块。

4.2.3无。

此指令可以在不添加新的控制信号的情况下实现。

它只需要改变控制逻辑。

4.3 4.3.1时钟周期时间由关键路径决定。

对于给定的延迟,它正好得到加载指令的数据值:I-Mem(读取指令)、Regs(长于控制时间)、Mux(选择ALU)输入)、ALU、数据存储器和Mux(从内存中选择要写入寄存器的值)。

这个路径的延迟是400ps吗?200秒?第30页?120秒?350马力?第30页?1130马力。

1430马力(1130马力?300 ps,ALU在关键路径上)。

4.3.2第4.3.2节加速度来自于时钟周期时间和程序所需时钟周期数的变化:程序要求的周期数减少了5%,但循环时间是1430而不是1130,所以我们的加速比是(1/0.95)*(1130/1430)?0.83,这意味着我们实际上在减速。

S-4第4章解决方案4.3.3成本始终是所有组件(不仅仅是关键路径上的组件)的总成本,因此原处理器的成本是I-Mem、Regs、Control、ALU、D-Mem、2个Add单元和3个Mux 单元,总成本是1000?200?500?100?2000年?2*30?3*10?3890我们将计算与基线相关的成本。

计算机组成与设计第五版答案

计算机组成与设计:《计算机组成与设计》是2010年机械工业出版社出版的图书,作者是帕特森(DavidA.Patterson)。

该书讲述的是采用了一个MIPS 处理器来展示计算机硬件技术、流水线、存储器的层次结构以及I/O 等基本功能。

此外,该书还包括一些关于x86架构的介绍。

内容简介:这本最畅销的计算机组成书籍经过全面更新,关注现今发生在计算机体系结构领域的革命性变革:从单处理器发展到多核微处理器。

此外,出版这本书的ARM版是为了强调嵌入式系统对于全亚洲计算行业的重要性,并采用ARM处理器来讨论实际计算机的指令集和算术运算。

因为ARM是用于嵌入式设备的最流行的指令集架构,而全世界每年约销售40亿个嵌入式设备。

采用ARMv6(ARM 11系列)为主要架构来展示指令系统和计算机算术运算的基本功能。

覆盖从串行计算到并行计算的革命性变革,新增了关于并行化的一章,并且每章中还有一些强调并行硬件和软件主题的小节。

新增一个由NVIDIA的首席科学家和架构主管撰写的附录,介绍了现代GPU的出现和重要性,首次详细描述了这个针对可视计算进行了优化的高度并行化、多线程、多核的处理器。

描述一种度量多核性能的独特方法——“Roofline model”,自带benchmark测试和分析AMD Opteron X4、Intel Xeo 5000、Sun Ultra SPARC T2和IBM Cell的性能。

涵盖了一些关于闪存和虚拟机的新内容。

提供了大量富有启发性的练习题,内容达200多页。

将AMD Opteron X4和Intel Nehalem作为贯穿《计算机组成与设计:硬件/软件接口(英文版·第4版·ARM版)》的实例。

用SPEC CPU2006组件更新了所有处理器性能实例。

图书目录:1 Computer Abstractions and Technology1.1 Introduction1.2 BelowYour Program1.3 Under the Covers1.4 Performance1.5 The Power Wall1.6 The Sea Change: The Switch from Uniprocessors to Multiprocessors1.7 Real Stuff: Manufacturing and Benchmarking the AMD Opteron X41.8 Fallacies and Pitfalls1.9 Concluding Remarks1.10 Historical Perspective and Further Reading1.11 Exercises2 Instructions: Language of the Computer2.1 Introduction2.2 Operations of the Computer Hardware2.3 Operands of the Computer Hardware2.4 Signed and Unsigned Numbers2.5 Representing Instructions in the Computer2.6 Logical Operations2.7 Instructions for Making Decisions2.8 Supporting Procedures in Computer Hardware2.9 Communicating with People2.10 ARM Addressing for 32-Bit Immediates and More Complex Addressing Modes2.11 Parallelism and Instructions: Synchronization2.12 Translating and Starting a Program2.13 A C Sort Example to Put lt AU Together2.14 Arrays versus Pointers2.15 Advanced Material: Compiling C and Interpreting Java2.16 Real Stuff." MIPS Instructions2.17 Real Stuff: x86 Instructions2.18 Fallacies and Pitfalls2.19 Conduding Remarks2.20 Historical Perspective and Further Reading2.21 Exercises3 Arithmetic for Computers3.1 Introduction3.2 Addition and Subtraction3.3 Multiplication3.4 Division3.5 Floating Point3.6 Parallelism and Computer Arithmetic: Associativity 3.7 Real Stuff: Floating Point in the x863.8 Fallacies and Pitfalls3.9 Concluding Remarks3.10 Historical Perspective and Further Reading3.11 Exercises4 The Processor4.1 Introduction4.2 Logic Design Conventions4.3 Building a Datapath4.4 A Simple Implementation Scheme4.5 An Overview of Pipelining4.6 Pipelined Datapath and Control4.7 Data Hazards: Forwarding versus Stalling4.8 Control Hazards4.9 Exceptions4.10 Parallelism and Advanced Instruction-Level Parallelism4.11 Real Stuff: theAMD OpteronX4 (Barcelona)Pipeline4.12 Advanced Topic: an Introduction to Digital Design Using a Hardware Design Language to Describe and Model a Pipelineand More Pipelining Illustrations4.13 Fallacies and Pitfalls4.14 Concluding Remarks4.15 Historical Perspective and Further Reading4.16 Exercises5 Large and Fast: Exploiting Memory Hierarchy5.1 Introduction5.2 The Basics of Caches5.3 Measuring and Improving Cache Performance5.4 Virtual Memory5.5 A Common Framework for Memory Hierarchies5.6 Virtual Machines5.7 Using a Finite-State Machine to Control a Simple Cache5.8 Parallelism and Memory Hierarchies: Cache Coherence5.9 Advanced Material: Implementing Cache Controllers5.10 Real Stuff: the AMD Opteron X4 (Barcelona)and Intel NehalemMemory Hierarchies5.11 Fallacies and Pitfalls5.12 Concluding Remarks5.13 Historical Perspective and Further Reading5.14 Exercises6 Storage and Other I/0 Topics6.1 Introduction6.2 Dependability, Reliability, and Availability6.3 Disk Storage6.4 Flash Storage6.5 Connecting Processors, Memory, and I/O Devices6.6 Interfacing I/O Devices to the Processor, Memory, andOperating System6.7 I/O Performance Measures: Examples from Disk and File Systems6.8 Designing an I/O System6.9 Parallelism and I/O: Redundant Arrays of Inexpensive Disks6.10 Real Stuff: Sun Fire x4150 Server6.11 Advanced Topics: Networks6.12 Fallacies and Pitfalls6.13 Concluding Remarks6.14 Historical Perspective and Further Reading6.15 Exercises7 Multicores, Multiprocessors, and Clusters7.1 Introduction7.2 The Difficulty of Creating Parallel Processing Programs7.3 Shared Memory Multiprocessors7.4 Clusters and Other Message-Passing Multiprocessors7.5 Hardware Multithreading 637.6 SISD,MIMD,SIMD,SPMD,and Vector7.7 Introduction to Graphics Processing Units7.8 Introduction to Multiprocessor Network Topologies7.9 Multiprocessor Benchmarks7.10 Roofline:A Simple Performance Model7.11 Real Stuff:Benchmarking Four Multicores Using theRooflineMudd7.12 Fallacies and Pitfalls7.13 Concluding Remarks7.14 Historical Perspective and Further Reading7.15 ExercisesInuexC D-ROM CONTENTA Graphics and Computing GPUSA.1 IntroductionA.2 GPU System ArchitecturesA.3 Scalable Parallelism-Programming GPUSA.4 Multithreaded Multiprocessor ArchitectureA.5 Paralld Memory System G.6 Floating PointA.6 Floating Point ArithmeticA.7 Real Stuff:The NVIDIA GeForce 8800A.8 Real Stuff:MappingApplications to GPUsA.9 Fallacies and PitflaUsA.10 Conduding RemarksA.1l HistoricalPerspectiveandFurtherReadingB1 ARM and Thumb Assembler InstructionsB1.1 Using This AppendixB1.2 SyntaxB1.3 Alphabetical List ofARM and Thumb Instructions B1.4 ARM Asembler Quick ReferenceB1.5 GNU Assembler Quick ReferenceB2 ARM and Thumb Instruction EncodingsB3 Intruction Cycle TimingsC The Basics of Logic DesignD Mapping Control to HardwareADVANCED CONTENTHISTORICAL PERSPECTIVES & FURTHER READINGTUTORIALSSOFTWARE作者简介:David A.Patterson,加州大学伯克利分校计算机科学系教授。

计算机组成与设计第五版答案

解决方案4第4章解决方案S-34.1 4.1.1信号值如下如下:RegWrite MemReadALUMux MemWrite aloop RegMux Branch0 0 1(Imm)1 ADD X 0ALUMux是在ALU输入处控制Mux 的控制信号,0(Reg)选择寄存器文件的输出,和1(Imm)从指令字中选择立即数作为第二个输入铝合金是控制输入到寄存器文件的Mux的控制信号,0(ALU)选择ALU 的输出,1(Mem)选择存储器的输出。

X值表示“不在乎”(不管信号是0还是1)4.1.2除了未使用的寄存器4.1.3的分支添加单元和写入端口:分支添加,寄存器的写入端口无输出:无(所有单元都产生输出)4.2 4.2.1第四条指令使用指令存储器,两个寄存器读端口,将Rd和Rs相加的ALU,数据存储器和寄存器中的写入端口。

4.2.2无。

此指令可使用现有的块来实现。

4.2.3无。

该指令无需添加新的控制信号即可实现。

它只需要改变控制逻辑。

4.3 4.3.1时钟周期时间由关键路径决定,对于给定的延迟,它恰好是为了得到加载指令的数据值:I-Mem(读取指令)、Regs(比控制时间长)、Mux(选择ALU 输入)、ALU、数据存储器,和Mux(从内存中选择要写入寄存器的值)。

这个路径的延迟是400ps?200秒?第30页?120秒?350马力?第30页?1130马力。

1430马力(1130马力?300 ps,ALU在关键路径上)。

4.3.2第4.3.2加速来自于时钟周期时间的变化和程序所需时钟周期数的变化:程序所需的周期数减少了5%,但周期时间是1430而不是1130,所以我们的加速比是(1/0.95)*(1130/1430)?0.83,这意味着我们实际上在减速。

S-4第4章解决方案4.3.3成本始终是所有组件(不只是关键路径上的组件)的总成本,因此原始处理器的成本为I-Mem、Regs、Control、ALU、D-Mem、2个Add单元和3个Mux 单元,总成本为1000?200?500?100?2000年?2*30?3*10?3890.我们将计算与基线相关的成本。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

解决方案4第4章解决方案S-34.1 4.1.1信号值如下:RegWrite MemReadALUMux MemWrite aloop RegMux Branch 0 0 1(Imm)1 ADD X 0 ALUMux是控制ALU输入处Mux 的控制信号,0(Reg)选择寄存器文件的输出,1(Imm)从指令字中选择立即数作为第二个输入。

铝合金是控制Mux输入寄存器文件的控制信号,0(ALU)选择ALU的输出,1(Mem)选择存储器的输出。

X值表示“不关心”(不管信号是0还是1)4.1.2除了未使用的寄存器4.1.3分支添加单元和写入端口:分支添加,寄存器写入端口没有输出:无(所有单元都生成输出)4.2 4.2.1第四条指令使用指令存储器、两个寄存器读取端口、添加Rd和Rs的ALU,寄存器中的数据存储器和写入端口。

4.2.2无。

此指令可以使用现有的块来实现。

4.2.3无。

此指令可以在不添加新的控制信号的情况下实现。

它只需要改变控制逻辑。

4.3 4.3.1时钟周期时间由关键路径决定。

对于给定的延迟,它正好得到加载指令的数据值:I-Mem(读取指令)、Regs(长于控制时间)、Mux(选择ALU)输入)、ALU、数据存储器和Mux(从内存中选择要写入寄存器的值)。

这个路径的延迟是400ps 吗?200秒?30秒?120秒?350马力?30秒?1130马力。

1430马力(1130马力?300

ps,ALU在关键路径上)。

4.3.2第4.3.2节加速度来自于时钟周期时间和程序所需时钟周期数的变化:程序要求的周期数减少了5%,但循环时间是1430而不是1130,所以我们的加速比是(1/0.95)*(1130/1430)?0.83,这意味着我们实际上在减速。

S-4第4章解决方案4.3.3成本始终是所有组件(不仅仅是关键路径上的组件)的总成本,因此原处理器的成本是I-Mem、Regs、Control、ALU、D-Mem、2个Add单元和3个Mux单元,总成本是1000?200?500?100?2000年?2*30?3*10?3890我们将计算与基线相关的成本。

相对于此基线的性能是我们先前计算的加速,相对于基线的成本/性能如下:新成本:3890?600?4490相对成本:4490/3890?1.15性价比:1.15/0.83?1.39条。

我们必须付出更高的代价来换取更差的性能;成本/性能比未经修改的处理器差得多。

4.2.2的单位是4.2倍,所以指令选择4.2倍的时间,而不是4.2倍的时间?4注意,通过另一个加法单元的路径较短,因为I-Mem的延迟比加法单元的延迟长。

我们有:200秒?15磅?10磅?70秒?20秒?315 ps4.4.3条件分支和无条件分支具有相同的长延迟路径来计算分支地址。

此外,它们还有一个长延迟路径,通过寄存器、Mux和ALU计算PCSrc

条件。

关键路径是这两条路径中较长的一条。

对于这些路径,通过PCSrc的路径具有更长的延迟:200ps?90秒?20秒?90秒?20秒?420 ps4.4.4 PC相关分支机构。

4.4.5 PC 相对无条件分支指令。

我们在c部分看到,这不是条件分支的关键路径,它只在PC相关分支上需要。

注意,MIPS没有实际的无条件分支(bnezero、zero和Label扮演这个角色,所以不需要无条件分支操作码),所以对于MIPS,这个问题的答案实际上是“None”。

4.4.6在这两条指令(bne和ADD)中,bne的关键路径较长,决定了时钟周期时间。

注意ADD的每条路径都小于或等于BNE的相应路径,因此第4章中解决方案S-5中的单位延迟变化不会影响这一点。

因此,我们关心的是单元的延迟如何影响BNE的关键路径,而这个单元不在关键路径上,所以这个单元成为关键的唯一方法就是增加它的延迟直到它通过符号扩展,移位和分支加法地址计算的路径比PCSrc通过寄存器、Mux和ALU的路径长。

所以延迟是2.5倍,所以延迟乘以2.5倍?10%?35%4.

5.2符号扩展电路实际上在每个循环中计算一个结果。