用DSP实现时钟复位功能

用DSP实现时钟复位功能

⽤DSP实现时钟复位功能第⼆章CPU基本功能实现2.1电源模块的设计TMS320F2812芯⽚采⽤双供电模式,1.8V(主频135MHz)内核电压和3.3V 外围接⼝电压。

芯⽚的上电顺序是:先加载外围接⼝电压3.3V,当外围接⼝电压升⾄2.5V时开始加载芯⽚核电压1.8V,电压爬升⼩于10ms。

芯⽚下电的顺序是:先断掉外围接⼝电压3.3V,复位信号始终低有效,保持8us,接着使芯⽚核电压1.8V降为0。

实际系统的外接电源采⽤的是+5V开关电源,所以硬件电路中必须采⽤电源转换芯⽚组。

市场上电源转换芯⽚的种类丰富、⼚家繁多,结果认真分析和⽐较,本系统中采⽤的电源转换芯⽚与DSP芯⽚为同⼀家⼚家TI公司,芯⽚之间的兼容性好,可靠性⾼,性能参数指标具有⼀致性。

电源芯⽚TPS767D301为+5V外接电压转换+3.3V提供可能,采⽤可调电源芯⽚TPS767D301为F2812提供1.8V (主频135MHz)或1.9V(主频150MHz)的核电压。

TMS320F2812典型的上电掉电次序图如下图所⽰:图2-1TMS320F2812典型的上电掉电次序图如下图所⽰:在使⽤TPS767D301芯⽚时要注意上电次序的问题,要求对3.3V先上电,1.8V 后上电,最好使1、8V的上电时间晚⼀点,利⽤电阻电容做到⼀些延迟。

当TMS320F2812芯⽚在主频135MHz情况下⼯作时,芯⽚功耗为565mW,电流消耗仅在0.2A左右,存储器需要0.2A的电流,CPLD需要0.1A,可调电源转换芯⽚TPS767D301的最⼤输出电流为1A,完全可以满⾜模块需要。

由于TPS767D301芯⽚⾃⾝能够产⽣复位信号,此复位信号可直接供DSP芯⽚使⽤,从芯⽚的22引脚直接输出复位信号。

图2-2TPS767D3xx结构图此电源转化芯⽚组既可以满⾜系统⼯作时的电流要求,⼜可以解决DSP芯⽚上、下电顺序问题。

DSP芯⽚的电源部分设计如图所⽰。

第四章 F2833x系统时钟及中断控制-TMS320F28335 DSP原理、开发及应用-符晓

看门狗计数器独立于CPU而运行 看门狗计数器溢出时,产生复位或者中断

CPU正常运行时看门狗计数器被定时复位,即“喂狗” 150MHz的时钟频率相当于6.67ns,看门狗计数器是16

位的,从0开始计数到计满溢出是65536个数,即 6.67ns*65536=4.396ms

第四章 系统时钟及中断控制

4.1 F2833x OSC与PLL (对应: SysCtrl.c)

3.3V时钟脉冲输入

外部晶振

片上振 荡器

PLL工作模式 XRS

表4-1 PLL工作模式

工作模式介绍

PLLSTS[DIVSEL]

PLL关闭

通过将PLLSTS寄存器中的PLLOFF位置1可将PLL模块关闭,从而减少

2-0

HSPCLK

ADC

2-0

LSPCLK

SCI / SPI / I2C / McBSP

4.2 外设时钟信号的寄存器

SysCtrlRegs.PCLKCR0

15

14

13

ECANB ECANA MA ENCLK ENCLK ENCLK

7

6

5

reserved reserved

SCIC ENCLK

12

MB ENCLK

0,1

系统噪声并减少功率损耗。在进入此模式前应首先将PLLCR寄存器设为

0x0000。

2

3

PLL旁路

上电复位或 复位后,PLL进入该模式。在该模式下时钟信号直接绕过

0,1

PLL模块,但PLL模块却未关闭。

2

3

PLL使能

向PLLCR寄存器中写入非零的数可使能PLL模块,一旦写入数据后,PLL

DSP28335的调试总结,这是一份总结很全面的资料,我在学

DSP28335的调试总结,这是一份总结很全面的资料,我在学习开发板的一些总结,希望能得到同行的帮助,愿与大家一起学习和分享1DSP的PWM信号1.1简介DSP28335共12路16位的ePWM,能进行频率和占空比控制。

ePWM的时钟TBCLK=SYSCLKOUT/(HSPCLKDIV×CLKDIV):PWM信号频率由时基周期寄存器TBPDR和时基计数器的计数模式决定。

初始化程序采用的计数模式为递增计数模式。

在递增计数模式下,时基计数器从零开始增加,直到达到周期寄存器值(TBPDR)。

然后时基计数器复位到零,再次开始增加。

PWM信号周期与频率的计算如下:1.2端口对应关系通道相应PWM的A/B对应JP0B端口号1ePWM1A92ePWM1B103ePWM2A114ePWM2B125ePWM3A136ePWM3B147ePWM4A158ePWM4B169ePWM5A1710ePWM5B1811ePWM6A1912ePWM6B20说明:JP0B的端口号按“Z”字形顺序数。

1.3初始化程序注释void InitPwm1AB(float32f){Uint16T= 2343750/f-1.0;//系统时钟SYSCLKOUT=150MHz,TBCLK=6.6666667ns,在连续增计数模式下,f=150000000/(TBPDR+1) EALLOW;//先初始化通用输入输出口//GpioCtrlRegs.GPAPUD.bit.GPIO0 = 0;GpioCtrlRegs.GPAMUX1.bit.GPIO0 = 1;GpioCtrlRegs.GPAPUD.bit.GPIO1 = 0;GpioCtrlRegs.GPAMUX1.bit.GPIO1 = 1;EPwm1Regs.TBPHS.half.TBPHS= 0; // 在相位寄存器中设置计数器的起始计数位置//下面两条语句组合对PWM的时钟进行分频EPwm1Regs.TBCTL.bit.CLKDIV = 6;EPwm1Regs.TBCTL.bit.HSPCLKDIV = 0;EPwm1Regs.TBPRD = T; //在周期寄存器中设置计数器的计数周期//TBCTL为定时器控制寄存器EPwm1Regs.TBCTL.bit.CTRMODE= TB_COUNT_UP; //设置计数模式位为连续增计数模式,产生对称方波EPwm1Regs.TBCTL.bit.PHSEN = TB_DISABLE; // 将定时器相位使能位关闭EPwm1Regs.TBCTL.bit.PRDLD = TB_SHADOW;//映射寄存器SHADOW使能并配置映射寄存器为自动读写EPwm1Regs.TBCTL.bit.SYNCOSEL = TB_CTR_ZERO; // 定时器时钟源选择,一共有四种时钟源EPwm1Regs.CMPA.half.CMPA= 0.0001*T;// 设置EPWM1A比较值寄存器的比较值,即体现EPWM1A的占空比EPwm1Regs.CMPB= 0.0001*T;EPwm1Regs.CMPCTL.bit.SHDWAMODE = CC_SHADOW;//A模块比较模式EPwm1Regs.CMPCTL.bit.SHDWBMODE = CC_SHADOW;//B模块比较模式EPwm1Regs.CMPCTL.bit.LOADAMODE= CC_CTR_ZERO; // A模块比较使能,通过写0来清除SHDWAMODE位来使能load on CTR=ZeroEPwm1Regs.CMPCTL.bit.LOADBMODE = CC_CTR_ZERO; // B模块比较使能,通过写0来清除SHDWBMODE位来使能load on CTR=Zero//AQCTLA为输出A比较方式控制寄存器EPwm1Regs.AQCTLA.bit.ZRO = AQ_SET; // TBCTR(计数器)计到零时使输出为反向EPwm1Regs.AQCTLA.bit.CAU = AQ_CLEAR;//TBCTR(计数器)与CMPA在up 计数时相等使输出为high,这关系的输出的占空比EPwm1Regs.AQCTLB.bit.ZRO = AQ_SET;EPwm1Regs.AQCTLB.bit.CBU = AQ_CLEAR;EDIS;}2DSP的CAN通信2.1CAN2.0B协议简述TMS320F28335上有2个增强型CAN总线控制器,符合CAN2.0B协议,其总线波特率可达到1Mbps。

DSP实验报告定时器2

实验二DSP系统定时器的使用一、实验目的:1、掌握5402 DSP片上定时器的初始化设置及应用;2、掌握DSP系统中实现定时的原理及方法;3、了解5402 DSP中断寄存器IMR、IFR的结构和使用;4、掌握5402 DSP系统中断的初始化设置过程和方法;5、掌握在C语言中嵌入汇编语句实现数字I/O的方法。

二、实验原理:1、定时器及其初始化在5402内部包括两个完全相同的定时器:定时器0和定时器1。

每个定时器分别包括3个寄存器:定时器周期寄存器PRD、定时器寄存器TIM、定时器控制寄存器TCR,其中TCR 寄存器中包括定时器分频系数TDDR、定时器预分频计数器PSC两个功能寄存器。

通过PRD 和TDDR可以设置定时器的初始值,TIM(16bits)和PSC(4bits)是用于定时的减法计数器。

CLKOUT是定时器的输入时钟,最大频率为100Mhz。

定时器相当于20bit的减法计数器。

定时器的结构如图1所示。

图1 定时器的组成框图定时器的定时周期为:CLKOUT×(TDDR+1)×(PRD+1)其中,CLKOUT为时钟周期,TDDR和PRD分别为定时器的分频系数和时间常数。

在正常工作情况下,当TIM减到0后,PRD中的时间常数自动地加载到TIM。

当系统复位或者定时器单独复位时,PRD中的时间常数重新加载到TIM。

同样地,每当复位或PSC减到0后,定时器分频系数TDDR自动地加载到PSC。

PSC在CLKOUT作用下,作减1计数。

当PSC 减到0时,产生一个借位信号,令TIM作减l计数。

TIM减到0后,产生定时中断信号TINT,传送至CPU和定时器输出引脚TOUT。

例如:欲设置定时器0的定时周期为1ms,当DSP工作频率为100Mhz时,通过上式计算可得出:TDDR=15,PRD=6520。

2、定时器的使用下面是一段定时器应用程序,每检测到一次中断,ms+1,利用查询方式每计500个数就令XF引脚的电平翻转一次,在XF引脚输出一矩形波信号,因定时器1ms中断一次,故500ms就使LED翻转一次,这样LED指示灯就不停地闪烁。

采用DSP实现日历时钟及时钟显示的方法

采用DSP实现日历时钟及时钟显示的方法西安石油大学井下信息探测实验室710065党瑞荣罗兵武张珂摘要:本文简要介绍了日历时钟12887、DSP及液晶模块的功能特点,以及它们的硬件接口及软件设计方法,通过DSP控制,实现日历时钟在液晶上的实时显示。

关键词:日历时钟DSP 接口液晶显示Abstract: This paper introduces traits of calendar clock 12887,DSP and the external controller SED1335 of LCD modle,and the hardware interface circuit .It also introduces the means of software degsin. calendar clock is diplayed in the LCD by the control of DSP.Key words :Calendar clock DSP interface LCD一引言在智能仪表中,除了必须具备信号测量,信号处理,键盘输入,屏幕显示等一些基本功能以外,有时也希望能向用户提供日历时钟显示之类的辅助功能以方便使用。

这时,就常常需要用到带后备电池的实时时钟器件。

一方面用以向系统提供长时间不间断的日历时钟,另一方面借用芯片内剩余的非易失静态RAM用以关机后长期保存系统的一些重要数据信息,具有这种功能的实时时钟芯片很多,如MCI4681、MSM5832等,它们都需要适当的外围电路支持,而且外带电池,不方便与用户接口。

而DS12887是DALLAS半导体公司研制的实时时钟器件,集成度高,不需要外围电路支持,与用户接口极为方便。

尤其是该芯片内含锂电池、石英晶振和写保护电路。

因此,DS12887是一个完整的子系统。

本文以作者的实践为基础。

介绍采用TMS320VC33实现日历时钟及时钟液晶显示的硬件设计和软件编程,其处理过程具有广泛的通用性。

DSP CLK信号详解

时钟与定时器包括时钟产生器、通用定时器、实时时钟以及看门狗定时器等。

时钟产生器的功能是产生CPU的工作时钟,并提供CLKOUT时钟输出;通用定时器、实时时钟及看门狗定时器的功能是通过计数器为系统提供定时时钟和年、月、日、时、分、秒等时钟信号,以及监控系统正常运行的看门狗时钟,并能发出相应中断。

1 . 时钟发生器1.1 时钟模式寄存器 CLKMD时钟发生器可以从CLKIN引脚接收输入的时钟,将其变换为CPU及其外设所需要的工作时钟,工作时钟经过分频也能够通过引脚CLKOUT输出,供其他器件使用,如图1所示。

时钟发生器内有一个数字锁相环(Digital Phase Lock Loop,DPLL)和一个时钟模式寄存器(CLKMD)。

时钟模式寄存器用于控制时钟发生器的工作状态在时钟模式寄存器中的PLL ENABLE位控制PLL的两种工作模式。

1.旁路模式(BYPASS)如果PLL ENABLE=0,PLL工作于旁路模式,PLL对输入时钟信号进行分频,分频值由BYPASS DIV确定:如果BYPASS DIV=00,输出时钟信号的频率与输入信号的频率相同,即一分频。

如果BYPASS DIV=01,输出时钟信号的频率是输入信号频率一半,即二分频。

如果BYPASS DIV=1x,输出时钟信号的频率是输入信号频率1/4,即四分频。

2.锁定模式(LOCK)如果PLL ENABLE=1,PLL工作于锁定模式,输出的时钟频率由下面公式确定:输入时钟即可乘以或者除以一个系数来获得期望的输出频率,并且输出时钟相位与输入信号锁定。

为了降低功耗,时钟发生器也有Idle模式,可以通过关闭CLKGEN Idle模块,使时钟发生器工作在Idle模式。

1.2 CLKOUT引脚CPU时钟也可以通过一个时钟分频器提供CLKOUT信号,CLKOUT的频率由系统寄存器(SYSR)中的CLKDIV确定:如果CLKDIV=000b, CLKOUT的频率等于CPU时钟的频率。

DSP-TIMER

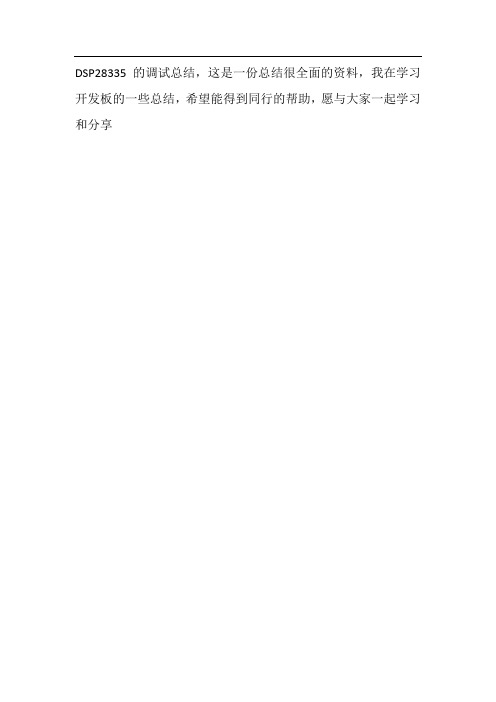

接着我们上一章(LED灯的点亮)的旅行!上一章我们使用了DSP的GPIO去点亮我们的LED灯,我们为了让人眼能够直接的感受LED的闪烁我们用到了一个延迟函数。

但是这样的延迟是让CPU空转,while内部的。

当然这样我们不好精确的计算出延迟了多长时间,幸好DSP内部用一个32bit的定时计数器(其实最简单的单片机里面都会有集成的8bit或者16bit定时计数器),我们可以使用它来精确的定时。

一般定时计数器有两个功能,一是定时:时钟源一般来源于DSP内部,当然也可以选择来自于外部。

二是计数:我们可以利用它的功能来计算外部脉冲在一段时间内到来的次数,所以叫做计数器(记录外部脉冲的次数)。

因为内部有一个计数的count,如果用作定时就是先输入一个数字,然后在来了一个时钟之后count自动减一。

如果用成计数就是在一个脉冲到来之后count自动加一!DSP6713内部有两个32bit的定时计数器(timer0和timer1),两个基本上是一样的。

我们先来看看定时器的内部构造:大家通过这样的原理框图就可以看出哪些bit影响哪些功能,比如CLKSRC bit 就是选择时钟源,为“0”选择TINP脚的和INVINP的异或信号作为时钟源,“1”选择的是CPU内部时钟源,为CPU主频的1/4.我们的DSP主频可以达到450MHz,那么我们的定时器使用的时钟就是112.5MHz。

GO bit就是使能定时器,让定时器开始计数,也就是定时开始信号。

HLD bit就是暂停和继续计数器控制位。

我们来看看Timer Control Register (CTL)寄存器的的实际用法我们这儿使用的是定时功能,所以我们就把红色标记的几个bit置成“1”,我们先分析一下这几个bit的意义。

一、设置CLKSRC bit位为“1”,这样就使用CPU内部的时钟源,CPU的主频的4分频。

二、设置CP bit位为“1”,这样我时钟源的占空比就为50%了。

DSP芯片原理及应用

《DSP芯片原理及应用》实验指导书唐山学院信息工程系DSP实验室2008年9月前言一.DSP原理及应用实验的任务数字信号处理实验是数字信号处理理论课程的一部分,它的任务是:1.通过实验进一步了解和掌握数字信号处理的基本理论及算法、数字信号处理的分析方法和设计方法。

2.学习和掌握数字信号处理的仿真和实现技术。

3.提高应用计算机的能力及水平。

二.实验设备DSP原理及应用实验所使用的设备由计算机、CPU板、语音单元、开关量输入输出单元、液晶显示单元、键盘单元、信号扩展单元、CPLD模块单元、模拟信号源、直流电源单元等组成。

其中计算机是CCS软件的运行环境,是程序编辑和调试的重要工具。

语音单元是语音输入和输出模块,主要完成语音信号的采集和回放。

开关量输入输出单元可以对DSP输入或输出开关量。

液晶显示单元可以对运行结果进行文字和图形的显示。

模拟信号源可以产生频率和幅度可调的正弦波、方波、三角波。

直流电源单元可以提供 3.3V、+5V、-12V和+12V 的直流电源。

装有CCS软件计算机与整个实验系统共同构成整个的DSP软、硬件开发环境。

所有的DSP芯片硬件的实验都是在这套实验装置上完成的。

三.对参加实验学生的要求1.阅读实验指导书,复习与实验有关的理论知识,明确实验目的。

2.按实验指导书要求进行程序设计。

3.在实验中注意观察,记录有关数据和图像,并由指导教师复查后才能结束实验。

4.实验后应断电,整理实验台,恢复到实验前的情况。

5.认真写实验报告,按规定格式做出图表、曲线、并分析实验结果。

字迹要清楚,画曲线要用坐标纸,结论要明确。

爱护实验设备,遵守实验室纪律。

目录第一章DSP原理及应用实验 (3)实验一常用指令实验 (3)实验二数据存储实验 (5)实验三I/O实验 (7)实验四定时器实验 (9)实验五外部中断实验 (11)实验六语音采集回放 (14)实验七语音信号的FFT分析 (18)实验八基于语音信号的IIR算法实验 (20)实验九语音信号的FIR算法实验 (23)第二章DSP CPU挂箱介绍 (26)第一节系统概述 (26)第二节54XB开发模板概述 (26)第一章DSP原理及应用实验实验一常用指令实验一.实验目的1.了解DSP开发系统的组成和结构;2.熟悉DSP开发系统的连接;3.熟悉DSP的开发界面,熟悉CCS的用户界面,学会CCS环境下程序编写、调试、编译、装载,学习如何使用观察窗口。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第二章CPU基本功能实现2.1电源模块的设计TMS320F2812芯片采用双供电模式,1.8V(主频135MHz)内核电压和3.3V 外围接口电压。

芯片的上电顺序是:先加载外围接口电压3.3V,当外围接口电压升至2.5V时开始加载芯片核电压1.8V,电压爬升小于10ms。

芯片下电的顺序是:先断掉外围接口电压3.3V,复位信号始终低有效,保持8us,接着使芯片核电压1.8V降为0。

实际系统的外接电源采用的是+5V开关电源,所以硬件电路中必须采用电源转换芯片组。

市场上电源转换芯片的种类丰富、厂家繁多,结果认真分析和比较,本系统中采用的电源转换芯片与DSP芯片为同一家厂家TI公司,芯片之间的兼容性好,可靠性高,性能参数指标具有一致性。

电源芯片TPS767D301为+5V外接电压转换+3.3V提供可能,采用可调电源芯片TPS767D301为F2812提供1.8V (主频135MHz)或1.9V(主频150MHz)的核电压。

TMS320F2812典型的上电掉电次序图如下图所示:图2-1TMS320F2812典型的上电掉电次序图如下图所示:在使用TPS767D301芯片时要注意上电次序的问题,要求对3.3V先上电,1.8V 后上电,最好使1、8V的上电时间晚一点,利用电阻电容做到一些延迟。

当TMS320F2812芯片在主频135MHz情况下工作时,芯片功耗为565mW,电流消耗仅在0.2A左右,存储器需要0.2A的电流,CPLD需要0.1A,可调电源转换芯片TPS767D301的最大输出电流为1A,完全可以满足模块需要。

由于TPS767D301芯片自身能够产生复位信号,此复位信号可直接供DSP芯片使用,从芯片的22引脚直接输出复位信号。

图2-2TPS767D3xx结构图此电源转化芯片组既可以满足系统工作时的电流要求,又可以解决DSP芯片上、下电顺序问题。

DSP芯片的电源部分设计如图所示。

2.2时钟信号设计TMS320F2812处理器片上带有基于PLL的时钟模块,为器件及各种外设提供时钟信号。

锁相环有4位倍频设置位,可以为处理器提供各种速度的时钟信号。

一般有两种方法为DSP芯片提供时钟电路。

(1)使用内部振荡器,即在DSP芯片的X1/XCLKIN和X2引脚之间连接一个石英晶体和两个电容,利用DSP芯片内部的振荡电路组成并联谐振电路,可产生与外加晶体同频率的时钟信号。

两个电容一般在10~30pF之间选择,它们可对时钟频率起到微调作用。

石英晶体的频率等于DSP芯片主频的80%×25%,即GPA1的频率=135MHz×80%×25%=27MHz,故选取30MHz的晶体,能够满足DSP芯片的工作要求,两个电容分别选取24pF。

(2)使用外部时钟源。

即采用封装好的晶体振荡器,将外部时钟源直接接到X1/XCLKIN引脚上,X2引脚悬空。

本报告中TMS320F2812处理器的时钟信号设计采用方法(1),其设计原理图如图2-2所示:图2-3DSP芯片的时钟信号设计TMS320F2812用30MHz外部晶体给F2812提供时钟,并使能F2812片上PLL 电路。

PLL倍频系数由PLL控制寄存器PLLCR的低4位控制,可有软件动态地修改,外部复位信号(XRS)将此4位控制位被清为0(CCS中的复位命令将不对此4位控制位作清0操作),F2812的CPU最高可工作在150MHz主频下,也即对30MHz 输入频率进行5倍频。

PLLCR控制位与倍频系数的关系如下表2-1所示:表2-1PLLCR控制位与倍频系数关系表位名称类型XRS重叠描述3:0DIV R/W0,0,0,0系统时钟输出=(x时钟输入*n)/2(n代表复位倍增因数)位值n系统时钟输出0000复位旁路X时钟输入/200011X时钟输入/200102X时钟输入00113X时钟输入*1.501004X时钟输入*201015X时钟输入*2.501106X时钟输入*301117X时钟输入*3.510008X时钟输入*410019X时钟输入*4.5101010X时钟输入*5101111保留位110012保留位110113保留位111014保留位111115保留位15:4保留位R=00:0时钟电路如图7所示,利用DSP内部的PLL锁相环,3OMHz频率输入,利用PLL 倍频至150M。

这里设置PLLCR的3,2,l,O位为1010,利用公式时钟输入CLKIN=(OSCCLK*10)/2,可验证得到CLKIN=150MHZ,恰好等于F2812芯片的最高主频。

在设计时钟电路和设置时钟倍频时,要注意切忌使倍频系数与外部时钟源频率的乘积大于F2812的最高主频150MHZ,否则芯片将不能正常工作。

2.3JTAG边界扫描接口的设计JTAG标准是1990年由国际电气和电子工程师协会(IEEE)公布的1149.1标准,是针对现代大规模集成电路测试、检验困难而提出的基于边界扫描机制和标准测试存取的国际标准。

边界扫描就是对含有JTAG逻辑的集成电路芯片边界引脚通过软件完全控制和扫描观察其状态的方法,这种能力使的高密度的大规模集成芯片在线测试成为可能。

其原理是在芯片的输入/输出引脚内部安排存储单元,用来保存引脚状态,并在内部将这些存储单元连接在一起,通过一个输入引脚TDI引入和一个输出引脚TDO引出。

正常情况下,这些存储单元不工作,在测试模式下,存储单元存储输入/输出状态,并在测试存储口(TAP)的控制下输入/输出。

此外,F2812和支持实时运行模式,在处理器正在运行,执行代码并且处理中断时,可修改存储器内容、外设、和寄存器位置。

用户也可以通过非时间关键代码进行单步操作,同时可在没有干扰的情况下启用即将被处理的时间关键中断。

F2812在CPU的硬件内执行实时模式。

这是F2812所特有的功能,无需软件监控。

此外,还提供了特别分析硬件,以使用户能够设定硬件断点或者数据/地址观察点并当一个匹配发生时生成不同的用户可选中断事件。

借助于JTAG的简化的流程为先固定器件到电路板上,从而大大加快工程进度,实现对DSP芯片内部所有部件的编程。

JTAG边界扫瞄和仿真接口包括TCK:测试时钟;TDI/TDO:测试数据输入和输出;TMS:测试模式选择;TRST:测试接口复位;EMU[1:0]仿真引脚;TCKRET:复制了的TCK信号。

一个完整的DSP应用系统必须具有仿真器的标准接口,通过这个接口,用户可以通过PC调试、下载应用软件到指定的应用板。

TI DSP芯片提供片上仿真支持,使CCS能控制程序的运行并实时监视程序的活动。

仿真器提供与主机通信的JTAG 接口,主机与目标DSP通信是通过JTAG接口来完成的,这种连接方式对DSP目标系统的实时性能没有太大的影响,片上仿真硬件提供以下功能:1、运行、停止或复位DSP芯片;2、将代码和数据加载到DSP芯片中;3、检查硬件指令或数据相关的断点;4、各种计算功能,包括精确到指令周期的剖切(Profile)功能;5、提供主机和目标系统间的实时数据交换。

一般情况下,在系统成功应用之前,需要大量的调试工作,以确保板卡和软件程序正常工作,为了方便软件调试,JTAG接口尤为重要,只有JTAG接口设置好,才能通过仿真器被CCS识别,从而进行大量的仿真测试实验。

图8是F2812的JTAG 接口电路。

TI公司为DSP芯片F2812设置了符合国际标准的JTAG逻辑测试口。

仿真电缆和JTAG测试口的连接通过一个14针的仿真头来实现,仿真头上的信号连接关系图所示。

其中TDI_DSP和TDO_DSP是测试数据的输入和输出,TMS_DSP是测试模式的选择,TCK_DSP和TRST_DSP是测试时钟的输出和返回。

考虑到JTAG下载口的抗干扰性,在与DSP相连接的端口需要采用上拉设计。

图2-4JTAG接口电路2.4DSP外围电路的设计DSP芯片的最小系统设计是保证DSP芯片正常工作,完成基本的运算处理功能。

但生产厂商为DSP芯片配置了大量的片内外围设备,给用户提供了丰富的硬件资源和系统操作能力。

F2812芯片的片内外围设备主要包括片内A/D、异步串行口、同步串行口、3个32位的CPU定时器、2个事件管理器、多通道缓冲串行口等。

DSP外围电路的设计就是完成F2812芯片的片内外围设备的连接和通信,使其为用户提供方便。

随着数据采样率的提高,数字信号处理方法的复杂化及运行实时库软件的使用,使得数据量和程序代码大大增加,DSP芯片内部的片内RAM无法满足实际需要,所以必须考虑外部存储器的扩展问题。

F2812芯片内部配置了18Kx16bits的单周期访问RAM,但它无法满足实时数据采集和存储要求,所以采用CYPRESS公司的CY7C1041BV33芯片扩展F2812芯片的外部存储器。

F2812芯片的外部存储器扩展接口XINTF是一种非多路选通的异步总线,它的最大扩展能力为512K×16bits,考虑到硬件成本太高,最后外部存储器扩展到256K×16bits。

CYPRESS公司的CY7C1041BV33芯片是一款高性能CMOS静态RAM,工作电压+3.3V,最快访问时间是12ns,它的最大容量为256K×16bits,具有的基本输入/输出信号有:地址总线(是输入信号)、数据总线(是双向传输信号)、片选信号(CE#,输入信号)、读信号(OE#,是输入信号)、写信号(WE#,是输出信号)。

由于采用统一寻址方式,它既可作为程序存储器,也可作为数据存储器。

外扩RAM的连接关系如图所示,F2812芯片的D0-D15芯片与CY7C1041BV33芯片的D0-D15引脚相连,A0-A15与A0-A15相连,F2812片上的XINTF区域2的片选信号与CE#输入信号相连,2812片上的读有效信号和写有效信号分别与片上的OE#,WE#相连,另外使能信号LB#,UB#接地,保证地电平有效,这样既完成的RAM 的外扩。

F2812芯片具有5个外部存储器扩展接口XZCS0AND0#,XZCS0AND1#,XZCS1#,XZCS2#,XZCS6AND7#,外扩RAM挂接在F2812芯片的外部存储扩展接口XZCS2#上,地址空间为0x080000~0x0BFFFF,共256K×16bits。

图2-5外扩RAM的连接关系图TMS320F2812内部具有128K*16位的Flash空间(4个8K*16位和6个16K*16位的空间),如果在DSP中所编译的代码段高于Flash的存储容量,则就需要外扩Flash空间来稳定的实现其功能。

外扩Flash的原理与外扩RAM的原理一样,设计的时候通过XINTF接口来外扩FLASH,外扩Flash芯片中的片选信号F_CS和DSP的XZCS2#引脚相连,使用的是XINTF2区,该空间的起始地址为0X80000,长度为512K字,实际使用了128K字。