语音芯片TLV320AIC23使用

ICETEK-AIC23使用说明书

CLKOUT CLKIN 0 0

CLKIN CLKOUT

时钟输入分割 时钟输出分割

0 = MCLK 0 = MCLK

ICETEK-AIC23 背板使用说明书

第一部分:TLV320AIC23 芯片介绍

TLV320AIC23 介绍: TLV320AIC23 是一个高性能的多媒体数字语音编解码器,它的内部 ADC 和 DAC 转换模块带有 完整的数字滤波器。 (digital interpolation filters)数据传输宽度可以是 16 位,20 位,24 位和 32 位,采样 频率范围支持从 8khz 到 96khz。在 ADC 采集达到 96khz 时噪音为 90-dBA,能够高保真的保存音频信号。 在 DAC 转换达到 96khz 时噪音为 100-Dba,能够高品质的数字回放音频,在回放时仅仅减少 23 mW。 TLV320AIC23 详细指标:

DEEMP[1:0]:De-emphasis 控制 00 = 禁止 01 = 32 kHz 10 = 44.1 kHz 11 = 48 Khz ADCHP:ADC 滤波器 0 = 禁止 1 = 激活 X:保留

启动控制 (Address: 0000110)

BIT Function Default D8 X 0 D7 OFF 0 D6 CLK 0 D5 OSC 0 D4 OUT 0 D3 DAC 0 D2 ADC 1 D1 MIC 1 D0 LINE 1

LRS:左右耳机通道控制 LZC:0 点检查 0 = Off

0 = 禁止 1 = 激活 1 = On

TLV320AIC23 CODEC

用.

I 2 两线 串行传输方式 ,D N为输 入串行 数 C是 SI 据 ,C K为 串行 时钟 , SL 具体应用可参考手册 。 222 寄 存器 设 置 ..

《声 术22第0总 2期 电 技 )0 1 第0 0年 期 8

I 2 C和 S I P 总线 兼 容控 制 接 口 , 能使 A C 3编码 解 码 I2 器 与其 它 微 处 理 器 共 同使 用 。 目前 已有 T V 2 A— L 30 I2 C 3的开 发 套件 产 品 , 与 T 4系 列 D P的套 件 可 I5 S 无 缝 连 接 开 发 , 而 且 在 50D P 的 套 件 中 , 59 S T V30 I2 L 2 AC 3已被 集 成 在 板 上 作 为 音 频 编 解 码 器 使 用 ,可 以看 出 该 器 件 会 得 到 广 泛 应 用 。

T V 2AC 3 内部有 1 L 3 0 I2 1个 可 编 程 控 制 寄 存 器 , 过 不 同设 置 , 以 改 变芯 片 的工 作 状 态 , 采 通 可 如 样 率 、 右声 道 音量 等 。 左 这些 寄 存器 都 是 通过 A C 3 I2 的控 制接 口来 编程 的 。控 制 接 口又 分 为 S I三线 ) P( 和 I 两 线 ) 口 , 部 引 脚 MO E置 0 I决 定 采 2 C( 接 外 D /

维普资讯

T V3 0 C2 L 2 AI 3 CODEC 与

D P的接 口应 用 S

计 丹 ,黄光 明 。雷 环 利

・技 应 用

f '

O ∞ =

( 武汉华 中师范大学物理 系,湖北 武汉 4 0 7 ) 30 9

l 引 言

TLV320AIC23芯片的介绍与应用实验(ppt 84页)

第5章 立体声芯片TLV320AIC23的应用 图5-5 图形属性对话框

第5章 立体声芯片TLV320AIC23的应用 图5-6 图形观察窗口中的左、右声道声音波形

第5章 立体声芯片TLV320AIC23的应用

5.2.5 参考程序清单

1. 主程序

.mmregs

.def _c_int00

;定义符号_c_int00为主程序入口

第5章 立体声芯片TLV320AIC23的应用

第5章 立体声芯片TLV320AIC23的 应用

5.1 TLV320AIC23芯片介绍

5.2 TLV320AIC23应用实验

第5章 立体声芯片TLV320AIC23的应用

5.1 TLV320AIC23芯片介绍

5.1.1 TLV320AIC23特点介绍 TLV320AIC23是TI公司生产的具有高度完整模拟功能

第5章 立体声芯片TLV320AIC23的应用 ■软件控制通过TI McBSP支持多种串行通信协议。 ◇兼容2线和SPI串行通信协议; ◇能直接和TI McBSPs相连。

第5章 立体声芯片TLV320AIC23的应用 ■音频数据输入/输出是可编程音频接口,兼容TI McBSP。 ◇I2C兼容协议只需要一个McBSP为A/D和D/A进 行通信; ◇标准的I2C,高位或低位数据填充传输; ◇16/20/24/32位数据长度。

.ref i2c_disable

;引用外部符号i2c_disable

.ref i2c_write

;引用外部符号i2c_write为总线写

.ref i2c_read

;引用外部符号i2c_read为总线读

.ref clkmd_init

;引用外部符号clkmd_init为时钟模块初

音频信号处理

DIN DOUT

J6 J7 J8

3.AIC23的工作方式

I2C 设置AIC23

SCL SDA TMS320VC5509 CLKR0 CLKX0 FSX0 FSR0 DX0 DR0 DIN DOUT SCLK SDIN MODE CS TLV320AIC23 BCLK LRCOUT J5 GND

c=1; g=0.5; M=1000; b=[c]; a=[1,zeros(1,M-1),-g]; [x,fs]=wavread('S5A.wav'); y=filter(b,a,x); wavplay(y,fs)

DSP系统的实现

C 语言编程 迭代算法 数据缓冲区

DSP系统的实现

实时数据

AIC23_Mixer() 声音信号处理子程序

while (!ReadMask(pMCBSP0 -> spcr2, SPCR2_XRDY)); // 等待McBSP0准备好

数据=Read(pMCBSP0->ddr1);// 读取左声道的数据 数据=Read(pMCBSP0->ddr2);//读取右声道的数据

DSP系统的实现

.gel文件

menuitem "Echo Parameters" slider Length(1,5,1,1,amplitudeparameter) /*incr by 1,up to 20*/ {length = amplitudeparameter; /*vary buffer size*/} dialog SetEcho(nParam1"1 Feedforward;2 Backforward;3 no):") {flag=nParam1;}

g=1 缓冲数据的编程方法

音频处理芯片AIC23完整中文资料全

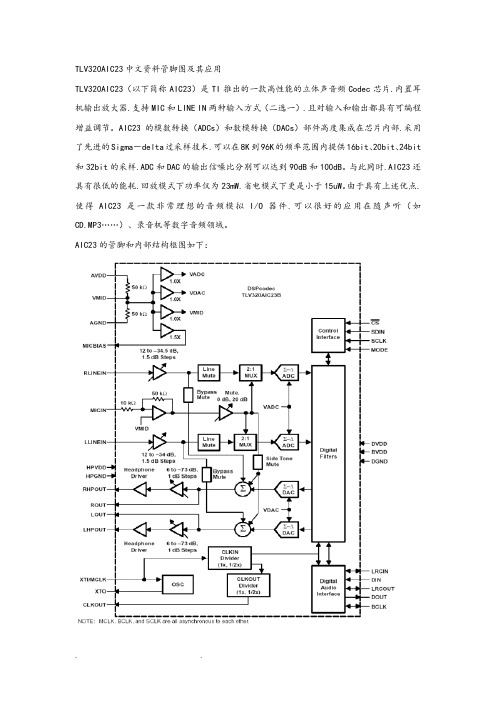

TLV320AIC23中文资料管脚图及其应用TLV320AIC23(以下简称AIC23)是TI推出的一款高性能的立体声音频Codec芯片.内置耳机输出放大器.支持MIC和LINE IN两种输入方式(二选一).且对输入和输出都具有可编程增益调节。

AIC23的模数转换(ADCs)和数模转换(DACs)部件高度集成在芯片内部.采用了先进的Sigma-delta过采样技术.可以在8K到96K的频率范围内提供16bit、20bit、24bit 和32bit的采样.ADC和DAC的输出信噪比分别可以达到90dB和100dB。

与此同时.AIC23还具有很低的能耗.回放模式下功率仅为23mW.省电模式下更是小于15uW。

由于具有上述优点.使得AIC23是一款非常理想的音频模拟I/O器件.可以很好的应用在随声听(如CD.MP3……)、录音机等数字音频领域。

AIC23的管脚和内部结构框图如下:从上图可以看出.AIC23主要的外围接口分为以下几个部分:一.数字音频接口:主要管脚为BCLK-数字音频接口时钟信号(bit时钟).当AIC23为从模式时(通常情况).该时钟由DSP 产生;AIC23为主模式时.该时钟由AIC23产生;LRCIN-数字音频接口DAC方向的帧信号(I2S模式下word时钟)LRCOUT-数字音频接口ADC方向的帧信号DIN-数字音频接口DAC方向的数据输入DOUT-数字音频接口ADC方向的数据输出这部分可以和DSP的McBSP(Multi-channel buffered serial port.多通道缓存串口)无缝连接.唯一要注意的地方是McBSP的接收时钟和AIC23的BCLK都由McBSP的发送时钟提供.连接示意图如下:二.麦克风输入接口:主要管脚为MICBIAS-提供麦克风偏压.通常是3/4 AVDDMICIN-麦克风输入.由AIC结构框图可以看出放大器默认是5倍增益连接示意图如下:三. LINE IN输入接口:主要管脚为LLINEIN-左声道LINE IN输入RLINEIN-右声道LINE IN输入连接示意图如下:四.耳机输出接口:主要管脚为LHPOUT-左声道耳机放大输出RHPOUT-右声道耳机放大输出LOUT-左声道输出ROUT-右声道输出从框图可以看出.LOUT和ROUT没有经过内部放大器.所以设计中常用LHPOUT和RHPOUT.连接示意图如下:五.配置接口:主要管脚为SDIN-配置数据输入SCLK-配置时钟DSP通过该部分配置AIC23的内部寄存器.每个word的前7bit为寄存器地址.后9bit为寄存器内容。

音频编解码器TLV320AIC23及其与DSP接口设计

DSP技术及其应用

· 265 ·

音频编解码器TLV320AlC23及其与DSP接口设计

上海大学 丁 祥 余小清 香港理工大学 万旺根

摘 要 介绍Tl公司的立体声音频CODEC TI。V320AIC23芯片的功能、内部结构、引脚排列; 给出通过DSP串行口配置它所特有的内部控制寄存器的方法,使得设计更加灵活;可以实现和DSP 无缝接口;从硬件和软件两个方面,结合该芯片串行口工作时序图,讨论与TMs320Vc5409 DSP的 接口设计。

2 TMS320VC5409 FIXEI)_P()INT DIGITAI。 SIGNAI。 PR(jCESS()R.Texas Instruments.2000

3 TMS320C54X DSP Reference Set Volume 5:Enhanced Pe “Dherals. Texas Instruments,1 999

VC5409 BCLKXl

AJC23 SCLK

MCLK

BFSXl

e§

MODE

BDXl

SDIN

BVDD

V

丁 BCLKX0

BCLK

BCLKR0

DVDD LINEIN

BFSXO BFSR0

BDX0

LRCIN RLINEIN

!竺唧嬲

DIN

LHP石面千

BDR0

DOUT

RHPOUT

MICIN

MICBIAS

图3 AIC23与VC5409接口原理图

2.2串行口工作时序

图4是对AIC23寄存器编程时的时序图。这16 位控制字中,B[15..9]为寄存器的地址,B[8..o]为 要写入寄存器的数据。在系统初始化时需要对寄存 器进行编程,这样CODEC才能正常工作。

TLV320AIC23

DSP/BIOS Driver Developer’s Kit(DDK)是TI为简化驱动程序开发为TMS320系列DSP及其EVM板等提供的 驱动程序开发套件。该套件为TMS320系列各种外围器件提供完整的标准化驱动程序模型,使得驱动程序可以很方 便地移植到其他应用中,大大提高驱动程序开发的效率。DDK是对每种TMS320系列DSP都提供的芯片支持库(Chip Support Library—CSL)的补充,CSL提供对外围器件寄存器配置及初始化等的低级控制,DDK完全通过CSL来对 外围器件进行控制。简单地说。DDK建立在CSL上层.所以用DDK来开发驱动程序将更为快捷且可移植性更好。

TLV320AIC23

TI公司推出的一款高性能立体声音频编 解码器

01 简介

目录

02 应用

TLV320AIC23是TI公司推出的一款高性能立体声音频编解码器,内置耳机输出放大器,支持mic和line in二 选一的输入方式。输入和输出都具有可编程的增益调节功能。

简介

1TLV320AIC23的模/数转换器(ADC)和数/模转换器(DAC)集成在芯片内部.采用先进的Σ一△过采样技 术.可以在8kHz至96kHz的采样率下提供16bit、20bit、24bit和32bit的采样数据。ADC和DAC的输出信噪比分 别可达90dB和100dB。同时。TLV320AIC23还具有很低的功耗(回放模式为23mW。节电模式为15μw)。上述优点使 得TLV320AIC23成为一款非常理想的音频编解码器,与TI的DSP系列相配合更是相得益彰。

DDK为开发驱动程序定义了标准模型和一系列的API。为简化程序设计。标准模型又被分为二个层次.其中高 层称为Class driver,低层称为Mini—driver。Class drivei与器件相对独立.完成诸如缓冲区管理和请求同 步等功能.同时扮演着与API和Mini—driver二者接口的角色。Mini—driver完成特定的器件初始化和控制功 能.它符合IOM(I/O Mini—driver)的接口标准。DDK的这种分层结构使得驱动开发人员仅需了解单一的Mini— driver API就可以完成整体外围器件的驱动设计,而且这一过程比设计整个驱动程序要简单得多,因为Class driver控制了缓冲区管理和同步等。DDK提供3种Class driver.分别为SIO/DIO、PIP/PIO和GIO,它们都可以 和任何Mini—driver结合使用。

TLV320AIC23BIRHDG4资料

TLV320AIC23B

Stereo Audio CODEC, 8Ć to 96ĆkHz, With Integrated Headphone Amplifier

Data Manual

February 2004

Digital Audio Pro Nhomakorabeaucts

SLWS106H

元器件交易网

Contents

Section 1 Title Page 1−1 1−1 1−3 1−4 1−5 1−5 2−1 2−1 2−1 2−2 2−2 2−3 2−3 2−4 2−4 2−4 2−4 2−5 2−5 2−6 2−7 2−7 3−1 3−1 3−1 3−1 3−2 3−5 3−5 3−6 3−6 3−6 3−7 3−7 3−7 3−7 Introduction . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.2 Functional Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.3 Terminal Assignments . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.4 Ordering Information . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1.5 Terminal Functions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . Specifications . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.1 Absolute Maximum Ratings Over Operating Free-Air Temperature Range . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.2 Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . 2.3 Electrical Characteristics Over Recommended Operating Conditions . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.3.1 ADC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.3.2 DAC . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.3.3 Analog Line Input to Line Output (Bypass) . . . . . . . . . . . . . 2.3.4 Stereo Headphone Output . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.3.5 Analog Reference Levels . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.3.6 Digital I/O . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.3.7 Supply Current . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.4 Digital-Interface Timing . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2.4.1 Audio Interface (Master Mode) . . . . . . . . . . . . . . . . . . . . . . . 2.4.2 Audio Interface (Slave-Mode) . . . . . . . . . . . . . . . . . . . . . . . . 2.4.3 Three-Wire Control Interface (SDIN) . . . . . . . . . . . . . . . . . . 2.4.4 Two-Wire Control Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . How to Use the TLV320AIC23B . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.1 Control Interfaces . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.1.1 SPI . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.1.2 2-Wire . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.1.3 Register Map . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2 Analog Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2.1 Line Inputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2.2 Microphone Input . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2.3 Line Outputs . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2.4 Headphone Output . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2.5 Analog Bypass Mode . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.2.6 Sidetone Insertion . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.3 Digital Audio Interface . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 3.3.1 Digital Audio-Interface Modes . . . . . . . . . . . . . . . . . . . . . . . .

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

左声道耳机音量控制

• LRS:L/R Simutaneout 左右声道同时音量控 制

• LZC:Left Zero Cross 左声道过零检测 • LHV:Left Headphone Volume

数字通道控制

• DACM:DAC静音 • DEEMP[1:0]:去加重控制

– 00:禁止 – 01:32kHz – 10:44.1kHz – 11:48kHz

• ADCHP:ADC高通滤波控制

功耗控制

• OFF:器件电源,0:ON;1:OFF • CLK:时钟 • OSC:振荡器 • OUT:输出 • DAC: • ADC: • MIC: • LINE:

采样率控制(1)

• CLKOUT输出时钟分频控制 • CLKIN输入时钟分频控制 • SR3~0:采样率控制 • BOSR:基本过采样率 • USB/NORMAL:时钟选择

采样率控制(2)USB模式

采用率控制寄存器应为: 0001 0000 0001 1100=0x101C(96kHz) 0001 0000 0000 0000=0x1000(48kHz)

制数据位)

• 数据接口(5根线):BCLK、DIN、DOUT、 LRCIN、LRCOUT

• 模拟接口

– 线入、线出 – MIC入、耳机出

控制接口时序

语音芯片TLV320AIC23使用.pdf

控制寄存器

左声道线入音量控制

• LRS:L/R Simutaneout 左右声道同时音量控 制

• LIM:Left In Mute • LIV:Left Input Volume

– I2CMDR=0x0620 //I2C处于工作状态

– I2CCLKL=I2CCLKH=45 //SCL时钟 =144/(14*100)=100kHz

I2CMDR

• 0x0000 0x4620 • BC:Bit Count 8bit per data byte • 0000 0110 0010 0000 • MST=1:主模式 • TRX=1: I2C模块发送数据 • IRS=1: I2C reset, 模块使能 • FREE=1: 遇到断点模块不停止

语音芯片TLV320AIC23使用

2012.12.15

硬件实物(正面)

AIC23

DSP PGE封装

CLKOUT

SDRAM LED驱动器

与门

语音芯片AIC23 0

主要信息

• 2路AD • 2路DA • 模拟输入增益调

整范围12~34.5dB

• 模拟输出调整范 围6~-73dB

• 自带参考源

C5509管脚说明-数据接口

• 0000 1110 0101 0011:

• D6=1(MS, AIC23为主模式,时钟、帧同步由AIC23驱动) • D5=0(LRSWAP, DAC左右声道交替被禁止) • D4=0(LRP, DAC左右声道相位,USB模式:MSB出现在LRCIN上升沿后

的第一个BCLK的上升沿) • D3D2=00(IWL10,输入数据宽度为16bit) • D1D0=11(FOR10,数据格式:DSP,帧同步后跟2个数据字)

个字的数据) • AIC23为主模式,数据为DSP模式,数据长度16位

– Uint16 digital_audio_inteface_format[2]={0x0e,0x53};

数字音频接口格式(2)

• Uint16 digital_audio_inteface_format[2]={0x0e,0x53};

数字音频接口格式(1)

• D6:MS=主(1)、从(0)模式 • D5:LRSWAP=0(DAC左右声道互换禁止) • D4:LRP=1(MSB出现在LRCIN上升沿后的第2个时钟上升沿

上) • D3~2:IWL=输入位宽:00(16位) • D1~0:FOR=11(数据格式:DSP模式,帧同步脉冲后跟随2

– 111 1111: +6dB – 111 1001: 0dB(缺省) – 000 0000: -73.0dB – 步长:1dB

模拟通道控制

• STA:SideTone Atten侧音衰减 • STE:侧音衰减使能 • DAC:DAC选择 • BYP:ByPass • INSEL:输入选择(0:线入) • MICM:麦克风静音 • MICB:麦克风前置放大使能

IIC部分说明

• 参考文件:TMS320C55x DSP IIC Module Reference Guide (Rev. B)

• IIC初始化过程

– I2CMDR=0

//I2C处于复位状态

– I2CSAR=0x1A //I2C设备的地址为0x1A

– 调用结构体I2Cinit设置参数 – I2CPCS=13 //前置分频比为14

I2CSAR

• I2C Slave Address Register • AIC23芯片的地址为:0x001A

I2C设置结构体(不起作用)

• typedef struct {

•

•

Uint16 addrmode;

address mode */

/* 7 or 10 bit

•

Uint16 ownaddr;

• DSP的McBSP1接口(接AIC23数据接口) • 连接关系

– S10:CLKR – S11:DR – S12:FSR – S13:DX – S14:CLKX – S15:FSX

硬件部分-其他接口

• 时钟12MHz • 控制接口IIC:SDA、SCL(MODE=0)

– 地址:001 1010 – 只能写:R/W=0 – 格式:地址+0+B15~B9(控制地址位)+B8~B0(控

master */

/* don't care if

• Uint16 sysinclock; */

/* clkout value (Mhz)

•

Uint16 rate;

10 and 400*/

/* a number between

•

Uint16 bitbyte;

/* number of

bits/byte to be received or transmitted */

•