低功耗 MCU TR4P153BT

STMCU低功耗产品系列详解

Clock Controller

Debug ModuleSWIM

Up to 41 I/Os

PVD

Xtal 32,768 KHz

DMA

12 bit DAC

2xComparators

Boot ROM

LCD driverUp to 4 x 28

1x16 bit TimerAdv Control3 Channels

超低功耗微控制器平台的关键词

低功耗的承诺从STM8L到STM32L完整的低功耗微控制器平台采用最新、超低漏电流的工艺极大的改善包括动态和静态的功耗高效率的承诺由于采用最新的架构,性能/功耗比达到新高运行模式功耗低至:150 µA/MHz在低功耗模式下,仅需 350nA,SRAM和寄存器数据还可以保留优化的产品分布采用通用单片机从8位到32位全覆盖的策略针对特殊的应用,提供片上集成的安全特性最佳的性价比

64 pins LQFP(10x10)

STM8L152M84 KB RAM

STM8L151M84 KB RAM

80 pins LQFP(14x14)

STM8L101 8K 结构框图

SPI

USART

I²C

2x16 bit Timer2 Channels

1x8-bit Timer

Ind. Wd with 38KHz int.

所有都包含:

USART, SPI, I2C

看门狗(STM8L15x 具有双看门狗)

多通道16-bit 定时器

内置 16 MHz 和 38 kHz RC 振荡器

复位电路(上电复位,掉电复位)

Up to 8 KB Flash

STM8L101

Up to 1.5 KB SRAM

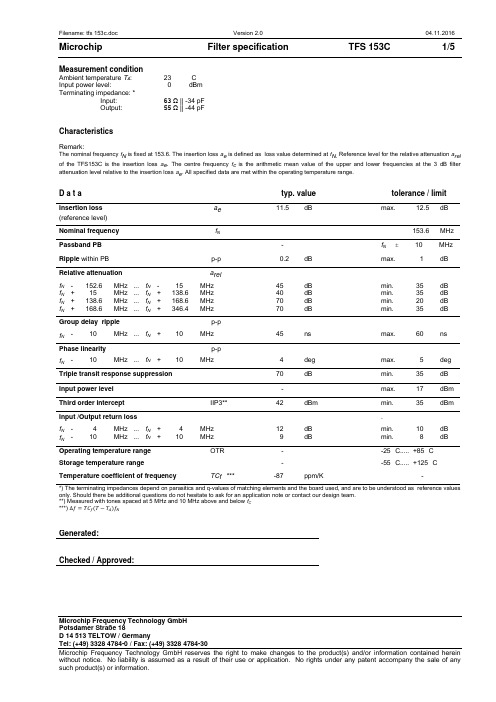

微芯片频率技术 TFS 153C 滤波器规格说明书

Measurement conditionAmbient temperature T A: 23 °CInput power level: 0 dBmTerminating impedance: *Input: 63 Ω || -34 pFOutput: 55 Ω || -44 pFCharacteristicsRemark:The nominal frequency f N is fixed at 153.6. The insertion loss a e is defined as loss value determined at f N. Reference level for the relative attenuation a rel of the TFS153C is the insertion loss a e. The centre frequency f c is the arithmetic mean value of the upper and lower frequencies at the 3 dB filter attenuation level relative to the insertion loss a e. All specified data are met within the operating temperature range.D a t a typ. value tolerance / limitInsertion loss a e11.5 dB max. 12.5 dB (reference level)Nominal frequency f N 153.6 MHz Passband PB - f N 10 MHz Ripple within PB p-p 0.2 dB max. 1 dB Relative attenuation a relf N- 152.6 MHz ... f N- 15 MHz 45 dB min. 35 dBf N+ 15 MHz ... f N+ 138.6 MHz 40 dB min. 35 dBf N+ 138.6 MHz ... f N+ 168.6 MHz 70 dB min. 20 dBf N+ 168.6 MHz ... f N+ 346.4 MHz 70 dB min. 35 dB Group delay ripple p-pf N- 10 MHz ... f N+ 10 MHz 45 ns max. 60 ns Phase linearity p-pf N- 10 MHz ... f N+ 10 MHz 4 deg max. 5 deg Triple transit response suppression 70 dB min. 35 dB Input power level - max. 17 dBm Third order intercept IIP3** 42 dBm min. 35 dBm Input /Output return loss .f N- 4 MHz ... f N+ 4 MHz 12 dB min. 10 dBf N- 10 MHz ... f N+ 10 MHz 9 dB min. 8 dB Operating temperature range OTR - -25 °C..... +85 °C Storage temperature range - -55 °C..... +125 °C Temperature coefficient of frequency TC f *** -87 ppm/K -*) The terminating impedances depend on parasitics and q-values of matching elements and the board used, and are to be understood as reference values only. Should there be additional questions do not hesitate to ask for an application note or contact our design team.**) Measured with tones spaced at 5 MHz and 10 MHz above and below f C***) ∆f=TC f(T−T A)f NGenerated:Checked / Approved:Microchip Frequency Technology GmbHPotsdamer Straße 18Microchip Frequency Technology GmbH Potsdamer Straße 18 Filter characteristicConstruction and pin connection(All dimensions in mm)50 Ω Test circuitL2Output 50 OhmInput L11,2,3,4,6,7,8,9,10,121 Ground2 Ground3 Ground4 Ground5 Output6 Ground7 Ground8 Ground9 Ground 10 Ground 11 Input 12 GroundDate code: Year + week H 2016 J 2017 K 2018 ...Microchip Frequency Technology GmbH Potsdamer Straße 18 Stability characteristics, reliabilityAfter the following tests the filter shall meet the whole specification:1. Shock: 500 g, 1 ms, half sine wave, 3 shocks each plane; DIN IEC 60068 T2 - 272. Vibration: 10 Hz to 2000 Hz, 0.35 mm or 5 g respectively, 1 octave per min, 10 cycles perplane, 3 planes; DIN IEC 60068 T2 - 63. Change of temperature: -55 °C to 125 °C / 15 min. each / 100 cycles DIN IEC 60068 part 2 – 14 Test N4. Resistance tosolder heat (reflow): reflow possible: three times max.; for temperature conditions refer to the attached "Air reflow temperature conditions" on page 4;5. SAW devices are Electrostatic Discharge (ESD) sensitive devices.This filter is RoHS compliant (2011/65/EU)PackingTape & Reel: IEC 286 – 3, with exception of value for N and minimum bending radius; tape type II, embossed carrier tape with top cover tape on the upper side; max. pieces of filters per reel:1700reel of empty components at start:min. 300 mm reel of empty components at start including leader: min. 500 mm trailer:min. 300 mmGDoWC tFEGD1P 2P 1P o BoAoP ull Off DirectionP IN Marker T ypDate Code K o tThe minimum bending radius is 45 mm.Tape (all dimensions in mm) W : 24.00 +0.30/-0.10 Po : 4.00 ±0.1 Do : 1.50 +0.1/0 E : 1.75 ±0.10 F : 11.50 ±0.10 G(min) : 0.60 P2 : 2.00 ±0.1 P1 : 12.00 ±0.1 D1(min) : 1.50 Ao : 7.00 ±0.10 Bo : 13.80 ±0.10 Ct : 21.00 ±0.1 Ko: 2.10 ±0.10 t : 0.30 ±0.05Reel (all dimensions in mm) A : 330 or 180 W1 : 24.4 +2/-0 W2(max) : 30.40 N(min) : 60.00 C : 13.0 +0.5/-0.2Microchip Frequency Technology GmbH Potsdamer Straße 18 Air reflow temperature conditionsConditionsExposureAverage ramp-up rate (30 °C to 217 °C) less than 3 °C / second> 100 °C between 300 and 600 seconds > 150 °C between 240 and 500 seconds > 217 °Cbetween 30 and 150 seconds Peak temperaturemax. 260 °CTime within 5 °C of actual peak temperature between 10 and 30 seconds Cool-down rate (Peak to 50 °C)less than 6 °C / secondTime from 30 °C to Peak temperatureno greater than 300 secondsTemperature / °CTime / smax. 260 °C217 °C10 ... 30 s 30 ... 150 smax. 300 sChip-mount air reflow profileHistoryVersion Reason of Changes Name Date1.0 - generation of specification according to customer requirements Roizengaft 02.02.2004 1.1 - generated filter specification Chilla 15.06.2004- added termination impedances- added typical values- changed insertion loss- changed group delay ripple- changed phase linearity- changed input/output return loss- changed IP3 description- changed storage temperature range- deleted description for power level- added filter characteristic- changed construction and pin connection- added test circuit- changed packing1.2 - added temperature coefficient of frequency Chilla 23.09.2005 1.3 - added IIP3 Chilla 27.02.20091.4 - changed temperature coefficient Chilla 06.04.20092.0 - Change tape & reel dimensions Bonnen 04.11.2016- Update header and footer sections- Update data section- Update storage temperature range- Update stability characteristics, reliabilityMicrochip Frequency Technology GmbHPotsdamer Straße 18。

MSP430系列16位超低功耗单片机原理与实践

MSP430单片机的中断系统 GIE、CPUOFF、

中断请求

中断响应过程

将当前指令执行完 PUSH PC PUSH SR 如果有多个中断 发生,选择最高 优先级的中断 如果是单源中断 则清除中断标志, 否则中断标志保 持置位状态

OSCOFF、 SCG1、C、N、 V、Z清零, SCG0不变

中断向量地址中 的内容装入PC, 开始执行中断服 务程序 POP SR

概述

单片微型计算机 单片机的概念 单片机的特点 单片机的应用

MSP430系列单片机 MSP430系列单片机的特点 MSP430系列单片机命名规则 MSP430系列单片机选型

单片微型计算机:单片机的概念

微处理器的发展一方面是朝着面向数据运算、 信息处理等功能的系统机方向发展。系统机 以速度快、功能强、存储量大、软件丰富、 输入/输出设备齐全为主要特点,采用高级语 言编程,适用于数据运算、文字信息处理、 人工智能、网络通信等场合。 另一方面,在一些应用领域中,如智能化仪 器仪表、电讯设备、自动控制设备、汽车乃 至家用电器等,要求的运算、控制功能相对

MSP430 Roadmap

MSP430X11X系列

MSP430X12X系列

MSP430X13X系列

MSP430X14X系列

MSP430F15X/F16(1)X 系列

MSP430F15X/F16(1)X 系列

MSP430X41X系列

MSP430F43X系列

MSP430F44X系列

函数类型 函数名(形式参数表) 形式参数说明 { 局部变量定义 函数体语句 } [ 存储变量类型 ] interrupt [ 中断矢量变量 ] 函数类型 函数名(形式参数表) 形式参数说明 { 局部变量定义 函数体语句 }

宇凡微电子YF153J 8位单片机用户手册说明书

深圳宇凡微电子有限公司8-Bit Single-Chip Microcontrollers YF153J用户手册(Ver1.1)2019年12月修订目录1芯片简介 (3)1.1功能特性 (3)1.2引脚分配 (4)1.3引脚描述 (5)1.4系统框图 (6)2存储器结构 (7)2.1程序存储器区 (7)2.2数据存储区 (8)3寄存器配置 (9)3.1操作寄存器 (9)3.1.1RPAGE~R0(间接地址存储器) (9)3.1.2RPAGE~R1(TCC定时计数器) (9)3.1.3RPAGE~R2(PC程序计数器) (9)3.1.4RPAGE~R3(STATUS状态寄存器) (10)3.1.5RPAGE~R4(FSR RAM选择寄存器) (11)3.1.6RPAGE~R5(P0RT5数据寄存器) (11)3.1.7RPAGE~R6(P0RT6数据寄存器) (12)3.1.8RPAGE~R7(LVD控制寄存器) (12)3.1.9RPAGE~R8(T1控制寄存器) (12)3.1.10RPAGE~R9(PWM周期寄存器) (13)3.1.11RPAGE~RA(PWM1占空比寄存器) (13)3.1.12RPAGE~RB(PWM2占空比寄存器) (13)3.1.13RPAGE~RC(PWM3占空比寄存器) (13)3.1.14RPAGE~RD(P6端口中断唤醒使能寄存器) (14)3.1.15RPAGE~RE(CPU模式控制寄存器) (14)3.1.16RPAGE~RF(中断标志寄存器) (15)3.2控制寄存器 (16)3.2.1CONT(控制寄存器) (17)3.2.2IOPAGE~IOC5(P5端口方向控制寄存器) (18)3.2.3IOPAGE~IOC6(P6端口方向控制寄存器) (18)3.2.4IOPAGE~IOC9(端口上下拉控制寄存器) (18)3.2.5IOPAGE~IOCB(端口下拉控制寄存器) (18)3.2.6IOPAGE~IOCD(P6端口上拉控制寄存器) (19)3.2.7IOPAGE~IOCE(WDT控制寄存器) (19)3.2.8IOPAGF~IOCF(WDT唤醒及中断使能控制寄存器) (20)3.3重要说明 (20)4封装类型 (21)5封装尺寸 (22)5.114PIN封装尺寸 (22)5.28PIN封装尺寸 (24)1芯片简介1.1功能特性CPU配置●1K×14-Bit OTP ROM●48×8-Bit SRAM●5级堆栈空间●28级可编程电压检测(LVD)2.0V~4.7V,0.1V/级●8级可编程电压复位(LVR)1.2V,1.6V,1.8V,2.4V2.7V,3.3V,3.6V,3.9V●工作电流小于2mA(4MHz/5V)●工作电流30μA(32KHz/3V)●休眠电流小于1μA(休眠模式)I/O配置●2组双向IO端口:P5,P6●12个I/O引脚●唤醒端口:P6口●12个可编程上拉I/O引脚●11个可编程下拉I/O引脚●端口驱动可增强●P63(复位引脚)可配置上拉和输出●外部电压检测:P63●外部中断:P60工作电压●工作电压范围:1.8V~5.5V(0℃-70℃)2.3V~5.5V(-40℃-85℃)常温(25℃)工作电压可低至1.5V●工作温度范围:工作温度-40℃-85℃工作频率范围●外部晶振HXT,LXT●外部晶振内置电容:Disable、7PF、9PF、12.5PF●内置IRC振荡电路:8MHz/1MHz●时钟周期分频选择:2Clock,4Clock,8Clock16Clock,32Clock外围模块●8Bit实时时钟/计数器●3路共周期8Bit脉宽调制器PWM 中断源●TCC溢出中断●外部中断●输入端口状态改变产生中断●T1/PWM周期溢出中断特性●可编程WDT定时器4.5ms、18ms、72ms、288ms●内置RC振荡器供电:VDD、LDO2.1V封装类型●YF153J-DIP14;●YF153J-SOP14;●YF153J-DIP8;●YF153J-SOP8;YF153J-14PIN脚位图YF153J-8PIN脚位图序号管脚名I/O功能描述P50P50I/O(上/下拉)GPIO,可编程上下拉、高驱动P51P51I/O(上/下拉)GPIO,可编程上下拉、高驱动P52P52I/O(上/下拉)GPIO,可编程上下拉、高驱动P53P53I/O(上/下拉)GPIO,可编程上下拉、高驱动P60P60I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒EXINT I(SMT)外部中断输入端口PWM3O PWM3输出P61P61I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒PWM20PWM2输出P62P62I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒TCC I外部TCC信号源输入脚PWM10PWM1输出P63P63I/O(上拉)GPIO,可编程上拉、端口唤醒RST I(SMT)复位引脚EXVDET I(ANALOG)电压检测引脚P64P64I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒P65P65I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒P66P66I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒P67P67I/O(上/下拉)GPIO,可编程上下拉、高驱动、端口唤醒VDD--电源VSS--地1.4系统框图2存储器结构2.1程序存储器区2.2数据存储区RPAGE\IOPAGE\Bank数据寄存器区地址R页面寄存器CTLX0页面寄存器0x00R0(间接地址存储器)保留0x01R1(TCC定时计数器)CONT(控制寄存器)0x02R2(PC程序计数器)保留0x03R3(STATUS状态寄存器)保留0x04FSR RAM选择寄存器保留0x05P0RT5数据寄存器P5方向控制寄存器0x06P0RT6数据寄存器P6方向控制寄存器0x07LVD控制寄存器保留0x08PWM控制寄存器保留0x09PWM周期寄存器端口上下拉控制寄存器0x0A PWM1占空比寄存器保留0x0B PWM2占空比寄存器端口下拉控制寄存器0x0C PWM3占空比寄存器保留0x0D输入状态变化中断使能控制器端口上拉控制寄存器0x0E CPU模式控制寄存器WDT使能控制寄存器0x0F中断标志寄存器中断使能控制寄存器地址Bank寄存器0x10~通用寄存器0x3F3寄存器配置3.1操作寄存器3.1.1RPAGE~R0(间接地址存储器)Bit7Bit6Bit5Bit4Bit3Bit2Bit1Bit0RIND<7:0>间接寻址寄存器并不是一个实际存在的寄存器,它的主要功能是作为间接寻址的指针。

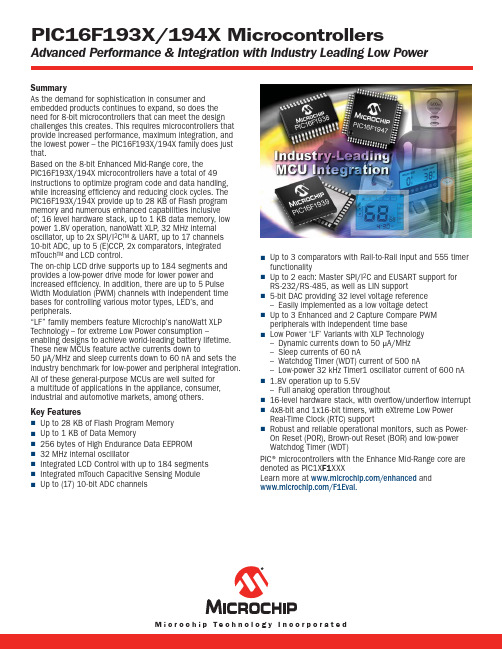

PIC16F193X 194X微控器高性能与行业领先的低功耗微控技术说明书

PIC16F193X/194X Microcontrollers Advanced Performance & Integration with Industry Leading Low PowerM i c r o chi p T e c h n o l o g y I n c o r p o r a t e dSummaryAs the demand for sophistication in consumer and embedded products continues to expand, so does the need for 8-bit microcontrollers that can meet the design challenges this creates. This requires microcontrollers that provide increased performance, maximum integration, and the lowest power – the PIC16F193X/194X family does just that.Based on the 8-bit Enhanced Mid-Range core, thePIC16F193X/194X microcontrollers have a total of 49 instructions to optimize program code and data handling, while increasing effi ciency and reducing clock cycles. The PIC16F193X/194X provide up to 28 KB of Flash program memory and numerous enhanced capabilities inclusive of; 16 level hardware stack, up to 1 KB data memory, low power 1.8V operation, nanoWatt XLP, 32 MHz internal oscillator, up to 2x SPI/I2C™ & UART, up to 17 channels 10-bit ADC, up to 5 (E)CCP, 2x comparators, integratedmTouch™ and LCD control.The on-chip LCD drive supports up to 184 segments and provides a low-power drive mode for lower power and increased effi ciency. In addition, there are up to 5 Pulse Width Modulation (PWM) channels with independent time bases for controlling various motor types, LED’s, and peripherals.“LF” family members feature Microchip’s nanoWatt XLP Technology – for extreme Low Power consumption – enabling designs to achieve world-leading battery lifetime. These new MCUs feature active currents down to50 μA/MHz and sleep currents down to 60 nA and sets the industry benchmark for low-power and peripheral integration. All of these general-purpose MCUs are well suited fora multitude of applications in the appliance, consumer, industrial and automotive markets, among others.Key Features■U p to 28 KB of Flash Program Memory■Up to 1 KB of Data Memory■256 bytes of High Endurance Data EEPROM■32 MHz internal oscillator■Integrated LCD Control with up to 184 segments■I ntegrated mTouch Capacitive Sensing Module■Up to (17) 10-bit ADC channels ■U p to 3 comparators with Rail-to-Rail input and 555 timer functionality■U p to 2 each: Master SPI/I2C and EUSART support for RS-232/RS-485, as well as LIN support■5-bit DAC providing 32 level voltage reference– Easily implemented as a low voltage detect■U p to 3 Enhanced and 2 Capture Compare PWM peripherals with independent time base■L ow Power ‘LF’ Variants with XLP Technology– Dynamic currents down to 50 μA/MHz– Sleep currents of 60 nA– Watchdog Timer (WDT) current of 500 nA– Low-power 32 kHz Timer1 oscillator current of 600 nA ■1.8V operation up to 5.5V– Full analog operation throughout■16-level hardware stack, with overfl ow/underfl ow interrupt ■4x8-bit and 1x16-bit timers, with eXtreme Low Power Real-Time Clock (RTC) support■R obust and reliable operational monitors, such as Power-On Reset (POR), Brown-out Reset (BOR) and low-power Watchdog Timer (WDT)PIC® microcontrollers with the Enhance Mid-Range core are denoted as PIC1X F1XXXLearn more at /enhanced and/F1Eval.Information subject to change. The Microchip name and logo, the Microchip logo, MPLAB and PIC are registered trademarks and mTouch, PICDEM and PICkit are trademarks of Microchip TechnologyIncorporated in the U.S.A. and other countries. All other trademarks mentioned herein are property of their respective companies. © 2010, Microchip Technology Incorporated. All Rights Reserved. Printed in the U.S.A. 8/10 DS41435A*DS41435A*Visit our web site for additional product information and to locate your local sales office.Microchip Technology Inc. • 2355 W. Chandler Blvd. • Chandler, AZ 85224-6199/enhanced /F1EvalPart Number Development Tool Part Number Development ToolDV164131PICkit™ 3 Debug Express(Coming Soon)F1 + Low Voltage Evaluation PlatformDV164035MPLAB ICD 3 In-Circuit Debugger Kit (Coming Soon)F1 BLDC Motor add-on for the F1 Evaluation Platform DM164130-1F1 Evaluation Platform/F1Eval (Coming Soon)F1 BDC Motor add-on for the F1 Evaluation PlatformDV164132F1 Evaluation Kit (Coming Soon)F1 Bipolar Stepper Motor add-on for the F1 Evaluation Platform DM183032PIC18 Explorer Board (Coming Soon)F1 Unipolar Stepper Motor add-on for the F1 Evaluation Platform DM163030PICDEM™ LCD 2 Demo Board(Coming Soon)PIC16F/LF1947 Plug-in Module(Accessory for the PIC18 Explorer or PICDEM LCD 2)Additional Information■ PIC16F/LF193X Data Sheet , DS41364■ PIC16F/LF194X Data Sheet , DS41414■ PIC1XF1XXX Software Migration , DS41375■ I 2C Bootloader for the PIC16F1XXX , AN1302■ mTouch™ Sensing Solution User’s Guide , DS41328■ 8-bit PIC Microcontroller Solution Brochure , DS39630■ Corporate Focus Product Selector Guide , DS01308■ Quick Guide to Microchip Development Tools Brochure ,DS51894Sample/Purchasing Information■ On-line Sampling: ■ On-line Purchasing: Device Flash (Bytes)Data RAM (Bytes)Data EEPROM (Bytes)LCD Segments 10-bit ADC ComparatorsECCP/CCP Communication Operating Voltage Pins Packages PIC16F1933 PIC16LF19337K 256256601123/2EUSART , I 2C, SPI 1.8V-5.5V 1.8V-3.6V 28SPDIP , SOIC, SSOP ,6X6 QFN, 4X4 UQFN PIC16F1934 PIC16LF19347K 256256961423/2EUSART , I 2C, SPI 1.8V-5.5V 1.8V-3.6V 40/44PDIP , TQFP , 8X8 QFN, 5X5 UQFN PIC16F1936 PIC16LF193614K 512256601123/2EUSART , I 2C, SPI 1.8V-5.5V 1.8V-3.6V 28SPDIP , SOIC, SSOP ,6X6 QFN, 4X4 UQFN PIC16F1937 PIC16LF193714K 512256961423/2EUSART , I 2C, SPI 1.8V-5.5V 1.8V-3.6V 40/44PDIP , TQFP , 8X8 QFN, 5X5 UQFN PIC16F1938 PIC16LF193828K 1024256601123/2EUSART , I 2C, SPI 1.8V-5.5V 1.8V-3.6V 28SPDIP , SOIC, SSOP ,6X6 QFN, 4X4 UQFN PIC16F1939 PIC16LF193928K 1024256961423/2EUSART , I 2C, SPI 1.8V-5.5V 1.8V-3.6V 40/44PDIP , TQFP , 8X8 QFN, 5X5 UQFN PIC16F1946 PIC16LF1946 14K 5122561841733/22x EUSART , 2x I 2C,2x SPI 1.8V-5.5V 1.8V-3.6V 64TQFP , 9X9 QFN PIC16F1947 PIC16LF194728K10242561841733/22x EUSART , 2x I 2C,2x SPI1.8V-5.5V 1.8V-3.6V64TQFP , 9X9 QFNAvailable in 28-, 44- & 64-pin packages.PIC16F193X/194X Block DiagramInternal Oscillator32 MHzData EEPROM256BData MemoryUp to 1 KB Linear AddressingEnhanced Mid-Range CPU14-bit Instruction49 Total Instructions(2) 16-bit File Select RegistersInterrupt Context SaveReliable Low PowerWDT, RTC, BOR, POR,nanoWatt XLPLCD Drive Up to 184 segments 10-bit ADC Up to 17 channelsUp to 3x Comparators with SR Latch mTouch™Capacitive Sensing ModuleCommunications Up to 2x each MI C, SPI, EUSARTCapture/Compare/PWMUp to 5 Channels16-Level Stack &Program CounterReset CapabilitiesProgram MemoryUp to 28 KB (16K Instructions)5-bit DAC 32-Level V。

MSP430系列十六位超低功耗单片机教学实验系统实验教程

在这里.需要对低功耗问题作一些说明。 首先,对一个处理器而言,活动模式时的功耗必须与其性能一起来考察、衡量,忽略性能来看功耗是 片面的。在计算机体系结构中,是用 W/MIPS(瓦特/百万指令每秒)来衡量处理器的功耗与性能关系的, 这种标称方法是合理的。MSP430 系列单片机在活动模式时耗电 250uA/MIPS,这个指标是很高的(传统 的 Mcs51 单片机约为 10~20mA/MIPS)。 其次,作为一个应用系统,功耗是整个系统的功耗,而不 仅仅是处理器的功耗。比如,在一个有多个输入信号的应用系统中,处理器输入端口的漏电流对系统的耗 电影响就较大了。MSP430 单片机输入端口的漏电流最大为 50nA,远低于其他系列单片机(一般为 l~10uA)。 另外,处理器的功耗还要看它内部功能模块是否可以关闭.以及模块活动情况下的耗电.比如低电压 监测电路的耗电等。还要注意,有些单片机的某些参数指标中.虽然典型值可能很小,但最大值和典型值 相差数十倍,而设计时要考虑到最坏情况,就应该关心参数标称的最大值,而不是典型值。总体而言, MSP430 系列单片机堪称目前世界上功耗最低的单片机,其应用系统可以做到用一枚电池使用 10 年。

MSP430 系列单片机有独特的时钟系统设计,包括两个不同的时钟系统:基本时钟系统和锁频环(FLL 和 FLL+)时钟系统或 DCO 数字振荡器时钟系统。由时钟系统产生 CPU 和各功能模块所需的时钟,并且这 些时钟可以在指令的控制下打开或关闭,从而实现对总体功耗的控制。由于系统运行时使用的功能模块不 同,即采用不同的工作模式,芯片的功耗有明显的差异。在系统中共有种活动模式(AM)和 5 种低功耗模式 (LPM0~LPM4)。

CA51F003 系列 MCU 中文用户手册

Built-in 16 Bit PWM / 12 Bit ADC / 1T 8051 18K Flash MCUCA51F003系列MCU中文用户手册REV 2.3深圳市锦锐科技股份有限公司电话:*************传真:*************地址:中国广东省深圳市南山区沙河西路深圳湾科技生态园一区2栋B座5层目录1概述 (6)2基本特性 (6)3芯片型号功能介绍 (9)4系统框图 (10)5引脚封装及其描述 (11)5.1封装定义 (11)5.2引脚描述 (13)6 中央处理器(CPU) (16)6.1CPU简介 (16)6.2寄存器描述 (16)7 存储器系统 (20)7.1 随机数据存储器(RAM) (20)7.2 特殊功能寄存器(SFR) (20)7.3 Flash存储器 (22)7.3.1 功能简介 (22)7.3.2 Flash存储器组织结构 (22)7.3.3 Flash寄存器描述 (22)7.3.4 Flash控制例程 (25)7.4外部RAM映射为程序空间 (27)8 中断系统 (28)8.1 功能简介 (28)8.2 中断逻辑 (28)8.3 中断向量表 (29)8.4 中断控制寄存器 (29)8.5 外部中断 (33)8.5.1外部中断介绍 (33)8.5.2外部中断寄存器 (33)8.5.3外部中断控制例程 (36)9 时钟系统 (38)9.1 时钟系统介绍 (38)9.1.1 时钟专用名称定义 (38)9.1.2 内置32MHz RC振荡器(IRCH) (38)9.1.3内置131 KHz RC振荡器(IRCL) (39)9.1.4外部高速晶体谐振器(XOSCH)和外部时钟输入(CLKIN) (39)9.2 时钟控制寄存器描述 (39)9.3 系统时钟 (42)9.3.1 系统时钟结构图 (42)9.3.2 系统时钟控制寄存器描述 (42)9.3.3 系统时钟控制方法及例程 (44)10 供电和复位系统 (46)10.1 供电系统 (46)10.1.1 LDO功能简介 (46)10.1.2 LDO控制寄存器 (47)10.2 复位系统 (49)11 功耗管理 (51)11.1 IDLE模式 (51)11.2 STOP模式 (51)11.3 低速运行模式 (52)11.4 低功耗相关寄存器描述 (52)11.5 低功耗模式控制例程 (54)12 通用定时器(定时器0,定时器1,定时器2) (56)12.1 定时器0 (56)12.1.1 定时器0介绍 (56)12.1.2 定时器0寄存器描述 (57)12.2 定时器1 (59)12.2.1 定时器1介绍 (59)12.2.2 定时器1寄存器描述 (60)12.3 定时器2 (61)12.3.1 功能简介 (61)12.3.2 定时器2寄存器描述 (62)13 看门狗定时器(WDT) (67)13.1 看门狗定时器(WDT)功能简介 (67)13.2 看门狗定时器(WDT)寄存器描述 (67)13.3 看门狗定时器控制例程 (69)14 TMC定时器 (70)14.1 TMC功能简介 (70)14.2 TMC寄存器描述 (70)14.3 TMC控制例程 (71)15 通用输入输出口(GPIO)及复用定义 (72)15.1 功能简介 (72)15.2 引脚寄存器描述 (74)15.3 引脚控制例程 (82)16 通用串行接口(UART1/UART2) (83)16.1 UART1和UART2 (83)16.1.1 介绍 (83)16.1.2 UARTx寄存器描述 (84)17 I²C接口 (88)17.1 功能简介 (88)17.2 I2C主要特点 (88)17.3 I2C功能描述 (88)17.4 I2C通信引脚的映射 (90)17.5 寄存器描述 (90)17.6 I2C控制例程 (94)18 PWM (100)18.1 PWM功能简介 (100)18.3 PWM寄存器描述 (105)18.4 PWM功能控制例程 (114)19 模/数转换器(ADC) (116)19.1 功能简介 (116)19.2 主要特性 (116)19.3 结构框图 (116)19.4 功能描述 (117)19.5 寄存器描述 (118)19.6 ADC控制例程 (122)20运放(AMP) (123)20.1 功能简介 (123)20.2寄存器描述 (123)21蜂鸣器(BUZZER) (124)21.1 功能描述 (124)21.2寄存器描述 (124)22低电压检测(LVD) (126)22.1 功能简介 (126)22.2 功能描述 (126)22.3 寄存器描述 (127)22.4 LVD控制例程 (128)23无线充解码 (129)23.1 功能简介 (129)23.2寄存器描述 (129)24乘除法器(MDU) (134)24.1 功能简介 (134)24.2 结构图 (134)24.3 功能描述 (135)24.3.1 乘法器 (135)24.3.2 除法器 (135)24.3.3 移位运算 (135)24.4 寄存器描述 (136)24.5 MDU控制例程 (138)25 SPI接口 (142)25.1 功能简介 (142)25.2 寄存器描述 (144)25.3 SPI控制例程 (146)26 SWIM接口 (149)26.1 简介 (149)26.2 寄存器描述 (149)26 程序下载和仿真 (152)26.1 程序下载 (152)26.2 在线仿真 (152)27 电气特性 (153)27.2 直流电气特性 (153)27.3交流电气特性 (155)28封装类型 (156)29附录 (159)附录1 指令集速查表 (159)1概述CA51F003系列芯片是基于1T 8051内核的8位微控制器,通常情况下,运行速度比传统的8051芯片快10倍,性能更加优越。

LTC2245-16 16 位、5 MSPS、低功耗、并行 16 位 ADC 数据手册说明书

产品特性单电源供电:1.8V 或3V 低功耗:32mW (电源电压1.8V )54mW (电源电压3.0V )信噪比(SNR):75dBFS(5MHz Fin 、10MSPS)无杂散动态范围(SFDR):95dBFs(5MHz Fin 、10MSPS)采样频率可以低至1MSPS CMOS 输出并口配置模式32引脚(5mm ×5mm )QFN 封装支持内置或外置参考电压源应用通信便携式医学成像多通道数据采集产品聚焦1.管脚兼容ADI 公司LTC2245系列2.单电源供电,支持1.8V 或3V 两档电源电压3.CMOS 输出4.并口配置支持1.8V~3.6V 电平功能框图图 1.功能框图修订历史(内部)版本时间位置修订内容V1.02021/11/09手册初稿目录产品特性 (1)应用 (1)产品聚焦 (1)功能框图 (1)修订历史(内部) (2)目录 (3)概述 (4)技术规格 (5)ADC直流规格 (5)ADC交流规格 (6)数字规格 (7)时序规格 (7)时序图 (8)绝对最大额定值 (9)热特性 (9)ESD警告 (9)引脚配置和功能描述 (10)典型工作特性 (12)等效电路 (13)应用信息 (13)转换器工作 (13)模拟输入 (13)输入滤波 (14)变压器耦合电路 (14)放大器电路 (15)参考电平 (15)REFH,REFL (15)时钟输入 (15)输出数据格式 (16)输出停用 (16)睡眠模式 (16)应用信息 (17)设计指南 (17)外形尺寸 (18)名词对照表 (19)概述ZYL2245是一款单通道、14位10MSPS低噪声模数转换器(ADC),旨在支持需要高性能、低噪声、低成本、小尺寸、多功能的数据采集和通信应用。

ZYL2245支持3V或1.8V两种电源模式。

这款双通道ADC内核采用差分、多级流水线结构,集成了输出纠错逻辑,集成内置基准源,支持引入外置基准源作为ADC的基准电压。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

TR4P153BT/BF General Purpose MCU1. General DescriptionsThe TR4P153BT/BF series are high-performance 4-bit RISC micro-controller embedded with 2KX12 bits OTP, 256X4 bits SRAM, 8 bit PWM, 11 Input/Output ports and one input port. It’s flexible and cost-effective solution for general purpose MCU applications.2. Featuresz Operating voltage: (1) 2.0V to 5.5V for Temp. = 25J (2) 2.2V to 5.5V for Temp. = -40J~+85Jz These MCU can operate in high speed. Oscillator type can be selected by option setting. High speed and low speed operating mode is selectable by software. Below is the chip performance in different modes.(a)Internal high speed HRCOSC: 8 MIPS / 4 MIPS / 2 MIPS / 1 MIPS or low speed LRCOSC114.69KIPS( thousand instructions per second) / 57.34 KIPS / 28.67 KIPS / 14.33 KIPS.(b)External EXTOSC: 8 MIPS (16 MHz X’tal) ~ 0.5 MIPS (1 MHz X’tal ).z Memory SizeProgram ROM size : 2KX12 bits (OTP type)SRAM size: total 256x4 bits SRAMz Wake up function for power-down modeHALT mode wake up source: RTC timer overflow, PA0~3, PB0~3 and PD0~3 edge triggerz11 input /output ports: PA0~PA2, PB0~PB3, PD0~PD3. Each I/O can be bit programmable as input or output port. These 11 I/Os also provided level-change-wakeup function. Pull up and pull down resistor setting is available by software.z 1 input port PA3, PA3 is shared with RSTB (reset) pin by option. It also provides level-change-wakeup function. Pull up and pull down resistor can be configured by software too.z Port A, Port B and Port D are provided with high sink current 24mA @VDD=5V,Vol=0.5V( except PA3 ) z Port A, Port B and Port D are provided with high drive current 23mA @VDD=5V,Voh=4.5V( except PA3 ) z PA1 built-in 38KHz modulator by option.z One Op-Amp is provided, three pins shared with PD0, PD1, PB2 (by option).z One comparator is provided, two input pins shared with PD2, PD3 (by option).z Three timersTimer 1: 8 bits timer/counter/PWM, its clock source can be from chip-internal or external.Timer 2: 8 bits timerRTC : time period 0.125 /0.25/0.5/1 Sec or 15.625/31.25/62.5/125 ms,RTC Clock source comes from internal LRCOSC.z Four reset conditionLow voltage reset (LVR 1.8V)Power on resetExternal RSTB pin shared with PA3 pin by option.Watch dog timer overflow reset ( 0.125 sec ~ 1 sec by option )z Three internal interrupt sources: TIMER1, TIMER2 or RTC interrupt.z WDT(Watch dog timer)WDT can be enabled/disabled in HALT mode by optionWDT clock source comes from internal LRCOSC.z Provides 8 Bits PWM, PWM signal output is shared with PA2 pin by option.z Built-in external X’tal oscillator ( EXTOSC, use 1MHz~16MHz external ceramic resonator or crystal oscillator ). These two crystal pins are shared with PB1 and PB0 by option.z Built-in high frequency internal 32MHz RC oscillator ( HRCOSC, frequency deviation within ¡2%, temperature range at -40J~+85J, Vdd = 2.0V to 5.5V )z Built-in low frequency internal RC OSC (LRCOSC) 459KHz ( frequency deviation within ¡12% )ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.codes …etc. It’s located at address 640h ~ 66Fh.Package (8/14 SOP)SOP 14PA0PA1/IR38KPA2/PWM/BZ/CKIPA3/RSTB/VPPPB0/XOUT/OSCADJPB1/XINPB2/CA3PB3PD1/CA2VDDVSSPD0/CA1PD3/CB2PD2/CB1PA0PA1/IR38KPA2/PWM/BZ/CKIPA3/RSTB/VPPPB0/XOUT/OSCADJPB1/XINVDDVSSSOP 8TR4P153BT/BFTR4P153BT/BFALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.3. Pads InformationPAD NameType State AfterResetDescriptionPower Input VDD I High Power input pinVSS I Low Ground input pinGeneral I/O ports PA0~PA2 I/OXXX PA0~PA2 are programmable I/O ports, with pull up and down resistor100K ohm.Level-change-wakeup function is provided. PA1 is shared with IR38K function by option.PA2 is shared with PWM/CKI/BZ functions by option.PA3 (RSTB/VPP) I X PA3 is an input pin only, with pull up resistor 60K ohm, or pull down resistor 100K ohm.Level-change-wakeup function is provided. PA3 is shared with RSTB pin by option.PB0~PB3 I/O XXXX PB0~PB3 are programmable I/O ports, with pull up and down resistor100K ohm.Level-change-wakeup function is provided.PB0 is shared with XOUT/OSCADJ by option. OSCADJ pin is used for frequency adjust of HRCOSC.PB1 is shared with XIN pin by option.XIN and XOUT is connected to external X’tal.PB2 is shared with the output CA3 of Op Amp by option.PD0~PD3 I/O XXXX Port D is a programmable I/O port, with pull up and down resistor 100Kohm.Level-change-wakeup function is provided.PD0 and PD1 are shared with two inputs (CA1, CA2) of Op AMP by option.PD2 and PD3 are shared with two inputs (CB1, CB2) of a comparator by option.Block DiagramVDD4. ELECTRICAL CHARACTERISTICS4.1 Absolute Maximum RatingsABSOLUTE MAXIMUM RATINGSPARAMETER SYSMBOL RATING UNIT DC Supply Voltage V+ < 7.0 V Input Voltage Range V IN-0.5 to VDD+0.5 VAStorage Temperature T STO-50 to +150 ºC 4.2 DC/AC CharacteristicsDC CHARACTERISTICS ( TA = 25¢J, VDD = 3V, unless otherwise noted )PARAMETER SYMBOL TEST CONDITIONSLIMITUNIT Min Typ MaxOperating voltage V VDD1Temp. = 25¢J 2.0 - 5.5 V V VDD2Temp.= -40¢J~+85¢J 2.2 5.5 VOperating Current I OP1VDD=3V , MCU run 8 MIPS 2.6 mA I OP2VDD=5V , MCU run 8 MIPS 3.0 mA I OP3VDD=3V , MCU run 1 MIPS 1.6 mA I OP4VDD=5V , MCU run 1 MIPS 2.0 mA I OP5VDD=3V , MCU run 14 KIPS50 uA I OP6VDD=3V , MCU run 114.7 KIPS200 uAStandby Current I STBY1 MCU stop in HALT mode WDT& RTC off2.5 (VDD=3V)3 (VDD=5V)uAI STBY2_1.VDD=5V2.MCU stop in HALT mode,WDT on or RTC on8 uAInput High Level VIHAll I/O port 0.8*V DD V Input Low Level V IL All I/O port 0.2*V DD VOutput Drive Current I OH1VDD=3V , V OH=2.5V,All I/O port-8 -15 mA I OH2VDD=5V , V OH=4.5V,All I/O port-12 -23 mAOutput Sink Current I OL1VDD=3V , V OL=0.5V,All I/O port8 15 mA I OL2VDD=5V , V OL=0.5V,All I/O port12 24 mAPA,PB,PD pull down Res. R down1Pull down 180K ohm, VDD=3V140 180 220 K ohm R down2Pull down 100K ohm, VDD=5V60 90 120 K ohmPA,PB,PD pull up Res. ( except PA3 ) R up1Pull up 180K ohm, VDD=3V 140 180 220 K ohm R up2Pull up 100K ohm, VDD=5V 60 90 120 K ohmPA3 pull up Res. R up3Pull up 60K ohm ,VDD=2V~5V40 60 80 K ohmLVR V LVR1Temp. = 25¢J 1.6 1.8 2.0 V V LVR2Temp.= -40¢J~+85¢J 1.4 1.8 2.2 VALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.AC characteristics ( TA = 25¢J, VDD = 3V, unless otherwise noted )PARAMETER SYMBOL TEST CONDITIONSLIMITUNIT Min Typ MaxInternal HRCOSC FrequencyF HRCOSC VDD = 2.0V~5.5VTemp = -40¢J~+85¢J31.3632 ¡2% 32.64MHzInternal LRCOSC Frequency F LRCOSC1VDD = 2.0V~5.5VTemp. = 25¢J458.752 ¡12% KHz F LRCOSC2VDD = 2.0V~5.5VTemp = -40¢J~+85¢J458.752 ¡20% KHzExternal X’tal EXTOSC F XTOSC VDD = 2.0V~5.5V1~16 MHzMCU operating frequency ( clock source from F HRCOSC or F XTOSC F MCk11.in NORMAL mode2.Clock source : F HRCOSC3.VDD = 2.0V~5.5V4.Temp. -40¢J~+85¢J8 ¡2%, 4 ¡2%2 ¡2%, 1 ¡2%(F HRCOSC/4, F HRCOSC /8,F HRCOSC /16, F HRCOSC /32 )MIPSF MCk21.in NORMAL mode2.Clock source : F XTOSC3.VDD = 2.0V~5.5V4 Temp. -40¢J~+85¢J5.If F XTOSC = 16Mhz8 , 4, 2, 1( F XTOSC/2, F XTOSC/4,F XTOSC/8, F XTOSC/16 )MIPSMCU operating frequency ( clock source F LRCOSC ) F MCk31.in GREEN mode2.VDD = 2.0V~5.5V3.Temp. = 25¢J114.69¡12%,57.34¡12%28.67¡12%,14.33¡12%KIPSPA1 38KHz output( clock source F HRCOSC or F XTOSC)F38K11.in NORMAL mode2.PA1 IR38K option enabled3.Register F38K=14.Temp. = 25¢J38.09 ¡2%(F HRCOSC /840)KHz38.09(F XTOSC=16Mhz)/420PA1 38KHz output ( clock source F LRCOSC ) F38K21.in GREEN mode2.PA1 IR38K option enabled3.Register F38K=14.Temp. = 25¢J38.23 ¡12%(F LRCOSC/12) KHzRTC period T RTC1VDD = 2.0V~5.5VTemp. = 25¢Jclock source F LRCOSCSPUP option enabled0.125¡12%, 0.25¡12%0.5¡12%, 1.0¡12%Sec T RTC2VDD = 2.0V~5.5VTemp. = 25¢Jclock source F LRCOSCSPUP option disabled15.625¡12%,31.25¡12%62.5¡12%, 125¡12%msWDT period TWDT VDD = 2.0V~5.5VTemp. = 25¢Jclock source F LRCOSC0.125¡12%, 0.25¡12%0.5¡12% , 1.0¡12%SecStable clock delayafter power on or system reset CKstable1System oscillator --HRCOSC( Note 1 )160us + 1024 x (1/ F MCK1)( Note 5 ) us CKstable2System oscillator --EXTOSC( Note 2 )160us + 1024 x (1/ F MCK2)( Note 5 ) usStable clock delay after wake up CKstable3System oscillator --HRCOSC( Note 3 )64 x (1/ F MCK1) ( Note 5 )us CKstable4System oscillator --EXTOSC( Note 4 )1024 x (1/ F MCK2) ( Note 5 )usALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.Note1: The stable clock delay (CKstable1) is a delay between HRCOSC-started and 1st instruction-execution.This delay will ensure stable system clock after power on or reset.Note2: The stable clock delay (CKstable2) is a delay between clock output of EXTOSC and 1st instruction. Thisdelay will ensure stable system clock after power on or reset.Note3: The stable clock delay (CKstable3) is a delay between HRCOSC-started and 1st instruction-execution ofwakeup. This delay will ensure stable system clock after wake up.Note4: The stable clock delay (CKstable4) is a delay between EXTOSC-started and 1st instruction-execution ofwakeup. This delay will ensure stable system clock after wake up.Note5: F MCK1 and F MCK2 are MCU operating clock.AC Characteristics of OP ( TA = 25¢J , VDD = 2V~5.5V, unless otherwise noted )PARAMETERSYMBOLTEST CONDITIONSLIMITUNITMinTypMaxQuiescent current I QUI VDD = 2V~5.5V305070uA Input voltage range V IN 0 VDD V Output voltage range V OUT 0.1 VDD-0.1V Offset voltage V OS 10 100 mV Output sink current I SINK 15 30 uA Output source current I SOU150 300 uA Output resistor load R L100KOhmAC Characteristics of Comparator ( TA = 25¢J , VDD = 2V~5.5V, unless otherwise noted )PARAMETERSYMBOLTEST CONDITIONSLIMITUNITMinTypMaxQuiescent current I QUI VDD = 2V~5.5V12uA Input voltage range V IN 0 VDD V Offset voltageV OS10100mVThe LRCOSC frequency VS. temperature, VDD=2.0V~5.5V380400420440460480-5050100L R C O S C (K H z )Temperature(C)ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.The HRCOSC frequency VS. temperature, VDD=2.0V~5.5V5. FUNCTIONAL DESCRIPTIONThis MCU inside TR4P153BT/BF is a high performance processor. The operation speed can be range from 0.5 MIPS to 8 MIPS depending on different applications.5.1 Program ROM (OTP ROM)TR4P153B series support two kind of OTP ROM arrangement. They are TR4P153BT and TR4P153BF. The OTP ROM memory plan is shown below:Address TR4P153BT ( 1.6 K OTP ROM ) TR4P153BF ( 2 K OTP ROM )000h ~ 0FFhUser area 1.5K ( 1536 X12 ) User area 1.5K ( 1536 X12 ) 100h ~ 1FFh 200h ~ 2FFh…..500h ~ 5FFh600h ~ 63FhReserved area Reserved area 640h ~ 66Fh User Information block (48X12). For datastore only, can't be used to store program. User area 0.5K( 448X12 ) 670h ~ 7FFh Reserved area Note: 1. For TR4P153BT and TR4P153BF, the content of OTP ROM address $640h~$66Fh can beread by program. Address $600h~$63Fh and $670h~$7FFh can’t be read by program.2. To read registers DMDL, DMDM and DMDH, only LD A,(n) instruction can be used. Otherinstructions are not allowed. ( n= DMDL, DMDM or DMDH )3. If DMA2~DMA0 pointed address is located at invalid address 600h~61Fh or 700h~7FFh, DMA2.2, DMA2.1, DMA2.0 will be regarded as 0 by hardware automatically, DMA0 and DMA1 will not be affected. 32.232.2532.332.3532.432.4532.5-5050100H R C O S C (M h z )Temperature(C)ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.TR4P153BT supports 1.6 K words OTP ROM which is located on $000h ~ $5FFh and $640h ~ $66Fh. The first area $000h ~ $5FFh stores user program area. The second area $640h ~ $66Fh that named user information block stores serial number, lot number or user optional codes…etc. The reserved area are $600h ~ $63Fh and $670h ~ $7FFh, they can’t be read by software.TR4P153BF supports 2 K words OTP ROM which is located on $000h ~ $5FFh and $640h ~ $7FFh.These two areas store user program. Although $640h~$7FFh is user area, but data in $670h~$7FFh can’t be read by software. The reserved area, $600h ~ $63Fh, can’t be read by program also.To read OTP ROM data, use DMA2~DMA0 registers as address pointer. The address range is located in $000H ~ $5FFH and $640H~$66FH. After these registers (DMA0~2) are specified by software, the 12bits data of ROM can be moved to A register by three instructions, they are “LD A, (DMDL)”, “LD A, (DMDM)” and “LD A, (DMDH)”. The three instructions mentioned above are two cycle instruction, all others instructions are single cycle instruction.Symbol Addr R/W Reset D3 D2D1D0DescriptionDMA0 18H R/W xxxxDMA0.3 DMA0.2DMA0.1 DMA0.0 DMA0~DMA2(exclude DMA2.3) build a 11bit addressing space for read ROM data. DMA0 is the lowest nibble address, DMA2 is the highest nibble address.DMA2.3: It’s a user usable register only, it's useless for address setting.DMA1 19H R/W xxxxDMA1.3 DMA1.2DMA1.1 DMA1.0 DMA2 1AH R/W xxxxDMA2.3 DMA2.2DMA2.1 DMA2.0 DMDL 1CH R xxxxDMDL.3 DMDL.2DMDL.1DMDL.0DMDL is used to read low nibble data from ROM that addressed by DMA0 ~ DMA2.DMDM 1DH R/W xxxxDMDM.3 DMDM.2DMDM.1DMDM.0(1) DMDM is used to read middle nibble data from ROM that addressed by DMA0 ~ DMA2.(2) Write this register with data 05h willclear watch dog timer (WDT)(3) Write this register with data 0Ah willclear RTC counter.DMDH 1EH Rxxxx DMDH.3 DMDH.2DMDH.1DMDH.0DMDH is used to read high nibble datafrom ROM that addressed by DMA0 ~ DMA2.For example, assume the data of address 356H is 587H.LD A, #3LD (DMA2), A LD A, #5LD (DMA1), A LD A, #6LD (DMA0), A ; ROM address = 356HLD A, (DMDL) ; A register = 7H ; low nibble data of ROM address 356H LD A, (DMDM) ; A register = 8H; middle nibble data of ROM address 356H LD A, (DMDH) ; A register = 5H; high nibble data of ROM address 356H…….5.2 SRAM and I/O Memory MapTR4P153BT/BF provides 256 nibbles SRAM. SRAM is separated into 8 pages (MAH0~7). Every page has 32 nibbles (with same address, $20H~$3FH). This addressing space of SRAM is different from ROM’s address.ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.Direct Addressing (use MAH )Real SRAM AddressSRAM MAPMAH=XH ( MAH no effect ) 00H~1FHCommon I/O port and SFR(special function register) register MAH=0H 20H~3FH 00H~1FHUSER SRAM (256x4) MAH=1H 20H~3FH 20H~3FH| | |MAH=6H 20H~3FH C0H~DFHMAH=7H 20H~3FH E0H~FFHThe addressing space is separated into several pages. Software can select working pages by setting MAH register. Each page contains two blocks and each block contains 32 nibbles. The lower block ( 00H ~1FH ) is used for IO registers and special registers, it's named “common I/O block”. This block will not affected by MAH setting. In any MAH setting, software can access register of this block directly. The higher block( 20H~3FH ) is used for user SRAM access. MAH register determines current access page of SRAM. The 20H~3FH address (in instructions) determines 32 nibble address in the current page.The working space shown as below:High 32 nibbles address space (20 ~ 3F H), MAH pointed SRAM spaceLow 32 nibbles address space (0 ~ 1F H), I/O and special register, “common I/O block”, MAH has no effect on this blockMAH = 0 selects 1st 32 nibbles SRAM MAH = 1 selects 2nd 32 nibbles SRAMMAH = 2 selects 3rd 32 nibbles SRAM ...etc.MAH can be written by a special instruction "LDMAH" with direct data.MAH can not be read by MCU. When interrupt happened, MAH data will be stored by hardware and restored by "RETI" command.5.3 I/O Memory MapThe I/O memory map consists of common I/O, control registers and extended I/O space. Detailed operations are as follows:5.4 Common I/O and control registerThe "common IO block" contains 32 addresses. All registers in this block can be accessed directly by these instructions : LD/ADC/SBC/OR/AND/XOR/INC/DEC/RLC/RRC/CMP/ADR. SET, CLR ( bit set/clear ) can only operate on the address range from 00H to 0FH.Read common I/O instruction: LD/ADC/SBC/CMP/OR/AND/XOR ( Ex. LD A,(n) ) Write data to common I/O instruction: LD (n),ARead and write common I/O instruction : DEC/INC/ADR/RRC/RLC ( Ex. DEC (n) )U: unchanged X: unknown value R/W: readable & writeable R: readable only W: writeable onlySymbol Addr R/W Reset D3D2D1D0DescriptionSTATUS 00H R/W 00xx TM2IFG TM1IFG CF ZFZF : Zero status register CF : Carry status registerTM1IFG: Timer 1 interrupt flag 0: no Timer1 interrupt occurred.1: Timer1 interrupt occurred, it can be cleared by software.ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.TM2IFG: Timer 2 interrupt flag 0: no Timer 2 interrupt occurred.1: Timer2 interrupt occurred, it can be cleared by software.RTC 01H R/W 0000RTCFG F38K RTCS1 RTCS0 RTC will cause an interrupt ($008h) when in NORMAL mode or GREEN mode. In HALT mode, RTC can wakeup MCU and program will go to wake up vector ($004h).RTCS1, RTCS0: RTC interrupt period detailed description in Real Time Clock Interrupt section.F38K is valid only when IREN is enabled.F38K = 1, PA1 output 38k clockF38K = 0, PA1 PIN 38K output signaldisabled. PA1 keeps low if (option) IRNOR0 disabled. PA1 keeps high when IRNOR0 enabled.RTCFG: RTC overflow flag 0: RTC overflow not occurred.1: RTC overflow occurred, it can be cleared by software.IOC_PA 02H R/W 0000X IOCA2 IOCA1 IOCA0 Port PA0~PA2 input/output direction : 1: set port as output port individually 0: set port as input port individually PA3 is input only.DATA_PA 03H R/W xxxxDPA3 (Read only ) DPA2 DPA1 DPA0 Read data from PA0~PA3 PIN or write data to PA0~PA2 PIN ( I/O direction is selected by IOC_PA register) Reserved 04H x xxxxx x x x reserved IOC_PB 05H R/W 0000IOCB3 IOCB2 IOCB1 IOCB0 Port PB0~PB3 input/output direction : 1: set port as output port individually 0: set port as input port individuallyDATA_PB 06H R/W xxxxDPB3 DPB2 DPB1 DPB0 Read data from PB0~PB3 port or write data to PB0~PB3 ( I/O direction is defined by IOC_PB register)USER1 07H R/W xxxxUSER1.3 USER1.2USER1.1USER1.0General purpose user RAM TMCTL 08H R/W 0000TM2EN TM1EN TM1SCK TM1ALD TM1ALD: Timer 1 auto load control 0 : Timer 1 auto load function turned off 1 : Timer 1 auto load function turned onTM1SCK:Timer1 clock source selection 0: internal clock ( frequency selected by SCALER1 register )1: external clock ( from PA2 pin ) IOCA2 must be set to 0.TM1EN: Timer 1 enable control bit 0 : Timer 1 disabled 1 : Timer 1 enabledTM2EN: Timer 2 enable control bit 0 : Timer 2 disabled 1 : Timer 2 enabledSYS0 09H R/W 0000 TM2MSK TM1MSK ENINT PWMO Notice: The PWMO, ENINT, TM1MSKand TM2MSK will be cleared by HALTinstructionPWMO: PWM signal output to PA2 pin0 : PA2 pin is I/O pin1 : PA2 pin is PWM output pin( The frequency of PWM is controlled byTM1OUT and TM1ALD if PWMO=1)ENINT: Global interrupt enable0 : global interrupt disabled1 : global interrupt enabled, (ENINTcontrol the interrupt enable of Timer1, Timer 2 and RTC )TM1MSK : Timer 1 interrupt mask0 : Timer 1 interrupt masked (Timer1interrupt disabled).1 : Timer 1 interrupt unmasked (Timer1interrupt enabled).TM2MSK : Timer 2 interrupt mask0 : Timer 2 interrupt masked (Timer2interrupt disabled).1 : Timer2 interrupt un-masked (Timer2interrupt enabled).TIM1 0AH R/W 0000 TIM1.3(TIM1.7) TIM1.2(TIM1.6)TIM1.1(TIM1.5)TIM1.0(TIM1.4)TIM1.7~TIM1.0: 8 bit TIMER 1 countervalue, read or write must follow fixedsequence as shown below:(1) Write: write low nibble first, and thenwrite high nibble.(2) Read: read low nibble first, and thenread high nibble.TIM2 0BH R/W 0000 TIM2.3(TIM2.7) TIM2.2(TIM2.6)TIM2.1(TIM2.5)TIM2.0(TIM2.4)TIM2.7~TIM2.0: 8 bit TIMER 2 countervalue, read or write must follow fixedsequence as shown below:(1) Write: write low nibble first, and thenwrite high nibble.(2) Read: read low nibble first, and thenread high nibble.IOC_PD 0CH R/W 0000 IOCD3 IOCD2 IOCD1 IOCD0 Port D input/output direction select1: set port as output port individually0: set port as input port individuallyDATA_PD 0DH R/W xxxx DPD3 DPD2 DPD1 DPD0 Read port D data from PD0~PD3 port orwrite data to PD0~PD3 ( I/O direction isdefined by IOC_PD register)SCALER1 0EH R/W 0000 TM1OUT T1DIV2T1DIV1T1DIV0T1DIV2~0: The pre-scaler of Timer 1.Timer 1 clock source definition table:(F MCK = MCU operating clock )T1DIV2T1DIV1 T1DIV0 TM1CK0 0 0 F MCK/2560 0 1 F MCK /1280 1 0 F MCK /640 1 1 F MCK /321 0 0 F MCK /161 0 1 F MCK /81 1 0 F MCK /41 1 1 F MCK /2TM1OUT: Select PA2 as "Timer 1 togglesignal output" (PWMO must be 0 toenable this function).0 : Disabled, PA2 port is I/O function1 : Enable PA2 as Timer 1 toggle output(BZ).ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.USER2 0FH R/W xxxx USER2.3 USER2.2USER2.1USER2.0General purpose user RAMMDCTL10H W 1100MD1 MD0 X X MCU operation mode selection table MD1MD0MCU MODE 0 0 Into HALT mode (or useHALT instruction)0 1 Enters NORMAL mode 1 0 Enters GREEN mode 1 1 reserved, do not set thisvalue.Reserved 11H~ 17HReserved DMA0 18H R/W xxxxDMA0.3 DMA0.2DMA0.1 DMA0.0 DMA0~DMA2(exclude DMA2.3) build a 11bit addressing space for read ROM data. DMA0 is the lowest nibble address,DMA2 is the highest nibble address.DMA2.3: It’s a user usable register only, it's useless for address setting.DMA1 19H R/W xxxxDMA1.3 DMA1.2DMA1.1 DMA1.0 DMA2 1AH R/W xxxx DMA2.3 DMA2.2DMA2.1 DMA2.0Reserved 1BH x xxxxx x x x Reserved DMDL 1CH R xxxxDMDL.3 DMDL.2DMDL.1DMDL.0DMDL is used to read low nibble data from ROM that addressed by DMA0 ~ DMA2.DMDM 1DH R/W xxxx DMDM.3 DMDM.2DMDM.1DMDM.0(1) DMDM is used to read middle nibbledata from ROM that addressed by DMA0 ~ DMA2.(2) Write this register with data 05h willclear watch dog timer (WDT)(3) Write this register with data 0Ah willclear RTC counter.DMDH 1EH Rxxxx DMDH.3 DMDH.2DMDH.1DMDH.0DMDH is used to read high nibble datafrom ROM that addressed by DMA0 ~ DMA2.SCALER2 1FH R/W 0000TM2ALD T2DIV2T2DIV1T2DIV0T2DIV2~0: The pre-scaler of Timer 2 ( F MCK = MCU operating clock ) T2DIV2T2DIV1 T2DIV0 TM2CK 0 0 0 F MCK /256 0 0 1 F MCK /128 0 1 0 F MCK /64 0 1 1 F MCK /32 1 0 0 F MCK /16 1 0 1 F MCK /8 1 1 0 F MCK /4 11 1 F MCK /2TM2ALD: Timer 2 auto load control0 : Timer 2 auto load function turned off 1 : Timer 2 auto load function turned onUSERSRAM256 nibbles20H~ 3FHR/W XXXXSRAM.3 SRAM.2SRAM.1SRAM.0User SRAM, MAH = 0~7H, use MAH to change SRAM page. 5.5 Extended I/OTR4P153BT/BF is provided one special instruction “LD EXIO (n), A”, where n = 00H ~ 0FH” to obtain the16 extra I/O registers. These registers are used for the I/O port pull up or down resistors control and can be accessed by two “LD” data transfer instruction only.For example, to enable the pull up resistor of port A, the program should be as below: LD A, #FH LD EXIO (00H), ARTCEN OPTION TM1ENTM2EN Wake up ( JMP $04H )U: unchanged X: unknown value R/W: readable & writeable R: readable only W: writeable only Symbol Addr R/W Reset D3 D2D1D0DescriptionPAPU 00H W 0000 PAPU.3 PAPU.2PAPU.1PAPU.0PA2~PA0 pull up 100K ohm resistorPA3 pull up 60K ohm resistor0: Port A pull up resistor disabled1: Port A pull up resistor enabledPAPL 01H W 0000 PAPL.3 PAPL.2PAPL.1PAPL.0Port A pull down 100K ohm resistor0: Port A pull down resistor disabled1: Port A pull down resistor enabledPBPU 02H W 0000 PBPU.3 PBPU.2PBPU.1PBPU.0Port B pull up 100K ohm resistor0: Port B pull up resistor disabled1: Port B pull up resistor enabledPBPL 03H W 0000 PBPL.3 PBPL.2PBPL.1PBPL.0Port B pull down 100K ohm resistor0: Port B pull down resistor disabled1: Port B pull down resistor enabledPDPU 04H W 0000 PDPU.3 PDPU.2PDPU.1PDPU.0Port D pull up 100K ohm resistor0: Port D pull up resistor disabled1: Port D pull up resistor enabledPDPL 05H W 0000 PDPL.3 PDPL.2PDPL.1PDPL.0Port D pull down 100K ohm resistor0: Port D pull down resistor disabled1: Port D pull down resistor enabledPAWK 06H W 0000 PAWK.3 PAWK.2PAWK.1PAWK.0Port A wake up enable control0: Port A wake up disabled1: Port A wake up enabledPBWK 07H W 0000 PBWK.3 PBWK.2PBWK.1PBWK.0Port B wake up enable control0: Port B wake up disabled1: Port B wake up enabledPDWK 08H W 0000 PDWK.3 PDWK.2PDWK.1PDWK.0Port D wake up enable control0: Port D wake up disabled1: Port D wake up enabledReserved 09H~0FHReserved5.6 Interrupt ProcessingInterrupt vector address definitionEvent Vector AddressRESET 00HSystem reserved 02HWAKE UP 04HSystem reserved 06HTimer1(PWM)/Timer2/RTC 08HWhen any interrupt requestflag ( RTCFG, TM1IFG,TM2IFG ) is set to “1”.Interrupt would happen or not.It depends on the interruptmask (TM1MSK, TM2MSK)and global interrupt enable(ENINT) setting. If interruptmask set to “1” and globalinterrupt enable set to “1”,Interrupt will be accepted onthe next clock after theseinterrupt request flag set to“1”. The following fourprocedures are done in one clock cycle by hardware as shown below:ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.1. Program Counter, MAH, PCDH and C/Z will be stored in special hardware registers.2. Program counter will be changed to the corresponding interrupt vector address.3. The global interrupt enable register ENINT is automatically stored in special hardware register byhardware.4. ENINT is cleared to “0”, so interrupt control circuit will be disabled by hardware to avoid unwantedinterrupt in interrupt handling routine.When interrupt service routine was finished, an RETI instruction will perform the procedures by hardware as shown below:1. Restore the Program Counter, MAH, PCDH and C/Z, which were stored when interrupt happened.2. The global interrupt enable register ENINT is restore from special register which is stored beforeinterrupt by hardware automatically. This will allow subsequent Interrupt to happen.The corresponding interrupt request flag must be cleared to “0” by software, before executing RETI instruction. Otherwise, the interrupt procedure will be executed again.In normal case, if the interrupt accepted by this chip and program jumps into interrupt service routing,the register ENINT must be “1”. It will not accept the interrupt when register ENINT is equal to “0”.But when clearing ENINT instruction (disable interrupt) is executed, and interrupt happened at next cycle, then the interrupt may still be accepted. This will sometimes causes fault. To avoid this, one "NOP" instruction right after "ENINT clear" is needed.Notice: Be very careful on the next instruction right after interrupt disabled ( ENINT = 0 ) or timer interrupt mask(TM1MSK=0 or TM2MSK=0). If this instruction contains global variable that is used in both main program and interrupt routine, then it may not work properly (as described above). To ensure the correct operation, one “NOP” instruction right after clearing register ENINT orTM1MSK,TM2MSK (set to zero) is needed.Example: (1) before modified…….CLR #1, (SYS0) ; clear ENINT to zero ( or TM1MSK=0 or TM2MSK=0 )SET #1,(XXX) ; XXX is global variable, interrupt may be accepted at this line and jump to; interrupt service routing after this instruction (SET #1(xx) ) executed; successfully. This will be incorrect.(2) after modified…….CLR #1, (SYS0) ; clear ENINT to zero ( or TM1MSK=0 or TM2MSK=0 )NOP ; inserted one “NOP” instruction, and ensure next instruction; SET #1,(XX) is executed after interrupt disabled ( ENINT=0 )SET #1,(XXX) ; XXX is global variable.5.7 Operation modeTR4P153BT/BF is provided 3 different modes for low power consumption management by switching around NORMAL mode, GREEN mode and HALT mode.Commom I/O control registerSymbol Addr R/W Reset D3 D2 D1 D0 DescriptionMDCTL 10H W 1100 MD1 MD0 X X MCU operation mode control register. Notice: After reset MD1, MD0 = 11, it’s meaningless. Don’t write MD1,MD0=11 to this register. There are three operation modes which are defined at the following table. It can be changed from NORMAL mode to HALT mode or GREEN mode for power saving by setting MD [1:0] of register MDCTL.ALL RIGHTS STRICTLY RESERVED, ANY PORTION IN THIS PAPER SHALL NOT BE REPRODUCED, COPIED WITHOUT PERMISSION.。