基才FPGA的DDSIP核设计

基于FPGA的DDS设计

基于FPGA的DDS设计初始频率设置为7.3682307MHz,系统频率为100MHz,根据DDS输出频率公式能计算出相位累加字:其中f为DDS输出频率;fclk为DDS系统频率;N为相位累加器的位数;DATA为相位累加器的累加值。

要得到7.3682307MHz的输出频率,相位累加值DATA=(100101101110011010111111110101101101111011100)2FPGA采用Xilinx Spartan3E XC3S500E,IP核+VerilogHDL+Sch编程。

下图为整个FPGA的原理框图:DCM_100MHz其中DCM_100MHz用了Spartan3E里面的DCM(时钟管理单元),由于输入的时钟为有正负的正弦波(100MHz 幅值5V 峰峰10V的正弦信号),所以经过DCM后,能得到一个很好的方波。

输出100MHz给DA作为DA的时钟,其中还经过一个BUFG,目的是使ROM的正弦数据输出稳定后,时钟才到来,DA才能读入数字值,这可以参考AD9744的Datasheet其中ts至少为2.0ns,如果少于2.0ns或时钟和DA数据同时甚至提前到达的话,DA 输出的模拟值会出错。

所以要加一个BUFG,但BUFG延时不太确定,.....(方面的我还不懂L)MCU_FPGA51单片机通过串口接受PC机给出的DATA(相位累加值),再通过与FPGA的通信,告诉FPGA相位累加模块(Accumulator)累加值。

MCU_FPGA所做的工作是把收到的数据出入模块内的ROM里,使得改变模块里的ROM地址,就能改变输出的累加值。

FPGA_MCU通信的时序为:DIN:48位累加值串行输入CLK_WR:输入写信号时钟,DIN的数据稳定后,CLK_WR上升沿写入FPGA内部的寄存器,寄存器的数据移位。

DIN_PRO:写保护,DIN_PRO=0时,模块内ROM的输出随地址变化而变化;DIN_PRO=1,模块内ROM的输出锁存,输出保持DIN_PRO=0时ROM地址所对应的ROM 值。

基才FPGA的DDSIP核设计

基才FPGA的DDSIP核设计石建平【摘要】以Ahera公司的QuartusⅡ7.2作为开发工具,研究了基于FPGA的DDSIP核设计,并给出基于SignalTapⅡ嵌入式逻辑分析仪的仿真测试结果。

将设计的DDSIP核封装成为SOPC Builder自定义的组件.结合32位嵌入式CPU 软核NiosⅡ,构成可编程片上系统(SOPC),利用极少的硬件资源实现了可重构信号源。

该系统基本功能都在FPGA芯片内完成,利用SOPC技术,在一片FPGA芯片上实现了整个信号源的硬件开发平台,达到既简化电路设计、又提高系统稳定性和可靠性的目的。

%The method of developing DDS IP core based on FPGA is studied in this paper making use of development tools Quartus Ⅱ 7.2 of Altera company, the simulation result is also given. Taking Nios Ⅱ soft-core as a CPU and combining a DDS IP core that is encapsulated in SOPC Builder component, a system on programmable chip (SOPC) is built to realize a signal generator. Most of the functions are completed in the FPGA, using SOPC technology to design hardware development platform of signal generator with only one FPGA chip so as to simplify design and to develop the stability and reliability of the system.【期刊名称】《电子设计工程》【年(卷),期】2012(020)005【总页数】4页(P184-186,189)【关键词】直接数字频率合成;现场可编程门阵列;Nios;Ⅱ;可编程片上系统【作者】石建平【作者单位】毕节职业技术学院,贵州毕节551700【正文语种】中文【中图分类】TP348SOPC (System on a Programmable Chip,片上可编程系统)[1]是Altera公司提出的一种灵活、高效的SOC解决方案。

基于FPGA的DDS信号发生器设计分析

基于FPGA的DDS信号发生器设计分析摘要:随着现代电子技术的飞速发展,直接数字频率合成DDS 技术逐渐被广泛使用,DDS 是目前数据调度常用的数据分发技术,此技术能够有效结合数据服务质量要求,完成数据分发操作。

为此提出基于FPGA的DDS信号发生器设计,以提升信号发生器精度效果。

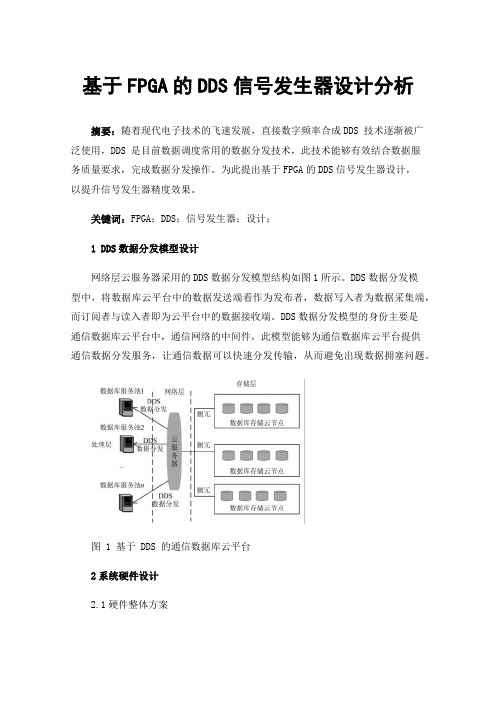

关键词:FPGA;DDS;信号发生器;设计;1 DDS数据分发模型设计网络层云服务器采用的DDS数据分发模型结构如图1所示。

DDS数据分发模型中,将数据库云平台中的数据发送端看作为发布者,数据写入者为数据采集端,而订阅者与读入者即为云平台中的数据接收端。

DDS数据分发模型的身份主要是通信数据库云平台中,通信网络的中间件,此模型能够为通信数据库云平台提供通信数据分发服务,让通信数据可以快速分发传输,从而避免出现数据拥塞问题。

图 1 基于 DDS 的通信数据库云平台2系统硬件设计2.1硬件整体方案函数信号发生器的硬件系统主要包括MCU控制电路,FPGA构成的DDS发生器、DAC转换和低通滤波电路,及一些用于输入输出的器件等。

按键输入和LCD输出显示主要由MCU负责控制,MCU然后将输入的信号运算处理后发送给FPGA,FPGA根据输入的各种参数在ROM表中寻址,同时输出对应控制的波形、频率和幅度的数字信号,最后经过DA转换为对应的模拟电压信号,在经过一个低通滤波器使得模拟电压信号变得平滑。

2.2硬件模块电路系统的硬件电路主要分为两个部分,一是系统主控电路,二是DDS信号发生器电路。

系统主控电路包括以STM32F103C8T6为主控的最小系统板、四路用户按键输入、OLED显示屏输出(SPI)、UART通信连接上位机、硬件SPI连接FPGA负责信号数据传输。

DDS信号发生器电路,其中的FPGA模块的核心芯片为LatticeLCMXO2-4000HC-4MG132,其模块上内置8路输出LED指示灯、4路按键输入、4路拨码输入和两位数码管输出灯资源。

基于FPGA的DDS信号发生器设计

基于FPGA的DDS信号发生器设计随着数字信号处理(DSP)技术的发展,直接数字频率合成器(DDS)逐渐取代了传统的频率合成器,成为一种高性能的信号发生器。

DDS信号发生器通过数字信号直接产生模拟信号,具有频率精度高、可编程性强和快速调频等优点。

本文将通过FPGA实现DDS信号发生器的设计。

首先,我们需要了解DDS信号发生器的基本原理。

DDS信号发生器的核心是相位累加器、查找表和数模转换器(DAC)。

通过累加器产生相位累积,将相位累积的结果通过查找表得到对应的振幅值,并经过数模转换器输出模拟信号。

1.确定需要生成的信号的参数,包括输出频率、相位步进精度、振幅等。

根据这些参数,计算累加器的增量值,即每个时钟周期累加器需要累加的值。

2.在FPGA中设计相位累加器。

相位累加器的宽度取决于相位步进精度,一般为32位或64位。

通过在每个时钟周期加上增量值,实现相位的累加。

3.设计查找表。

查找表的大小取决于数字信号的分辨率,一般为2^N 位。

通过输入相位值查找对应的振幅值。

4.设计数模转换器(DAC)。

通过DAC将数字信号转换为模拟信号输出。

5.在FPGA中实现控制逻辑,包括控制相位累加器和查找表的读写操作,使其按照设定的参数进行相位累加和振幅输出。

6.将设计好的FPGA模块进行综合、布局和时序约束,生成比特流文件。

通过以上步骤,基于FPGA的DDS信号发生器的设计就完成了。

设计好的FPGA模块可以实现高精度、高稳定性的信号发生器,广泛应用于通信、雷达、医疗设备等领域。

需要注意的是,在设计过程中需要考虑到FPGA的资源限制,包括LUT资源的利用、频率分辨率和输出频率的限制等。

此外,还可以通过增加相位累积周期、使用多路查找表和多路DAC等方法进一步优化设计。

综上所述,基于FPGA的DDS信号发生器设计是一个较为复杂的过程,需要对DDS原理有深入的理解,并结合FPGA的特点进行设计。

通过合理的设计和优化,可以实现高性能的DDS信号发生器。

基于FPGA的DDS设计报告

DDS设计报告摘要:DDS信号发生器能够产生多种波形,如三角波、锯齿波、矩形波(含方波)、正弦波的电路被称为函数信号发生器。

随着可编程逻辑器件(FPGA)的不断发展,直接频率合成(DDS)技术应用的愈加成熟,利用DDS原理在FPGA平台上开发高性能的多种波形信号发生器与基于DDS芯片的信号发生器相比,成本更低,操作更加灵活,而且还能根据要求在线更新配置,系统开发趋于软件化、自定义化。

本文研究了基于FPGA的DDS信号发生器设计,实现了满足预定指标的多波形输出。

同时采用STM32来进行控制频率,幅度的输入以及对波形类型,频率,幅度值进行显示,从而很好地实现了人机交界。

关键字:DDS信号发生器FPGA STM32 频率幅度值目录1.系统设计 (3)1.1设计要求 (3)1.1.1任务 (3)1.1.2要求 (3)1.1.3说明 (3)1.2总体设计方案……………………………………………………………………………………………………..1.2.1设计思路…………………………………………………………………………………………………1.2.2方案论证与比较……………………………………………………………………………………….1.2.3系统组成…………………………………………………………………………………………………..2.单元硬件电路设计………………………………………………………………………………………………………2.1电路的设计…………………………………………………………………………………………………….2.2……………………………………………………………………………………………………..2.3………………………………………………………………………………………………………2.4……………………………………………………………………………………………………….3.软件设计……………………………………………………………………………………………………………………..3.1软件设计与硬件设计的关系…………………………………………………………………………………3.2部分程序设计…………………………………………………………………………………………………..3.3部分程序设计………………………………………………………………………………………………….4.系统测试…………………………………………………………………………………………………………………………4.1测试使用的仪器…………………………………………………………………………………………………….4.2指标测试和测试结果…………………………………………………………………………………………….4.3结果分析………………………………………………………………………………………………………………..5.结论………………………………………………………………………………………………………………………………. 参考文献………………………………………………………………………………………………………………………………附录1 主要元器件清单……………………………………………………………………………………………………附录2 电路原理图及印刷板图……………………………………………………………………………………….附录3 程序清单………………………………………………………………………………………………………………..1.系统设计1.1设计要求1.1.1设计任务设计并制作一个波形发生器,该波形发生器能产生正弦波、方波、三角波和由用户编辑的特定波形形状。

FPGA DDS IP核实现_单频 线性调频

FPGA DDS IP 核实现DDS (Direct Digital Synthesizer ),即直接数字频率合成器,本文主要介绍如何调用Xilinx 的DDS IP 核生成某一频率的Sin 和Cos 信号,以及LFM 信号。

1.相关参数的介绍及求解(1)DDS 输出频率输出频率out f 是系统时钟频率clk f 、相位累加器中相位数据位宽)(n B θ和相位增量θ∆的函数。

)(2n B clk out f f θθ∆=因此,要得到输出频率out f ,要求相位增量θ∆为clk Bout f f n )(2θθ=∆如果要采用时分复用的多个通道,则降低每个通道的有效时钟效率。

对于C 个通道,要求相位增量为clk Bout f Cf n )(2θθ=∆(2)频率分辨率频率分辨率f ∆是系统时钟频率clk f 和相位累加器数据位宽)(n B θ的函数。

)(2n B clk f f θ=∆对于时分复用的多通道,频率分辨率随通道数的增加而提高,对于C 个通道:Cf f n B clk )(2θ=∆(3)相位增量相位增量值是无符号的,当相位增量值与相位位宽匹配时,也可以将其看作有符号数。

假设相位增量和相位数据位宽均为N ,如果看成无符号数,范围由0到N 2表示的是(] 3600,的角度范围;如果看成有符号数,则范围变成)1(2--N 到)1(2-N ,相位表示的是[) 180180,-的角度范围。

根据正弦信号的周期性和对称性,两种表示范围内的信号采样是一致的。

相位增量定义了综合其的输出频率。

相位增量是系统时钟频率clk f 、输出频率out f 和相位数据位宽)(n B θ的函数。

clk B out f f n )(2θθ=∆2.线性调频信号线性调频信号的时间函数表达式可表示为2,2[)],2(exp[)(20T T t Kt t f j t s -∈+=ππ其瞬时频率为]2,2[,)(21)(0T T t Kt f t dt d t f -∈+==ϕπ其中,TB K =,B 为信号调频宽度,T 为信号脉宽。

《基于FPGA的PLL+DDS的频率合成器》范文

《基于FPGA的PLL+DDS的频率合成器》篇一一、引言随着通信技术的飞速发展,频率合成器作为电子系统中的关键部件,其性能和稳定性直接影响到整个系统的性能。

本文将详细介绍一种基于FPGA(现场可编程门阵列)的PLL(锁相环)+DDS(直接数字合成器)的频率合成器,并对其设计原理、实现方法及性能优势进行深入探讨。

二、PLL+DDS频率合成器的工作原理PLL+DDS频率合成器通过将PLL与DDS结合,利用两者的优势来达到高精度、高稳定性的频率输出。

PLL模块主要负责跟踪和生成参考频率,而DDS模块则能够快速生成多种频率的波形。

FPGA作为核心控制器,负责协调PLL和DDS模块的工作,实现频率的合成和输出。

三、设计实现1. 硬件设计在硬件设计方面,PLL+DDS频率合成器主要包含FPGA、PLL模块、DDS模块以及输出电路等部分。

其中,FPGA作为核心控制器,负责协调整个系统的运行。

PLL模块采用高精度的锁相环电路,以实现稳定的参考频率输出。

DDS模块则采用数字方式生成多种频率的波形。

2. 软件设计在软件设计方面,需要编写FPGA的程序代码来实现对PLL 和DDS模块的控制。

通过配置FPGA的IO口,实现对PLL和DDS模块的驱动和控制。

同时,还需要编写相应的算法程序,以实现频率的合成和输出。

四、性能优势基于FPGA的PLL+DDS频率合成器具有以下优势:1. 高精度:PLL和DDS的结合使得频率合成器具有高精度的频率输出。

2. 高稳定性:通过PLL模块的锁相环电路,可以实现稳定的参考频率输出,从而提高整个系统的稳定性。

3. 快速响应:DDS模块采用数字方式生成波形,具有快速响应的特点,可以快速调整输出频率。

4. 灵活性:FPGA的可编程性使得频率合成器具有很高的灵活性,可以方便地实现多种功能的扩展和升级。

五、应用领域基于FPGA的PLL+DDS频率合成器在通信、雷达、电子测量等领域具有广泛的应用。

例如,在通信系统中,它可以为基站提供稳定的射频信号;在雷达系统中,它可以为雷达提供精确的扫描频率;在电子测量领域,它可以用于信号源的生成和测试等。

《基于FPGA的PLL+DDS的频率合成器》范文

《基于FPGA的PLL+DDS的频率合成器》篇一一、引言随着现代电子技术的飞速发展,频率合成器作为电子系统中的关键部件,其性能的优劣直接影响到整个系统的稳定性和可靠性。

传统的频率合成器往往存在体积大、功耗高、灵活性差等问题。

因此,研究和开发新型的、高性能的频率合成器显得尤为重要。

本文将介绍一种基于FPGA的PLL+DDS的频率合成器,并对其原理、设计、实现及应用进行详细阐述。

二、PLL+DDS原理PLL(Phase-Locked Loop)即锁相环,是一种用于实现两个信号相位同步的电路。

DDS(Direct Digital Synthesizer)即直接数字合成器,是一种通过数字方式产生正弦波等信号的技术。

将PLL和DDS结合起来,可以实现高精度、高稳定性的频率合成。

在基于FPGA的PLL+DDS的频率合成器中,PLL负责跟踪输入信号的频率和相位,将其锁定在目标频率上。

DDS则通过数字方式产生所需的信号波形。

两者的结合,可以在保持高精度的同时,实现快速的频率切换和调节。

三、设计实现1. 硬件设计硬件设计主要包括FPGA芯片、PLL芯片、DDS芯片及其他辅助电路。

其中,FPGA芯片作为核心控制器,负责整个系统的协调和控制。

PLL芯片和DDS芯片分别负责实现锁相和数字波形产生功能。

2. 软件设计软件设计主要包括FPGA的程序设计。

程序设计需要实现对输入信号的采集、处理、控制等功能。

同时,还需要对PLL和DDS进行配置和控制,以实现所需的频率合成功能。

四、性能分析基于FPGA的PLL+DDS的频率合成器具有以下优点:1. 高精度:由于采用了PLL和DDS技术,可以实现高精度的频率合成。

2. 高稳定性:PLL的锁相功能可以保证输出信号的稳定性和一致性。

3. 灵活性好:通过FPGA的控制,可以实现快速的频率切换和调节。

4. 体积小、功耗低:相比于传统的频率合成器,该设计具有更小的体积和更低的功耗。

五、应用领域基于FPGA的PLL+DDS的频率合成器广泛应用于通信、雷达、电子对抗、测控等领域。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

De i n fDDS I c r s d o FPGA sl O  ̄ P o e ba e n

S inpn HIJa — ig

( பைடு நூலகம் ct nl n eh i l f , o 5 7 0 C i ) 哟 oao a ad Tcnc f i a e B ' 5 10 , hn i e a

g n r tr Mo t f h n t n r o l td i eF GA, sn OP c n l g e in h r wae d v l p n l t r e e ao . s o e f c i sa e c mp ee n t P t u o h u i g S C t h o o y t d s a d r e e o me t af m e o g p o

摘要 :以 A ea 司的 Q atsI 72作为开发工具 。 究 了基 于 F G hr公 u r I . u 研 P A的 D SI 设计 . D P核 并给 出基 于 Sg a T pI i l a I n

嵌 入 式 逻 辑 分 析 仪 的仿 真 测试 结 果 。 将 设 计 的 D SI D P核 封 装 成 为 S P ule O C B i r自定 义 的 组 件 。 结合 3 d 2位 嵌 入 式

Ab t a t h t o fd v lp n S I o e b s d o P sr c :T e meh d o e eo ig DD P c r a e n F GA ssu id i h s p p rma i g u e o e e o me t o l i t d e n t i a e k n s fd v l p n os t

第2 0卷 第 5期

Vo .O 1 2

No5 .

电子 设计 工程

El c r n c De in En i e rn e to i sg g n e i g

21 0 2年 3月

Ma . r 201 2

基才 F GA 的 D P核设计 P DSI

石 建 平

( 节职 业 技 术 学 院 贵 州 毕 节 5 10 ) 毕 5 7 0

o i a e ea o t n yo e F G c i oa i l y d sg n e eo esa i t dr l b l yo es s m. f g l n rt r h o l n P A hp s s osmp i e i a d t d v lp t t b l ya i i t f y t sn g wi t f n o h i n ea i h t e

Q a u . o lr o p n ,te i ua o slias i n T kn i o-oe s P n o bnn D u  ̄ sI 2 f t acm ay h m linr uts l gv . aigNo Isfc r a C U adcm ii aD S I7 A e s t e o e sI t a g

S P (yt o r a m beC i, 片 上 可 编 程 系 O C S s m naPo m al h e r g p 统 )] A e 【 1 是 hr a公 司提 出 的 一 种 灵 活 、 效 的 S C解 决 方 案 。 高 O 它 将 处 理 器 、存 储 器 、0 接 口 、V S C R 等 系 统 设 计 需 要 I , L D 、D 的功 能 模 块 集 成 到 一 个 可 编 程 逻 辑 器 件 上 . 建 一 个 可 编 程 构 的 片 上 系 统 。 它 具 有 灵 活 的 设 计 方 式 , 硬 件 可 裁 减 、 扩 软 可 充 、 升级 . 具备软硬件在系统可编程 的功能。S P 可 并 O C的 核 心 器 件 F G 已 经 发 展 成 一 种 实用 技 术 。 系 统 设 计 者 把 开 PA 让 发 新 产 品 的 时 问 和 风 险 降 到 最 小 。最 重 要 的是 , 有 现 场 可 具

K y w r s D rc D g a F e u n yS n e s ( D ) FedP o a ma l G t A r ( P A) N o I S s m o e o d : i t i t rq e c y t d i D S ; i rg m b e ae r y F G ; i I; y t na e i l h s l r a s e Po a a l C i S P ) rg mm be hp( O C r

C U软 核 No , 成 可 编 程 片 上 系 统 (O C , 用极 少 的 硬 件 资 源 实现 了可 重 构 信 号 源 。 该 系统 基 本 功 能都 在 P i I构 sI S P )利

F G 芯 片 内完 成 , 用 S P P A 利 O C技 术 , 一 片 F G 芯 片上 实现 了整 个 信 号 源 的硬 件 开 发 平 台, 到 既 简化 电路 设 计 、 在 P A 达 又 提 高 系统 稳 定 性 和 可 靠性 的 目的 。 关 键 词 :直接 数 字 频 率 合 成 ; 场 可编 程 门 阵列 ; i ; 编 程 片 上 系统 现 No I 可 sI 中 图 分 类 号 : P 4 T 38 文献标识码 : A 文 章 编 号 : 6 4 63 (0 2 0 — 14 0 1 7 — 2 6 2 1 )5 0 8 — 3