spra958f

TMS320C28x MCU 快速入门指南

On-board XDS100TMS320F28027Pins Emulator4. ControlSUITE 介绍和 LED 闪烁例程开发仿真调试C2000 的开发工具软件包 (controlSUITE) 可以创建开放式平台,提供特定于器件的外设配置包,它包含基础软件和示例,可帮助您立即开始项目开发。

运行 ControlSUITE安装程序并选择想要使用的软件包,所有相关项都将自动下载和安装。

具体介绍可参照安装后目录下的 controlSUITE™ Getting Started Guide 和 ControlSUITE™ Software 文档。

与 ControlSTICK 配套的开发包(controlSTICK Software )同样可以从TI 的网站免费下载,安装后在目录..\Piccolo controlSTICK 下找到软件示例项目、完整硬件文档和参考应用文档。

在..\Piccolo controlSTICK\<project name> 的目录下可以找到 <project name>.pdf 文档,其介绍了ControlSTICK 的配置和应用。

启动 CCSV4.1 软件 (Start->All Program->Texas Instruments->Code Composer Studio V4.1.2)用 Project->Import Legacy CCSv3.3 Project 打开..\Piccolo controlSTICK\Timer – BlinkingLED\ BlinkingLED.pjt 项目工程文件。

如前一节所描述建立对应的 XDS100V1 目标配置文件 File->New->Target Configuration File 。

用 Project->Rebuild All 编译和连接源文件生成目标代码 <project name>.out 。

CORONA 2.4GHz Spread Spectrum (FASST COMPATIBLE) R

CORONA 2.4GHz Spread Spectrum (FASST COMPATIBLE)Receiver Instruction Manual for R4FA‐SB and R6FA‐SB Compatibility:The CORONA 2.4GHz Spread Spectrum FASST Compatible Receiver is designed for use with FUTABA’s FASST 2.4GHz transmitters; including the 3PM,3PKS,3VCS,3GR,4PK(S),TM7, TM8, TM10, TM14 and the T6EX‐2.4G, 7C‐2.4G, 8FG, 10CG, 12FG. The R4FA‐SB and R6FA‐SB receivers supply a more useful mode for users. Both the R4FA‐SB and R6FA‐SB support FUTABA’s FASST air system and surface system. The R4FA‐SB supports 7‐channel with continuous PPM (positive and negative) output ,RSSI output and S.BUS output, R6FA‐SB supports 6 channel high speed PPM(HS) mode to optimize helicopter response control and S.BUS output.Under S.BUS output mode, both R4FA‐SB and R6FA‐SB supply 12 proportional channels and 2 DG channels. Therefore, the R4FA‐SB or R6FA‐SB becomes 14‐channel receivers when using S.BUS output.Specifications:Operating Current: 50mA maxOperating Voltage: 3.6 ~10VLatency: R4FA‐SB’s description14mS for independent 4 channel output and S.BUS output @ FASST multi‐channel mode21mS for Continuous PPM output and RSSI output@ FASST multi‐channel mode16mS for independent 4 channel output and S.BUS output @ FASST 7ch mode24mS for Continuous PPM output and RSSI output@ FASST 7ch mode14mS for independent 3 channel output@ FASST surface system C1 CODE modeR6FA‐SB’s description7mS for independent 6 channel (HS) output@ FASST multi‐channel mode14mS for independent 7 channel (LS) output and S.BUS output @ FASST multi‐channel mode 8ms for independent 6 channel (HS) output@ FASST 7ch mode16mS for independent 7 channel (LS) output and S.BUS output @ FASST 7ch mode14ms for independent 3 channel output@ FASST surface system C1 CODE modeSensitivity: about ‐100dBmOperation temperature:‐10~80 deg CSetup:Bind procedure:∙Turn on the FASST transmitter∙Connect the battery to the receiver while pressing the receiver’s F/S button.∙The Dual‐color LED’s will continuously cycle through the following:o Red LED light (searching radio signal)o Green LED light (acquired the radio signal)o Red LED off (bind ok)o Green LED flashes 10 times (ID stored in memory)o Green LED lights solid (normal operation)Note: FASST surface systems take a bit more time to complete the bind procedure.Fail‐safe setting:There are two ways to set the Failsafe setting on the CORONA 2.4GHz Spread Spectrum FASST Compatible Receiver;1.TX‐failsafe feature: This method sets the failsafe on the FASST transmitter and has priority (works onchannel 3 only under FASST 7ch mode or on multiple‐channels under FASST multi‐channel mode) while the receiver is on, just like FUTABA receivers (only available on FASST air system).2.RX‐failsafe feature: Turn on the FASST transmitter and then turn on the CORONA 2.4GHz Spread SpectrumReceiver, put all the sticks and switches to control inputs you want if the receiver looses signal and Press the F/S button down for about 5 ‐ 6 seconds while the Green LED lights solid (Rx in normal operation), then release the button. You will see the Red LED will flash for about 4 ‐ 5 seconds. (Note: The Red LED will FLASH high speed to indicate the RX‐failsafe is turned on OR FLASH low speed to indicate the RX‐failsafe is turned off). If you press the F/S button a second time while the Red LED is flashing, the receiver will change its RX‐failsafe status (on / off), then the LED will return to Green solid again. If you not press the F/S button, nothing will be changed and the LED will return to solid Green. If you want to cancel the RX‐failsafe feature (not just turn it off), you can do so by binding the receiver again. After binding operation the receiver will be back to factory settings without any failsafe feature.Note: If you do not set a failsafe setting, the receiver will hold all controls at the position of the last command received before signal was lost. When RX‐failsafe is turned on, the receiver will initiate the RX‐failsafe settings after loosing signal for over 1 second and the receiver will hold the last received positions until the failsafe takes over. When the RX‐failsafe and TX‐failsafe feature are both turned on, the receiver will use the TX‐failsafe command.We highly recommend you set failsafe feature before flying your models. An example of a minimal useful, failsafe setting would be to shut down the model’s throttle, so that it does not fly or drive away uncontrolled.Output mode setting (only available on FASST air system):Turn off the transmitter, connect the battery to the receiver, you will see the Red LED light flashing. The RED LED flashes at high speed to indicate the receiver is in the special output mode OR a Low speed indicates the receiver is under (LS) low speed PPM normal output mode, press the F/S button for 5‐6 seconds while the Green LED is off (Rx in signal searching status), then release the button. You will see the Green LED flash for about 4 ‐ 5 seconds. (Note: The Green LED will FLASH high speed under special mode OR FLASH low speed under normal output mode). If you press the F/S button a second time while the Green LED is flashing, the receiver will change its output mode status (special/normal), if you do not press the F/S button the output mode will not be changed and the Red LED will flash at its original speed.Note: Output mode function is described in the form below,R4FA‐SB R6FA‐SBnormal Ch1~CH4 independent PPM output normal Ch1~CH7 independent PPM outputCH1 Neg CPPM out(FUTABA trainer FUNC)^1 CH2 Pos CPPM out for special user^2 CH1~CH6 independent high speed(HS)PPM out for helicopter fast response controlCH3 RSSI PWM out for FPV()^3 specialCH4 S.BUS output for compact system specialCH7 S.BUS output for compact systemNote: ^1 refer the signal description picture below^2 refer the signal description picture below^3 refer the signal description picture belowRSSI PWM out define: Pulse width from about 900uS~ 2100uS to indicate RSSI strength from ‐100dBm~‐40dBm.Important Note: If you are using analog servos in your model you must keep your receiver under the factory settings (normal output mode) or your analog servo will get hot and possibly burn out. As well you cannot use a non S.BUS servo on a channel while S.BUS signal output present.LED status indicated under normal working status:RED LED GREEN LED Statusflash off No signal searchedoff solid Signal is very goodSometime flash solid Signal is not very goodflash flash Signal is weak。

SSD-XDS510PLUS仿真器安装、使用指南_2.x

本仿真器支持 TI 的 C2000、C5000、C6000 系列芯片

※TMS320LF24xx TMS320F28xx TMS320VC54xx ※TMS320C67xx ※TMS320C64xx

※TI OMAP

2

感谢你使用索思达电子(SSDDSP)产品: 使用前请您对照仿真器型号仔细阅读本手册。 该手册协助您正确的将 XDS510 仿真器及软件安装在您的计算机上。 索思达电子(SSDDSP)产品在出厂前经过严格的测试,使用中遇到问题请随时同我公司联系。 您的问题可以通过我公司的网站 的 FAQ 得到及时的答复;可以将问题提交到 ssddsp@,web_61ic@ 得到直至您满意的 服务。 在线技术支持 QQ: 客服 A:66860430 客服 B:84569832

4. 单击 Install命令

11

5. 单击finish命令

12

1.2.2 SSD-XDS510PLUS 仿真器硬件设备安装 1. 安装准备 用所提供的USB连接线将XDS510PLUS仿真器与电脑主机相连。 2. 安装过程 将仿真器的USB口插入PC机端口后系统会自动提示安装‘找到新的硬件向导’; 单击‘下 一 步’ ,按照提示进行仿真器硬件的安装。

品种全

※对不同种类的 DSP 芯片,您无需重复购买硬件设备,只需改换不同的 DSP 开发软 件,一机多用,同时每种软件均支持 C 语言和汇编源码调试。

通用性

※XDS510 PLUS 的硬件设计采用超大规模集成电路技术,功能强大,性能可靠,同时仿真 控制板和仿真头(POD)之间设计有多级缓冲驱动,大大增强了系统的安全性和可靠性。

2010

Flash程序如何下载到RAM中

从上面的一段看出,如果需要配置FLASH的寄存器,必须执行FLASH以外存储

空间的程序才可以实现,我又发现这些寄存器是受EALLOW和CSM保护的,所以我按照

以下步骤试图重新配置寄存器:

1,在执行存放于FLASH中的主程序段时,将一段存于FLASH中的初始化flash

* Function: InitFlash()

* Description: Initializes the F281x flash timing registers.

* Notes:

* 1) This function MUST be executed out of RAM. Executing it out of

&secureRamFuncs_loadend -

&secureRamFuncs_loadstart);

InitFlash();

烧到内部flash中速度慢是不是没有设置flash的配置寄存器?可参考如上设置

{

asm(" EALLOW";

// Enable EALLOW protected register access

/*** Force a complete pipeline flush to ensure that the write to the last

register

configured occurs before returning. Safest thing is to wait 8 full

FlashRegs.FPWR.bit.PWR = 3;

// Pump and bank set to active mode

TMS320f280x 数据手册NEW

TMS320F2809, TMS320F2808, TMS320F2806, TMS320F2802, TMS320F2801TMS320C2802, TMS320C2801,and TMS320F2801x DSPs数据手册著作编号:SPRS230J2003年-2007年9月修正除非有其他说明,本文档中包含了自发布日起的产品数据信息。

同时,产品也与德州仪器的每期标准规范说明书一致。

对产品的处理不包括所有参数的测试。

目录修订历史1 F280x,C2801x,C280x DSPs1.1特点1.2商标2 介绍2.1 引脚分配2.2 信号描述3 功能概况3.1 内存映射3.2 简单描述3.2.1 C28X CPU3.2.2 存储器总线(哈佛总线结构)3.2.3 外设总线3.2.4 实时JTAG接口和分析3.2.5 FLASH存储器3.2.6 ROM存储器3.2.7 M0,M1 SARAMs3.2.8 L0,L1,H0 SARAMs3.2.9 BOOT ROM3.2.10 安全性3.2.11 外设中断扩展(PIE)模块3.2.12 外部中断(XINT1,XINT2,XNMI)3.2.13 振荡器和锁相环(PLL)电路3.2.14 看门狗3.2.15 外部时钟3.2.16 低功耗模式3.2.17 外设框架3.2.18 通用输入输出(GPIO)复用引脚3.2.19 32位CPU定时器(0,1,2)3.2.20 控制外设3.2.21 串口外设3.3 寄存器映射3.4 器件仿真寄存器3.5 中断3.5.1 外部中断3.6 系统控制3.6.1 OSC和PLL模块3.6.2 看门狗模块3.7 低功耗模式模块4 外设4.1 32位CPU定时器0/1/24.2 增强型PWM模块(ePWM1/2/3/4/5/6)4.3 高精度PWM(HRPWM)4.4 增强型CAP模块(eCAP1/2/3/4)4.6 增强型AD转换模块4.6.1 ADC不用时引脚连接4.6.2 ADC寄存器4.7 增强型CAN模块(e-CAN-A和eCAN-B)4.8 SCI模组(SCI-A,SCI-B)4.9 SPI模组(SPI-A,SPI-B,SPI-C,SPI-D)4.10 I2C总线4.11 GPIO复用引脚5 器件支持5.1 器件和开发工具名称5.2 文档支持6 电路规范6.1 绝对最大额定值6.2 推荐运行条件6.3 电气特性6.4 电流消耗6.4.1 减小电流消耗6.4.2 电流消耗图表6.5 DSP无信号缓冲区时的引脚冲突连接6.6 时序参数模型6.6.1 时序参数的一般注意事项6.6.2 测试负荷电路6.7 时钟要求和特性6.8 上电时序6.8.1 电源管理和监控电路解决方案6.9 通用输入输出(GPIO)多路复用器6.9.1 GPIO-输出时序6.9.2 GPIO-输入时序6.10 增强型控制外设6.10.1 增强型脉宽调制(ePWM)时序6.10.2 Trip-Zone 输入时序6.10.3 外部中断时序6.10.4 I2C电路特性和时序6.10.5 串行外设接口(SPI)主动模式时序6.10.6串行外设接口(SPI)被动模式时序6.10.7 片上模-数转换器6.10.7.1 ADC上电控制位时序6.11 详细描述6.12 FLASH时序6.13 ROM时序(仅适用于C280x)7 从F280X到C280X的移植7.1 移植方法8 机械数据图形列表2-1 TMS320F2809,TMS320F2808 100-pin PZ LQFP(Top V iew)2-2 TMS320F2806 100-pin PZ LQFP(Top V iew)2-3 TMS320F2802,TMS320F2801,TMS320C2802,TMS320C2801,100-pin PZ LQFP(Top V iew)2-4 TMS320F2801x 100-Pin PZ LQFP(Top V iew)2-5 TMS320F2809,TMS320F2808,TMS320F2806,TMS320F2802,TMS320F2801,TMS320F28016,TMS320F28015,TMS320C2802,TMS320C2801 100-ball GGM and ZGM MicroStar BGA(Bottom View) 3-1 原理框图3-2 F2809内存映射3-3 F2808内存映射3-4 F2806内存映射3-5 F2802,C2802内存映射3-6 F2801, F28015,F28016,C2801内存映射3-7 外设中断资源3-8 使用外设中断模块时的中断复用3-9 时钟和复位电路3-10 OSC和PLL 方块图3-11 3.3V外部晶振的使用3-12 1.8V外部晶振的使用3-13 内部晶振的使用3-14 看门狗模块4-1 CPU定时器4-2 CPU定时器中断信号和输出信号4-3 280x系统的多路PWM模块4-4 ePWM4-5 eCAP功能方块图4-6 eQEP功能方块图4-7 ADC模块方块图4-8 使用内部参考时的ADC引脚连接4-9使用外部参考时的ADC引脚连接4-10 eCAN方块图和接口电路4-11 Ecan-A存储映射4-12 Ecan-B存储映射4-13 串行通信接口模组方块图4-14 SPI模组方块图(被动模式)4-15 I2C接口设计4-16 GPIO复用引脚方块图4-17 使用取样窗口的条件5-1 TMS320X280X器件命名举例6-1 典型的运行电流相对频率(F2808)6-2 典型的运行电流相对频率(F2808)6-3 无信号缓冲时的硬件连接6-4 3.3V测试负荷电路6-5 时钟时序6-7 热复位6-8 有效写入PLLCR寄存器的举例6-9 通用输出时序6-10 采样模式6-11 通用输入时序6-12 空闲进入和退出时序6-13 备用进入和退出时序6-14 使用通用IO口的中断唤醒6-15 PWM HI-Z特性6-16 ADCSOCAO or ADCSOCBO 时序6-17 外部中断时序6-18 SPI主动模式外部时序(CLOCK PHASE = 0)6-19 SPI主动模式外部时序(CLOCK PHASE = 1)6-20 SPI被动模式外部时序(CLOCK PHASE = 0)6-21 SPI被动模式外部时序(CLOCK PHASE = 1)6-22 ADC上电控制位时序6-23 ADC 模拟输入阻抗模式6-24 单通道模式时序6-25多通道模式时序表单列表2-1 硬件特性(100MHZ器件)2-2 硬件特性(60MHZ器件)2-3 信号描述3-1 F2809的FLASH段地址3-2 F2808的FLASH段地址3-3 F2802、F2806的FLASH段地址3-4 F2801、F28015、F28016的FLASH段地址3-5 使用代码保护模式的影响3-6 等待状态3-7 自举模式选择3-8 外部frame0寄存器3-9 外部frame1寄存器3-10 外部frame2寄存器3-11 器件硬件寄存器3-12 PIE外部中断3-13 PIE配置和控制寄存器3-14 外部中断寄存器3-15 PLL,Clocking,Watchdog,and Low-Power Mode 寄存器3-16 PLLCR寄存器位定义3-17 可能的PLL配置模式3-18 低功耗模式4-1 CPU定时器0,1,2配置和控制寄存器4-2 ePWM控制和标准寄存器4-4 eQEP控制和标准寄存器4-5 ADC寄存器4-6 3.3V eCAN收发器4-7 CAN寄存器MAP4-8 SCI-A寄存器4-9 SCI-B寄存器4-10 SPI-A寄存器4-11 SPI-B寄存器4-12 SPI-C寄存器4-13 SPI-D寄存器4-14 SPI-C寄存器4-15 GPIO寄存器4-16 F2808 GPIO复用表6-1 系统时钟为100MHZ时TMS320F2809,TMS320F2808的电流消耗6-2系统时钟为100MHZ时TMS320F2806的电流消耗6-3系统时钟为100MHZ时TMS320F2802,TMS320F2801的电流消耗6-4系统时钟为100MHZ时TMS320C2802,TMS320C2801的电流消耗6-5各种外设的典型电流消耗(100MHZ时)6-6 TMS320x280x时钟表和命名(100MHZ器件)6-7 TMS320x280x时钟表和命名(60MHZ器件)6-8 输入时钟频率6-9 XCLKIN时序要求-PLL enabled6-10 XCLKIN时序要求-PLL disabled6-11 XCLKOUT 开关特性(PLL bypassed or enabled)6-12 电源管理和监控电路解决方案6-13 Reset(XRS)时序要求6-14 通用输出开关特性6-15 通用输入时序要求6-16 IDLE模式时序要求6-17 IDLE模式开关特性6-18 STANDBY模式时序要求6-19 STANDBY模式开关特性6-20 HALT模式时序要求6-21 HALT模式开关特性6-22 ePWM时序要求6-23 ePWM开关特性6-24 Trip-Zone 输入时序要求6-25 高精度PWM特性(SYSCLKOUT=(60~100MHZ)6-26 eCAP时序要求6-27 eCAP开关特性6-28 eQEP时序要求6-29 eQEP开关特性6-30 外部ADC启动转换开关特性6-31 外部中断时序要求6-32 外部重点开关特性6-34 SPI主动模式外部时序(Clock Phase=0)6-35 SPI主动模式外部时序(Clock Phase=1)6-36 SPI被动模式外部时序(Clock Phase=0)6-37 SPI被动模式外部时序(Clock Phase=0)6-38 ADC电器特性(通过推荐运行条件验证)6-39 ADC上电延时6-40 不同ADC配置时的电流消耗(ADCCLK=12.5MHZ)6-41 单通道模式时序6-42 多通道模式时序6-43 Flash耐性6-44 SYSCLKOUT=100MHZ时的Flash参数6-45 Flash/OTP进入时序6-46 不同频率时的最大最小要求Flash/OTP等待状态6-47 ROM/OTP进入时序6-48不同频率时的最大最小要求ROM/OTP等待状态8-1 F280x Thermal Model 100-pin GGM Results8-2 F280x Thermal Model 100-pin PZ Results8-3 C280x Thermal Model 100-pin GGM Results8-4 C280x Thermal Model 100-pin PZ Results8-5 F2809 Thermal Model 100-pin GGM Results8-6 F2809 Thermal Model 100-pin PZ Results版本历史注意:早期版本的页码可能和当前版本页码有所不同该数据手册自SPRS230I到SPRS230J修正该文档因保证技术的准确性,已经被再次审阅。

tms320f28数字信号控制器入门

步骤 4. 转到更多高级主题— 要获得更多的应用软件和其它高级主题,请访问 TI 网站或 者/c2000getstarted。

TMS320C28x, Code Composer Studio, C28x are trademarks of Texas Instruments. eZdsp is a trademark of Spectrum Digital. All other trademarks are the property of their respective owners.

要使用 eZdsp 套件开始开发,请访问并且为电路原理图和快速启动指南选 择合适的 eZdsp。

调试器和仿真工具:如果在您自己的硬件上开发,您将需要一个稳健耐用的软件开发工具包和支持实时 JTAG 仿真的仿真器。

图片列表

1 Spectrum Digital 公司的 C2000 开发工具网站 .......................................................................... 6 2 eZdspF2808 上的启动至 SARAM 开关 1 配置。 ....................................................................... 6 3 Code Composer Studio 文件视图 (File View) 窗口 ......................................... 7 4 280x CPU 定时器示例监视窗口 ........................................................................................... 8 5 添加变量到 Watch Window ................................................................................................ 8 6 调试菜单 (Debug Menu) 中实时模式选项 (Real-time Mode Option) ................................................. 9

カットラック 548 548 LL 森林機说明书

Cat ®548/548 LLForest MachinesThe 548 and 548 LL feature ultimate machine efficiency coupled with enhanced performance. Cat ®components, purpose built upper and lower frames, and application specific linkage confi gurations increase machine up time and lower machine operating costs.Effi ciency• Engine, hydraulics, and work tool integration are optimized to minimize power losses and increase overall machine ef fi ciency • S t eady state high idle speed and U.S. EPA Tier 4 Final technology reduce fuel consumption• Larger hydraulic pumps allow engine to operate at lower rpms with increased per f ormance to maximize ef fi ciency• Component layout and back-to-back main hydraulic control valve reduce oil flow restrictions and aid in greater fuel economy • Machine designed for integration and optimization with Cat grapples • Power f ul, multi-functioning hydraulics, combined with strong machine per f ormance ensure work tools function quickly and smoothly to complete work fasterPerformance• Cat 152 kW (2 0 4 hp) C7.1 ACERT ™ Tier 4 Final engine with increased horsepower maintains maximum per f ormance under load • S t rong hydraulic horsepower for ef fi cient implement per f ormance and greater productivit y• An increase in swing torque of 19 percent on General Forestr ymodels and 18 percent on Log Loader models, provides added power to move trees, which enables more ef fi ciency and productivit y • Heav y lif t mode features increased lif t capacit y to handle larger payloads with improved control• 9 8 9 L (2 61 gal) counter w eight fuel tank for ex t ended machine operation and maximum uptime• Machine width and track length designed for s t abilit y in varied logging applicationsApplication Versatility• Boom arrangements and hydraulic systems for specific applications enable more ef f ective road building, loading, processing, shoveling, or millyard stacking• New track options meet shovel logging and low ground pressure application requirements• Ground saw hydraulics are available for log loader applications • Two premium rear entr y cab choices, available on the Log Loader, include a 1219 mm (4 8 in) or a 182 9 mm (72 in) cab for w ard riser • Purpose built processor cab option that includes 19 mm (0.75 in) front windowsReliability and Durability• Variable pitch, reversing cooling fan maintains optimum fluid temperature in heav y dut y fores t r y applications• Cooling capabilit y increased 12 percent for trouble-free operation • Purpose built upper frame, high-wide carbody, robust linkage configurations, and heav y -dut y enclosures are reinforced with thick doubler plates, ex t ra gussets, and other reinforcements for structural integrit y in severe applications• Large, 216 mm (8.5 in) pitch (3 3 6 HE X ), grease lubricated tracks, provide excellent life in variable fores t r y working conditions • Validated and proven excavator technologies ensure overall machine reliabilit yServiceability• One-piece engine hood design, with t w o opening angles, allowseasy access to engine and cooling compar t ments• Side-by-side engine and hydraulic coolers are easy to access for cleaning, while reduced cooling fins per inch allows bet t er debris flow-through and reduced clogging potential • 0.5 6 m 3 (19.8 f t 3) of s t orage space at ground level, provides ready access to tools, equipment , and supplies that operators use dailyOperator Comfort and Technology• Premium fit and finishes to maximize operator experience • Fully adjustable, air ride cab seat that includes heating and cooling capabilit y for comfor t and reduced operator fatigue • LED lights increase visibilit y• Rear entr y cab option provides improved access on a fully lit plat f orm through the use of a key FOB• Rear entr y cab window design improves visibilit y for shovel logging and other applications• Rear entr y cab includes a new innovative cab lock down system that minimizes transpor t time and improves uptime• Tool control sof t w are as standard equipment for swapping and selecting tools quickly and ef fi ciently• Cat Product Link™ allows for remote location of a machine and enables tracking of fuel consumption and other eventsCat® 548/ 548 LL Forest MachinesEngine Model Cat C 7.1 ACER T Gross Power at 1, 800 rpm 152 kW 20 4 hp Engine SpeedOperation 1, 600 rpmTravel 1, 800 rpm Displacement 7.01 L 42 8 in3 Number of Cylinders 6Estimated Operating Weight without At t achment5 48 (General Forestr y, Processor) 3 5 3 54 kg 7 7,9 42 lb5 48 LL (Log Loader, U/ U) 3 8 15 3 kg 8 4,113 lbMaximum Speed (tur t le) 2.6 km /h 1.6 mph Maximum Speed (rabbit) 4 .8 km /h 3.0 mph Maximum Drawbar Pull 313 kN 70, 32 0 lbf Swing Torque – 5 48 (GF )8 7.4 kN·m 6 4, 441 lbf-f t Swing Torque – 5 48 LL 9 9.9 kN∙m 73, 677 lbf-f t Maximum Swing Speed – 5 48 (GF )9.3 rpm Maximum Swing Speed – 5 48 L L9.3 rpmMain Pumps Maximum Flow (per pump) 2 26 L /min 59.7 gal/min Main Pumps Maximum Flow (both pumps) 4 52 L /min 119.4 gal /min Maximum System PressureImplements 3 5 0 00 kPa 5, 076 psi Travel 3 5 0 00 kPa 5, 076 psi Swing – 5 48 (GF ) 3 0 5 00 kPa 4, 424 psi Swing – 5 48 LL 3 4 0 00 kPa 4, 931 psi Heav y L i f t Mode 3 8 0 00 kPa 5, 511 psi Auxiliar y Pump – U/ U and O/ U (5 48 L L)Maximum F l ow 4 8 L /min 12.8 gal /min Maximum Pressure 10 3 35 kPa 1, 499 psi Auxiliar y Pump – Reach w/ R otate (5 48)/Power Clam /B nt (5 48 LL)Pump Drive Gear Ratio 1.2 8:1Maximum Flow 12 9 L /min 3 4.1 gal /min Maximum Pressure 10 3 35 kPa 1, 499 psi Fuel Tank – C W T9 89. 3 L 261.4 gal DEF Tank 4 6.0 L 12 .2 gal Engine Crankcase 24 .0 L 6.3 gal Cooling System 3 0.0 L 7.9 gal Final Drive – Each 11.0 L 2 .9 gal Hydraulic Tank 175.0 L 4 6.2 gal Hydraulic System – Total 2 85.0 L 75. 3 gal Swing Drive 9.0 L 2 .4 galUndercarriage Pitch 215.9 mm 8.5 in Track Gauge 2 809 mm 110.6 in Track Length 5 035 mm 19 8.2 in Ground Clearance 7 74 mm 3 0.5 inGeneral Fores t r y – 5 48 Processor(boom stretched out)Height of Tilted Side Entr y Cab 3 479 mm 13 7.0 in Boom Height 3 74 5 mm 147.4 in Overall Height 416 6 mm 16 4.0 in Overall Length (Reach) 12 5 92 mm 4 95.7 in Tail Swing Radius 3 501 mm 13 7.8 in Distance Bet w een Idlerand Sprocket Centerline4 019 mm 15 8.2 inTrack Length 5 035 mm 19 8.2 in Ground Clearance 7 74 mm 3 0.5 in Track Gauge 2 809 mm 110.6 in Width with 70 0 mm (2 8 in) Shoes 3 509 mm 13 8.1 in Log Loader – 5 48 L L Under/ U nder(boom stretched out)Height of Tilted Side Entr y Cab 3 479 mm 13 7.0 in Boom Height 2 864 mm 112.8 in Overall Height 4 928 mm 19 4.0 in Overall Length (U/ U) 15 14 3 mm 59 6.2 in Tail Swing Radius 3 501 mm 13 7.8 in Distance Bet w een Idlerand Sprocket Centerline4 019 mm 15 8.2 inTrack Length 5 035 mm 19 8.2 in Ground Clearance 7 74 mm 3 0.5 in Track Gauge 2 809 mm 110.6 in Width with 70 0 mm (2 8 in) Shoes 3 509 mm 13 8.1 inF o r more complete infor m ation on Cat product s, dealer ser v ices, and indus t r y solutions, v i sit us on the web at © 2 018 CaterpillarAll rights reser v edMaterials and speci fi cations are subject to change wi t hou t not i ce. Feat u red machines in photos may include addi t ional equipment . See your Cat dealer for available opt i ons .C A T, C A T E R PIL L A R, S A F E T , their respective logos, “Caterpillar Yellow ” and t h e “Power Edge” trade dress, as well as corporate and product iden t i t y used herein, are trademarks of Caterpillar and may not be used wi t hout permission. AE X Q 2231 (01-2018)(NACD, ANZ)。

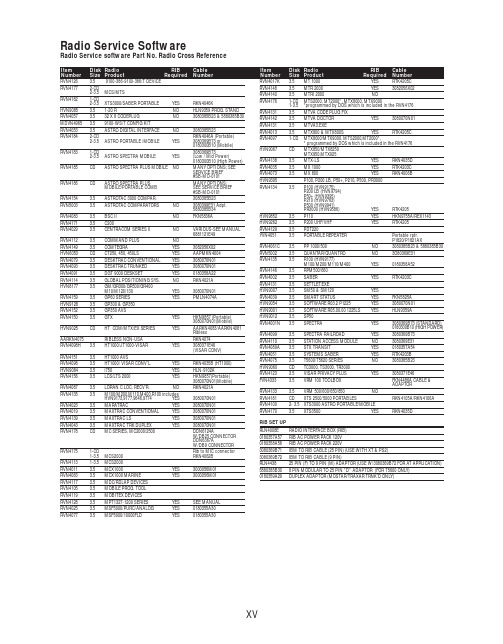

Motorola 3.5 kHz 产品说明书

RVN4126 3.59100-386-9100-386/T DEVICERVN41772-CD2-3.5MCS/MTSRVN41821-CD2-3.5XTS3000/SABER PORTABLE YES RKN4046KHVN9085 3.51-20 R NO HLN9359 PROG. STAND RVN4057 3.532 X 8 CODEPLUG NO3080385B23 & 5880385B30 MDVN4965 3.59100-WS/T CONFIG KITRVN4053 3.5ASTRO DIGITAL INTERFACE NO3080385B23RVN41842-CD RKN4046A (Portable) 2-3.5ASTRO PORTABLE /MOBILE YES3080369B73 or0180300B10 (Mobile) RVN41831-CD3080369B732-3.5ASTRO SPECTRA MOBILE YES(Low / Mid Power)0180300B10 (High Power) RVN4185CD ASTRO SPECTRA PLUS MOBILE NO MANY OPTIONS; SEESERVICE BRIEF#SB-MO-0101RVN4186CD ASTRO SPECTRA PLUS MANY OPTIONS;MOBILE/PORTABLE COMB SEE SERVICE BRIEF#SB-MO-0101RVN4154 3.5ASTROTAC 3000 COMPAR.3080385B23RVN5003 3.5ASTROTAC COMPARATORS NO3080399E31 Adpt.5880385B34RVN4083 3.5BSC II NO FKN5836ARVN4171 3.5C200RVN4029 3.5CENTRACOM SERIES II NO VARIOUS-SEE MANUAL6881121E49RVN4112 3.5COMMAND PLUS NORVN4149 3.5COMTEGRA YES3082056X02HVN6053CD CT250, 450, 450LS YES AAPMKN4004RVN4079 3.5DESKTRAC CONVENTIONAL YES3080070N01RVN4093 3.5DESKTRAC TRUNKED YES3080070N01RVN4091 3.5DGT 9000 DESKSET YES0180358A22RVN4114 3.5GLOBAL POSITIONING SYS.NO RKN4021AHVN8177 3.5GM/GR300/GR500/GR400M10/M120/130YES3080070N01RVN4159 3.5GP60 SERIES YES PMLN4074AHVN9128 3.5GP300 & GP350RVN4152 3.5GP350 AVSRVN4150 3.5GTX YES HKN9857 (Portable)3080070N01(Mobile) HVN9025CD HT CDM/MTX/EX SERIES YES AARKN4083/AARKN4081RiblessAARKN4075RIBLESS NON-USA RKN4074RVN4098H 3.5HT1000/JT1000-VISAR YES3080371E46(VISAR CONV)RVN4151 3.5HT1000 AVSRVN4098 3.5HT1000/ VISAR CONV’L.YES RKN4035B (HT1000) HVN9084 3.5i750YES HLN-9102ARVN4156 3.5LCS/LTS 2000YES HKN9857(Portable)3080070N01(Mobile) RVN4087 3.5LORAN C LOC. RECV’R.NO RKN4021ARVN4135 3.5M100/M200,M110,M400,R100 includesHVN9173,9177,9646,9774YES3080070N01RVN4023 3.5MARATRAC YES3080070N01RVN4019 3.5MAXTRAC CONVENTIONAL YES3080070N01RVN4139 3.5MAXTRAC LS YES3080070N01RVN4043 3.5MAXTRAC TRK DUPLEX YES3080070N01RVN4178CD MC SERIES, MC2000/2500DDN6124AW/DB25 CONNECTORDDN6367AW/DB9 CONNECTOR RVN41751-CD Rib to MIC connector 1-3.5MCS2000 RKN4062BRVN41131-3.5MCS2000RVN4011 3.5MCX1000YES3000056M01RVN4063 3.5MCX1000 MARINE YES3000056M01RVN4117 3.5MDC/RDLAP DEVICESRVN4105 3.5MOBILE PROG. TOOLRVN4119 3.5MOBITEX DEVICESRVN4128 3.5MPT1327-1200 SERIES YES SEE MANUALRVN4025 3.5MSF5000/PURC/ANALOG YES0180355A30RVN4077 3.5MSF5000/10000FLD YES0180355A30RVN4017K 3.5MT 1000YES RTK4205CRVN4148 3.5MTR 2000YES3082056X02RVN4140 3.5MTRI 2000NORVN41761-CD MTS2000, MT2000*, MTX8000, MTX90001-3.5*programmed by DOS which is included in the RVN4176RVN4131 3.5MTVA CODE PLUG FIXRVN4142 3.5MTVA DOCTOR YES3080070N01RVN4131 3.5MTVA3.EXERVN4013 3.5MTX800 & MTX800S YES RTK4205CRVN4097 1-CD MTX8000/MTX9000,MTS2000,MT2000*,* programmed by DOS which is included in the RVN4176HVN9067CD MTX850/MTX8250MTX950,MTX925RVN4138 3.5MTX-LS YES RKN4035DRVN4035 3.5MX 1000YES RTK4203CRVN4073 3.5MX 800YES RKN4006BHVN9395 P100, P200 LB, P50+, P210, P500, PR3000RVN4134 3.5P100 (HVN9175)P200 LB (HVN9794)P50+ (HVN9395)P210 (HVN9763)P500 (HVN9941)PR3000 (HVN9586)YES RTK4205HVN9852 3.5P110YES HKN9755A/REX1143 HVN9262 3.5P200 UHF/VHF YES RTK4205RVN4129 3.5PDT220YVN4051 3.5PORTABLE REPEATER Portable rptr.P1820/P1821AXRVN4061C 3.5PP 1000/500NO3080385B23 & 5880385B30 RVN5002 3.5QUANTAR/QUANTRO NO3O80369E31RVN4135 3.5R100 (HVN9177)M100/M200/M110/M400YES0180358A52RVN4146 3.5RPM500/660RVN4002 3.5SABER YES RTK4203CRVN4131 3.5SETTLET.EXEHVN9007 3.5SM50 & SM120YESRVN4039 3.5SMART STATUS YES FKN5825AHVN9054 3.5SOFTWARE R03.2 P1225YES3080070N01HVN9001 3.5SOFTWARE R05.00.00 1225LS YES HLN9359AHVN9012 3.5SP50RVN4001N 3.5SPECTRA YES3080369B73 (STANDARD)0180300B10 (HIGH POWER) RVN4099 3.5SPECTRA RAILROAD YES3080369B73RVN4110 3.5STATION ACCESS MODULE NO3080369E31RVN4089A 3.5STX TRANSIT YES0180357A54RVN4051 3.5SYSTEMS SABER YES RTK4203BRVN4075 3.5T5600/T5620 SERIES NO3080385B23HVN9060CD TC3000, TS3000, TR3000RVN4123 3.5VISAR PRIVACY PLUS YES3080371E46FVN4333 3.5VRM 100 TOOLBOX FKN4486A CABLE &ADAPTORRVN4133 3.5VRM 500/600/650/850NORVN4181CD XTS 2500/5000 PORTABLES RKN4105A/RKN4106A RVN41002- 3.5XTS3000 ASTRO PORTABLE/MOBILERVN4170 3.5XTS3500YES RKN4035DRIB SET UPRLN4008E RADIO INTERFACE BOX (RIB)0180357A57RIB AC POWER PACK 120V0180358A56RIB AC POWER PACK 220V3080369B71IBM TO RIB CABLE (25 PIN) (USE WITH XT & PS2)3080369B72IBM TO RIB CABLE (9 PIN)RLN443825 PIN (F) TO 9 PIN (M) ADAPTOR (USE W/3080369B72 FOR AT APPLICATION) 5880385B308 PIN MODULAR TO 25 PIN ”D” ADAPTOR (FOR T5600 ONLY)0180359A29DUPLEX ADAPTOR (MOSTAR/TRAXAR TRNK’D ONLY)Item Disk Radio RIB Cable Number Size Product Required Number Item Disk Radio RIB Cable Number Size Product Required NumberUtilizing your personal computer, Radio Service Software (RSS)/Customer Programming Software (CPS)/CustomerConfiguration Software (CCS) enables you to add or reprogram features/parameters as your requirements change. RSS/CPS/CCS is compatible with IBM XT, AT, PS/2 models 30, 50, 60 and 80.Requires 640K RAM. DOS 3.1 or later. Consult the RSS users guide for the computer configuration and DOS requirements. (ForHT1000, MT/MTS2000, MTX838/8000/9000, Visar and some newer products —IBM model 386, 4 MEG RAM and DOS 5.0 or higher are recommended.) A Radio Interface Box (RIB) may be required as well as the appropriate cables. The RIB and cables must be ordered separately.Licensing:A license is required before a software (RVN) order is placed. The software license is site specific (customer number and ultimate destination tag). All sites/locations must purchase their own software.Be sure to place subsequent orders using the original customer number and ship-to-tag or other licensed sites; ordering software without a licensed customer number and ultimate tag may result in unnecessary delays. To obtain a no charge license agreement kit, order RPX4719. To place an order in the U.S. call 1-800-422-4210. Outside the U.S., FAX 847-576-3023.Subscription Program:The purchase of Radio ServiceSoftware/Customer Programming/Customer ConfigurationSoftware (RVN & HVN kits) entitles the buyer/subscriber to three years of free upgrades. At the end of these three years, the sub-scriber must purchase the same Radio Service Software kit to receive an additional three years of free upgrades. If the sub-scriber does not elect to purchase the same Radio Service Software kit, no upgrades will be sent. Annually a subscription status report is mailed to inform subscribers of the RSS/CPS/CCS items on our database and their expiration dates.Notes:1)A subscription service is offered on “RVN”-Radio Service Software/Customer Programming/Customer Configuration Software kits only.2)“RVN” software must only be procured through Radio Products and Services Division (RPSD). Software not procured through the RPSD will not be recorded on the subscription database; upgrades will not be mailed.3)Upgrades are mailed to the original buyer (customer number & ultimate tag).4)SP software is available through the radio product groups.The Motorola General Radio Service Software Agreement is now available on Motorola Online. If you need assistance please feel free to submit a “Contact Us” or call 800-422-4210.SMART RIB SET UPRLN1015D SMART RIB0180302E27 AC POWER PACK 120V 2580373E86 AC POWER PACK 220V3080390B49SMARTRIB CABLE (9 PIN (F) TO 9 PIN (M) (USE WITH AT)3080390B48SMARTRIB CABLE (25 PIN (F) TO 9 PIN (M) (USE WITH XT)RLN4488ASMART RIB BATTERY PACKWIRELESS DATA GROUP PRODUTS SOFTWARERVN4126 3.59100-386/9100T DEVICES MDVN4965 3.59100-WS/T CONFIG’TN RVN41173.5MDC/RDLAP DEVICESPAGING PRODUCTS MANUALS6881011B54 3.5ADVISOR6881029B90 3.5ADVISOR ELITE 6881023B20 3.5ADVISOR GOLD 6881020B35 3.5ADVISOR PRO FLX 6881032B30 3.5BR8506881032B30 3.5LS3506881032B30 3.5LS5506881032B30 3.5LS7506881033B10 3.5LS9506881035B20 3.5MINITOR III8262947A15 3.5PAGEWRITER 20008262947A15 3.5PAGEWRITER 2000X 6881028B10 3.5TALKABOUT T3406881029B35 3.5TIMEPORT P7308262947A15 3.5TIMEPORT P930NLN3548BUNIVERSAL INTERFACE KITItem Disk Radio NumberSize Product。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Application ReportSPRA958F – January 2006 Running an Application from Internal Flash Memory onthe TMS320F28xx DSP David M. Alter DSP Applications - Semiconductor GroupABSTRACTSeveral special requirements exist for running an application from on-chip flash memoryon the TMS320F28xx DSP. These requirements generally do not manifest themselvesduring development in RAM since the Code Composer Studio™ debugger can maskproblems associated with initialized sections and how they are linked to memory. Thisapplication report covers the requirements needed to properly configure applicationsoftware for execution from on-chip flash memory. Requirements for both DSP/BIOS™and non-DSP/BIOS projects are presented. Some performance considerations andtechniques are also discussed. Example code projects are included that run from on-chipflash on the eZdsp™ F2812 and eZdsp F2808 development boards (or alternately, anyF2801, F2806, F2808, F2810, F2811, or F2812 DSP board). Code examples that runfrom internal RAM are also provided for completeness. These code examples provide astarting point for code development, if desired.Note that the issues discussed in this application report apply directly to current F281xand F280x members of the TMS320F28xx DSP family, specifically the F2801, F2806,F2808, F2810, F2811, and F2812 DSP devices. Applicability to future devices in theF28xx family, although quite likely, is not guaranteed. In addition, the code andtechniques presented in this application report for DSP/BIOS projects was developed onCode Composer Studio v3.1 using C-compiler v4.1.1 and DSP/BIOS v5.20. Earlierversions of DSP/BIOS used a different configuration file format. It is suggested that thereader upgrade to the latest version. Future versions of DSP/BIOS may have differencesthat make some of the items discussed in this report unnecessary (although in alllikelihood backwards compatibility will be maintained, so that the techniques discussedhere should still work). The reader should keep this in mind if using a newer version.Finally, this application report does not provide a tutorial on writing and building code forthe F28xx DSP. It is assumed that the reader already has at least the main framework oftheir application code running from RAM, probably using the Code Composer Studiodebugger to perform the code download. This report only identifies the special items thatmust be considered when moving the application into on-chip flash memory.Code Composer Studio and DSP/BIOS are trademarks of Texas Instruments.eZdsp is a trademark of Spectrum Digital Incorporated.Trademarks are the property of their respective owners.1SPRA958FContents1Introduction (3)2Creating a User Linker Command File (3)2.1Non-DSP/BIOS Projects (3)2.2DSP/BIOS Projects (4)3Where to Link the Sections (5)3.1Non-DSP/BIOS Projects (5)3.2DSP/BIOS Projects (7)4Copying Sections from Flash to RAM (9)4.1Copying the Interrupt Vectors (non-DSP/BIOS projects only) (9)4.2Copying the .hwi_vec Section (DSP/BIOS projects only) (10)4.3Copying the .trcdata Section (DSP/BIOS projects only) (10)4.4Initializing the Flash Control Registers (DSP/BIOS and non-DSP/BIOS projects) (12)4.5Maximizing Performance by Executing Time-critical Functions from RAM (14)4.6Maximizing Performance by Linking Critical Global Constants to RAM (15)4.6.1Method 1: Running All Constant Arrays from RAM (15)4.6.2Method 2: Running a Specific Constant Array from RAM (18)5Programming the Code Security Module Passwords (19)6Executing Your Code from Flash after a DSP Reset (23)7Disabling the Watchdog Timer During C-Environment Boot (25)8C-Code Examples (27)8.1General Overview (27)8.2Directory Structure and File Utilizations (28)8.3Additional Information (33)References (35)Revision History (36)FiguresFigure 1.Specifying the User Init Function in the DSP/BIOS Configuration tool (11)Figure 2.Specifying the Link Order In Code Composer Studio (17)Figure 3.DSP/BIOS MEM Properties for CSM Password Locations (22)Figure 4.DSP/BIOS MEM Properties for CSM Reserved Locations (22)Figure 5.DSP/BIOS MEM Properties for Jump to Flash Entry Point (24)TablesTable 1.Section Linking in Non-DSP/BIOS Projects (Large memory model) (6)Table 2.Section Linking In DSP/BIOS Projects (Large Memory Model) (7)Table 3.Example Code File Directories (28)Table 4.F281x Example Code File Inventory and Utilization (29)Table 5.F280x Example Code File Inventory and Utilization (31)2Running an Application from Internal Flash Memory on the TMS320F28xx DSPSPRA958F1 IntroductionThe TMS320F28xx DSP family has been designed for standalone operation in embeddedcontroller applications. The on-chip flash usually eliminates the need for external non-volatilememory and a host processor from which to bootload. Configuring an application to run fromflash memory is a relatively easy matter provided that one follow a few simple steps. This report covers the major concerns and steps needed to properly configure application software forexecution from internal flash memory. Requirements for both DSP/BIOS and non-DSP/BIOSprojects are presented. Some performance considerations and techniques are also discussed.Note that the issues discussed in this application report apply directly to current F281x andF280x members of the TMS320F28xx DSP family. Throughout the remainder of this report, the term current F28xx devices will refer specifically to the F2801, F2806, F2808, F2810, F2811,and F2812 DSP devices. Applicability to future devices in the F28xx family, although quitelikely, is not guaranteed. In addition, the code and techniques presented in this applicationreport for DSP/BIOS projects was developed on Code Composer Studio v3.1 using C-compiler v4.1.1 and DSP/BIOS v5.20. Earlier versions of DSP/BIOS used a different configuration fileformat. It is suggested that the reader upgrade to the latest version. Future versions ofDSP/BIOS may have differences that make some of the items discussed in this reportunnecessary (although in all likelihood backwards compatibility will be maintained, so that thetechniques discussed here should still work). The reader should keep this in mind if using anewer version.Finally, this application report does not provide a tutorial on writing and building code for theF28xx DSP. It is assumed that the reader already has at least the main framework of theirapplication code running from RAM, probably using the Code Composer Studio debugger toperform the code download. This report only identifies the special items that must beconsidered when moving the application into on-chip flash memory.2 Creating a User Linker Command File2.1 Non-DSP/BIOS ProjectsIn non-DSP/BIOS applications, the user linker command file will be where most memory isdefined, and where the linking of most sections is specified. The format of this file is no different than the linker command file you are currently using to run your application from RAM. Thedifference will be in where you link the sections (to be discussed in Section 3). More information on linker command files can be found in reference [6]. The non-DSP/BIOS code projects thataccompany this application report contain linker command files that can be used for reference.Running an Application from Internal Flash Memory on the TMS320F28xx DSP 3SPRA958FThe DSP281x and DSP280x peripheral header files contain linker command files namedDSP281x_Headers_nonBIOS.cmd and DSP280x_Headers_nonBIOS.cmd, respectively (see references [10] and [11]). These files contains linker MEMORY and SECTIONS declarations for linking the peripheral register structures. Since Code Composer Studio supports having more than one linker command file in a project, all one needs to do is add the header file linkercommand file to their project in addition to their user linker command file. In general, the order of the linker command files is unimportant since during a project build, Code Composer Studio evaluates the MEMORY section of every linker command file before evaluating the SECTIONS section of any linker command file. This ensures that all memories are defined before linking any sections to those memories. However, advanced users may need manual control over the order of linker command file evaluation in some rare situations. This can be specified withinCode Composer Studio on the Project → Build_Options, Link_Order tab.2.2 DSP/BIOS ProjectsThe DSP/BIOS configuration tool generates a linker command file that specifies how to link all DSP/BIOS generated sections, and by default all C-compiler generated sections. When running your application from RAM, this linker command file may be the only one in use. However,when executing from flash memory, there will likely be a need to generate and link one or more user defined sections. In particular, any code that configures the on-chip flash control registers(e.g. flash wait-states) cannot execute from flash. In addition, one may want to run certain timecritical functions from RAM (instead of flash) to maximize performance. A user linker command file must be created to handle these user defined sections.Code Composer Studio supports having more than one linker command file in a project. Hence, all one needs to do is add both the user linker command file, as well as the DSP/BIOSgenerated linker command file, to their project. In general, the order of the linker command files is unimportant since during a project build, Code Composer Studio evaluates the MEMORYsection of every linker command file before evaluating the SECTIONS section of any linkercommand file. This ensures that all memories are defined before linking any sections to those memories. However, advanced users may need manual control over the order of linkercommand file evaluation in some rare situations (for example, to preempt and overrideDSP/BIOS linkage of a section). This can be specified within Code Composer Studio on the Project → Build_Options, Link_Order tab.The DSP281x and DSP280x peripheral header files contain linker command files namedDSP281x_Headers_nonBIOS.cmd and DSP280x_Headers_nonBIOS.cmd, respectively (see references [10] and [11). These file contains linker MEMORY and SECTIONS declarations for linking the peripheral register structures. Simply add the appropriate one of these linkercommand files to your code project as well.4Running an Application from Internal Flash Memory on the TMS320F28xx DSPSPRA958F 3 Where to Link the SectionsTwo basic section types exist: initialized, and uninitialized. Initialized sections must contain valid values at device power-up. For example, code and constants are found in initialized sections.When designing a stand-alone embedded system with the F28xx DSP (e.g., no emulator ordebugger in use, no host processor present to perform bootloading), all initialized sections must be linked to non-volatile memory (e.g., on-chip flash). An uninitialized section does not contain valid values at device power-up. For example, variables are found in uninitialized sections.Code will write values to the variable locations during code execution. Therefore, uninitialized sections must be linked to volatile memory (e.g., RAM).It is suggested that the -w linker option be invoked. The -w option will produce a warning if the linker encounters any sections in your project that have not been explicitly specified for linking ina linker command file. When the linker encounters an unspecified section, it uses a defaultallocation algorithm to link the section into memory (it will link the section to the first definedmemory with enough available free space). This is almost always risky, and can lead tounreliable and unpredictable code behavior. The -w option will identify any unspecified sections(e.g., those accidentally forgotten by the user) so that the user can make the necessary additionto the appropriate linker command file. The -w option can be selected in Code Composer Studio on the Project → Build_Options menu, Linker tab, select the Advanced category, and thencheck the -w option box. It is checked by default for new projects.CAUTION:It is important that the large memory model be used with the C-compiler (asopposed to the small memory model). Small memory model requires certaininitialized sections to be linked to non-volatile memory in the lower 64Kw ofaddressable space. However, no flash memory is present in this region on anycurrent F28xx devices, and this will likely be true for future F28xx devices aswell. Therefore, large memory model should be used. In Code ComposerStudio, the large memory model is on the Project → Build_Options menu. Selectthe Compiler tab, choose the Advanced category, and check the -ml option box.For non-DSP/BIOS projects, one should include the large memory model C-compiler runtime support library, rts2800_ml.lib, into their code project (asopposed to rts2800.lib, which is for the small memory model). For DSP/BIOSprojects, DSP/BIOS will take care of including the required library. The usershould not include the rts2800_ml.lib (or rts2800.lib) library into a DSP/BIOSproject.3.1 Non-DSP/BIOS ProjectsThe compiler uses a number of specific sections. These sections are the same whether you are running from RAM or flash. However, when running a program from flash, all initialized sections must be linked to non-volatile memory, whereas all uninitialized sections must be linked tovolatile memory. Table 1 shows where to link each compiler generated section on the F28xxDSP. Information on the function of each section can be found in reference [3]. Any usercreated initialized section should be linked to flash (e.g., those sections created using theCODE_SECTION compiler pragma), whereas any user created uninitialized sections should be linked to RAM (e.g., those sections created using the DATA_SECTION compiler pragma).Running an Application from Internal Flash Memory on the TMS320F28xx DSP 5SPRA958F6 Running an Application from Internal Flash Memory on the TMS320F28xx DSPTable 1. Section Linking in Non-DSP/BIOS Projects (Large memory model) Section Name Where to Link.cinit Flash.cio RAM.const Flash.econst Flash.pinit Flash.switch Flash.text Flash .bss RAM.ebss RAM.stack Lower 64Kw RAM.sysmem RAM.esysmem RAM.reset RAM 1Table 1 Notes:1The .reset section contains nothing more than a 32-bit interrupt vector that points to theC-compiler boot function in the runtime support library (the _c_int00 routine). It generally is not used. Instead, the user typically creates their own branch instruction to point to the starting point of the code (see Sections 6 and 7). When not in use, the .reset section should be omitted from the code build by using a DSECT modifier in the linker command file. For example:/******************************************************************** * User's linker command file********************************************************************/SECTIONS{.reset : > FLASH, PAGE = 0, TYPE = DSECT}SPRA958FRunning an Application from Internal Flash Memory on the TMS320F28xx DSP 73.2 DSP/BIOS ProjectsThe memory section manager in the DSP/BIOS configuration tool allows one to specify where to link the various DSP/BIOS and C-compiler generated sections. Table 2 indicates where the sections shown on each tab of the memory section manager should be linked (i.e., RAM or FLASH). Note that this information has been tabulated specifically for DSP/BIOS v5.20. Later versions of DSP/BIOS, although quite likely to be the same, may have some differences. The reader should check the version they are using and simply be aware of potential differences while proceeding. To check your DSP/BIOS version from within Code Composer Studio, go to the Help → About menu, click the Component_Manager button, and view the TMS320C28XX DSP/BIOS version under the Target_Content_(DSP/BIOS) tree.Table 2. Section Linking In DSP/BIOS Projects (Large Memory Model) Memory Section Manager TAB Section NameWhere to Link Segment for DSP/BIOS ObjectsRAM General Segment for malloc()/free()RAM Argument Buffer Section (.args)RAM Stack Section (.stack)Lower 64Kw RAM DSP/BIOS Init Tables (.gblinit)Flash TRC Initial Values (.trcdata)RAM 1 DSP/BIOS Kernel State (.sysdata)RAM BIOS Data DSP/BIOS Conf Sections (*.obj)RAM BIOS Code Section (.bios)Flash Startup Code Section (.sysinit)Flash Function Stub Memory (.hwi)Flash Interrupt Service Table Memory (.hwi_vec)PIEVECT RAM 2 BIOS Code RTDX Text Segment (.rtdx_text)Flash Text Section (.text)Flash Switch Jump Tables (.switch) Flash C Variables Section (.bss) RAM C Variables Section (.ebss) RAM Data Initialization Section (.cinit)FlashCompiler Sections C Function Initialization Table (.pinit) FlashSPRA958F8 Running an Application from Internal Flash Memory on the TMS320F28xx DSP Constant Section (.econst)Flash Constant Section (.const)Flash Data Section (.data)Flash Data Section (.cio)RAM Load Address - BIOS Code Section (.bios)Flash 3 Load Address - Startup Code Section (.sysinit)Flash 3 Load Address - DSP/BIOS Init Tables (.gblinit)Flash 3 Load Address - TRC Initial Value (.trcdata)Flash 1 Load Address - Text Section (.text)Flash 3 Load Address - Switch Jump Tables (.switch)Flash 3 Load Address - Data Initialization Section (.cinit)Flash 3 Load Address - C Function Initialization Table (.pinit)Flash 3 Load Address - Constant Section (.econst)Flash 3 Load Address - Constant Section (.const)Flash 3 Load Address - Data Section (.data)Flash 3 Load Address - Function Stub Memory (.hwi)Flash 3 Load Address - Interrupt Service Table Memory (.hwi_vec)Flash 2 Load Address Load Address - RTDX Text Segment (.rtdx_text) Flash 3Table 2 Notes:1 The .trcdata section must be copied by the user from its load address (specified on theLoad_Address tab) to its run address (specified on the BIOS_Data tab) at runtime. See Section4.3 for details on performing this copy.2 The PIEVECT RAM is a specific block of RAM associated with the Peripheral InterruptExpansion (PIE) peripheral. On current F28xx devices, the PIE RAM is a 256x16 block starting at address 0x000D00 in data space. For other devices, confirm the address in the device datasheet. The memory section manager in the DSP/BIOS configuration tool should already have a pre-defined memory named PIEVECT. The .hwi_vec section must be copied by the user from its load address (specified on the memory section manager Load_Address Tab) to its run address (specified on the memory section manager BIOS_Code Tab) at runtime. See Section4.2 for details on performing this copy.3The specific flash memory selected as the load address for this section should be the same flash memory selected previously as the run address for the section (e.g., on the BIOS_Data, BIOS_Code, or Compiler_Sections tab).SPRA958FRunning an Application from Internal Flash Memory on the TMS320F28xx DSP 94 Copying Sections from Flash to RAM4.1 Copying the Interrupt Vectors (non-DSP/BIOS projects only)The Peripheral Interrupt Expansion (PIE) module manages interrupt requests on F28xx devices. At power-up, all interrupt vectors must be located in non-volatile memory (i.e., flash), but copied to the PIEVECT RAM as part of the device initialization procedure in your code. The PIEVECT RAM is a specific block of RAM, which on current F28xx devices is a 256x16 block starting at address 0x000D00 in data space.Several approaches exist for linking the interrupt vectors to flash and then copying them to the PIEVECT RAM at runtime. One approach is to create a constant C-structure of function pointers that contains all 128 32-bit vectors. If using the DSP281x or DSP280x peripheral structures (see references [10] and [11), such a structure, called PieVectTableInit , has already beencreated in the file DSP281x_PieVect.c or DSP280x_PieVect.c . Since this structure is declared using the const type qualifier, it will be placed in the .econst section by the compiler. One simply needs to copy this structure to the PIEVECT RAM at runtime. The C-compiler runtime support library contains a memory copy function called memcpy() that can be used to perform the copy task. This function is used as follows:/******************************************************************** * User's C-source file********************************************************************//********************************************************************* NOTE: This function assumes use of the DSP281x or DSP280x Header * File structures (TI Literature #SPRC097 and #SPRC191).********************************************************************/#include <string.h>void main(void){/*** Initialize the PIE_RAM ***/PieCtrlRegs.PIECTRL.bit.ENPIE = 0; // Disable the PIEasm(" EALLOW"); // Enable EALLOW protected register access memcpy((void *)0x000D00, &PieVectTableInit, 256);asm(" EDIS"); // Disable EALLOW protected register access }The above example uses a hard coded address for the start of the PIE RAM, specifically 0x000D00. If this is objectionable (as hard coded addresses are not good programming practice), one can use a DATA_SECTION pragma to create an uninitialized dummy variable, and link this variable to the PIE RAM. The name of the dummy variable can then be used in place of the hard coded address. For example, when using the DSP281x or DSP280xperipheral structures, an uninitialized structure called PieVectTable is created and linked over the PIEVECT RAM. The memcpy() instruction in the previous example can be replaced by: memcpy(&PieVectTable, &PieVectTableInit, 256);Note that the length is 256. The memcpy function copies 16-bit words (as opposed to copying 128 32-bit words).SPRA958F10 Running an Application from Internal Flash Memory on the TMS320F28xx DSP 4.2 Copying the .hwi_vec Section (DSP/BIOS projects only)The DSP/BIOS .hwi_vec section contains the interrupt vectors, and must be loaded to flash but run from RAM. The user is responsible for copying this section from its load address to its run address. This is typically done in main(). The DSP/BIOS configuration tool generates global symbols that can be accessed by code in order to determine the load address, run address, and length of the .hwi_vec section. These symbol names are:hwi_vec_loadstarthwi_vec_loadend hwi_vec_runstartEach symbol is self-explanatory from its name. Note that the symbols are not pointers, butrather symbolically reference the 16-bit data value found at the corresponding location (i.e., start or end) of the section. The C-compiler runtime support library contains a memory copy function called memcpy() that can be used to perform the copy task. A C-code example of how to use this function to perform the section copy follows. Note that the PIEVECT RAM is EALLOWprotected. Therefore, inline EALLOW and EDIS assembly instructions must bracket the memory copy of the .hwi_vec section, as shown./******************************************************************** * User's C-source file********************************************************************/#include <string.h>extern unsigned int hwi_vec_loadstart;extern unsigned int hwi_vec_loadend;extern unsigned int hwi_vec_runstart;void main(void){/*** Initialize the .hwi_vec section ***/asm(" EALLOW"); /* Enable EALLOW protected register access */memcpy(&hwi_vec_runstart,&hwi_vec_loadstart,&hwi_vec_loadend - &hwi_vec_loadstart);asm(" EDIS"); /* Disable EALLOW protected register access */ }4.3 Copying the .trcdata Section (DSP/BIOS projects only)The DSP/BIOS .trcdata sections must be loaded to flash, but run from RAM. The user isresponsible for copying this section from its load address to its run address. However, unlike the .hwi_vec section, the copying of .trcdata must be performed prior to main(). This is because DSP/BIOS modifies the contents of .trcdata during DSP/BIOS initialization (which also occurs prior to main()).The DSP/BIOS configuration tool provides for a user initialization function which can be utilized to perform the .trcdata section copy prior to both main() and DSP/BIOS initialization. This can be found in the project configuration file under System - Global Settings Properties, as shown in Figure 1.Figure 1. Specifying the User Init Function in the DSP/BIOS Configuration toolWhat remains is to create the user initialization function. The DSP/BIOS configuration toolgenerates global symbols that can be accessed by code in order to determine the load address, run address, and length of each section. These symbol names are:trcdata_loadstarttrcdata_loadend trcdata_runstartEach symbol is self-explanatory from its name. Note that the symbols are not pointers, butrather symbolically reference the 16-bit data value found at the corresponding location (i.e., start or end) of the section. The C-compiler runtime support library contains a memory copy function called memcpy() that can be used to perform the copy task. A C-code example of a user init function that performs the .trcdata section copy follows.Check this box Enter yourfunction namehere (note theleading underscore)/********************************************************************* User's C-source file********************************************************************/#include <string.h>extern unsigned int trcdata_loadstart;extern unsigned int trcdata_loadend;extern unsigned int trcdata_runstart;void UserInit(void){/*** Initialize the .trcdata section before main() ***/memcpy(&trcdata_runstart,&trcdata_loadstart,&trcdata_loadend - &trcdata_loadstart);}4.4 Initializing the Flash Control Registers (DSP/BIOS and non-DSP/BIOS projects)The initialization code for the flash control registers, FOPT, FPWR, FSTDBYWAIT,FACTIVEWAIT, FBANKWAIT, and FOTPWAIT, cannot be executed from the flash memory or unpredictable results may occur. Therefore, the initialization function for the flash controlregisters must be copied from flash (its load address) to RAM (its run address) at runtime.CAUTION:The flash control registers are protected by the Code Security Module (CSM). Ifthe CSM is secured, you must run the flash register initialization code fromsecured RAM (e.g., L0 or L1 SARAM) or the initialization code will be unable toaccess the flash registers. Note that the CSM is always secured at device reset,although the ROM bootloader will unlock it if you are using dummy passwordsof 0xFFFF.The CODE_SECTION pragma of the C compiler can be used to create a separately linkable section for the flash initialization function. For example, suppose the flash register configuration is to be performed in the C function InitFlash(), and it is desired to place this function into alinkable section called secureRamFuncs. The following C-code example shows proper use of the CODE_SECTION pragma along with an example configuration of the flash registers:。