芯片硬件

硬件看门狗芯片

硬件看门狗芯片硬件看门狗芯片,又称为硬件看门狗电路,是一种嵌入式系统中的重要组成部分。

它主要用于监控系统的运行状态,当系统出现异常情况时,硬件看门狗芯片会自动重置系统,以恢复系统的正常工作。

硬件看门狗芯片由看门狗定时器、看门狗复位电路和看门狗计时寄存器组成。

首先,我们来看看看门狗定时器。

看门狗定时器是硬件看门狗芯片的核心部分,它会定期向看门狗芯片发送某个特定的信号。

这个信号会被看门狗复位电路接收并处理。

如果系统正常工作,看门狗定时器会在规定的时间内定期发送信号,以表明系统仍然在正常运行中。

但是,如果系统出现异常情况,如死循环、程序卡死等,看门狗定时器将不会正常发送信号。

那么接下来就是看门狗复位电路的工作了。

看门狗复位电路会监测看门狗定时器发送的信号。

如果看门狗定时器在规定的时间内没有发送信号,说明系统出现了故障。

看门狗复位电路会立即向系统发送一个复位信号,强制将系统重启,以恢复系统的正常工作。

看门狗计时寄存器是用来控制看门狗定时器的运行时间的。

它有一个预置的定时值,比如60秒。

当看门狗定时器开始工作时,计时寄存器开始倒计时,直到倒计时结束。

如果看门狗定时器在倒计时结束前没有发送信号,看门狗复位电路将立即启动复位操作。

硬件看门狗芯片在嵌入式系统中有很多应用。

首先,它可以用于监控嵌入式系统的运行状态。

当系统处于正常工作状态时,看门狗定时器会定期发送信号,而看门狗复位电路会接收并处理信号。

如果系统出现异常情况,看门狗定时器将不会发送信号,看门狗复位电路会立即启动复位操作,以恢复系统的正常工作。

此外,硬件看门狗芯片还可以用于检测系统的死锁。

死锁是指系统中的两个或多个进程互相等待对方所持有的资源,导致系统无法继续运行的情况。

当系统发生死锁时,看门狗定时器将无法发送信号,看门狗复位电路会立即启动复位操作,以解除死锁状态。

硬件看门狗芯片还可以用于保护嵌入式系统的安全性。

一些恶意软件可能会导致系统崩溃或瘫痪。

使用硬件看门狗芯片可以及时检测并处理这些异常情况,确保系统的安全性。

华为芯片的软硬件协同设计提升系统性能

华为芯片的软硬件协同设计提升系统性能随着信息技术的快速发展,芯片作为计算机硬件中的核心组件,对于计算机系统的性能提升起着至关重要的作用。

为了满足现代计算需求的不断增加,华为公司在自主研发的芯片中,采用了软硬件协同设计的策略,通过软件和硬件的紧密结合,提升了芯片的系统性能。

软硬件协同设计是指将软件和硬件开发过程紧密结合起来,相互配合,以实现更高效、更优质的系统性能。

在芯片设计中,软硬件协同设计有以下几个方面的应用。

首先,华为芯片通过软硬件协同设计,实现了高度集成的硬件设计。

华为芯片大量采用了定制化的硬件设计,通过与软件的协同配合,充分发挥了硬件的性能优势。

同时,华为芯片中的硬件设计也能够根据软件的需求进行灵活调整,使得芯片能够更好地满足用户的应用需求。

其次,华为芯片在软硬件协同设计中,重点优化了软件编译器的设计。

编译器是将高级语言代码翻译成机器语言的关键工具,对于芯片的性能有着至关重要的影响。

华为芯片通过优化编译器的设计,使得软件代码能够更加高效地在芯片上运行,提升了芯片的性能表现。

此外,华为芯片还通过软硬件协同设计,实现了更高效的算法处理。

在芯片设计过程中,算法的设计和优化是至关重要的一环。

华为芯片通过软硬件协同设计,将算法的实现与硬件结构的设计相结合,充分发挥了算法在芯片上的优势。

这不仅提升了芯片的计算能力,还降低了功耗和资源消耗,提高了芯片的综合性能。

最后,华为芯片还通过软硬件协同设计,实现了更好的系统优化。

系统优化是指通过硬件和软件的协同设计,对整个系统进行优化,使得系统能够在各个方面达到最佳状态。

华为芯片通过软硬件协同设计,充分考虑了硬件和软件的配合,使得整个系统能够更高效地运行,提升了系统性能。

总结起来,华为芯片的软硬件协同设计是一种有效的策略,通过软件和硬件的密切结合,提升了芯片的系统性能。

华为芯片在设计过程中,充分考虑了软硬件的配合,优化了硬件设计、编译器设计、算法处理和系统优化,使得芯片能够更好地满足用户的需求。

芯片的硬件构造、成本及其厂商之间的对比

芯片的硬件构造、成本及其厂商之间的对比集成电路产业的特色是赢者通吃,像Intel这样的巨头,巅峰时期的利润可以高达60%。

那么,相对应动辄几百、上千元的CPU,它的实际成本到底是多少呢?芯片的硬件成本构成芯片的成本包括芯片的硬件成本和芯片的设计成本。

芯片硬件成本包括晶片成本+掩膜成本+测试成本+封装成本四部分(像ARM阵营的IC设计公司要支付给ARM设计研发费以及每一片芯片的版税,但笔者这里主要描述自主CPU 和Intel这样的巨头,将购买IP的成本省去),而且还要除去那些测试封装废片。

用公式表达为:芯片硬件成本=(晶片成本+测试成本+封装成本+掩膜成本)/ 最终成品率对上述名称做一个简单的解释,方便普通群众理解,懂行的可以跳过。

从二氧化硅到市场上出售的芯片,要经过制取工业硅、制取电子硅、再进行切割打磨制取晶圆。

晶圆是制造芯片的原材料,晶片成本可以理解为每一片芯片所用的材料(硅片)的成本。

一般情况下,特别是产量足够大,而且拥有自主知识产权,以亿为单位量产来计算的话,晶片成本占比最高。

不过也有例外,在接下来的封装成本中介绍奇葩的例子。

封装是将基片、内核、散热片堆叠在一起,就形成了大家日常见到的CPU,封装成本就是这个过程所需要的资金。

在产量巨大的一般情况下,封装成本一般占硬件成本的5%-25%左右,不过IBM的有些芯片封装成本占总成本一半左右,据说最高的曾达到过70%...... 测试可以鉴别出每一颗处理器的关键特性,比如最高频率、功耗、发热量等,并决定处理器的等级,比如将一堆芯片分门别类为:I5 4460、I5 4590、I5 4690、I5 4690K等,之后Intel就可以根据不同的等级,开出不同的售价。

不过,如果芯片产量足够大的话,测试成本可以忽略不计。

掩膜成本就是采用不同的制程工艺所需要的成本,像40/28nm的工艺已经非常成熟,成本也低——40nm低功耗工艺的掩膜成本为200万美元;28nm SOI工艺为400万美元;28nm HKMG成本为600万美元。

芯片编程原理

芯片编程原理芯片编程原理可以分为三个方面:芯片硬件、编程语言和编程工具。

一、芯片硬件芯片硬件是芯片编程的基础。

在硬件方面,需要了解芯片的基本组成、封装形式、内部结构和功能等内容。

1.芯片的基本组成芯片由外围设备控制器、中央处理器、存储器等多个组成部分组成。

其中,外围设备控制器可以控制输入输出设备,中央处理器可以计算数据,存储器可以存储数据和程序代码等。

2.芯片的封装形式芯片的封装形式有很多种,常见的有DIP、SOP等。

DIP芯片是通过插脚固定在PCB上,而SOP芯片则是通过焊接固定在PCB上。

3.芯片的内部结构芯片的内部结构包括逻辑电路、模拟电路等,在编程中需要考虑到这些结构的特点来进行编程。

4.芯片的功能不同芯片的功能不同,对于不同的应用场景需选择不同的芯片。

二、编程语言编程语言是进行芯片编程的工具。

常见的芯片编程语言有C语言、汇编语言、Verilog、VHDL等。

1.C语言C语言是一种高级编程语言,它可以进行面向对象编程,其语言结构比较清晰,语法简单、使用方便。

在芯片编程中,C语言是最常见的编程语言之一,因为其可以方便地对硬件进行控制。

2.汇编语言汇编语言是一种低级语言,其语言结构类似于机器语言,但更为易懂。

在芯片编程中,汇编语言可以直接操作硬件,从而实现更高精度的控制。

3.Verilog和VHDLVerilog和VHDL是描述硬件电路的语言,其不同于软件编程语言,只能描述硬件的行为。

在芯片编程中,Verilog和VHDL可以描述CPU、存储器等芯片内部结构。

三、编程工具编程工具是进行芯片编程的助手,常见的编程工具有编译器、调试器和仿真器等。

1.编译器编译器是将源代码转换成机器码的工具,常见的编译器有GCC、Keil等。

在芯片编程中,需要依据芯片的底层指令集对编译器进行选择。

2.调试器调试器是用于定位芯片硬件故障和软件运行时错误的工具,可以帮助用户快速定位问题的原因。

常见的调试器有JTAG、ICE、OSCOPE等。

硬件加密芯片原理

硬件加密芯片原理

硬件加密芯片原理是一种通过物理控制的方式对敏感数据进行保护的技术。

其主要原理是通过在硬件级别上使用专用的硬件加密芯片来执行加密和解密操作,从而保护数据的机密性和完整性。

硬件加密芯片通常由安全的硬件模块和相关的加密算法组成。

安全的硬件模块包括随机数生成器、密钥存储器、加密引擎和安全寄存器等。

加密算法包括对称加密算法和非对称加密算法,如AES、RSA等。

在加密过程中,硬件加密芯片可以生成随机的加密密钥,并将其存储在安全的密钥存储器中。

加密引擎会根据所选择的加密算法,使用密钥对待加密数据进行加密操作。

同时,硬件加密芯片还会生成加密的验证数据或数字签名,以确保数据的完整性和真实性。

在解密过程中,硬件加密芯片会使用存储在密钥存储器中的密钥对密文进行解密操作,并验证数据的完整性和真实性。

解密后的数据可以被应用程序使用,以完成相应的业务逻辑。

硬件加密芯片具有以下优点:

1. 安全性高:硬件级别的加密保护可以有效地防止软件层面的攻击,提供更高的安全性。

2. 效率高:硬件加密芯片采用专用的加密引擎执行加密和解密操作,速度更快,效率更高。

3. 灵活性强:硬件加密芯片支持多种加密算法,可以满足不同应用场景的需求。

4. 易于集成:硬件加密芯片可以通过标准接口与主板或其他设备进行集成,便于应用开发和系统集成。

总而言之,硬件加密芯片通过在硬件级别上提供专门的加密硬件模块和加密算法,为敏感数据的保护提供了一种安全、高效和可靠的解决方案。

硬件:主板篇-主板上有哪些重要芯片

主板篇-主板上有哪些重要芯片主板上的重要芯片很多,包括芯片组、BIOS 芯片、I/O 控制芯片、集成声卡芯片和集成网卡芯片等,下面分别进行介绍。

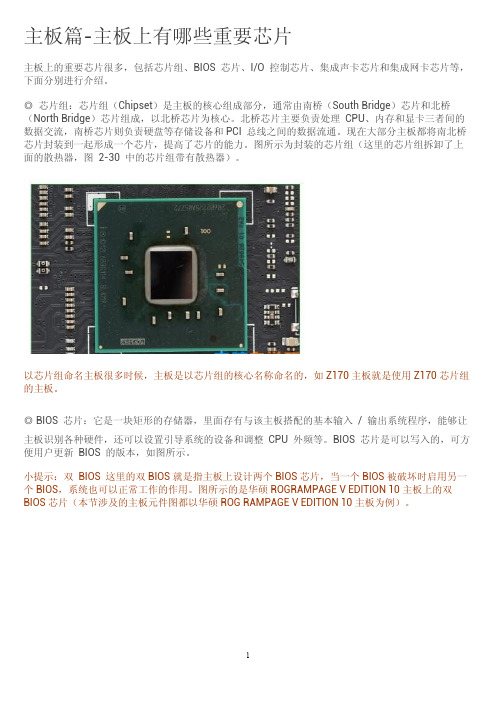

◎芯片组:芯片组(Chipset)是主板的核心组成部分,通常由南桥(South Bridge)芯片和北桥(North Bridge)芯片组成,以北桥芯片为核心。

北桥芯片主要负责处理CPU、内存和显卡三者间的数据交流,南桥芯片则负责硬盘等存储设备和PCI 总线之间的数据流通。

现在大部分主板都将南北桥芯片封装到一起形成一个芯片,提高了芯片的能力。

图所示为封装的芯片组(这里的芯片组拆卸了上面的散热器,图2-30 中的芯片组带有散热器)。

以芯片组命名主板很多时候,主板是以芯片组的核心名称命名的,如Z170主板就是使用Z170芯片组的主板。

◎ BIOS 芯片:它是一块矩形的存储器,里面存有与该主板搭配的基本输入/ 输出系统程序,能够让主板识别各种硬件,还可以设置引导系统的设备和调整CPU 外频等。

BIOS 芯片是可以写入的,可方便用户更新BIOS 的版本,如图所示。

小提示:双BIOS 这里的双BIOS就是指主板上设计两个BIOS芯片,当一个BIOS被破坏时启用另一个BIOS,系统也可以正常工作的作用。

图所示的是华硕ROGRAMPAGE V EDITION 10主板上的双BIOS芯片(本节涉及的主板元件图都以华硕ROG RAMPAGE V EDITION 10主板为例)。

◎ I/O 控制芯片:主要实现硬件监控功能,能将硬件的健康状况、风扇转速、CPU 核心电压等情况显示在BIOS 信息里面,如图所示。

小提示:CMOS 电池 CMOS电池的主要作用是在电脑关机的时候保持BIOS设置不丢失。

当电池电力不足的时候,BIOS里面的设置会自动还原回出厂设置。

图所示为CMOS电池。

◎集成声卡芯片:芯片中集成了声音的主处理芯片和解码芯片,代替声卡处理电脑音频。

◎集成网卡芯片:指整合了网络功能的主板所集成的网卡芯片。

单片机芯片的硬件结构课件

3、P3口线的情况却有所不同,它的第二功能信号都 是单片机的重要控制信号。因此在实际使用时,总是 先按需要优先选用它的第二功能,剩下不用的才作为 口线使用。

引脚表现出的是单片机的外特性或硬件特性。在硬件方 面用户只能使用引脚,即通过引脚组建系统。因此熟 悉引脚是单片机硬件学习的重点。

VSS(20脚): 接+5 V电源地端。

外接晶体引脚XTAL1和XTAL2 当使用芯片内部时钟时,此二引脚用于外接石英晶体 和微调电容。当使用外部时钟时,用于外接时钟脉冲 信号。

控制信号或与其它电源复用引脚 控制信号或与其它电源复用引脚有下面四个

单片机芯片的硬件结构

为复位信号,当输入的复位信号延续2个机器周 期以上高电平时即为有效,用于完成单片机的复位操 作。

P3口(10脚~17脚): P3.0~P3.7统称为P3口。

单片机芯片的硬件结构

2 信号引脚的第二功能

P3口线的第二功能

单片机芯片的硬件结构

引脚的第一、第二功能会不会混淆呢?

答案是肯定的,不会。理由有三。

1、对于各种型号的芯片,其引脚的第一功能信号是 相同的,所不同的只在引脚的第二功能信号上。

单片机芯片的硬件结构

9 位处理器

单片机主要用于控制,需要有较强的位处理功 能,因此位处理器是它的必要组成部分,在一 些书中常把位处理器称为布尔处理器。

位处理器以状态寄存器中的进位标志位C位累 加位,可进行置位、复位、取反、等于“0” 转移、等于“1”转移且清“0”以及C与可寻 址位之间的传送、逻辑与、逻辑或等位操作。

37H

(16B) 20H

什么是芯片的硬件最小系统,它由哪几部分组成?简要阐述各部分技术要点。

什么是芯片的硬件最小系统,它由哪几部分组成?简要阐述各部分技术要点。

芯片的硬件最小系统是指芯片能够独立运行的最小功能集合,它由多个部分组成。

这些部分包括中央处理器(CPU)、存储器、输入输出接口和时钟系统等。

首先,中央处理器(CPU)是芯片的核心部分,负责执行各种指令和控制芯片的运行。

CPU通常由运算逻辑单元(ALU)、控制单元(CU)和寄存器组成。

ALU负责执行算术和逻辑运算,CU负责控制指令的执行过程,寄存器用于存储临时数据和指令。

其次,存储器是芯片的重要组成部分,用于存储程序、数据和临时结果等。

存储器包括随机存储器(RAM)和只读存储器(ROM)两种类型。

RAM用于存储程序和数据,可以读写操作;ROM用于存储不变的程序和数据,只能读取不能写入。

输入输出接口是芯片与外部设备进行数据交换的通道。

它包括通用输入输出(GPIO)接口、串行接口、并行接口等。

GPIO接口可以连接各种外部设备,如键盘、鼠标、显示器等;串行接口用于与外部设备进行串行通信,如串口、USB接口等;并行接口用于与外部设备进行并行通信,如并口、PCI接口等。

时钟系统是芯片的基础,用于提供统一的时钟信号给各个部件。

时钟信号可以同步各个部件的工作,确保芯片的正常运行。

时钟系统由晶振、时钟发生器和时钟分频器等组成。

晶振产生稳定的振荡信号,时钟发生器将振荡信号转换为时钟信号,并通过时钟分频器进行分频,得到不同频率的时钟信号。

除了以上几个部分,芯片的硬件最小系统还可能包括其他功能模块,如电源管理模块、DMA控制器、中断控制器等。

电源管理模块用于管理芯片的供电和电源状态;DMA控制器用于实现直接内存访问,提高数据传输效率;中断控制器用于处理外部设备的中断请求。

在设计芯片的硬件最小系统时,需要考虑各个部分之间的协调与配合。

例如,CPU需要能够正确读取存储器中的指令和数据,并执行相应的操作;输入输出接口需要能够正确地与外部设备进行数据交换;时钟系统需要能够提供稳定的时钟信号给各个部件。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

芯片硬件训练课程资料Version 1.0应用中心整理MAR. 11, 2004注意:本文档仅供凌耀内部参考使用,文中所有说明与数据资料已尽可能更新验证,但未必完全正确。

读者若有疑义,皆以凌阳课程训练影音资料为依据,对文中的不妥和错误之处,欢迎不吝指正!目录1I/O 配置1.1输入口(Input) (6)1.1.1INPUT结构 (6)1.1.2输入口浮空(Floating) (6)1.1.3输入口上拉(Pull high) (6)1.1.4输入口下拉(Pull low) (6)1.1.5输入口自动配置(Auto feedback) (7)1.2输出口(Output) (7)1.2.1OUTPUT结构 (7)1.2.2缓冲输出(Buffer) (7)1.2.3PMOS漏极开路输出(ODP) (7)1.2.4NMOS漏极开路输出(ODN) (8)1.3利用输入、输出特性组态 (8)1.3.1用输出sink和输入floating组态ODN (8)1.3.2用输出send和输入floating组态ODP (8)1.4I/O结构图 (9)1.5I/O基本应用 (9)1.5.1I/O默认状态 (9)1.5.2键盘扫描 (9)1.5.3键盘和LED扫描 (12)1.5.4用RC电路实现数字I/O读取模拟量 (12)1.5.5在没有实时时钟的条件下实现定时唤醒 (14)1.5.6斯密特触发器用途 (14)1.5.7I/O在debug时的用途 (15)1.5.8用RC电路评估中断占用的CPU时钟资源 (15)1.6应用注意事项 (15)1.6.1输出latch up问题 (15)1.6.2寄生二极管对马达驱动的影响 (16)1.6.3输入Floating静态电流问题 (17)1.6.4输出切换到输入问题 (17)1.6.5Read-Modify-Write问题 (18)1.6.6时钟线和数据线的安排 (18)1.6.7节省指令周期的问题 (18)1.6.8输入输出的耐压问题 (18)1.6.9如何检查I/O是否有Floating (19)1.6.10I/O Option和I/O Switch (20)1.6.11I/O输入输出之间切换时应注意的问题 (20)1.6.12马达驱动问题 (20)1.6.13输入弹跳问题 (21)2Audio输入/输出2.1DAC输出原理 (21)2.2PWM输出原理 (21)2.3DAC其他应用 (22)2.3.2用DAC做A/D (22)2.4应用注意问题 (22)2.4.1 电流输出DAC放大线路 (22)2.4.1.1 最基本的晶体管DAC放大线路 (22)2.4.1.2 静态工作点可调整的基本DAC放大线路 (23)2.4.1.3 切入电压提高的基本DAC放大线路 (23)2.4.1.4 小信号提升的基本DAC放大线路 (24)2.4.1.5 喇叭与晶体管DAC放大线路阻抗匹配问题 (24)2.4.1.6 集成音频放大器 (25)2.4.1.7 不同音频输出方式信号混合 (26)2.4.2 Ramp Up/Ramp Down (26)2.4.3 Concatenate接音问题 (27)3液晶显示(LCD)3.1驱动液晶的两个基本特性 (28)3.1.1液晶的驱动电压应该为交流信号 (28)3.1.2液晶的驱动显示由驱动电压的有效值决定 (28)3.2液晶显示动态扫描的原理 (29)3.3占空比(Duty) (30)3.4偏压比(Bias) (30)3.5工作电压(V op或Vlcd) (31)3.6液晶显示器件的类型 (31)3.6.1V.T 曲线 (31)3.6.2TN型液晶显示器 (32)3.6.3STN型液晶显示器 (32)3.7驱动类型 (33)3.7.1Type A ………………………………………………………..………………… .. 333.7.2Type B (33)3.7.3TFT (34)3.8断电的问题 (34)3.9升压原理 (34)3.9.1电容交换式充放电的原理 (34)4系统问题4.1上电复位 (35)4.1.1马达启动时电源电压被拉低 (35)4.1.2旧电池将电源电压拉低 (35)4.1.3电源端噪声将电源电压拉低 (35)4.1.4芯片内部的上电复位部分 (35)4.1.5外部Reset ……………………………………………………………………… .. 354.2低电压复位(LVD) (36)4.2.1电池的使用寿命与系统崩溃 (36)4.3看门狗计数器(WATCHDOG)的架构 (37)4.4系统复位不成功的软件处理方法 (37)4.5芯片之间的连接问题 (37)4.5.1SPDC + SPLD (37)4.6电池电压超过器件手册规定电压 (38)4.6.1基本规格 (38)4.6.2增加二极管 (38)4.6.3使用 regulator (38)4.7PCB layout 应注意的问题 (38)4.7.1系统特定的一些管脚 (38)4.7.1.1振荡电阻部分 (38)4.7.1.2晶振部分 (38)4.7.1.3Reset管脚 (39)4.7.2电源和地 (39)5系统稳定性及检测方法5.1RAM 的检测 (39)5.2ROM 的检测 (39)5.3下载程序 (39)5.4功能检测 (39)5.5程序撰写的注意事项 (39)5.6调试工具的使用(示波器) (39)5.6.1校正 (39)5.6.2触发模式 (39)5.6.3持续模式 (40)5.6.4接地问题 (40)5.6.5其他 (40)6程序问题6.1中断和背景程序寄存器使用问题 (40)6.2ICE断点设置 (40)6.3实时性程式的调试 (40)7音质问题7.1对采样频率的限制 (40)7.2算法因素 (41)7.3实时中断问题 (41)7.4输出功率问题 (41)8典型的Sunplus振荡线路8.1R- oscillator结构 (42)8.2R- oscillator原理 (42)8.3SUNPLUS R-C oscillator (43)8.4crystal oscillator原理 (44)8.5CMOS Crystal oscillator原理 (44)8.6测量振荡电路的增益 (47)8.7选择晶体振荡器 (47)8.7.1Crystal Type(晶体振荡) (47)8.7.2Ceramic Resonator(陶瓷振荡) (48)8.7.3Crystal应用上之关键参数 (48)8.8振荡器应用 (48)8.8.1Crystal OSC应用注意事项 (48)8.8.2客户应用常见问题 (48)9常用应用线路9.1简单类似ADC功能应用电路 (49)9.1.1 最基本的I/O ADC (49)9.1.2 较佳的I/O ADC (50)9.1.3 用比较器做ADC (51)9.2AC电路9.2.1AC电源负载电路 (52)9.2.2AC控制电路 (52)10ESD和Latch-up10.1ESD概念 (53)10.2芯片级ESD的评估和测量 (53)10.3从系统的角度进行ESD保护 (53)10.3.1 系统ESD概念 (53)10.3.2 ESD如何干扰系统 (53)10.4测量I/V曲线检查ESD破坏 (53)10.5芯片级和系统级ESD的区别 (54)10.6CMOS Latch-up Scheme (54)10.6.1 CMOS寄生闸流体的结构 (54)10.6.2 CMOS DEVICE SYMBOL&LAYOUT (55)10.6.3MOS LAYOUT & CROSS SECTION (56)10.6.4 Latch-up Scheme (56)10.7从系统的角度分析Latch-up保护 (57)10.7.1 可能触发IC Latch-up的因素 (57)10.7.2 因ESD导致Latch-up (57)10.7.3 系统防Latch-up对策 (57)10.8ESD和Latch-up案例分析 (58)10.8.1 HBM ESD损坏 (58)10.8.2 CDM ESD损坏 (58)10.8.3 System ESD损坏 (59)11客诉处理11.1客户问题处理步骤 (59)11.2不良问题复制方向 (59)11.3问题分析建言 (59)11.4软件常犯错误 (60)口就能实现多个按键扫描。

标志位检测出I/O状态,用LDA指令就可检测出P/N位的状态。

1.6.8 输入输出的耐压问题:2.4.2 Ramp Up/Ramp DownDAC输出音频信号的时候,其参考电平不是0,否则负半周音频信号无法输出。

如果直接开始或结束音频输出,因开始和结束点参考电平突变,会产生一个“bo”音,因此,需在开始和结束音频信号播放时使DAC缓慢的上升和下降,以最低限度地降低“bo”音,这种过程称为Ramp Up和Ramp Down,如图2-16所示。

阈值电压则工作电压(Vlcd或V op)也要相应的增加,具体值由各LCD厂商提供。

3.6液晶显示器件的类型3.6.1 V.T曲线V.T.曲线描绘了所加驱动电压波形的有效值与液晶显示器件显示部分亮度变化的对应关系。

3.6.2 TN 型液晶显示器TN (Twist Nematic )即扭曲向列型液晶。

将涂有透明导电层的两片玻璃基板间夹上一层正介电异向性液晶,液晶分子沿玻璃表面平行排列,排列方向在上下玻璃之间连续扭转90°。

然后上下各加一偏光片,底面加上反光片,基本就构成了TN 型液晶。

示意图如图所示:TN型器件分子排布与透过光示意图3.6.3 STN型液晶显示器STN (Super TN)型液晶,跟TN 型液晶结构大体相同,只不过液晶分子不是扭曲90°而是扭曲180°,还可以扭曲210°或270°等,其特点是电光响应曲线更好,可以适应更多的行列驱动。

3.7 驱动类型3.7.1 Type A驱动波形如下所示:3.7.2 Type B驱动波形如下所示:3.7.3 TFTTFT(Thin Film Transistor)为薄膜晶体管有源矩阵液晶显示器件,在每个像素点上设计一个场效应开关管,这样就容易实现真彩色、高分辨率的液晶显示器件。

基于FET(场效应管)工作原理:至当机。

若RESET pin 未接电容,VDD 和RESET pin同时以相同速度加电时,IC 内部工作秩序会因为没有参考信号而不确定,所以,必须在上电时依靠外部时序做参考,这就要求RESET pin 电平上升速度比VDD pin 电平上升速度慢,以保证IC 每次加电时按同一流程可靠工作。