24c64C储存单元使用说明及程序控制

MSP430 24C64控制程序

#ifndef _I2C_H#define _I2C_H#define SDA_1 P4OUT|=0x02 //SDA = 1#define SDA_0 P4OUT&=~0x02 //SDA = 0#define SCL_1 P4OUT|=0x01 //SCL = 1#define SCL_0 P4OUT&=~0x01 //SCL = 0#define SDA_IN P4DIR&=~0x02; //I/O口为输入#define SDA_OUT P4DIR|=0x02 //I/0口为输出#define J_SDA_1_or_0 (P4IN&0x02)==0x02//--------------------------------------------//--------以下为24C64读写子函数//DELAY 函数程序//功能:延时子程序//========================================== static void Delay(unsigned int n){while(n!=0){n--;}}//=========================================//START 函数程序//功能:开始闪存操作//========================================== void Start(void){SDA_OUT;SDA_1;Delay(10);SCL_1;Delay(10);SDA_0;Delay(10);SCL_0;Delay(10);}//=========================================//STOP 函数程序//功能:停止闪存操作//========================================== void Stop(void){SDA_0;Delay(10);SCL_1;Delay(10);SDA_1;Delay(10);}void TX_Byte(unsigned char WriteData){unsigned char i,j;j="WriteData";SDA_OUT;for (i=0; i<8; i++){if ((j&0x80)==0){ SDA_0;}else{ SDA_1;}j <<=1;Delay(10);SCL_1;Delay(10);SCL_0;Delay(10);}}unsigned char RX_Byte(void){unsigned char i;unsigned char TempData = 0;SDA_IN;for (i=0; i<8; i++){Delay(10);SCL_1;Delay(10);TempData <<= 1;if (J_SDA_1_or_0){ TempData++; }SCL_0;Delay(10);}SDA_OUT;return(TempData);}//=========================================//ACK 函数程序//功能:挂高电平表示闪存时钟信号//========================================== void ReceiveAck(void){SDA_IN;SCL_1;Delay(10);while (J_SDA_1_or_0){ }SCL_0;SDA_OUT;Delay(10);}unsigned char ReadWord(unsigned long int unit/*address*/) {unsigned char LowAdd = 0;unsigned char HighAdd = 0;unsigned char TempData = 0;LowAdd = (unsigned char)unit;HighAdd = (unsigned char)(unit >> 8);SDA_OUT;Start();TX_Byte(0xa0);ReceiveAck();TX_Byte(HighAdd);ReceiveAck();TX_Byte(LowAdd);ReceiveAck();Start();TX_Byte(0xa1);ReceiveAck();TempData = RX_Byte();Stop();Delay(8000);return(TempData);}void WriteWord(unsigned long int unit/*address*/, unsigned char WriteData) {unsigned char LowAdd = 0;unsigned char HighAdd = 0;LowAdd = (unsigned char)unit;HighAdd = (unsigned char)(unit >> 8);Start();TX_Byte(0xa0);ReceiveAck();TX_Byte(HighAdd);ReceiveAck();TX_Byte(LowAdd);ReceiveAck();TX_Byte(WriteData);ReceiveAck();Stop();Delay(8000);}#endif。

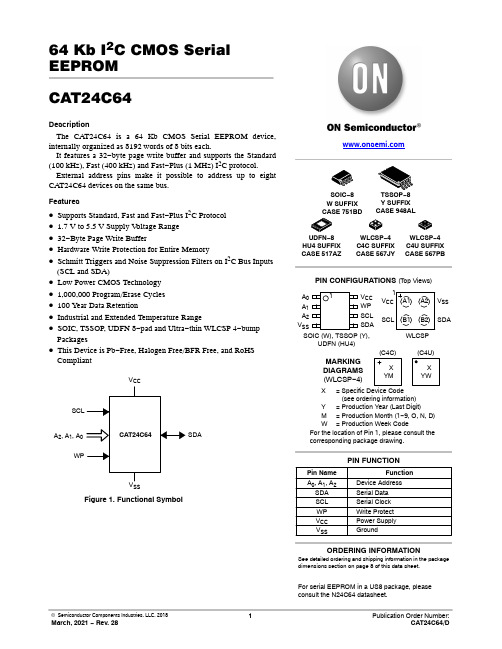

CAT24C64 D64 64Kb I2C CMOS 序列 EEPROM 数据手册说明书

64 Kb I2C CMOS Serial EEPROMCAT24C64DescriptionThe CAT24C64 is a 64 Kb CMOS Serial EEPROM device, internally organized as 8192 words of 8 bits each.It features a 32−byte page write buffer and supports the Standard (100 kHz), Fast (400 kHz) and Fast−Plus (1 MHz) I2C protocol. External address pins make it possible to address up to eight CAT24C64 devices on the same bus.Features•Supports Standard, Fast and Fast−Plus I2C Protocol•1.7 V to 5.5 V Supply V oltage Range•32−Byte Page Write Buffer•Hardware Write Protection for Entire Memory•Schmitt Triggers and Noise Suppression Filters on I2C Bus Inputs (SCL and SDA)•Low Power CMOS Technology•1,000,000 Program/Erase Cycles•100 Year Data Retention•Industrial and Extended Temperature Range•SOIC, TSSOP, UDFN 8−pad and Ultra−thin WLCSP 4−bump Packages•This Device is Pb−Free, Halogen Free/BFR Free, and RoHS CompliantFigure 1. Functional Symbol SDASCL WPV CC SSA2, A1, APIN CONFIGURATIONS (Top Views)See detailed ordering and shipping information in the package dimensions section on page 8 of this data sheet.ORDERING INFORMATIONSOIC−8W SUFFIXCASE 751BDSOIC (W), TSSOP (Y),UDFN (HU4)Y SUFFIXCASE 948ALDevice AddressA0, A1, A2Serial DataSDASerial ClockSCLWrite ProtectWPPower SupplyV CCGroundV SSFunctionPin NamePIN FUNCTIONFor the location of Pin 1, please consult thecorresponding package drawing.UDFN−8HU4 SUFFIXCASE 517AZWLCSP−4C4C SUFFIXCASE 567JYSDAWPV CCV SSA2A1A01SCLWLCSPA1A2B1B2SDAV SSSCLV CC1X= Specific Device Code(see ordering information)Y= Production Year (Last Digit)M= Production Month (1−9, O, N, D)W= Production Week CodeMARKINGDIAGRAMS(WLCSP−4)WLCSP−4C4U SUFFIXCASE 567PBXYM(C4C)For serial EEPROM in a US8 package, pleaseTable 1. ABSOLUTE MAXIMUM RATINGSParameters Ratings Units Storage Temperature–65 to +150°C Voltage on Any Pin with Respect to Ground (Note 1)–0.5 to +6.5V Stresses exceeding those listed in the Maximum Ratings table may damage the device. If any of these limits are exceeded, device functionality should not be assumed, damage may occur and reliability may be affected.1.The DC input voltage on any pin should not be lower than −0.5 V or higher than V CC + 0.5 V. During transitions, the voltage on any pin mayundershoot to no less than −1.5 V or overshoot to no more than V CC + 1.5 V, for periods of less than 20 ns.Table 2. RELIABILITY CHARACTERISTICS (Note 2)Symbol Parameter Min UnitsN END (Note 3)Endurance1,000,000Program/Erase Cycles T DR Data Retention100Years2.These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC−Q100and JEDEC test methods.3.Page Mode, V CC = 5 V, 25°C.Table 3. D.C. OPERATING CHARACTERISTICS(V CC = 1.8 V to 5.5 V, T A = −40°C to +125°C and V CC = 1.7 V to 5.5 V, T A = −40°C to +85°C, unless otherwise specified.)Symbol Parameter Test Conditions Min Max UnitsI CCR Read Current Read, f SCL = 400 kHz1mAI CCW Write Current Write, f SCL = 400 kHz2mAI SB Standby Current All I/O Pins at GND or V CC T A = −40°C to +85°CV CC≤ 3.3 V1m AT A = −40°C to +85°CV CC > 3.3 V3T A = −40°C to +125°C5I L I/O Pin Leakage Pin at GND or V CC2m AV IL Input Low Voltage−0.5V CC x 0.3V V IH Input High Voltage V CC x 0.7V CC + 0.5V V OL1Output Low Voltage V CC≥ 2.5 V, I OL = 3.0 mA0.4V V OL2Output Low Voltage V CC < 2.5 V, I OL = 1.0 mA0.2V Table 4. PIN IMPEDANCE CHARACTERISTICS(V CC = 1.8 V to 5.5 V, T A = −40°C to +125°C and V CC = 1.7 V to 5.5 V, T A = −40°C to +85°C, unless otherwise specified.) Symbol Parameter Conditions Max UnitsC IN (Note 4)SDA I/O Pin Capacitance V IN = 0 V8pFC IN (Note 4)Input Capacitance (other pins)V IN = 0 V6pFI WP (Note 5)WP Input Current V IN < V IH, V CC = 5.5 V130m AV IN < V IH, V CC = 3.3 V120V IN < V IH, V CC = 1.8 V80V IN> V IH2I A (Note 5)Address Input Current(A0, A1, A2)Product Rev F V IN < V IH, V CC = 5.5 V50m A V IN < V IH, V CC = 3.3 V35V IN < V IH, V CC = 1.8 V25V IN> V IH24.These parameters are tested initially and after a design or process change that affects the parameter according to appropriate AEC−Q100and JEDEC test methods.5.When not driven, the WP, A0, A1 and A2 pins are pulled down to GND internally. For improved noise immunity, the internal pull−down is relativelystrong; therefore the external driver must be able to supply the pull−down current when attempting to drive the input HIGH. T o conserve power, as the input level exceeds the trip point of the CMOS input buffer (~ 0.5 x V CC), the strong pull−down reverts to a weak current source.Table 5. A.C. CHARACTERISTICS(V CC = 1.8 V to 5.5 V, T A = −40°C to +125°C and V CC = 1.7 V to 5.5 V, T A = −40°C to +85°C.) (Note 6)Symbol ParameterStandardV CC = 1.7 V − 5.5 VFastV CC = 1.7 V − 5.5 VFast−PlusV CC = 1.7 V − 5.5 VT A = −405C to +855CUnits Min Max Min Max Min MaxF SCL Clock Frequency1004001,000kHzt HD:STA START Condition Hold Time40.60.25m s t LOW Low Period of SCL Clock 4.7 1.30.45m s t HIGH High Period of SCL Clock40.60.40m s t SU:STA START Condition Setup Time 4.70.60.25m s t HD:DAT Data In Hold Time000m s t SU:DAT Data In Setup Time25010050ns t R (Note 7)SDA and SCL Rise Time1,000300100ns t F (Note 7)SDA and SCL Fall Time300300100ns t SU:STO STOP Condition Setup Time40.60.25m s t BUF Bus Free Time BetweenSTOP and START4.7 1.30.5m st AA SCL Low to Data Out Valid 3.50.90.40m s t DH Data Out Hold Time10010050ns T i (Note 7)Noise Pulse Filtered at SCLand SDA Inputs100100100ns t SU:WP WP Setup Time000m s t HD:WP WP Hold Time 2.5 2.51m s t WR Write Cycle Time555mst PU (Notes 7, 8)Power−up to Ready Mode110.11ms Product parametric performance is indicated in the Electrical Characteristics for the listed test conditions, unless otherwise noted. Product performance may not be indicated by the Electrical Characteristics if operated under different conditions.6.Test conditions according to “A.C. Test Conditions” table.7.Tested initially and after a design or process change that affects this parameter.8.t PU is the delay between the time V CC is stable and the device is ready to accept commands.Table 6. A.C. TEST CONDITIONSInput Levels0.2 x V CC to 0.8 x V CCInput Rise and Fall Times≤ 50 nsInput Reference Levels0.3 x V CC, 0.7 x V CCOutput Reference Levels0.5 x V CCOutput Load Current Source: I OL = 3 mA (V CC≥ 2.5 V); I OL = 1 mA (V CC< 2.5 V); C L = 100 pFPower −On Reset (POR)Each CAT24C64 incorporates Power −On Reset (POR)circuitry which protects the internal logic against powering up in the wrong state. The device will power up into Standby mode after V CC exceeds the POR trigger level and will power down into Reset mode when V CC drops below the POR trigger level. This bi −directional POR behavior protects the device against ‘brown −out’ failure following a temporary loss of power.Pin DescriptionSCL: The Serial Clock input pin accepts the clock signal generated by the Master.SDA: The Serial Data I/O pin accepts input data and delivers output data. In transmit mode, this pin is open drain. Data is acquired on the positive edge, and is delivered on the negative edge of SCL.A 0, A 1 and A 2: The Address inputs set the device address that must be matched by the corresponding Slave address bits. The Address inputs are hard −wired HIGH or LOW allowing for up to eight devices to be used (cascaded) on the same bus. When left floating, these pins are pulled LOW internally. The Address inputs are not available for use with WLCSP 4−bumps.WP: When pulled HIGH, the Write Protect input pin inhibits all write operations. When left floating, this pin is pulled LOW internally. The WP input is not available for the WLCSP 4−bumps, therefore all write operations are allowed for the device in this package.Functional DescriptionThe CAT24C64 supports the Inter −Integrated Circuit (I 2C) Bus protocol. The protocol relies on the use of a Master device, which provides the clock and directs bus traffic, and Slave devices which execute requests. The CAT24C64operates as a Slave device. Both Master and Slave cantransmit or receive, but only the Master can assign those roles.I 2C Bus ProtocolThe 2−wire I 2C bus consists of two lines, SCL and SDA,connected to the V CC supply via pull −up resistors. The Master provides the clock to the SCL line, and either the Master or the Slaves drive the SDA line. A ‘0’ is transmitted by pulling a line LOW and a ‘1’ by letting it stay HIGH. Data transfer may be initiated only when the bus is not busy (see A.C. Characteristics). During data transfer, SDA must remain stable while SCL is HIGH.START/STOP Condition An SDA transition while SCL is HIGH creates a START or STOP condition (Figure 2). The START consists of a HIGH to LOW SDA transition, while SCL is HIGH. Absent the START, a Slave will not respond to the Master. The STOP completes all commands, and consists of a LOW to HIGH SDA transition, while SCL is HIGH.Device AddressingThe Master addresses a Slave by creating a START condition and then broadcasting an 8−bit Slave address. For the CA T24C64, the first four bits of the Slave address are set to 1010 (Ah); the next three bits, A 2, A 1 and A 0, must match the logic state of the similarly named input pins. The devices in WLCSP 4−bumps respond only to the Slave Address with A2 A1 A0 = 000 (CA T24C64C4xTR). The R/W bit tells the Slave whether the Master intends to read (1) or write (0) data (Figure 3).AcknowledgeDuring the 9th clock cycle following every byte sent to the bus, the transmitter releases the SDA line, allowing the receiver to respond. The receiver then either acknowledges (ACK) by pulling SDA LOW, or does not acknowledge (NoACK) by letting SDA stay HIGH (Figure 4). Bus timing is illustrated in Figure 5.START CONDITIONSTOP CONDITIONSDASCLFigure 2. Start/Stop TimingFigure 3. Slave Address BitsDEVICE ADDRESS** The devices in WLCSP 4−bumps respond only to the Slave Address with: A2 A1 A0 = 000, CAT24C64C4xTRFigure 4. Acknowledge TimingSCL FROM MASTERDATA OUTPUTFROM TRANSMITTERDATA OUTPUT FROM RECEIVER≥ t SU:DAT )Figure 5. Bus TimingSCLSDA INSDA OUTWRITE OPERATIONSByte WriteTo write data to memory, the Master creates a START condition on the bus and then broadcasts a Slave address with the R/W bit set to ‘0’. The Master then sends two address bytes and a data byte and concludes the session by creating a STOP condition on the bus. The Slave responds with ACK after every byte sent by the Master (Figure 6). The STOP starts the internal Write cycle, and while this operation is in progress (t WR ), the SDA output is tri −stated and the Slave does not acknowledge the Master (Figure 7).Page WriteThe Byte Write operation can be expanded to Page Write,by sending more than one data byte to the Slave before issuing the STOP condition (Figure 8). Up to 32 distinct data bytes can be loaded into the internal Page Write Buffer starting at the address provided by the Master. The page address is latched, and as long as the Master keeps sending data, the internal byte address is incremented up to the end of page, where it then wraps around (within the page). New data can therefore replace data loaded earlier. Following the STOP, data loaded during the Page Write session will be written to memory in a single internal Write cycle (t WR ).Acknowledge PollingAs soon (and as long) as internal Write is in progress, the Slave will not acknowledge the Master. This feature enables the Master to immediately follow −up with a new Read or Write request, rather than wait for the maximum specified Write time (t WR ) to elapse. Upon receiving a NoACK response from the Slave, the Master simply repeats the request until the Slave responds with ACK.Hardware Write ProtectionWith the WP pin held HIGH, the entire memory is protected against Write operations. If the WP pin is left floating or is grounded, it has no impact on the Write operation. The state of the WP pin is strobed on the last falling edge of SCL immediately preceding the 1st data byte (Figure 9). If the WP pin is HIGH during the strobe interval,the Slave will not acknowledge the data byte and the Write request will be rejected.Delivery StateThe CAT24C64 is shipped erased, i.e., all bytes are FFh.SLAVE ADDRESSSA ***C KA C KA C KS T O P PST ARTA CKBUS ACTIVITY:MASTER SLAVEADDRESS BYTE ADDRESS BYTE DAT A BYTE Figure 6. Byte Write Sequence*a 15 − a 13 are don’t care bits.a 15 − a 8a 7 − a 0d 7 − d 0Figure 7. Write Cycle TimingSTOPCONDITIONSTARTCONDITIONADDRESSSCLSDASLAVE ADDRESSSA C K A C K C K ST ARTC K S T O C KC K C K BUSACTIVITY:MASTER SLAVEADDRESS BYTE ADDRESS BYTEDATA BYTE DATA BYTE DATA BYTE Figure 8. Page Write SequenceFigure 9. WP TimingADDRESS BYTE DATA BYTESCLSDA WPREAD OPERATIONSImmediate ReadTo read data from memory, the Master creates a START condition on the bus and then broadcasts a Slave address with the R/W bit set to ‘1’. The Slave responds with ACK and starts shifting out data residing at the current address.After receiving the data, the Master responds with NoACK and terminates the session by creating a STOP condition on the bus (Figure 10). The Slave then returns to Standby mode.Selective ReadTo read data residing at a speci fic address, the selected address must first be loaded into the internal address register.This is done by starting a Byte Write sequence, whereby the Master creates a START condition, then broadcasts a Slave address with the R/W bit set to ‘0’ and then sends two address bytes to the Slave. Rather than completing the ByteWrite sequence by sending data, the Master then creates a START condition and broadcasts a Slave address with the R/W bit set to ‘1’. The Slave responds with ACK after every byte sent by the Master and then sends out data residing at the selected address. After receiving the data, the Master responds with NoACK and then terminates the session by creating a STOP condition on the bus (Figure 11).Sequential ReadIf, after receiving data sent by the Slave, the Master responds with ACK, then the Slave will continue transmitting until the Master responds with NoACK followed by STOP (Figure 12). During Sequential Read the internal byte address is automatically incremented up to the end of memory, where it then wraps around to the beginning of memory.Figure 10. Immediate Read Sequence and TimingSCL SDA 8th Bit STOPNO ACKDATA OUT89SLAVE ADDRESSSA C KDATA BYTEN OA C K S T O P PST ARTBUS ACTIVITY:MASTER SLAVEFigure 11. Selective Read SequenceSLAVE ADDRESS SA C KA C KA C K ST ARTSLAVE SA C KS T A R T PS T O P ADDRESS BYTE ADDRESS BYTE ADDRESSN O A C KDATA BYTEBUS ACTIVITY:MASTER SLAVEFigure 12. Sequential Read SequenceS T O SLAVE C KA C A C N O A C A C BYTE n BYTE n+1BYTE n+2BYTE n+xBUS ACTIVITY:MASTERSLAVEORDERING INFORMATIONDevice Order Number SpecificDeviceMarking Package Type Temperature Range Lead Finish ShippingCAT24C64WI−GT324C64F SOIC−8, JEDEC I = Industrial(−40°C to +85°C)NiPdAu Tape & Reel,3,000 Units / ReelCAT24C64YI−GT3C64F TSSOP−8I = Industrial(−40°C to +85°C)NiPdAu Tape & Reel,3,000 Units / ReelCAT24C64HU4I−GT3C6U UDFN−8I = Industrial(−40°C to +85°C)NiPdAu Tape & Reel,3,000 Units / ReelCAT24C64C4CTR A WLCSP−4with Die CoatIndustrial(−40°C to +85°C)N/A Tape & Reel,5,000 Units / ReelCAT24C64C4UTR A WLCSP−4with Die CoatIndustrial(−40°C to +85°C)N/A Tape & Reel,5,000 Units / Reel9.All packages are RoHS−compliant (Lead−free, Halogen−free).10.The standard lead finish is NiPdAu.11.For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel PackagingSpecifications Brochure, BRD8011/D.12.Caution: The EEPROM devices delivered in WLCSP must never be exposed to ultra violet light. When exposed to ultra violet lightthe EEPROM cells lose their stored data.UDFN8, 2x3 EXTENDED PADCASE 517AZ ISSUE ADATE 23 MAR 2015SCALE 2:1NOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DIMENSION b APPLIES TO PLATEDTERMINAL AND IS MEASURED BETWEEN 0.15 AND 0.25MM FROM THE TERMINAL TIP .4.COPLANARITY APPLIES TO THE EXPOSEDPAD AS WELL AS THE TERMINALS.DIM MIN MAX MILLIMETERS A 0.450.55A10.000.05b 0.200.30D 2.00 BSC D2 1.35 1.45E 3.00 BSC E2 1.25 1.35e 0.50 BSC L 0.250.35*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*DIMENSIONS: MILLIMETERSDETAIL AA30.13 REF L1DETAIL ALALTERNATE CONSTRUCTIONSLL1−−−0.15RECOMMENDEDGENERICMARKING DIAGRAM*XXXXX = Specific Device Code A = Assembly Location WL = Wafer Lot Y = YearW = Work WeekG= Pb −Free Package*This information is generic. Please refer to device data sheet for actual part marking.Pb −Free indicator, “G” or microdot “ G ”,may or may not be present.XXXXX AWLYW G18XDETAIL BALTERNATE CONSTRUCTIONSWLCSP4, 0.77x0.77CASE 567JY ISSUE CDATE 07 MAR 2017PIN A1REFERENCESCALE 4:1TOP VIEWBOTTOM VIEWDIMENSIONS: MILLIMETERS*For additional information on our Pb −Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*RECOMMENDEDNOTES:1.DIMENSIONING AND TOLERANCING PER ASME Y14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DATUM C, THE SEATING PLANE, IS DEFINED BY THE SPHERICAL CROWNS OF THE SOLDER BALLS.4.COPLANARITY APPLIES TO SPHERICAL CROWNS OF THE SOLDER BALLS.5.DIMENSION b IS MEASURED AT THE MAXIMUMCONTACT BALL DIAMETER PARALLEL TO DATUM C.6.BACKSIDE COATING IS OPTIONAL.DIM A MIN NOM −−−MILLIMETERS A1D E b 0.150.155e0.40 BSC−−−0.040.06A20.23 REF A30.025 REF 0.750.770.750.77MAX 0.160.350.080.790.79DETAIL ANOTE 6X = Specific Device Code Y = YearW= Work Week*This information is generic. Please refer to device data sheet for actual part marking.Pb −Free indicator, “G” or microdot “ G ”,may or may not be present.GENERICMARKING DIAGRAM*X YWWLCSP4, 0.77x0.77CASE 567PBISSUE ADATE 09 NOV 2016PIN A1REFERENCESCALE 4:1TOP VIEWBOTTOM VIEWDIMENSIONS: MILLIMETERS*For additional information on our Pb−Free strategy and solderingdetails, please download the ON Semiconductor Soldering andMounting Techniques Reference Manual, SOLDERRM/D.SOLDERING FOOTPRINT*RECOMMENDEDNOTES:1.DIMENSIONING AND TOLERANCING PER ASMEY14.5M, 1994.2.CONTROLLING DIMENSION: MILLIMETERS.3.DATUM C, THE SEATING PLANE, IS DEFINED BY THESPHERICAL CROWNS OF THE SOLDER BALLS.4.COPLANARITY APPLIES TO SPHERICAL CROWNS OFTHE SOLDER BALLS.5.DIMENSION b IS MEASURED AT THE MAXIMUMCONTACT BALL DIAMETER PARALLEL TO DATUM C.6.BACKSIDE COATING IS OPTIONAL.DIMAMIN NOM−−−MILLIMETERSA1DEb0.150.155e0.40 BSC−−−0.040.055A20.19 REFA30.025 REF0.750.770.750.77MAX0.160.300.070.790.79DETAIL ANOTE 6X= Specific Device CodeY= YearW= Work Week*This information is generic. Please refer todevice data sheet for actual part marking.Pb−Free indicator, “G” or microdot “ G”,may or may not be present.GENERICMARKING DIAGRAM*XYWSOIC −8, 150 mils CASE 751BD ISSUE ODATE 19 DEC 2008IDENTIFICATIONTOP VIEWSIDE VIEWEND VIEWNotes:(1) All dimensions are in millimeters. Angles in degrees.(2) Complies with JEDEC MS-012.SYMBOLMIN NOM MAX θA A1b cD E E1e h 0º8º0.100.330.190.254.805.803.801.27 BSC1.750.250.510.250.505.006.204.00L0.401.271.35TSSOP8, 4.4x3.0, 0.65PCASE 948AL ISSUE ADATE 20 MAY 2022qXXX = Specific Device Code Y = YearWW = Work WeekA = Assembly Location G= Pb −Free Package*This information is generic. Please refer to device data sheet for actual part marking.Pb −Free indicator, “G” or microdot “G ”, may or may not be present. Some products may not follow the Generic Marking.GENERICMARKING DIAGRAM*XXX YWW A GPUBLICATION ORDERING INFORMATIONTECHNICAL SUPPORTLITERATURE FULFILLMENT:。

M24C32,M24C64--存储芯片手册免费下载

64Kbit and 32Kbit Serial I²C Bus EEPROM

FEATURES SUMMARY

■ Two-Wire I2C Serial Interface Supports 400kHz Protocol

■ Single Supply Voltage: – 4.5 to 5.5V for M24Cxx – 2.5 to 5.5V for M24Cxx-W – 1.8 to 5.5V for M24Cxx-R

Table 1. Product List

Reference

Part Number

M24C64

M24C64

M24C64-W

M24C64-R

M24C32

M24C32

M24C32-W

M24C32-R

Figure 1. Packages

8 1

PDIP8 (BN)

8 1

SO8 (MN) 150 mil width

MEMORY ORGANIZATION . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 Figure 6. Block Diagram . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7

TSSOP8 (DW) 169 mil width

UFDFPN8 (MB) 2x3mm² (MLP)

数据存储AT24Cxx及其应用

AT24CXX电气特性

AT24CXX电气特性

ቤተ መጻሕፍቲ ባይዱ 100KHz参数分析

• f=100KHz=0.1MHz • t=1/0.1us=5us(一个高电平持续的时间+一 个低电平持续的时间) • scl的高低电平持续时间各为3us • scl为高电平时,sda数据线电平不能变化 (否则就是开始信号或停止信号);scl为 低电平时,sda数据线电平才能变化(即此 时给sda赋需要发送的值)。

I2C总线的信号类型

• 开始信号:SCL为高电平时,SDA由高电 平向低电平跳变,开始传送数据。 • 结束信号:SCL为高电平时,SDA由低电 平向高电平跳变,结束传送数据。

I2C总线的信号类型

• 位的传输 SDA 线上的数据必须在时钟的高电平周期 保持稳定,数据线的高或低电平状态只有 在SCL 线的时钟信号是低电平时才能改变。

SDA SDA

存储器

SCL

SCL

SDA SCL

SDA

SDA

SCL

SCL

A/D

LED

SCL

SCL

Vcc

I2C (I2C、 IIC )总线概述

R1 R2

单片机 键盘 D/A

SDA

SDA

SDA SDA

存储器

SCL

SCL

SDA SCL

SDA

SDA

SCL

SCL

A/D

LED

• 其中,I2C总线的SCL和SDA端口(开漏极,线与)在使用时 必须连接上拉电阻。I2C总线的传输速率可以支持100khz和 400khz两种,对于100khz的速率一般采用10k欧姆的上拉电 阻,对于400khz的速率一般采用2k欧姆的上拉电阻。

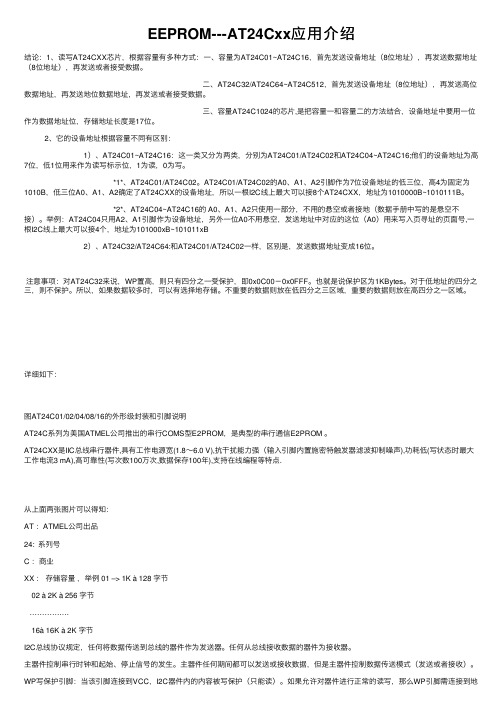

EEPROM---AT24Cxx应用介绍

EEPROM---AT24Cxx应⽤介绍结论:1、读写AT24CXX芯⽚,根据容量有多种⽅式:⼀、容量为AT24C01~AT24C16,⾸先发送设备地址(8位地址),再发送数据地址(8位地址),再发送或者接受数据。

⼆、AT24C32/AT24C64~AT24C512,⾸先发送设备地址(8位地址),再发送⾼位数据地址,再发送地位数据地址,再发送或者接受数据。

三、容量AT24C1024的芯⽚,是把容量⼀和容量⼆的⽅法结合,设备地址中要⽤⼀位作为数据地址位,存储地址长度是17位。

2、它的设备地址根据容量不同有区别: 1)、AT24C01~AT24C16:这⼀类⼜分为两类,分别为AT24C01/AT24C02和AT24C04~AT24C16;他们的设备地址为⾼7位,低1位⽤来作为读写标⽰位,1为读,0为写。

*1*、AT24C01/AT24C02。

AT24C01/AT24C02的A0、A1、A2引脚作为7位设备地址的低三位,⾼4为固定为1010B,低三位A0、A1、A2确定了AT24CXX的设备地址,所以⼀根I2C线上最⼤可以接8个AT24CXX,地址为1010000B~1010111B。

*2*、AT24C04~AT24C16的 A0、A1、A2只使⽤⼀部分,不⽤的悬空或者接地(数据⼿册中写的是悬空不接)。

举例:AT24C04只⽤A2、A1引脚作为设备地址,另外⼀位A0不⽤悬空,发送地址中对应的这位(A0)⽤来写⼊页寻址的页⾯号,⼀根I2C线上最⼤可以接4个,地址为101000xB~101011xB 2)、AT24C32/AT24C64:和AT24C01/AT24C02⼀样,区别是,发送数据地址变成16位。

注意事项:对AT24C32来说,WP置⾼,则只有四分之⼀受保护,即0x0C00-0x0FFF。

也就是说保护区为1KBytes。

对于低地址的四分之三,则不保护。

所以,如果数据较多时,可以有选择地存储。

经典的24C01--24C256读写操作程序

//EepromType为枚举变量 需为M2401至M24256中的一种 分别对应24C01至24C256;

//函数返回值为一个位变量,若返回1表示此次操作失效,0表示操作成功;

//ERRORCOUNT为允许最大次数,若出现ERRORCOUNT次操作失效后,则函数中止操作,并返回1

{

SDA=1;

SCL=1;

_nop_();

_nop_();

_nop_();

_nop_();

SCL=0;

}

/*******************向IIC总线写数据*********************/

void IICSendByte(unsigned char sendbyte)

{

void Delay(unsigned char DelayCount);

void IICStart(void);

void IICStop(void);

bit IICRecAck(void);

void IICNoAck(void);

void IICAck(void);

unsigned char IICReceiveByte(void);

/**********************从IIC总线上读数据子程序**********/

unsigned char IICReceiveByte(void)

{

register receivebyte i=8;

SCL=0;

while(i--)

{

SCL=1;

receivebyte=(receivebyte<<1)|SDA;SCL=0;

24C64中文资料

EEPROM是"Electrically Erasable Programmable Read-only"(电可擦写可编程只读存储器)的缩写,EEPROM在正常情况下和EPROM一样,可以在掉电的情况下保存数据,所不同的是它可以在特定引脚上施加特定电压或使用特定的总线擦写命令就可以在在线的情况下方便完成数据的擦除和写入,这使EEPROM被用于广阔的的消费者范围,如:汽车、电信、医疗、工业和个人计算机相关的市场,主要用于存储个人数据和配置/调整数据。

EEPROM又分并行EEPROM和串行EEPROM,并行EEPROM器件虽然有很快的读写的速度,但要使用很多的电路引脚。

串行EEPROM器件功能上和并行EEPROM基本相同,提供更少的引脚数、更小的封装、更低的电压和更低的功耗,是现在使用的非易失性存储器中灵活性最高的类型。

串行EEPROM按总线分,常用的有I2C,SPI,Microwire总线。

本文将介绍这三种总线连接单片机的编程方法。

I2C总线I2C总线(Inter Integrated Circuit内部集成电路总线)是两线式串行总线,仅需要时钟和数据两根线就可以进行数据传输,仅需要占用微处理器的2个IO引脚,使用时十分方便。

I2C总线还可以在同一总线上挂多个器件,每个器件可以有自己的器件地址,读写操作时需要先发送器件地址,该地址的器件得到确认后便执行相应的操作,而在同一总线上的其它器件不做响应,称之为器件寻址,这个原理就像我们打电话的原理相当。

I2C总线产生80年代,由PHLIPS公司开发,早期多用于音频和视频设备,如今I2C总线的器件和设备已多不胜数。

最常见的采用I2C总线的EEPROM也已被广泛使用于各种家电、工业及通信设备中,主要用于保存设备所需要的配置数据、采集数据及程序等。

生产I2C总线EEPROM的厂商很多,如ATMEL、Microchip公司,它们都是以24来开头命名芯片型号,最常用就是24C系列。

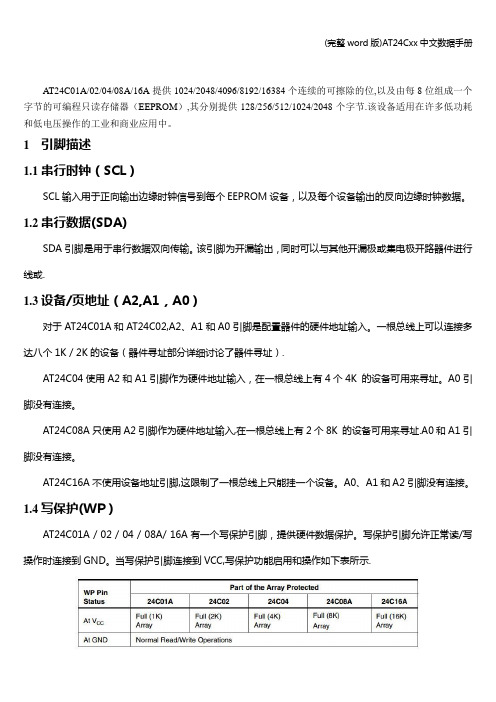

(完整word版)AT24Cxx中文数据手册

AT24C01A/02/04/08A/16A提供1024/2048/4096/8192/16384个连续的可擦除的位,以及由每8位组成一个字节的可编程只读存储器(EEPROM),其分别提供128/256/512/1024/2048个字节.该设备适用在许多低功耗和低电压操作的工业和商业应用中。

1引脚描述1.1串行时钟(SCL)SCL输入用于正向输出边缘时钟信号到每个EEPROM设备,以及每个设备输出的反向边缘时钟数据。

1.2串行数据(SDA)SDA引脚是用于串行数据双向传输。

该引脚为开漏输出,同时可以与其他开漏极或集电极开路器件进行线或.1.3设备/页地址(A2,A1,A0)对于AT24C01A和AT24C02,A2、A1和A0引脚是配置器件的硬件地址输入。

一根总线上可以连接多达八个1K / 2K的设备(器件寻址部分详细讨论了器件寻址).AT24C04使用A2和A1引脚作为硬件地址输入,在一根总线上有4个4K 的设备可用来寻址。

A0引脚没有连接。

AT24C08A只使用A2引脚作为硬件地址输入,在一根总线上有2个8K 的设备可用来寻址.A0和A1引脚没有连接。

AT24C16A不使用设备地址引脚,这限制了一根总线上只能挂一个设备。

A0、A1和A2引脚没有连接。

1.4写保护(WP)AT24C01A / 02 / 04 / 08A/ 16A有一个写保护引脚,提供硬件数据保护。

写保护引脚允许正常读/写操作时连接到GND。

当写保护引脚连接到VCC,写保护功能启用和操作如下表所示.2设备操作2.1时钟和数据转换SDA引脚通常情况下拉高.SDA引脚上的数据只能在SCL低时间段内更改,而启动条件或停止条件在SCL 为高时进行。

2.2启动条件在任何其他指令之前,SDA由高变为低,且SCL为高。

2.3停止条件SDA由低变为高,且SCL为高。

在读取序列之后,执行停止命令后EEPROM进入备用电源模式.2.4应答所有地址和数据字都是从EEPROM串行发送和接收8位字节。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

{ uchar i;

if(n>32) //n 不能大于 32,会从头覆盖字节

{ n=32; } start_24c64();

writebyte_24c64(0xa0);//写 写指令(A0A1A2=000)

writebyte_24c64(addH);//写高位地址 writebyte_24c64(addL);//写低位地址 stop_24c64(); start_24c64();

{ n = 32; }

for(i=0;i<n;i++)

{ writebyte_24c64(*(m_data_24c64++));//写储存数据

Delay_xus(1);

}

stop_24c64();

}

void read_m_data_24c64(uchar addH,uchar addL,uchar n)//从某地址开始连续读取 n 个数据

scl_24c64 = 1;

Delay_xus(1);

sda_24c64 = 1; //SDA 上升沿

Delay_xus(1);

scl_24c64 = 0;

}

void ask_24c64() //写数据应答,第九个脉冲 sda_24c64 为低,则 24c64 成功接受数据

{ uchar k=30;

void Delay_xus(uint i)//(16+9*i)us(51) { while(i--); } void Delay_100ms()//(16+9*i)us(51) { uchar i;

uint j = 1000; for(;j>0;j--) { i = 14;

while(i--); } } /*****24c64 开始启动,停止,应答*************/ /*当 SCL 为高电平时 SDA 为下降沿时为起始条件,SDA 为上升沿则叫停止*/ void start_24c64() //开始 { sda_24c64 = 1; scl_24c64 = 1; Delay_xus(1); //也可不用延时,怕你单片机快; sda_24c64 = 0; //SDA 下降沿 Delay_xus(1); scl_24c64 = 0; //控制时钟线,防止数据误入;I2C 总线空闲时,sda、scl 为高电平 } void stop_24c64() //停止 { sda_24c64 = 0;

3)读操作 读操作的初始化与写操作是相同的,唯一不同的是读/写选择位要置为 1。

读操作有三种:当前地址读、字节读、序列读。 1.当前地址读: 芯片内部地址计数器记录了最后一次读或写操作后的地址(地址自动加 1),

这个地址只要芯片电源供给正常就一直有效。在读操作中,当地址到达最后一个 地址(最后一个页的最后一个字节)后会自动“回滚”到最开始的位置(第一个 页的第一个字节)。而在写操作中,“回滚”则是从当前页的最后一个字节转到该 页的第一个字节。当选择位置 1 后的设备地址码写入芯片,并回应后,当前地址 上的数据将会串行输出。此时,单片机应产生一个停止条件。 当前地址读的时序图:

源程序

#include <reg51.h> #define uint unsigned int #define uchar unsigned char /********************24c64 定义*********************/ sbit sda_24c64 = P2^0; //24c64 定义数据线 sbit scl_24c64 = P2^1; //24c64 定义时钟线 /******************延时***********************/

//sda_24c64=0;

scl_24c64 = 0;

scl_24c64 = 1;

Delay_xus(1);

while(sda_24c64&&k--);//结合写数据发第九个脉冲,检查应答位,若无应答,一定时间

后退出

scl_24c64 = 0;

}

/****************************************/

{ uchar temp; Nhomakorabeastart_24c64();

writebyte_24c64(0xa0);//写 写指令(A0A1A2=000)

writebyte_24c64(addH);//写高位地址

writebyte_24c64(addL);//写低位地址

stop_24c64();

start_24c64();

第 8 位是读/写操作选择位。如果是 1 的话,一个读操作将被初始化, 而如果是 0 的话,则一个写操作将被初始化。 2)写操作

1.任意字节写:在进行写操作时,在设备地址与回复后,需要写入两个 8 位地址。在收到地址后,芯片会返回一个低电平应答打信号,然后就可以写入一 个 8 位数据。在收到这个 8 位数据后,芯片会返回一个低电平答打信号,此时应 产生一个停止条件。芯片开始自身的读入过程。在读入过程中,所有的数据输入 都是无效的,芯片也不会给予回复

字节写的时序:

2.页写:24C64 也是支持页写的。 页写的初始化与字节写是相同的,页写初始化与字节写相同,只是主器

件不会在第一个数据后发送停止条件,而是在EEPROM的ACK以后,接着发送7个 (24C02)或15个(24C04/08/16)或31个(24C32/64)数据。EEPROM收到每个数 据后都应答“0”。最后仍需由主器件发送停止条件,终止写序列。接收到每个数 据后,字地址的低5位内部自动加1,高位地址位不变,维持在当前页内。当内部 产生的字地址达到该页边界地址时,随后的数据将写入该页的页首。如果32个数 据传送给了EEPROM,字地址将回转到该页的首字节,先前的字节将会被覆盖。 页写的时序图:

scl_24c64 = 0;

for(i=0;i<8;i++)

{ data_from_24c64<<=1;

scl_24c64 = 1;

Delay_xus(1);

data_from_24c64 |= sda_24c64;

Delay_xus(1); scl_24c64 = 0; } sda_24c64 = ack;

在开始条件使芯片使能后,需要给其写入一个 8 位的设备地址码,以使 某一芯片被命中。在地址码的开头有两个“10”序列,共 4 位,然后是 3 位 的 地址,最后是 1 位的读写标识位。具体的地址码结构如下:

24C64 使用 3 个设备地址位 A2、A1、A0 使多达 8 个芯片同时存在于一 条总线上。这个地址码被每一个芯片与自身设置的地址相比较。

void writebyte_24c64(uchar data_to_24c64)//写入数据

{ uchar i;

scl_24c64 = 0;

for(i=0;i<8;i++)

{ if(data_to_24c64&0x80)sda_24c64 = 1;

else

sda_24c64 = 0;

scl_24c64 = 1; //时钟线低变高,发数据

scl_24c64 = 1;

scl_24c64 = 0;

sda_24c64 = 1;

return data_from_24c64;

}

void write_o_data_24c64(uchar addH,uchar addL,uchar data_24c64)//写入单个数据

{ start_24c64();

I2C 24c64 储存单元说明及使用

24C64 提供 65536 个位,它们是以字节方式进行组织的。通过设置不同的地 址,可以实现多达 8 个芯片共享两线总线。它被广泛应用于工业、化工等需要低 功耗与低电压的领域。同时,它还提供诸如 4.5V~5.5V、2.7V~5.5V、2.5V~5.5V 与 1.8V~5.5V 各种工作电压范围的芯片,从而使其应用更加通用。 24C64 的引脚定义:

Delay_xus(1);

scl_24c64 = 0;

data_to_24c64<<=1;

}

ask_24c64();

}

uchar readbyte_24c64(uchar ack) //ack 应答位,ack=1,MCU 不应答(不继续接受数据),ack=0,

MCU 应答,继续接受数据

{ uchar i,data_from_24c64=0;

引脚功能详细描述:

引脚名称 A0~A2 SDA SCL WP

功能 地址输入 串行数据 串行时钟输入 写保护

引脚功能描述: 串行时钟(SCL):在 SCL 的上升沿数据写入芯片中,在下降沿从芯片中读出数 据。 串行数据(SDA):SDA 用作双向数据传输。这个引脚是漏极开路驱动,需要加 上拉电阻。 设备地址(A2,A1,A0):A2~A0 是设备地址设置引脚,可以通过接高或接低 来设置不同的地址,也可以直接悬空。设置为不同地址时最多可以在同一总线上 存在多达 8 个芯片。当这些引脚悬空时,默认地址为 0。 写保护(WP):当此引脚接到 GND 上时,允许正常的写操作。当 WP 接到 VCC 时,所有的写操作都是被禁止的。如果悬空,则 WP 在内部被拉到 GND。 24C64 的组织方式:

writebyte_24c64(0xa1);//写 读指令(A0A1A2=000)

temp = readbyte_24c64(1);

stop_24c64();

return temp;

}

/*void write_m_data_24c64(uchar addH,uchar addL,uchar *m_data_24c64,uchar n) //从某地址开