EDA07

简述eda技术

简述eda技术EDA技术,即电子设计自动化技术(Electronic Design Automation),是应用计算机技术和软件工具来辅助电子系统的设计、验证和制造的一种技术。

EDA技术在电子系统设计领域起到了重要的作用,大大提高了设计效率和产品质量。

EDA技术主要包括电子系统级设计(ESL)、硬件描述语言(HDL)、逻辑综合、电路仿真、布局布线、测试和制造等方面。

其中,硬件描述语言是EDA技术的核心之一。

硬件描述语言是一种用于描述电子系统结构和行为的高级语言,常用的硬件描述语言有VHDL和Verilog。

通过硬件描述语言,设计工程师可以方便地描述电路的逻辑功能和时序特性,实现电路设计的高效、精确和灵活。

逻辑综合是EDA技术中的重要环节,它将高级语言描述的电路转化为门级电路的表示。

逻辑综合过程中,常常涉及到逻辑优化、时序优化和面积优化等技术。

逻辑综合的目标是使电路满足特定的性能指标,如时序约束、功耗限制和面积约束等,同时尽量减少电路的成本和设计周期。

电路仿真是EDA技术中另一个重要的环节,它通过计算机模拟电路的行为,验证电路的正确性和性能是否满足设计要求。

电路仿真可以分为功能仿真和时序仿真两个层次。

功能仿真主要验证电路的逻辑功能是否正确,而时序仿真则进一步验证电路的时序特性是否满足设计要求。

通过仿真,设计工程师可以及时发现和解决电路设计中的问题,提高设计的可靠性和稳定性。

布局布线是EDA技术中的另一个重要环节,它主要负责将逻辑电路映射到物理布局上,并进行连线。

布局布线过程中,需要考虑到电路的时序约束、功耗和面积等因素,以及避免电路中的时序冲突和信号干扰等问题。

布局布线的目标是使电路在给定的约束条件下,尽量满足性能要求,并达到最佳的物理布局效果。

测试是EDA技术中的另一个重要环节,它主要用于验证电路的正确性和可靠性。

测试过程中,常常需要设计和生成一系列的测试模式,以覆盖电路的所有可能工作状态,并通过测试模式来判断电路的输出是否与预期一致。

eda数字系统设计自动化知识点

eda数字系统设计自动化知识点

EDA数字系统设计自动化主要包含以下几个知识点:

1.EDA技术概述:EDA技术即电子设计自动化技术,是以计算机为工具,使用通用软件包,开展电子电路设计、电子电路仿真、PCB设计,CPLD/FPGA设计,IC设计等工作。

它是基于大规模可编程器件的,以硬件描述语言HDL来完成表达,实现对逻辑的编译化简、分割、布局、优化等目标的一门新技术。

2.EDA技术实现目标:EDA技术的目标是电子系统设计,具体包括ASIC设计和PCB设计两部分。

3.可编程逻辑器件PLD:PLD的应用与集成规模的扩大为数字系统的设计带来了极大的方便和灵活性,变革了传统的数字系统设计理念、过程、方法。

通过对PLD技术不断地改进提高,EDA技术应运而生。

4.ASIC设计与应用:ASIC是一种具有专门功能的集成电路,通常也被称为IC、芯片。

EDA技术被广泛应用于ASIC设计。

5.FPGA设计与应用:FPGA是现场可编程门阵列的简称,也是一种常见的数字系统设计自动化工具。

通过EDA技术,操作者可以通过利用软件来实现对硬件功能的一个描述,之后利用FPGA/CPLD才可得到最终设计结果。

6.CPLD设计与应用:CPLD是复杂可编程逻辑器件的简称,与FPGA一样,是EDA技术应用的重要领域。

此外,还需要掌握硬件描述语言(如VHDL或Verilog)、仿真工具(如ModelSim)、布局布线工具(如Allegro或Palladium)等EDA工具的使用。

eda实验7段数码显示译码器

7段数码显示译码器设计宁夏大学物理电气信息学院 2010级通信工程专业马福蕊 2012/12/16【摘要】7段数码管是纯组合电路,通常的小规模专用IC,如74或4000系列的器件只能做十进制BCD译码,然而数字系统中的处理和运算都是二进制,所以输出表达都是十六进制的,为了满足十六进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD中来实现。

本实验中的7段译码管输出信号LED7S的7位分别接数码管的7个段,高位在左,低位在右。

【关键字】七段显示译码器;VHDL语言;QuartusⅡ软件一、相关介绍1、VHAL语言的简介VHDL 的英文全名是 Very-High-Speed Integrated Circuit Hardware Description Language,诞生于 1982 年。

1987 年底,VHDL被 IEEE 和美国国防部确认为标准硬件描述语言。

VHDL主要用于描述数字系统的结构,行为,功能和接口。

除了含有许多具有硬件特征的语句外,VHDL的语言形式和描述风格与句法是十分类似于一般的计算机高级语言。

VHDL的程序结构特点是将一项工程设计,或称设计实体(可以是一个元件,一个电路模块或一个系统)分成外部(或称可视部分,及端口)和内部(或称不可视部分),既涉及实体的内部功能和算法完成部分。

在对一个设计实体定义了外部界面后,一旦其内部开发完成后,其他的设计就可以直接调用这个实体。

这种将设计实体分成内外部分的概念是VHDL 系统设计的基本点。

VHDL语言用于数字系统设计的主要优点是:允许用软件描述系统的硬件结构,即描述系统怎样分解为子系统和子系统间怎样互连;允许使用类似常用编程语言形式的系统功能指标;允许对系统设计在制造前以低廉的花费进行性能模拟验证;允许设计的详细结构从更抽象的性能指标出发沿自顶向下的路线分层次地进行综合;允许设计重用和在可编程ASIC器件上生成设计芯片。

2、Quartus II的简介Quartus II提供了完全集成且与电路结构无关的开发包环境,具有数字逻辑设计的全部特性,包括:可利用原理图、结构框图、VerilogHDL、AHDL 和VHDL完成电路描述,并将其保存为设计实体文件;芯片(电路)平面布局连线编辑; LogicLock增量设计方法,用户可建立并优化系统,然后添加对原始系统的性能影响较小或无影响的后续模块;功能强大的逻辑综合工具;完备的电路功能仿真与时序逻辑仿真工具;定时/时序分析与关键路径延时分析;可使用SignalTap II逻辑分析工具进行嵌入式的逻辑分析;支持软件源文件的添加和创建,并将它们链接起来生成编程文件;使用组合编译方式可一次完成整体设计流程;自动定位编译错误;高效的期间编程与验证工具;可读入标准的EDIF网表文件、VHDL网表文件和Verilog网表文件;能生成第三方EDA软件使用的VHDL网表文件和Verilog网表文件。

EDA技术-实验七.八-频率计文件

TESTCTL程序library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity TESTCTL isport (clk:in std_logic;tsten,clr_cnt,load:out std_logic); end TESTCTL;architecture behav of TESTCTL is signal div2clk: std_logic;beginprocess(clk)beginif clk'event and clk='1' thendiv2clk<=not div2clk;end if;end process;process(clk,div2clk)beginif clk='0'and div2clk='0' thenclr_cnt<='1';else clr_cnt<='0'; end if;end process;load<=not div2clk; tsten<=div2clk; end behav;cnt1000程序library ieee;use ieee.std_logic_1164.all;entity cnt1000 isport(clk:in std_logic;clr:in std_logic;ena:in std_logic;cout: out std_logic);end cnt1000;architecture behav of cnt1000 is beginprocess(clk,clr,ena)variable cqi:integer range 0 to 1000; beginif clr='1' then cqi:=0;elsif clk'event and clk='1' thenif ena='1' thenif cqi<999 then cqi:=cqi + 1 ;else cqi:=0;end if;end if;end if;if cqi=999then cout<='1';else cout<='0';end if;end process;end behav;library ieee;use ieee.std_logic_1164.all;USE IEEE.STD_LOGIC_UNSIGNED.ALL; entity cnt10 isport(clk:in std_logic;clr:in std_logic;ena:in std_logic;cq:out std_logic_vector(3 downto 0);carry_out: out std_logic);end cnt10;architecture behav of cnt10 issignal cqi: std_logic_vector(3 downto 0); beginprocess(clk,clr,ena)beginif clr='1' then cqi<="0000";elsif clk'event and clk='1' thenif ena='1' thenif cqi < "1001" thencqi<=cqi + 1 ;else cqi<="0000";end if;end if;end if;end process;process(cqi)beginif cqi="1001"then carry_out<='1';else carry_out<='0';end if;end process;cq<=cqi;end behav;library ieee;use ieee.std_logic_1164.all;entity reg4b isport(load:in std_logic;din:in std_logic_vector(3 downto 0); dout:out std_logic_vector(3 downto 0)); end reg4b;architecture behav of reg4b isbeginprocess(load,din)beginif load'event and load='1' then dout<=din; end if;end process;end behav;reg1b程序library ieee;use ieee.std_logic_1164.all;entity reg1b isport(load:in std_logic;din:in std_logic;dout:out std_logic);end reg1b;architecture behav of reg1b isbeginprocess(load,din)beginif load'event and load='1' then dout<=din; end if;end process;end behav;xcqxcq程序library ieee;use ieee.std_logic_1164.all;entity xcqxcq isport(a:in std_logic;d1:in std_logic_vector(3 downto 0);d2:in std_logic_vector(3 downto 0);d3:in std_logic_vector(3 downto 0);d4:in std_logic_vector(3 downto 0);O1:out std_logic_vector(3 downto 0);O2:out std_logic_vector(3 downto 0);O3:out std_logic_vector(3 downto 0);O4:out std_logic_vector(3 downto 0));end xcqxcq;architecture behav of xcqxcq isbeginprocess(a,d1,d2,d3,d4)beginif a='1' then O1<="1111"; O2<="1111";O3<="1111"; O4<="1111";elsif d2="0000"and d3="0000"and d4="0000" then O1<="0000"; O2<="0000";O3<="0000"; O4<="0000"; else O1<=d1;O2<=d2;O3<=d3;O4<=d4;end if;end process;end behav;decl7s程序library ieee;use ieee.std_logic_1164.all;entity decl7s isport(a :in bit_vector(3 downto 0);led7s:out bit_vector(6 downto 0));end;architecture one of decl7s isbeginprocess(a)begincase a(3 downto 0) iswhen "0000"=>led7s<="0111111"; when "0001"=>led7s<="0000110"; when "0010"=>led7s<="1011011"; when "0011"=>led7s<="1001111"; when "0100"=>led7s<="1100110"; when "0101"=>led7s<="1101101"; when "0110"=>led7s<="1111101"; when "0111"=>led7s<="0000111"; when "1000"=>led7s<="1111111"; when "1001"=>led7s<="1101111"; when "1111"=>led7s<="1110110"; when others=>led7s<="0111111"; end case;end process;end;波形仿真。

EDA实验七报告

实验七FIR滤波器1.已知4阶直接型FIR滤波器的表述如下,试实现该逻辑:y(n)=x(n)h(0)+x(n-1)h(1)+x(n-2)h(2)+x(n-3)h(3)其中x(n)与x(n-m),m=0,1,2,3是延迟关系,m表示延迟的clk数。

x(n-m)与h(m)的位宽均为8位,y(n)为10位,其中h(m)在模块例化后为常数。

该模块的输入为x(n)、clk,输出为y(n)。

程序设计:module FIR1(x,clk,RST,y);input [7:0]x;input clk;input RST;output [9:0]y;reg [7:0]x0,x1,x2,x3;parameter h0=1,h1=1,h2=1,h3=1;always@(posedge clk or negedge RST)beginif(!RST) beginx3<=0; x2<=0; x1<=0;x0<=0; endelse beginx0<=x;x1<=x0;x2<=x1;x3<=x2; endendassign y=x0*h0+x1*h1+x2*h2+x3*h3;endmodule图7-1 4阶直接性FIR滤波器的仿真波形图图7-2 4阶直接型FIR滤波器的RTL图实验分析:该程序主要由一个过程语句组成,敏感信号为时钟信号的上升沿和复位端的下降沿,实现同步时钟异步清零功能:若 RST=0,四个寄存器都清零;RST≠0,移位寄存。

最后使用阻塞式赋值语句输出y的值。

仿真波形图如图7-1所示,x=02H时,y=02H*1+01H*1+12H*1+11H*1=026H;x=12H时,y=12H*1+11H*1=23H;x=10H时,y=10H*1+05H*1+04H*1+02H*1=01BH;RST=0时,y=0,经过验证波形符合实验要求,证明程序正确。

该程序的RTL图如图7-2所示。

eda简介(eda简介)

---------------------------------------------------------------最新资料推荐------------------------------------------------------eda简介(eda简介)eda 简介(eda 简介) EDA in the communications industry (Telecommunication) another explanation is the enterprise data architecture, EDA gives a general view of an enterprise data architecture, and in accordance with the characteristics of telecom enterprises, the framework and hierarchy. EDA is an electronic design automation (Electronic Design Automation): from the computer aided design in the middle of 1960s (CAD), computer aided manufacturing (CAM), computer aided test (CAT) and Computer Aided Engineering (CAE) and the concept of development. Catalog First, what is EDA? Two, design methods Three 、 EDA tool software classification Four, EDA tool software vendors tycoon three Five, compounds Six. Exploratory data analysis Seven. Distribution estimation algorithm 1. What is EDA? Two, design methods Three 、 EDA tool software classification Four, EDA tool software vendors tycoon three Five, compounds Six. Exploratory data analysis Seven, distribution estimation algorithm Edit this paragraph 1. What is EDA? In 1990s, the international advanced electronic and computer technology in the world, has been exploring new methods of electronic circuit design actively,1 / 23and made a thorough change in design methods, tools etc, with great success. In the field of electronic technology design, the application of programmable logic devices (such as CPLD, FPGA) has been widely popularized. These devices bring great flexibility to the design of digital systems. These devices can be programmed by software to reconstruct their hardware structure and working mode, so that the hardware design can be as convenient and fast as the software design. All these greatly changed the traditional digital system design method, design process and design concept, and promoted the rapid development of EDA technology. EDA technology is a computer as a tool for designers in the EDA software platform, using hardware description language VHDL to complete the design documents, and then the computer automatically complete logic compilation, simplification, segmentation, synthesis, optimization, layout, simulation, adaptive translation, logical mapping and programming work until the chip for the specific target the. The emergence of EDA technology greatly improves the efficiency and operability of circuit design, and reduces the labor intensity of designers. Using EDA tools, the electronics designer can start the electronic system design from concept, algorithm and protocol, a lot of work can be done through the---------------------------------------------------------------最新资料推荐------------------------------------------------------ computer and electronic products can be from circuit design and performance analysis to design the whole process of IC territory or PCB layout of the computer automatically complete the processing. Now, the concept or category of EDA is very wide. Including mechanical, electronic, communications, aerospace, chemical, mineral, biological, medical, military and other fields, there are EDA applications. At present, EDA technology has been widely used in major companies, enterprises and institutions and scientific research and teaching departments. For example, in the aircraft manufacturing process, from design, performance testing and characteristic analysis until the flight simulation, may involve EDA technology. The concept of EDA EDA technology refers to the computer as the work platform, the latest achievements of the integration application of electronic technology, computer technology, information processing and intelligent technology, the automatic design of electronic products. Using EDA tools, the electronics designer can start the electronic system design from concept, algorithm and protocol, a lot of work can be done through the computer and electronic products can be from circuit design and performance analysis to design the whole process of IC3 / 23territory or PCB layout of the computer automatically complete the processing. Now, the concept or category of EDA is very wide. Including mechanical, electronic, communications, aerospace, chemical, mineral, biological, medical, military and other fields, there are EDA applications. At present, EDA technology has been widely used in major companies, enterprises and institutions and scientific research and teaching departments. For example, in the aircraft manufacturing process, from design, performance testing and characteristic analysis until the flight simulation, may involve EDA technology. This paper refers to the EDA technology, mainly for electronic circuit design, PCB design and IC design. EDA design can be divided into system level, circuit level and physical implementation level. Edit paragraph two, design method (1) front end design (system modeling, RTL level description), back end design (FPGAASIC) system modeling (2) IP multiplexing (3) front-end design (4) system description: establish the mathematical model of the system. (5) function description: describe the behavior of the system or the data flow diagram among the sub modules. (6) logic design: the system function is structured, usually with text, schematics, logic diagrams, Boolean expressions to represent the design results. (7)---------------------------------------------------------------最新资料推荐------------------------------------------------------ simulation: including function simulation and timing simulation, mainly verify the correctness and timing characteristics of the system function. Edit this paragraph three, EDA tool software classification EDA tool software can be roughly divided into three categories: chip design assistance software, programmable chip aided design software, system design auxiliary software and so on. Currently entering the country and has a wide influence in the EDA software system design software and programmable chip design software: Protel, Altium Designer, PSPICE, multiSIM10 (the latest version of the original EWB, OrCAD, PCAD), LSIIogic, MicroSim, ISE, Modelsim, Matlab and so on. These tools are strong function, generally can be used in several aspects such as many software can realize the circuit design and simulation, PCB automatic layout and also can output a variety of file with third party software interface. According to the main function or the main application situation, divided into circuit design and simulation tools, PCB design software, IC design software, PLD design tools and other EDA software, a brief introduction. 3.1 electronic circuit design and simulation tools, we may have used the test board or something else to make some electronic5 / 23system to practice. But sometimes, we find that there are a lot of problems to be done, not previously thought, so that waste our time and supplies. It also increases the product development cycle and extends the product listing time, so that the product loses the market competitive advantage. Is there a way to know the result without using the electric iron test board? The conclusion is that this is the circuit design and simulation technology. When it comes to electronic circuit design and simulation tools, this technology can not be mentioned in the United States, can not help but mention their aircraft design why high efficiency. Our previous design of a medium-sized aircraft, from the draft to the detailed design to the wind tunnel test, and finally to the map to the actual production, the entire cycle is about 10 years. And the United States is 1 years old. Why is there such a big gap? Because the United States is most used in the design of virtual simulation technology, the wind tunnel experiment parameters accumulated over the years into the computer, and then through the computer programming written in a virtual environment of software, and enable it to experience parameters automatically apply the relevant formula and call after long-term accumulated input computer. In this way, as long as the aircraft shape meter data---------------------------------------------------------------最新资料推荐------------------------------------------------------in the virtual wind tunnel test software, where unreasonable have changes there, until the best effect, efficiency is high, as long as the final test several times for shortage in the actual environment can be established, from their Boeing 747 to F16 is this method uses the. The aerodynamic data are provided by senior experts, and the software developer is IBM. The engineer of the aerocraft only needs to use the simulation software to do a variety of simulation debugging work on the computer platform. Similarly, many of their other things are using a similar approach, from big to small, from complexity to simplicity, and even to design furniture and composition, but the specific content of the software is different. In fact, they invented the first generation of computers for this purpose (originally for efficient design of artillery and related shells and other large amount of design). Electronic circuit design and simulation tools include SPICE/PSPICE; multiSIM7; Matlab; SystemView; mmicad LiveWire、爱迪生、蒂娜亲明亮的火花等。

什么是EDA技术

什么是EDA技术EDA是电子设计自动化(Electronic Design Automation)缩写,是90年代初从CAD(计算机辅助设计)、CAM(计算机辅助制造)、CAT(计算机辅助测试)和CAE(计算机辅助工程)的概念发展而来的。

EDA技术是以计算机为工具,根据硬件描述语言HDL( Hardware Description language)完成的设计文件,自动地完成逻辑编译、化简、分割、综合及优化、布局布线、仿真以及对于特定目标芯片的适配编译和编程下载等工作。

典型的EDA工具中必须包含两个特殊的软件包,即综合器和适配器。

综合器的功能就是将设计者在EDA平台上完成的针对某个系统项目的HDL、原理图或状态图形描述,针对给定的硬件系统组件,进行编译、优化、转换和综合,最终获得我们欲实现功能的描述文件。

综合器在工作前,必须给定所要实现的硬件结构参数,它的功能就是将软件描述与给定的硬件结构用一定的方式联系起来。

也就是说,综合器是软件描述与硬件实现的一座桥梁。

综合过程就是将电路的高级语言描述转换低级的、可与目标器件FPGA/CPLD相映射的网表文件。

适配器的功能是将由综合器产生的王表文件配置与指定的目标器件中,产生最终的下载文件,如JED文件。

适配所选定的目标器件(FPGA/CPLD芯片)必须属于在综合器中已指定的目标器件系列。

硬件描述语言HDL是相对于一般的计算机软件语言,如:C、PASCAL而言的。

HDL语言使用与设计硬件电子系统的计算机语言,它能描述电子系统的逻辑功能、电路结构和连接方式。

设计者可利用HDL程序来描述所希望的电路系统,规定器件结构特征和电路的行为方式;然后利用综合器和适配器将此程序编程能控制FPGA和CPLD内部结构,并实现相应逻辑功能的的门级或更底层的结构网表文件或下载文件。

目前,就FPGA/CPLD开发来说,比较常用和流行的HDL主要有ABEL-HDL、AHDL和VHDL。

EDA实验七八实验报告(1)

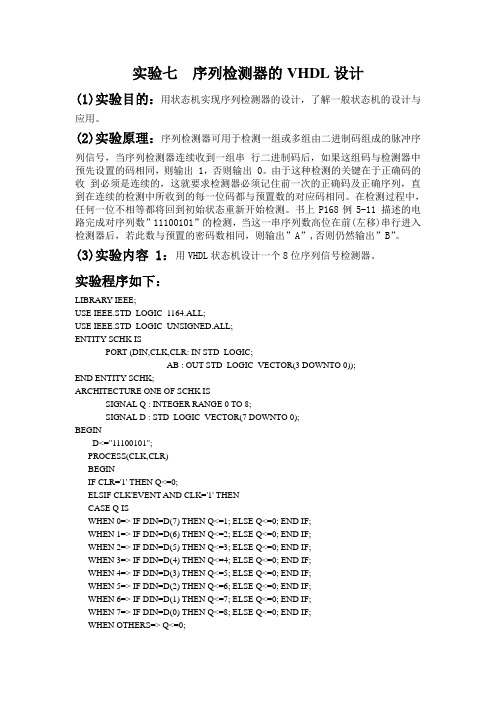

实验七序列检测器的VHDL设计(1)实验目的:用状态机实现序列检测器的设计,了解一般状态机的设计与应用。

(2)实验原理:序列检测器可用于检测一组或多组由二进制码组成的脉冲序列信号,当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出 1,否则输出 0。

由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置数的对应码相同。

在检测过程中,任何一位不相等都将回到初始状态重新开始检测。

书上P168例5-11 描述的电路完成对序列数”11100101”的检测,当这一串序列数高位在前(左移)串行进入检测器后,若此数与预置的密码数相同,则输出”A”,否则仍然输出”B”。

(3)实验内容 1:用VHDL状态机设计一个8位序列信号检测器。

实验程序如下:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY SCHK ISPORT (DIN,CLK,CLR: IN STD_LOGIC;AB : OUT STD_LOGIC_VECTOR(3 DOWNTO 0));END ENTITY SCHK;ARCHITECTURE ONE OF SCHK ISSIGNAL Q : INTEGER RANGE 0 TO 8;SIGNAL D : STD_LOGIC_VECTOR(7 DOWNTO 0);BEGIND<="11100101";PROCESS(CLK,CLR)BEGINIF CLR='1' THEN Q<=0;ELSIF CLK'EVENT AND CLK='1' THENCASE Q ISWHEN 0=> IF DIN=D(7) THEN Q<=1; ELSE Q<=0; END IF;WHEN 1=> IF DIN=D(6) THEN Q<=2; ELSE Q<=0; END IF;WHEN 2=> IF DIN=D(5) THEN Q<=3; ELSE Q<=0; END IF;WHEN 3=> IF DIN=D(4) THEN Q<=4; ELSE Q<=0; END IF;WHEN 4=> IF DIN=D(3) THEN Q<=5; ELSE Q<=0; END IF;WHEN 5=> IF DIN=D(2) THEN Q<=6; ELSE Q<=0; END IF;WHEN 6=> IF DIN=D(1) THEN Q<=7; ELSE Q<=0; END IF;WHEN 7=> IF DIN=D(0) THEN Q<=8; ELSE Q<=0; END IF;WHEN OTHERS=> Q<=0;END CASE;END IF;END PROCESS;PROCESS(Q)BEGINIF Q=8 THEN AB<="1010";ELSE AB<="1011";END IF;END PROCESS;END ARCHITECTURE ONE;实验步骤如下:1 将源程序以SCHK.vhd的形式存入D盘名为liulin的文件夹中2 全程编译3 时序仿真4 引脚锁定和下载引脚锁定如下:CLR-PIN34;CLK-PIN32;DIN- PIN33;AB[0]- PIN77、 AB[1]- PIN78、AB[2]- PIN83、 AB[3]- PIN84;5 实际测试时序仿真波形如下图:实验分析:选择电路模式 No.8 。