A case for flash memory ssd in enterprise database applications

电脑开机英文注解

英文:Reboot and select proper Boot device or Insert Boot Media in Selected Boot device and press a key中文:重新启动,并选择适当的启动设备或插入开机媒体在选定的开机装置,并按下一个键。

解决:你的电脑可能检测不到硬盘,重新插在主板另一个IDE槽里。

如果不行重装系统。

英文:CMOS battery failed中文:CMOS电池失效。

解释:这说明CMOS电池已经快没电了,只要更换新的电池即可。

英文:CMOS check sum error-Defaults loaded中文:CMOS 执行全部检查时发现错误,要载入系统预设值。

解释:一般来说出现这句话都是说电池快没电了,可以先换个电池试试,如果问题还是没有解决,那么说明CMOS RAM可能有问题,如果没过一年就到经销商处换一块主板,过了一年就让经销商送回生产厂家修一下吧!英文:Press ESC to skip memory test中文:正在进行内存检查,可按ESC键跳过。

解释:这是因为在CMOS内没有设定跳过存储器的第二、三、四次测试,开机就会执行四次内存测试,当然你也可以按ESC 键结束内存检查,不过每次都要这样太麻烦了,你可以进入COMS设置后选择BIOS FEATURS SETUP,将其中的Quick Power On Self Test设为Enabled,储存后重新启动即可。

英文:Keyboard error or no keyboard present中文:键盘错误或者未接键盘。

解释:检查一下键盘的连线是否松动或者损坏。

英文:Hard disk install failure中文:硬盘安装失败。

解释:这是因为硬盘的电源线或数据线可能未接好或者硬盘跳线设置不当。

你可以检查一下硬盘的各根连线是否插好,看看同一根数据线上的两个硬盘的跳线的设置是否一样,如果一样,只要将两个硬盘的跳线设置的不一样即可(一个设为Master,另一个设为Slave)。

Atmel AT25128B 256B 131K 16K 电池电源 EEPROM 数据手册说明书

AT25128B and AT25256BSPI Serial EEPROM128K (16,384 x 8), 256K (32,768 x 8)DATASHEET Features●Serial Peripheral Interface (SPI) Compatible●Supports SPI Modes 0 (0,0) and 3 (1,1)Data Sheet Describes Mode 0 Operation●Low-voltage and Standard-voltage OperationV CC = 1.8V to 5.5V●20MHz Clock Rate (5V)●64-byte Page Mode and Byte Write Operation●Block Write ProtectionProtect 1/4, 1/2, or Entire Array●Write Protect (WP) Pin and Write Disable Instructions for Both Hardware andSoftware Data Protection●Self-timed Write Cycle (5ms max)●High ReliabilityEndurance: 1,000,000 Write CyclesData Retention: 100 Years●Green (Pb/Halogen-free/RoHS Compliant) Packaging Options●Die Sales: Wafer Form, Waffle Pack, and Bumped WafersDescriptionThe Atmel® AT25128B/256B provides 131,072/262,144 bits of Serial Electrically Erasable Programmable Read-Only Memory (EEPROM) organized as16,384/32,768 words of 8 bits each. The device is optimized for use in many industrial and commercial applications where low-power and low-voltage operation are essential. The AT25128B/256B is available in space saving JEDEC SOIC, TSSOP, UDFN, and VFBGA packages.The AT25128B/256B is enabled through the Chip Select pin (CS) and accessed via a 3-Wire interface consisting of Serial Data Input (SI), Serial Data Output (SO), and Serial Clock (SCK). All programming cycles are completely self-timed, and no separate erase cycle is required before write.Block Write protection is enabled by programming the status register with one of four blocks of Write Protection. Separate Program Enable and Program Disable instructions are provided for additional data protection. Hardware Data Protection is provided via the WP pin to protect against inadvertent write attempts. The HOLD pin may be used to suspend any serial communication without resetting the serial sequence.AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_01201521.Pin ConfigurationsTable 1-1.Pin Configurations 2.Absolute Maximum Ratings*Operating Temperature . . . . . . . . . . .-55︒C to +125︒C Storage Temperature. . . . . . . . . . . . .-65︒C to +150︒C Voltage on any pinwith respect to ground . . . . . . . . . . . . . -1.0V to +7.0V Maximum Operating Voltage . . . . . . . . . . . . . . . 6.25V DC Output Current. . . . . . . . . . . . . . . . . . . . . . .5.0mA*Notice:Stresses beyond those listed under “AbsoluteMaximum Ratings” may cause permanent damage to the device. This is a stress rating only and functional operation of the device at these or any other conditions beyond those indicated in the operational sections of this specification is not implied. Exposure to absolute maximum rating conditions forextended periods may affect device reliability.Note: Drawings are not to scale.8-lead SOICCS SO WP GNDV CC HOLD SCK SI12348765Top ViewTop View8-lead TSSOP12348765CS SO WP GNDV CC HOLD SCK SIV CC HOLD SCK SICS SO WP GND123487658-ball VFBGABottom View8-pad UDFNBottom ViewV CC HOLD SCK SI CS SO WP GND123487653AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_0120153.Block DiagramFigure 3-1.Block DiagramV CCAT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_01201544.Electrical Characteristics4.1Pin Capacitance (1)Table 4-1.Pin CapacitanceNote:1.This parameter is characterized and is not 100% tested.4.2DC CharacteristicsTable 4-2.DC CharacteristicsNote:1.V IL min and V IH max are reference only and are not tested.Applicable over recommended operating range from T A = 25°C, f = 1MHz, V CC = +5V (unless otherwise noted).Applicable over recommended operating range from: T AI = -40︒C to +85︒C, V CC = +1.8V to +5.5V, (unless otherwise noted).5AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_0120154.3AC CharacteristicsTable 4-3.AC CharacteristicsApplicable over recommended operating range from T AI = -40 to +85°C, V CC = As Specified, CL = 1 TTL Gate and 30pF (unless otherwise noted).AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_0120156Note:1.This parameter is characterized and is not 100% tested.5.Serial Interface DescriptionMaster: The device that generates the serial clock.Slave: Because the Serial Clock pin (SCK) is always an input, the AT25128B/256B always operates as a slave.Transmitter/Receiver: The AT25128B/256B has separate pins designated for data transmission (SO) and reception (SI).MSB: The Most Significant Bit (MSB) is the first bit transmitted and received.Serial Opcode: After the device is selected with CS going low, the first byte will be received. This byte contains the opcode which defines the operations to be performed.Invalid Opcode: If an invalid opcode is received, no data will be shifted into the AT25128B/256B, and the serial output pin (SO) will remain in a high-impedance state until the falling edge of CS is detected again. This will reinitialize the serial communication.Chip Select: The AT25128B/256B is selected when the CS pin is low. When the device is not selected, data will not be accepted via the SI pin, and the SO pin will remain in a high-impedance state.Hold: The HOLD pin is used in conjunction with the CS pin to select the AT25128B/256B. When the device is selected and a serial sequence is underway, HOLD can be used to pause the serial communication with the master device without resetting the serial sequence. To pause, the HOLD pin must be brought low while the SCK pin is low. To resume serial communication, the HOLD pin is brought high while the SCK pin is low (SCK may still toggle during HOLD). Inputs to the SI pin will be ignored while the SO pin is in the high-impedance state.Write Protect: The Write Protect pin (WP) will allow normal read/write operations when held high. When the WP pin is brought low and WPEN bit is one, all write operations to the status register are inhibited. WP going low while CS is still low will interrupt a write to the status register. If the internal write cycle has already been initiated, WP going low will have no effect on any write operation to the status register. The WP pin function is blocked when the WPEN bit in the status register is zero. This will allow the user to install the AT25128B/256B in a system with the WP pin tied to ground and still be able to write to the status register. All WP pin functions are enabled when the WPEN bit is set to one.Table 4-3.AC Characteristics (Continued)Applicable over recommended operating range from T AI = -40 to +85°C, V CC = As Specified, CL = 1 TTL Gate and 30pF (unless otherwise noted).7AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_012015Figure 5-1.SPI Serial InterfaceMaster :MicrocontrollerSlave :AT25128B/256BAT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_01201586.Functional DescriptionThe AT25128B/256B is designed to interface directly with the synchronous Serial Peripheral Interface (SPI) of the 6800 series of microcontrollers.The AT25128B/256B utilizes an 8-bit instruction register. The list of instructions and their operation codes are contained in Figure 6-1. All instructions, addresses, and data are transferred with the MSB first and start with a high-to-low CS transition.Table 6-1.Instruction Set for the AT25010B/020B/040BWrite Enable (WREN): The device will power-up in the Write Disable state when V CC is applied. Allprogramming instructions must therefore be preceded by a Write Enable instruction. The WP pin must be held high during a WREN instruction.Write Disable (WRDI): To protect the device against inadvertent writes, the Write Disable instruction disables all programming modes. The WRDI instruction is independent of the status of the WP pin.Read Status Register (RDSR): The Read Status Register instruction provides access to the status register. The Read/Busy and Write Enable status of the device can be determined by the RDSR instruction. Similarly, the Block Write Protection bits indicate the extent of protection employed. These bits are set by using the WRSR instruction.Table 6-2.Status Register FormatTable 6-3.Read Status Register Bit Definition9AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_012015Write Status Register (WRSR): The WRSR instruction allows the user to select one of four levels of protection. The AT25128B/256B is divided into four array segments. None, one-quarter (¼), one-half (½), or all of the memory segments can be protected. Any of the data within any selected segment will therefore be read-only. The block write protection levels and corresponding status register control bits are shown in Table 6-4.Bits BP1, BP0, and WPEN are nonvolatile cells that have the same properties and functions as the regular memory cells (e.g., WREN, t WC , RDSR).Table 6-4.Block Write Protect BitsThe WRSR instruction also allows the user to enable or disable the write protect (WP) pin through the use of the Write Protect Enable (WPEN) bit. Hardware write protection is enabled when the WP pin is low and the WPEN bit is one. The hardware write protection is disabled when either the WP pin is high or the WPEN bit is zero. When the device is hardware write protected, writes to the Status Register including the Block Protect bits, the WPEN bit, and the block protected sections in the memory array are disabled. Writes are only allowed to sections of the memory which are not block-protected.Note:When the WPEN bit is hardware write protected, it cannot be changed back to zero as long as the WP pin is held low.Table 6-5.WPEN Operation Read Sequence (READ): Reading the AT25128B/256B via the SO pin requires the following sequence. After the CS line is pulled low to select a device, the Read opcode is transmitted via the SI line followed by the byte address to be read (Table 6-6). Upon completion, any data on the SI line will be ignored. The data (D7 – D0) at the specified address is then shifted out onto the SO line. If only one byte is to be read, the CS line should be driven high after the data comes out. The Read Sequence can be continued since the byte address isautomatically incremented and data will continue to be shifted out. When the highest address is reached, the address counter will roll-over to the lowest address allowing the entire memory to be read in one continuous read cycle.AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_01201510Write Sequence (WRITE): In order to program the AT25128B/256B, the Write Protect pin (WP) must be held high and two separate instructions must be executed. First, the device must be write enabled via the WREN instruction. Then a Write (WRITE) instruction may be executed. Also, the address of the memory location(s) to be programmed must be outside the protected address field location selected by the Block Write Protection level. During an internal write cycle, all commands will be ignored except the RDSR instruction.A Write instruction requires the following sequence. After the CS line is pulled low to select the device, the Write opcode is transmitted via the SI line followed by the byte address and the data (D7 D0) to be programmed (see Table 6-6 for the address key). Programming will start after the CS pin is brought high. The low-to-hightransition of the CS pin must occur during the SCK low time immediately after clocking in the D0 (LSB) data bit.The Ready/Busy status of the device can be determined by initiating a Read Status Register (RDSR)instruction. If Bit 0 is one, the write cycle is still in progress. If Bit 0 is zero, the write cycle has ended. Only the RDSR instruction is enabled during the write programming cycle.The AT25128B/256B is capable of an 64-byte Page Write operation. After each byte of data is received, the six low-order address bits are internally incremented by one; the high-order bits of the address will remain constant. If more than 64 bytes of data are transmitted, the address counter will roll-over, and the previously written data will be overwritten. The AT25128B/256B is automatically returned to the Write Disable state at the completion of a write cycle.Note:If the WP pin is brought low or if the device is not Write Enabled (WREN), the device will ignore the Write instruction and will return to the standby state, when CS is brought high. A new CS falling edge is required to reinitiate the serial communication.Table 6-6.Address Key7.Timing Diagrams — SPI Mode 0 (0,0)Figure 7-1.Synchronous Data Timing (for Mode 0)Figure 7-2.WREN TimingFigure 7-3.WRDI TimingSOSISCKCSV V ILV V ILV V ILV V SOSISCK CSWREN OpcodeHI-ZSOSISCK CSWRDI OpcodeHI-ZAT25128B/256B [DATASHEET]12Figure 7-5.WRSR TimingFigure 7-6.READ TimingSOSISCKCSSOSISCKCSInstruction76543210Data InHigh-impedanceMSBSOSI SCKCSFigure 7-8.HOLD TimingSOSISCKCSInstructionByte AddressData InHigh-impedance7654321015 14 13 (3)210HOLDSOSCKCSt HDAT25128B/256B [DATASHEET]148.Ordering Code DetailAtmel DesignatorProduct FamilyDevice DensityDevice RevisionShipping Carrier OptionOperating Voltage128 = 128 kilobit 256 = 256 kilobit25 = Standard SPI Serial EPPROMB or Blank = Bulk (Tubes)T = Tape and Reel, Standard Quantity Option E = Tape and Reel, Expanded Quantity OptionL = 1.8V to 5.5VPackage Device Grade or Wafer/Die ThicknessH = Green, NiPdAu Lead Finish, Industrial Temperature Range (-40°C to +85°C)U = Green, Matte Sn Lead Finish, Industrial Temperature Range (-40°C to +85°C)11 = 11mil Wafer ThicknessPackage OptionSS = JEDEC SOIC X = TSSOP MA = UDFN C = VFBGAWWU = Wafer UnsawnWDT = Die in Tape and ReelA T 25128B -S S H L -B9.Part MarkingsNote: 1.Contact Atmel Sales for Wafer sales.AT25128B/256B [DATASHEET]1611.18S1 — 8-lead JEDEC SOICAT25128B/256B [DATASHEET]1811.28X — 8-lead TSSOP11.38MA2 — 8-pad UDFNAT25128B/256B [DATASHEET]2011.48U2-1 — 8-ball VFBGA21AT25128B/256B [DATASHEET]Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_01201512.Revision HistoryX X X X X XAtmel Corporation 1600 Technology Drive, San Jose, CA 95110 USA T: (+1)(408) 441.0311F: (+1)(408) 436.4200| © 2015 Atmel Corporation. / Rev.: Atmel-8698E-SEEPROM-AT25128B-256B-Datasheet_012015.Atmel ®, Atmel logo and combinations thereof, Enabling Unlimited Possibilities ®, and others are registered trademarks or trademarks of Atmel Corporation in U.S. and other countries. Other terms and product names may be trademarks of others.DISCLAIMER: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT. IN NO EVENT SHALL ATMEL BE LIABLE FOR ANY DIRECT, INDIRECT, CONSEQUENTIAL, PUNITIVE, SPECIAL OR INCIDENTAL DAMAGES (INCLUDING, WITHOUT LIMITATION, DAMAGES FOR LOSS AND PROFITS, BUSINESS INTERRUPTION, OR LOSS OF INFORMATION) ARISING OUT OF THE USE OR INABILITY TO USE THIS DOCUMENT, EVEN IF ATMEL HAS BEEN ADVISED OF THE POSSIBILITY OF SUCH DAMAGES. Atmel makes no representations or warranties with respect to the accuracy or completeness of the contents of this document and reserves the right to make changes to specifications and products descriptions at any time without notice. Atmel does not make any commitment to update the information contained herein. Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel products are not intended,authorized, or warranted for use as components in applications intended to support or sustain life.SAFETY-CRITICAL, MILITARY, AND AUTOMOTIVE APPLICATIONS DISCLAIMER: Atmel products are not designed for and will not be used in connection with any applications where the failure of such products would reasonably be expected to result in significant personal injury or death (“Safety-Critical Applications”) without an Atmel officer's specific written consent. Safety-Critical Applications include, without limitation, life support devices and systems, equipment or systems for the operation of nuclear facilities and weapons systems.Atmel products are not designed nor intended for use in military or aerospace applications or environments unless specifically designated by Atmel as military-grade. Atmel products are not designed nor intended for use in automotive applications unless specifically designated by Atmel as automotive-grade.。

电脑出现错误?看不懂英文?小编整理了电脑常见错误中英文翻译

电脑出现错误?看不懂英⽂?⼩编整理了电脑常见错误中英⽂翻译经常遇到电脑出现问题,但是⾃⼰⼜看不懂英⽂,⽆法和维修⼈员表达出电脑的问题。

⼩编今天帮你整理出电脑常见问题有中英对译,希望对你有帮助!建议收藏哦!⼀、BIOS中的提⽰信息提⽰信息说明Drive A error 驱动器A错误System halt 系统挂起Keyboard controller error 键盘控制器错误Keyboard error or no keyboard present 键盘错误或者键盘不存在BIOS ROM checksum error BIOSROM 校验错误Single hardisk cable fail 当硬盘使⽤Cable选项时硬盘安装位置不正确FDD Controller Failure BIOS 软盘控制器错误HDD Controller Failure BIOS 硬盘控制器错误Driver Error 驱动器错误Cache Memory Bad, Do not Enable Cache ⾼速缓存Cache损坏,不能使⽤Error: Unable to control A20 line 错误提⽰:不能使⽤A20地址控制线Memory write/Read failure 内存读写失败Memory allocation error 内存定位错误CMOS Battery state Low CMOS没电了Keyboard interface error 键盘接⼝错误Hard disk drive failure 加载硬盘失败Hard disk not present 硬盘不存在Floppy disk(s) fail (40) 软盘驱动器加载失败,⼀般是数据线插反,电源线没有插接,CMOS内部软驱设置错误CMOS checksum error-efaults loaded. CMOS校验错误,装⼊缺省(默认)设置打开应⽤保存⾼清⼤图⼆、BIOS刷新失败后,Bootblock启动时出现的提⽰信息提⽰信息说明Detecting floppy drive A media... 检测软驱A的格式Drive media is : 1.44Mb1.2Mb 720Kb 360K 驱动器格式是1.44Mb、12Mb、720kb、360kb的⼀种DISK BOOT FAILURE, INSERT SYSTEM DISK AND PRESS ENTER 磁盘引导失败,插⼊系统盘后按任意键继续三、MBR主引导区提⽰信息提⽰信息说明Invalid partition table ⽆效的分区表Error loading operating sy stem 不能装⼊引导系统Missing operating system 系统引导⽂件丢失说明:如果在计算机启动过程中,在硬件配置清单下⽅(也就时在平时正常启动时出现Starting Windows 98…的地⽅)出现不可识别字符,此时可判断硬盘分区表损坏。

SoCDesign

¥ ¤ ¤ ¡ £¢ ¡

Through TE7720 Directly to FPGA

¡ ¡

¥ ¤ ¤ ¡ £¢ ¡

¡

Suzaku MicorBlaze Memory MAP

Start Address 0x0000 0000 0x0000 1000 0x8000 0000 0x8100 0000 0xFF00 0000 0xFF80 0000 0xFFE0 0000 0xFFF0 0000 0xFFFF 1000 0xFFFF 1100 0xFFFF 2000 0xFFFF 2100 0xFFFF 3000 0xFFFF 3100 0xFFFF A000 End Address 0x0000 1FFF 0x7FFF FFFF 0x80FF FFFF 0xFEFF FFFF 0xFF7F FFFF 0xFFCF FFFF 0xFFEF FFFF 0xFFFF 0FFF 0xFFFF 10FF 0xFFFF 1FFF 0xFFFF 20FF 0xFFFF 2FFF 0xFFFF 30FF 0xFFFF 9FFF 0xFFFF A0FF Peripheral BRAM Reserved OPB-SDRAM Controller Free OPB-EMC Free OPB-EMC Free OPB-Timer Free OPB-UART Lite Free OPB-Interrupt Controller Free OPB-GPIO Boot Mode Jumper LED Software Reset RS232C LAN Controller FLASH Memory 4MByte SDRAM 16MByte Device

0xFFFF A100

0xFFFF FFFF

National Instruments PXIe系列产品数据手册说明书

Board Assembly Part Number(s)Part Number Description159040B-01L or later NI PXIe-7846R159040B-02L or later NI PXIe-7847R159040B-03L or later NI PXIe-7856R159040B-04L or later NI PXIe-7857R159040B-05L or later NI PXIe-7858RManufacturer: National InstrumentsVolatile MemoryUser Accessible/ BatteryType Size System Accessible1Backup? Purpose Method of Clearing2(7846R/7847R/7856R/7857R)FPGA Block RAM 11,700 KB Yes/Yes No Data storage during Cycle PowerVI Execution(7858R)FPGA Block RAM 16,020 KB Yes/Yes No Data storage during Cycle PowerVI Execution (7847R/7857R/7858R)DRAM 512MB Yes/Yes No Onboard Memory Storage Cycle PowerNon-Volatile MemoryUser Accessible/ BatteryType Size System Accessible Backup? Purpose Method of Clearing(7846R/7847R/7856R/7857R)Flash 64 Mb No- Device information No/Yes Product Identification None available to user- Calibration data3No/Yes Calibration Information None available to user- Calibration metadata Yes/Yes User-defined See Clearing Notes- FPGA bitstream Yes/Yes User LV FPGA VI Bitstream See Clearing Notes(7858R)Flash 128 Mb- Device information No/Yes No Product Identification None available to user- Calibration data3No/Yes Calibration Information None available to user- Calibration metadata Yes/Yes User-defined See Clearing Notes- FPGA bitstream Yes/Yes User LV FPGA VI Bitstream See Clearing Notes1 Items are designated No for the following reason(s):a) Hardware changes or a unique software tool from National Instruments are required to modify contents of the memorylisted.b) Hardware-modifying software tools are not distributed to customers for any personal access or customization, also knownas non-normal use.2 The designation None Available to User indicates that the ability to clear this memory is not available to the user undernormal operation. The utilities required to clear the memory are not distributed by National Instruments to customers fornormal use.3 Calibration constants that are stored in device calibration memory include information for the device’s full operating range. Calibration constants do not maintain any unique data for specific configurations at which the device is used unlessotherwise specified.Media StorageUser Accessible/ BatteryType Size System Accessible Backup? Purpose Method of Clearing NONEClearing Notes:Calibration metadata: There are two items in the calibration metadata that need to be cleared:1.To clear the user-defined information, you can use the Calibration Utility to write a known value to the user stringfield.2.To clear the calibration password, you can use the Calibration Utility to change the password to a known value.FPGA bitstream: You can use the NI-RIO Device Setup utility to erase the FPGA bitstream data. For more details, visit /info and enter the infocode fpgaflashclr.Terms and DefinitionsUser Accessible Allows the user to directly write or modify the contents of the memory during normal instrument operation. System Accessible Does not allow the user to access or modify the memory during normal instrument operation. However, system accessible memory may be accessed or modified by background processes. This can be something that is not deliberate by the user and can be a background driver implementation, such as storing application information in RAM to increase speed of use.Cycle Power The process of completely removing power from the device and its components. This process includes a complete shutdown of the PC and/or chassis containing the device; a reboot is not sufficient for the completion of this process. Volatile Memory Requires power to maintain the stored information. When power is removed from this memory, its contents are lost.Non-Volatile Retains its contents when power is removed. This type of memory typically contains calibration or chip configuration information, such as power up states.。

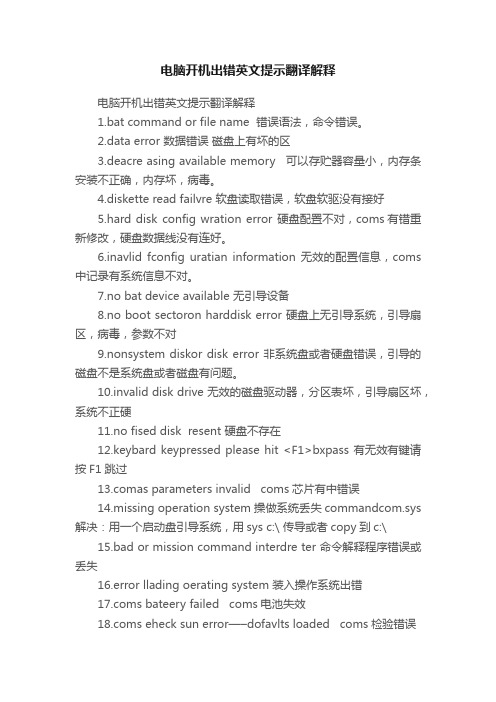

电脑开机出错英文提示翻译解释

电脑开机出错英文提示翻译解释电脑开机出错英文提示翻译解释1.bat command or file name 错误语法,命令错误。

2.data error 数据错误磁盘上有坏的区3.deacre asing available memory 可以存贮器容量小,内存条安装不正确,内存坏,病毒。

4.diskette read failvre 软盘读取错误,软盘软驱没有接好5.hard disk config wration error 硬盘配置不对,coms有错重新修改,硬盘数据线没有连好。

6.inavlid fconfig uratian information 无效的配置信息,coms 中记录有系统信息不对。

7.no bat device available 无引导设备8.no boot sectoron harddisk error 硬盘上无引导系统,引导扇区,病毒,参数不对9.nonsystem diskor disk error 非系统盘或者硬盘错误,引导的磁盘不是系统盘或者磁盘有问题。

10.invalid disk drive 无效的磁盘驱动器,分区表坏,引导扇区坏,系统不正硬11.no fised disk resent 硬盘不存在12.keybard keypressed please hit <F1>bxpass 有无效有键请按F1跳过as parameters invalid coms芯片有中错误14.missing operation system 操做系统丢失commandcom.sys 解决:用一个启动盘引导系统,用sys c:\ 传导或者copy到c:\15.bad or mission command interdre ter 命令解释程序错误或丢失16.error llading oerating system 装入操作系统出错s bateery failed coms电池失效s eheck sun error—–dofavlts loaded coms检验错误19.press esc to skiiip rnemory test 按ESC健跳过内存自检20.hard disk lnstall railure 硬盘安装失败不正确,coms不正确21.seeondary slave hard fail 检查从盘失败,把IDE接口设为自动22.floppy disk fail或floppy disk (s)fail80或floppy disk(s)fail40 无法驱动软驱,重新在COMS中把它弄没有了,F1跳过23.memory test fail 内存检测失败可能有病毒24.override enadle——dofavles loaded 当前coms设置无法启动系统(生设)25.presi F1 to comtinve del to enter setap 检查出错跳过,DEL 键重新设置COMS26.disk boot rallure insere system disk and dress ente 磁盘启动错误,插入系统盘确认,修改COMS参数把IDE接口关闭硬盘中的一些错误信息:1.hdd controller failure 硬盘驱动器控制失败硬盘坏了2.hdc controller fail 硬盘控制器控制失败可能是控制器损坏或电缆没有接好,另外硬盘参数不正确也会出现错误3.no rom baslc system halt 没有固化BASLC系统,系统停机,这个错误出现在486及以前的一些早期的电脑中出现问题4.Non-system disk or disk error replace and press any key when ready 非系统盘或磁盘错误,重新换盘后按任意键,可能是BPB表坏了,即用软盘启动后硬盘不能正确的读写,可以用NDD修复,如果BPB表完好,只需要SYS C:传送系统就可引导了5.lnvalid partition table 无效的分区表,如果一个硬盘出现用第三方分区软件作了几个激活分区的话就很容易出现6.DRLVE NOT READY ERROR lnsert Boot Diskette in a: Press any key when ready 设备未准备好,插入引导盘到A驱,准备好后按任意健,第一硬盘读电路故障,使读操作失败,属于硬件故障;第二0面0道磁道格式和扇驱ID逻辑或物理损坏,找不到指定的扇区;第三读盘没有出错,但读出的MBR尾标不为55AA,系统认为MBR不正确,这是软故障7.c:drive failure RUN SETUP UTILITY Press to Resume 硬盘C 驱动失败,运行设置功能,按键重新开始,硬盘参数不对,格式化时所用的对数不对。

Running an Application from Internal Flash Memory on the TMS320F28xxx DSP(spra958h)

Application ReportSPRA958H – September 2008 Running an Application from Internal Flash Memory on theTMS320F28xxx DSP David M. Alter DSP Applications - Semiconductor GroupABSTRACTSeveral special requirements exist for running an application from on-chip flash memoryon the TMS320F28xxx DSP. These requirements generally do not manifest themselvesduring development in RAM since the Code Composer Studio™ debugger can maskproblems associated with initialized sections and how they are linked to memory. Thisapplication report covers the requirements needed to properly configure applicationsoftware for execution from on-chip flash memory. Requirements for both DSP/BIOS™and non-DSP/BIOS projects are presented. Some performance considerations andtechniques are also discussed. Example code projects are included that run from on-chipflash on the eZdspF2812™, eZdspF2808, and eZdspF28335 development boards. Codeexamples that run from internal RAM are also provided for completeness. These codeexamples provide a starting point for code development, if desired.Project collateral and source code discussed in this application report can be downloadedfrom the following URL: /sc/techlit/spra958.zip.Note that the issues discussed in this application report apply directly to current membersof the TMS320F28xxx DSP family, specifically: F2810, F2811, F2812, F2801, F2801-60,F2802, F2802-60, F2806, F2808, F2809, F28015, F28016, F28044, F28232, F28234,F28235, F28332, F28334, and F28335 devices. Applicability to future devices in theTMS320F28xxx family, although quite likely, is not guaranteed. In addition, the code andtechniques presented in this application report for DSP/BIOS projects were developed onCode Composer Studio v3.3.81.5 using C-compiler v5.1.0 and DSP/BIOS v5.33. It isalways suggested that the reader upgrade to the latest version. However, keep in mindthat future versions of DSP/BIOS may have differences that make some of the itemsdiscussed in this report unnecessary (although in all likelihood backwards compatibility willbe maintained, so that the techniques discussed here should still work).Finally, this application report does not provide a tutorial on writing and building code forthe F28xxx DSP. It is assumed that the reader already has at least the main framework oftheir application code running from RAM, probably using the Code Composer Studiodebugger to perform the code download. This report only identifies the special items thatmust be considered when moving the application into on-chip flash memory.Code Composer Studio and DSP/BIOS are trademarks of Texas Instruments.eZdsp is a trademark of Spectrum Digital Incorporated.Trademarks are the property of their respective owners.1SPRA958HContents1Introduction (3)2Creating a User Linker Command File (3)2.1Non-DSP/BIOS Projects (3)2.2DSP/BIOS Projects (4)3Where to Link the Sections (4)3.1Non-DSP/BIOS Projects (5)3.2DSP/BIOS Projects (7)4Copying Sections from Flash to RAM (9)4.1Copying the Interrupt Vectors (non-DSP/BIOS projects only) (9)4.2Copying the .hwi_vec Section (DSP/BIOS projects only) (10)4.3Copying the .trcdata Section (DSP/BIOS projects only) (10)4.4Initializing the Flash Control Registers (DSP/BIOS and non-DSP/BIOS projects) (12)4.5Maximizing Performance by Executing Time-critical Functions from RAM (14)4.6Maximizing Performance by Linking Critical Global Constants to RAM (15)4.6.1Method 1: Running All Constant Arrays from RAM (15)4.6.2Method 2: Running a Specific Constant Array from RAM (18)5Programming the Code Security Module Passwords (19)6Executing Your Code from Flash after a DSP Reset (23)7Disabling the Watchdog Timer During C-Environment Boot (25)8C-Code Examples (27)8.1General Overview (27)8.2Directory Structure and File Utilizations (28)8.3Additional Information (35)References (38)Revision History (39)FiguresFigure 1.Specifying the User Init Function in the DSP/BIOS Configuration tool (11)Figure 2.Specifying the Link Order In Code Composer Studio (17)Figure 3.DSP/BIOS MEM Properties for CSM Password Locations (22)Figure 4.DSP/BIOS MEM Properties for CSM Reserved Locations (22)Figure 5.DSP/BIOS MEM Properties for Jump to Flash Entry Point (24)TablesTable 1.Section Linking in Non-DSP/BIOS Projects (Large memory model) (6)Table 2.Section Linking In DSP/BIOS Projects (Large Memory Model) (7)Table 3.Example Code File Directories (28)Table 4.F2812 Example Code File Inventory and Utilization (29)Table 5.F2808 Example Code File Inventory and Utilization (31)Table 6.F28335 Example Code File Inventory and Utilization (33)2Running an Application from Internal Flash Memory on the TMS320F28xxx DSPSPRA958H1 IntroductionThe TMS320F28xxx DSP family has been designed for standalone operation in embeddedcontroller applications. The on-chip flash usually eliminates the need for external non-volatilememory and a host processor from which to bootload. Configuring an application to run fromflash memory is a relatively easy matter provided that one follow a few simple steps. This report covers the major concerns and steps needed to properly configure application software forexecution from internal flash memory. Requirements for both DSP/BIOS and non-DSP/BIOSprojects are presented. Some performance considerations and techniques are also discussed.Note that the issues discussed in this application report apply directly to current membersof the TMS320F28xxx DSP family. The term F28xxx here, and throughout the remainderof this document, refers specifically to the F2810, F2811, F2812, F2801, F2801-60,F2802, F2802-60, F2806, F2808, F2809, F28015, F28016, F28044, F28232, F28234,F28235, F28332, F28334, and F28335 devices. Applicability to future devices in theTMS320F28xxx family, although quite likely, is not guaranteed. In addition, the code andtechniques presented in this application report for DSP/BIOS projects were developed onCode Composer Studio v3.3.81.5 using C-compiler v5.1.0 and DSP/BIOS v5.33. It isalways suggested that the reader upgrade to the latest version. However, keep in mindthat future versions of DSP/BIOS may have differences that make some of the itemsdiscussed in this report unnecessary (although in all likelihood backwards compatibility willbe maintained, so that the techniques discussed here should still work).Finally, this application report does not provide a tutorial on writing and building code for theF28xx DSP. It is assumed that the reader already has at least the main framework of theirapplication code running from RAM, probably using the CCS debugger to perform the codedownload. This report only identifies the special items that must be considered when moving the application into on-chip flash memory.2 Creating a User Linker Command File2.1 Non-DSP/BIOS ProjectsIn non-DSP/BIOS applications, the user linker command file will be where most memory isdefined, and where the linking of most sections is specified. The format of this file is no different than the linker command file you are currently using to run your application from RAM. Thedifference will be in where you link the sections (to be discussed in Section 3). More information on linker command files can be found in reference [9]. The non-DSP/BIOS code projects thataccompany this application report contain linker command files that can be used for reference.The DSP281x, DSP280x, DSP2804x, and DSP2833x peripheral header files contain linkercommand files named DSP281x_Headers_nonBIOS.cmd, DSP280x_Headers_nonBIOS.cmd, DSP2804x_Headers_nonBIOS.cmd, and DSP2833x_Headers_nonBIOS.cmd respectively (see references [15-18]). These files contains linker MEMORY and SECTIONS declarations forlinking the peripheral register structures. Simply add the appropriate one of these linkercommand files to your code project in addition to your user linker command file.Running an Application from Internal Flash Memory on the TMS320F28xxx DSP 3SPRA958HIn general, the order of the linker command files is unimportant since during a project build, CCS evaluates the MEMORY section of every linker command file before evaluating the SECTIONS section of any linker command file. This ensures that all memories are defined before linkingany sections to those memories. However, advanced users may need manual control over the order of linker command file evaluation in some rare situations. This can be specified withinCCS on the Project → Build_Options, Link_Order tab.2.2 DSP/BIOS ProjectsThe DSP/BIOS configuration tool generates a linker command file that specifies how to link all DSP/BIOS generated sections, and by default all C-compiler generated sections. When running your application from RAM, this linker command file may be the only one in use. However, when executing from flash memory, there will likely be a need to generate and link one or more user defined sections. In particular, any code that configures the on-chip flash control registers (e.g.flash wait-states) cannot execute from flash. In addition, one may want to run certain timecritical functions from RAM (instead of flash) to maximize performance. A user linker command file must be created to handle these user defined sections.CCS supports having more than one linker command file in a project. Hence, all one needs to do is add both the user linker command file, as well as the DSP/BIOS generated linkercommand file, to their project. In general, the order of the linker command files is unimportant since during a project build, CCS evaluates the MEMORY section of every linker command file before evaluating the SECTIONS section of any linker command file. This ensures that allmemories are defined before linking any sections to those memories. However, advanced users may need manual control over the order of linker command file evaluation in some raresituations (for example, to preempt and override DSP/BIOS linkage of a section). This can be specified within CCS on the Project → Build_Options, Link_Order tab.The DSP281x, DSP280x, DSP2804x, and DSP2833x peripheral header files contain linkercommand files named DSP281x_Headers_nonBIOS.cmd, DSP280x_Headers_nonBIOS.cmd, DSP2804x_Headers_nonBIOS.cmd, and DSP2833x_Headers_nonBIOS.cmd respectively (see references [15-18]). These file contains linker MEMORY and SECTIONS declarations for linking the peripheral register structures. Simply add the appropriate one of these linker command files to your code project as well.3 Where to Link the SectionsTwo basic section types exist: initialized, and uninitialized. Initialized sections must contain valid values at device power-up. For example, code and constants are found in initialized sections.When designing a stand-alone embedded system with the F28xxx DSP (e.g., no emulator ordebugger in use, no host processor present to perform bootloading), all initialized sections must be linked to non-volatile memory (e.g., on-chip flash). An uninitialized section does not contain valid values at device power-up. For example, variables are found in uninitialized sections.Code will write values to the variable locations during code execution. Therefore, uninitialized sections must be linked to volatile memory (e.g., RAM).4Running an Application from Internal Flash Memory on the TMS320F28xxx DSPSPRA958H It is suggested that the -w linker option be invoked. The -w option will produce a warning if the linker encounters any sections in your project that have not been explicitly specified for linking ina linker command file. When the linker encounters an unspecified section, it uses a defaultallocation algorithm to link the section into memory (it will link the section to the first definedmemory with enough available free space). This is almost always risky, and can lead tounreliable and unpredictable code behavior. The -w option will identify any unspecified sections(e.g., those accidentally forgotten by the user) so that the user can make the necessary additionto the appropriate linker command file. The -w option can be selected in CCS on the Project →Build_Options menu, Linker tab, select the Advanced category, and then check the -w optionbox. It is checked by default for new projects.CAUTION:It is important that the large memory model be used with the C-compiler (asopposed to the small memory model). Small memory model requires certaininitialized sections to be linked to non-volatile memory in the lower 64Kw ofaddressable space. However, no flash memory is present in this region on anyF28xxx devices, and this will likely be true for future F28xxx devices as well.Therefore, large memory model should be used. In Code Composer Studio, thelarge memory model is on the Project → Build_Options menu. Select theCompiler tab, choose the Advanced category, and check the -ml option box. Fornon-DSP/BIOS projects, one should include the large memory model C-compilerruntime support library into their code project. For the fixed-point devices, thisis library rts2800_ml.lib (as opposed to rts2800.lib, which is for the smallmemory model). For the floating-point devices, this is file rts2800_fpu32.lib forplain C code, or rts2800_fpu32_eh.lib for C++ code (there are no small memorymodel libraries for the floating-point devices). For DSP/BIOS projects,DSP/BIOS will take care of including the required library. The user should notinclude any runtime support library in a DSP/BIOS project.3.1 Non-DSP/BIOS ProjectsThe compiler uses a number of specific sections. These sections are the same whether you are running from RAM or flash. However, when running a program from flash, all initialized sections must be linked to non-volatile memory, whereas all uninitialized sections must be linked tovolatile memory. Table 1 shows where to link each compiler generated section on the F28xxx DSP. Information on the function of each section can be found in reference [5]. Any usercreated initialized section should be linked to flash (e.g., those sections created using theCODE_SECTION compiler pragma), whereas any user created uninitialized sections should be linked to RAM (e.g., those sections created using the DATA_SECTION compiler pragma).Running an Application from Internal Flash Memory on the TMS320F28xxx DSP 5SPRA958H6 Running an Application from Internal Flash Memory on the TMS320F28xxx DSPTable 1. Section Linking in Non-DSP/BIOS Projects (Large memory model) Section Name Where to Link.cinit Flash.cio RAM.const Flash.econst Flash.pinit Flash.switch Flash.text Flash .bss RAM.ebss RAM .stack Lower 64Kw RAM.sysmem RAM.esysmem RAM.reset RAM 1Table 1 Notes:1The .reset section contains nothing more than a 32-bit interrupt vector that points to theC-compiler boot function in the runtime support library (the _c_int00 routine). It generally is not used. Instead, the user typically creates their own branch instruction to point to the starting point of the code (see Sections 6 and 7). When not in use, the .reset section should be omitted from the code build by using a DSECT modifier in the linker command file. For example:/********************************************************************* User's linker command file********************************************************************/SECTIONS{.reset : > FLASH, PAGE = 0, TYPE = DSECT}SPRA958HRunning an Application from Internal Flash Memory on the TMS320F28xxx DSP 73.2 DSP/BIOS ProjectsThe memory section manager in the DSP/BIOS configuration tool allows one to specify where to link the various DSP/BIOS and C-compiler generated sections. Table 2 indicates where the sections shown on each tab of the memory section manager should be linked (i.e., RAM or FLASH). Note that this information has been tabulated specifically for DSP/BIOS v5.33. Later versions of DSP/BIOS, although quite likely to be the same, may have some differences. The reader should check the version they are using and simply be aware of potential differences while proceeding. To check your DSP/BIOS version from within CCS, go to the Help → About menu, click the Component_Manager button, and view the TMS320C28XX DSP/BIOS version under the Target_Content_(DSP/BIOS) tree.Table 2. Section Linking In DSP/BIOS Projects (Large Memory Model) Memory Section Manager TAB Section NameWhere to Link Segment for DSP/BIOS ObjectsRAM General Segment for malloc()/free()RAM Argument Buffer Section (.args)RAM Stack Section (.stack)Lower 64Kw RAM DSP/BIOS Init Tables (.gblinit)Flash TRC Initial Values (.trcdata)RAM 1 DSP/BIOS Kernel State (.sysdata)RAM BIOS Data DSP/BIOS Conf Sections (*.obj)RAM BIOS Code Section (.bios)Flash Startup Code Section (.sysinit)Flash Function Stub Memory (.hwi)Flash Interrupt Service Table Memory (.hwi_vec)PIEVECT RAM 2 BIOS Code RTDX Text Segment (.rtdx_text)Flash Text Section (.text)Flash Switch Jump Tables (.switch) Flash C Variables Section (.bss) RAM C Variables Section (.ebss) RAM Data Initialization Section (.cinit)FlashCompiler Sections C Function Initialization Table (.pinit) FlashSPRA958H8 Running an Application from Internal Flash Memory on the TMS320F28xxx DSP Constant Section (.econst)Flash Constant Section (.const)Flash Data Section (.data)Flash Data Section (.cio)RAM Load Address - BIOS Code Section (.bios)Flash 3 Load Address - Startup Code Section (.sysinit)Flash 3 Load Address - DSP/BIOS Init Tables (.gblinit)Flash 3 Load Address - TRC Initial Value (.trcdata)Flash 1 Load Address - Text Section (.text)Flash 3 Load Address - Switch Jump Tables (.switch)Flash 3 Load Address - Data Initialization Section (.cinit)Flash 3 Load Address - C Function Initialization Table (.pinit)Flash 3 Load Address - Constant Section (.econst)Flash 3 Load Address - Constant Section (.const)Flash 3 Load Address - Data Section (.data)Flash 3 Load Address - Function Stub Memory (.hwi)Flash 3 Load Address - Interrupt Service Table Memory (.hwi_vec)Flash 2 Load Address Load Address - RTDX Text Segment (.rtdx_text) Flash 3Table 2 Notes:1 The .trcdata section must be copied by the user from its load address (specified on theLoad_Address tab) to its run address (specified on the BIOS_Data tab) at runtime. See Section4.3 for details on performing this copy.2 The PIEVECT RAM is a specific block of RAM associated with the Peripheral InterruptExpansion (PIE) peripheral. On current F28xxx devices, the PIE RAM is a 256x16 block starting at address 0x000D00 in data space. For other devices, confirm the address in the device datasheet. The memory section manager in the DSP/BIOS configuration tool should already have a pre-defined memory named PIEVECT. The .hwi_vec section must be copied by the user from its load address (specified on the memory section manager Load_Address Tab) to its run address (specified on the memory section manager BIOS_Code Tab) at runtime. See Section4.2 for details on performing this copy.3The specific flash memory selected as the load address for this section should be the same flash memory selected previously as the run address for the section (e.g., on the BIOS_Data, BIOS_Code, or Compiler_Sections tab).SPRA958H 4 Copying Sections from Flash to RAM4.1 Copying the Interrupt Vectors (non-DSP/BIOS projects only)The Peripheral Interrupt Expansion (PIE) module manages interrupt requests on F28xxxdevices. At power-up, all interrupt vectors must be located in non-volatile memory (i.e., flash), but copied to the PIEVECT RAM as part of the device initialization procedure in your code. The PIEVECT RAM is a specific block of RAM, which on current F28xxx devices is a 256x16 block starting at address 0x000D00 in data space.Several approaches exist for linking the interrupt vectors to flash and then copying them to the PIEVECT RAM at runtime. One approach is to create a constant C-structure of function pointers that contains all 128 32-bit vectors. If using the DSP28xx peripheral structures (see references [15-18]), such a structure, called PieVectTableInit, has already been created in thecorresponding file DSP28xxx_PieVect.c. Since this structure is declared using the const typequalifier, it will be placed in the .econst section by the compiler. One simply needs to copy this structure to the PIEVECT RAM at runtime. The C-compiler runtime support library contains amemory copy function called memcpy() that can be used to perform the copy task. Thisfunction is used as follows:/********************************************************************* User's C-source file********************************************************************//********************************************************************* NOTE: This function assumes use of the DSP28xxx Peripheral Header* File structures (see References [15-18]).********************************************************************/#include <string.h>void main(void){/*** Initialize the PIE_RAM ***/PieCtrlRegs.PIECTRL.bit.ENPIE = 0; // Disable the PIEasm(" EALLOW"); // Enable EALLOW protected register access memcpy((void *)0x000D00, &PieVectTableInit, 256);asm(" EDIS"); // Disable EALLOW protected register access }The above example uses a hard coded address for the start of the PIE RAM, specifically0x000D00. If this is objectionable (as hard coded addresses are not good programmingpractice), one can use a DATA_SECTION pragma to create an uninitialized dummy variable,and link this variable to the PIE RAM. The name of the dummy variable can then be used inplace of the hard coded address. For example, when using any of the DSP28xxx deviceperipheral structures, an uninitialized structure called PieVectTable is created and linked overthe PIEVECT RAM. The memcpy() instruction in the previous example can be replaced by:memcpy(&PieVectTable, &PieVectTableInit, 256);Note that the length is 256. The memcpy function copies 16-bit words (as opposed to copying 128 32-bit words).Running an Application from Internal Flash Memory on the TMS320F28xxx DSP 9SPRA958H4.2 Copying the .hwi_vec Section (DSP/BIOS projects only)The DSP/BIOS .hwi_vec section contains the interrupt vectors, and must be loaded to flash but run from RAM. The user is responsible for copying this section from its load address to its run address. This is typically done in main(). The DSP/BIOS configuration tool generates globalsymbols that can be accessed by code in order to determine the load address, run address, and length of the .hwi_vec section. These symbol names are:hwi_vec_loadstarthwi_vec_loadendhwi_vec_runstartEach symbol is self-explanatory from its name. Note that the symbols are not pointers, butrather symbolically reference the 16-bit data value found at the corresponding location (i.e., start or end) of the section. The C-compiler runtime support library contains a memory copy function called memcpy() that can be used to perform the copy task. A C-code example of how to use this function to perform the section copy follows. Note that the PIEVECT RAM is EALLOWprotected. Therefore, inline EALLOW and EDIS assembly instructions must bracket the memory copy of the .hwi_vec section, as shown./********************************************************************* User's C-source file********************************************************************/#include <string.h>extern unsigned int hwi_vec_loadstart;extern unsigned int hwi_vec_loadend;extern unsigned int hwi_vec_runstart;void main(void){/*** Initialize the .hwi_vec section ***/asm(" EALLOW"); /* Enable EALLOW protected register access */ memcpy(&hwi_vec_runstart,&hwi_vec_loadstart,&hwi_vec_loadend - &hwi_vec_loadstart);asm(" EDIS"); /* Disable EALLOW protected register access */ }4.3 Copying the .trcdata Section (DSP/BIOS projects only)The DSP/BIOS .trcdata sections must be loaded to flash, but run from RAM. The user isresponsible for copying this section from its load address to its run address. However, unlike the .hwi_vec section, the copying of .trcdata must be performed prior to main(). This is becauseDSP/BIOS modifies the contents of .trcdata during DSP/BIOS initialization (which also occurs prior to main()).10Running an Application from Internal Flash Memory on the TMS320F28xxx DSPThe DSP/BIOS configuration tool provides for a user initialization function which can be utilized to perform the .trcdata section copy prior to both main() and DSP/BIOS initialization. This can be found in the project configuration file under System - Global Settings Properties, as shown in Figure 1.Figure 1. Specifying the User Init Function in the DSP/BIOS Configuration toolWhat remains is to create the user initialization function. The DSP/BIOS configuration toolgenerates global symbols that can be accessed by code in order to determine the load address, run address, and length of each section. These symbol names are:trcdata_loadstarttrcdata_loadend trcdata_runstartEach symbol is self-explanatory from its name. Note that the symbols are not pointers, butrather symbolically reference the 16-bit data value found at the corresponding location (i.e., start or end) of the section. The C-compiler runtime support library contains a memory copy function called memcpy() that can be used to perform the copy task. A C-code example of a user init function that performs the .trcdatasection copy follows. Check this box Enter yourfunction namehere (note theleading underscore)/********************************************************************* User's C-source file********************************************************************/#include <string.h>extern unsigned int trcdata_loadstart;extern unsigned int trcdata_loadend;extern unsigned int trcdata_runstart;void UserInit(void){/*** Initialize the .trcdata section before main() ***/memcpy(&trcdata_runstart,&trcdata_loadstart,&trcdata_loadend - &trcdata_loadstart);}4.4 Initializing the Flash Control Registers (DSP/BIOS and non-DSP/BIOS projects)The initialization code for the flash control registers, FOPT, FPWR, FSTDBYWAIT,FACTIVEWAIT, FBANKWAIT, and FOTPWAIT, cannot be executed from the flash memory or unpredictable results may occur. Therefore, the initialization function for the flash controlregisters must be copied from flash (its load address) to RAM (its run address) at runtime.CAUTION:The flash control registers are protected by the Code Security Module (CSM). Ifthe CSM is secured, you must run the flash register initialization code from CSMsecured RAM (e.g. L0 through L3 SARAM, see the device data sheet for yourspecific device) or the initialization code will be unable to access the flashregisters. Note that the CSM is always secured at device reset, although theROM bootloader will unlock it if you are using dummy passwords of 0xFFFF.The CODE_SECTION pragma of the C compiler can be used to create a separately linkable section for the flash initialization function. For example, suppose the flash register configuration is to be performed in the C function InitFlash(), and it is desired to place this function into alinkable section called secureRamFuncs. The following C-code example shows proper use of the CODE_SECTION pragma along with an example configuration of the flash registers:。

微星主板P67A-C43说明书

Revision History

Revision V1.1 Revision History Update cover page for PCB 1.X Date December 2010

Technical Support

If a problem arises with your system and no solution can be obtained from the user’s manual, please contact your place of purchase or local distributor. Alternatively, please try the following help resources for further guidance.

Micro-Star International MS-7673 This device complies with Part 15 of the FCC Rules. Operation is subject to the following two conditions: 1) this device may not cause harmful interference, and 2) this device must accept any interference received, including interference that may cause undesired operation.

ii

MS-7673

Safety Instructions

■ ■ ■ ■ ■

Always read the safety instructions carefully. Keep this User’s Manual for future reference. Keep this equipment away from humidity. Lay this equipment on a reliable flat surface before setting it up. The openings on the enclosure are for air convection hence protects the equipment from overheating. DO NOT COVER THE OPENINGS. equipment to the power inlet.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。