计算机组成原理实验三-存储器读写和总线控制实验

计算机组成原理实验

计算机组成原理实验一、实验目的本实验旨在通过实际操作,加深对计算机组成原理的理解,掌握计算机硬件的基本原理和工作方式。

二、实验设备和材料1. 计算机主机:型号为XXX,配置了XXX处理器、XXX内存、XXX硬盘等。

2. 显示器:型号为XXX,分辨率为XXX。

3. 键盘和鼠标:标准配置。

4. 实验板:包括CPU、内存、存储器、输入输出接口等模块。

5. 逻辑分析仪:用于分析和调试电路信号。

6. 示波器:用于观测电路信号的波形。

三、实验内容1. 实验一:CPU的工作原理a. 将实验板上的CPU模块插入计算机主机的CPU插槽中。

b. 连接逻辑分析仪和示波器,用于观测和分析CPU的工作信号和波形。

c. 打开计算机主机,启动操作系统。

d. 运行一段简单的程序,观察CPU的工作状态和指令执行过程。

e. 通过逻辑分析仪和示波器的数据分析,了解CPU的时钟信号、数据总线、地址总线等工作原理。

2. 实验二:内存的存储和读写a. 将实验板上的内存模块插入计算机主机的内存插槽中。

b. 打开计算机主机,启动操作系统。

c. 编写一个简单的程序,将数据存储到内存中。

d. 通过逻辑分析仪和示波器的数据分析,观察内存的写入和读取过程,了解内存的存储原理和读写速度。

3. 实验三:存储器的工作原理a. 将实验板上的存储器模块插入计算机主机的存储器插槽中。

b. 打开计算机主机,启动操作系统。

c. 编写一个简单的程序,读取存储器中的数据。

d. 通过逻辑分析仪和示波器的数据分析,观察存储器的读取过程,了解存储器的工作原理和数据传输速度。

4. 实验四:输入输出接口的工作原理a. 将实验板上的输入输出接口模块插入计算机主机的扩展插槽中。

b. 打开计算机主机,启动操作系统。

c. 编写一个简单的程序,通过输入输出接口实现数据的输入和输出。

d. 通过逻辑分析仪和示波器的数据分析,观察输入输出接口的工作过程,了解数据的传输和控制原理。

四、实验结果分析1. 实验一:通过观察CPU的工作状态和指令执行过程,可以验证CPU的时钟信号、数据总线、地址总线等工作原理是否正确。

《计算机组成原理》存储器读写实验报告

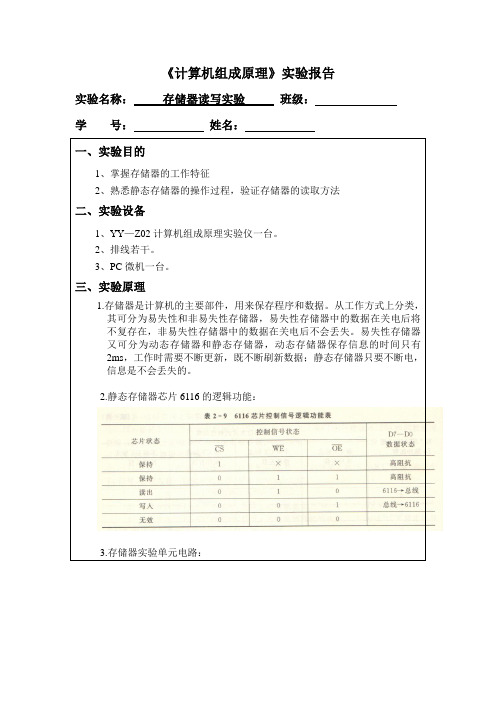

《计算机组成原理》实验报告实验名称:存储器读写实验班级:学号:姓名:一、实验目的1、掌握存储器的工作特征2、熟悉静态存储器的操作过程,验证存储器的读取方法二、实验设备1、YY—Z02计算机组成原理实验仪一台。

2、排线若干。

3、PC微机一台。

三、实验原理1.存储器是计算机的主要部件,用来保存程序和数据。

从工作方式上分类,其可分为易失性和非易失性存储器,易失性存储器中的数据在关电后将不复存在,非易失性存储器中的数据在关电后不会丢失。

易失性存储器又可分为动态存储器和静态存储器,动态存储器保存信息的时间只有2ms,工作时需要不断更新,既不断刷新数据;静态存储器只要不断电,信息是不会丢失的。

2.静态存储器芯片6116的逻辑功能:3.存储器实验单元电路:存储器实验单元电路控制信号逻辑功能表:4.存储器实验电路:存储器读写实验需三部分电路共同完成:存储器单元、地址寄存器单元和输入、输出单元。

存储器单元以6116芯片为中心构成,地址寄存器单元主要由一片74LS273组成,控制信号B-AR的作用是把总线上的数据送人地址寄存器,向存储器单元电路提供地址信息,输入、输出单元作用与以前相同。

四、实验结果记录(1)连线准备1.连接输入、输出实验的全部连线。

2.按实验逻辑原理图连接M-W、M-R两根信号低电平有效信号线。

3.连接A7—A0 8根地址线。

4.连接B-AR正脉冲有效信号线。

(2)记录结果(包含采集结果前的动作)地址写入数据读出数据结果说明01H 00100000 00100000 数据的写入与读取02H 00010011 00010011 数据的写入与读取03H 00100110 00100110 数据的写入与读取04H 10000001 10000001 数据的写入与读取05H 00000101 00000101 数据的写入与读取25H 不写存储器11110011 一个随机地址36H 00100001 00100001 数据的写入与读取0A0H 写总线悬空时的数据11111111 总线悬空时表示的数据是FFH,即写入的数据是11111111,所以读出结果为11111111。

存储器和总线实验报告

存储器和总线实验报告一、实验目的:1.了解存储器和总线的基本概念和原理;2.学习存储器和总线的组成和工作方式;3.掌握存储器和总线在计算机系统中的应用。

二、实验仪器及材料:1.计算机实验箱;2.存储器芯片;3.总线驱动芯片;4.示波器;5.万用表等。

三、实验原理及过程:存储器是计算机系统中的重要组成部分,用于存储数据和指令。

总线是计算机系统中的信息传输通道,用于连接各个硬件设备。

本实验通过实际操作和观察,深入理解存储器和总线的原理与应用。

1.存储器实验:将存储器芯片插入计算机实验箱的指定插槽,并连接好电源和控制线。

打开计算机实验箱的电源,通过示波器和万用表,观察存储器的读写操作。

2.总线实验:将总线驱动芯片插入计算机实验箱的指定插槽,并连接好电源和控制线。

打开计算机实验箱的电源,并连接外部硬件设备,如打印机、显示器等,通过控制总线,进行数据传输和设备控制。

四、实验结果及分析:在存储器实验中,通过示波器和万用表观察到了存储器的读写操作,可以看到存储器的读取速度相对较快,写入速度较慢。

这是因为存储器的读取是通过直接寻址方式,直接获取指定地址上的数据,速度较快;而写入需要进行写入操作,写入数据需要经过一系列的控制和验证步骤,速度较慢。

在总线实验中,通过控制总线进行数据传输和设备控制,可以实现设备间的数据共享和信息传递。

例如,将计算机连接到打印机,通过总线进行数据传输,可以将计算机上的文件直接打印出来。

通过总线还可以连接各种外部设备,如键盘、鼠标、显示器等,实现设备的控制和数据输入输出。

通过本次实验,加深了对存储器和总线的理解和认识。

存储器是计算机系统中重要的存储单元,用于存储数据和指令;总线是计算机系统中的信息传输通道,用于连接各个硬件设备。

存储器和总线的性能对计算机的运行速度和稳定性有重要影响,因此,合理使用和优化存储器和总线是提高计算机系统性能的关键。

五、实验总结:本次实验通过实际操作和观察,加深了对存储器和总线的理解和认识。

计算机组成原理实验_存储器部件教学实验

实验题目存储器部件教学实验一、实验目的:1. 熟悉ROM芯片和RAM芯片在功能和使用方法等方面的相同和差异之处。

学习用编程器设备向EEPROM芯片内写入一批数据的过程和方法。

2. 理解并熟悉通过字、位扩展技术实现扩展存储器系统容量的方案。

3. 了解静态存储器系统使用的各种控制信号之间正常的时序关系。

4. 了解如何通过读、写存储顺的指令实现对58C65 ROM芯片的读、写操作。

加深理解存储器部件在计算机整机系统中的作用。

二、实验设备与器材:TEC-XP+教学实验系统和仿真终端软件PCEC。

三、实验说明和原理:1、内存储器原理内存储器是计算机中存放正在运行中的程序和相关数据的部件。

在教学计算机存储器部件设计中,出于简化和容易实现的目的,选用静态存储器芯片实现内存储器的存储体,包括唯读存储区和随读写存储区两部分,ROM存储区选用4片长度8位、容易8KB的58C65芯片实现,RAM存储区选用2片长度8位、容量2KB的6116芯片实现,每2个8位的芯片合成一组用于组成16位长度的内存字,6个芯片被分成3组,其地址空间分配关系是:0-1777h用于第一组ROM,固化监控程序,2000-2777h用于RAM,保存用户程序和用户数据,其高端的一些单元作监控程序的数据区,第二组ROM的地址范围可以由用户选择,主要用于完成扩展内存容量的教学实验。

地址总线的低13位送到ROM芯片的地址线引脚,用于选择芯片内的一个存储字。

用于实现存储字的高位字节的3个芯片的数据线引脚、实现低位字节的3个芯片的数据线引脚分别连接在一起接到数据总线的高、低位字节,是实现存储器数据读写的信息通路。

数据总线要通过一个双向三态门电路与CPU一侧的内部总线IB 相连接,已完成存储器、接口电路和CPU之间的数据通讯。

2、扩展教学机的存储空间四、实验内容:1) 要完成存储器容量扩展的教学实验,需为扩展存储器选择一个地址,并注意读写和OE等控制信号的正确状态。

计算机组成原理实验(存储器)

引言

• 教学实验系统简介: 本教学实验系统采用部件单元式结构,主要部件单元 见实验箱。 • 教学实验系统特性: 1.若控制信号的跳线器跳左边,表示手动给信号,跳右边 表示控制信号自动产生。 2.实验箱正逻辑设计,指示灯亮表示1,指示灯灭表示0。 3.总清可清地址,需拨0—1—0。 4.做所有实验,总清不能拨在0位置,否则地址总线总为 0000000出厂默认跳线: J1~J12 跳左边 J13~J16 跳右边 J17 、J28空 J18 、J19、J23、J24、J25 跳左边 J20、J21、J22、J26、J27接上跳线 编程开关,拔在“运行”状态 ; 运行程序开关,拔在“运行”状态; 运行方式开关,拔在“单步”状态; SWC,SWA,总清,拔在上面。

实验一 存储器实验

• 本次实验所需用线 两根8芯接线,无需动跳线器。

实验一 存储器实验

• 教学实验系统出厂默认跳线: • J1~J12 跳左边 • J13~J16 跳右边 • J17 、J28空 • J18 、J19、J23、J24、J25 跳左边 • J20、J21、J22、J26、J27接上跳线 • 编程开关,拔在“运行”状态 ; • 运行程序开关,拔在“运行”状态; • 运行方式开关,拔在“单步”状态; • SWC,SWA 总清,拔在上面。

实验一 存储器实验

• 实验要求 1.往存储器的任意两个存储单元(你可自由设定, 应为16进制数)中写入相应的数据(你也可自由设 定,应为16进制数) 。 2.读出你刚才设定的那两个存储单元中的数据, 检验是否是你在实验1中所写入的数据。 • 实验拓展内容 试着将乘法口诀表中的3*1=3、3*2=6、3*3=9、 3*4=12、3*5=15、3*6=18、3*7=21、3*8=24 、 3*9=27写入到存储器中,然后检验之。

计算机组成原理实验报告

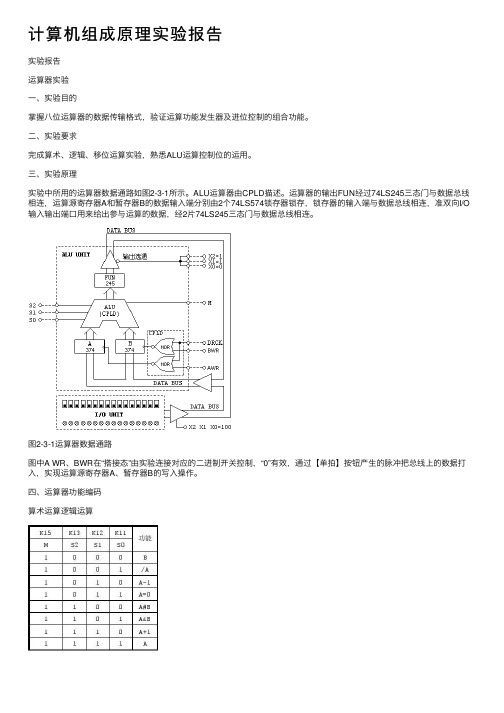

计算机组成原理实验报告实验报告运算器实验⼀、实验⽬的掌握⼋位运算器的数据传输格式,验证运算功能发⽣器及进位控制的组合功能。

⼆、实验要求完成算术、逻辑、移位运算实验,熟悉ALU运算控制位的运⽤。

三、实验原理实验中所⽤的运算器数据通路如图2-3-1所⽰。

ALU运算器由CPLD描述。

运算器的输出FUN经过74LS245三态门与数据总线相连,运算源寄存器A和暂存器B的数据输⼊端分别由2个74LS574锁存器锁存,锁存器的输⼊端与数据总线相连,准双向I/O 输⼊输出端⼝⽤来给出参与运算的数据,经2⽚74LS245三态门与数据总线相连。

图2-3-1运算器数据通路图中A WR、BWR在“搭接态”由实验连接对应的⼆进制开关控制,“0”有效,通过【单拍】按钮产⽣的脉冲把总线上的数据打⼊,实现运算源寄存器A、暂存器B的写⼊操作。

四、运算器功能编码算术运算逻辑运算K23~K0置“1”,灭M23~M0控位显⽰灯。

然后按下表要求“搭接”部件控制路。

表2.3.2 运算实验电路搭接表算术运算1.运算源寄存器写流程通过I/O单元“S7~S0”开关向累加器A和暂存器B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K18=K17=“1”,按下流程分别读A、B。

3.加法与减法运算令M S2 S1 S0(K15 K13~K11=0100),为算术加,FUN及总线单元显⽰A+B的结果令M S2 S1 S0(K15 K13~K11=0101),为算术减,FUN及总线单元显⽰A-B的结果。

逻辑运算1.运算源寄存器写流程通过“I/O输⼊输出单元”开关向寄存器A和B置数,具体操作步骤如下:2.运算源寄存器读流程关闭A、B写使能,令K17= K18=1,按下流程分别读A、B。

①若运算控制位设为(M S2 S1 S0=1111)则F=A,即A内容送到数据总线。

②若运算控制位设为(M S2 S1 S0=1000)则F=B,即B内容送到数据总线。

计算机组成原理 总线控制实验报告

福建农林大学计算机与信息学院信息工程类实验报告系:计算机系专业:计算机科学与技术年级: 2007级姓名:学号:实验课程:计算机组成原理实验室号:___ 实验设备号: 1 实验时间: 2009年5月18日指导教师签字:成绩:实验三总线控制实验1.实验目的和要求1.理解总线的概念及其特性。

2.掌握线总线传输控制特性。

2.实验原理总线是多个部件之间进行数据传送的公共通路,是构成计算机系统的骨架。

借助总线连接,计算机在系统各部件之间实现传送地址、数据和控制信息的操作。

因此,所谓总线就是指能为多个功能部件服务的一组公用信息线。

总线传输实验框图如图1-11所示,它将几种不同的设备挂至总线上,有存储器、输入设备、输出设备、寄存器。

这些设备都需要有三态输出控制,按照传输要求恰当有序的控制它们,就可实现总线信息传输。

3.主要仪器设备(实验用的软硬件环境)ZYE1603B计算机组成原理及系统结构教学使用箱一台,排线若干。

4.操作方法与实验步骤1.根据在总线上的几个基本部件,设计一个简单的流程:①输入设备将一个数写入地址寄存器。

②输入设备将另一个数写入到存储器的当前地址单元中。

③将存储器当前地址单元中的数用LED数码管显示。

2.按照图1-12实验接线图进行连线,仔细检查无误后,接通电源。

(图中箭头表示需要接线的地方,接总线和控制信号要注意高低位—一对应,可用彩排线的颜色来进行区分)图1-12 总线控制实验接线图3.具体操作步骤图示如下:首先使各个控制电平的初始状态位SW_G=1,CE=1,WE=1,LDAR=0,299_G(LED_G)=0,PC_G(WE)=1,CLR=101,并将控制台单元的开关SP05打在“NORM ”状态,然后按下图所示步骤进行。

图中方括号的控制电平要按照从上到下的顺序来进行,其中LDAR 的正脉冲是通过开关单元的LDAR 开关做010变化来产生的,而WE_G 和PC_G(WE)的脉冲则是通过开关单元的WE 和PC_G 开关做101变化来产生的。

存储器读写和总线控制实验报告

存储器读写和总线控制实验报告目录一、实验目的 (2)1.1 熟悉存储器的基本概念和工作原理 (2)1.2 掌握存储器的基本读写操作 (4)1.3 理解总线控制系统的作用和原理 (5)二、实验设备 (6)2.1 存储器模块 (7)2.2 总线控制单元 (8)2.3 示波器 (10)2.4 逻辑分析仪 (11)2.5 计算机调试软件 (12)三、实验原理 (13)3.1 存储器的结构及读写机制 (14)3.2 总线控制的基本概念及组成 (15)3.3 实验中的关键信号和时序 (16)四、实验步骤 (18)4.1 连接实验设备 (19)4.2 加载存储器读操作程序 (21)4.3 观察并记录存储器读操作的时序和信号波形 (22)4.4 加载存储器写操作程序 (23)4.5 观察并记录存储器写操作的时序和信号波形 (24)4.6 调试和优化总线控制单元 (26)4.7 执行完整流程并检查读写数据的一致性 (27)五、实验结果与分析 (27)5.1 存储器读操作的实验结果及数据分析 (29)5.2 存储器写操作的实验结果及数据分析 (30)5.3 总线控制单元的调试效果及实验结果 (31)5.4 实验中遇到的问题与解决方案 (32)六、实验结论与建议 (34)6.1 实验总结 (35)6.2 改进建议 (36)6.3 未来研究 (37)一、实验目的本次实验的主要目的是通过实践操作,深入理解和掌握存储器的基本工作原理、读写操作以及总线控制的基本概念和实现方法。

本实验旨在:理解存储器的分类及其特点,包括只读存储器(ROM)、随机存取存储器(RAM)等。

掌握存储器的寻址方式、存储单元的访问规则以及数据读取写入的基本流程。

学习并实践总线的通信协议,包括信号线的分组、时序控制以及冲突检测与解决。

通过实际操作,培养动手能力和解决问题的能力,加深对计算机系统底层工作的认识。

1.1 熟悉存储器的基本概念和工作原理在实施存储器读写和总线控制实验之前,首先需要对存储器的基本概念和工作原理有一个清晰的认识。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

《计算机组成原理》

实验报告

实验三存储器读写和总线控制实验

一、实验目的

1、掌握半导体静态随机存储器 RAM 的特性和使用方法。

2、掌握地址和数据在计算机总线的传送关系。

3、了解运算器和存储器如何协同工作。

二、实验环境

EL-JY-II 型计算机组成原理实验系统一套,排线若干。

三、实验内容与实验过程及分析(写出详细的实验步骤,并分析实验结果)

实验步骤:

开关控制操作方式实验

注:为了避免总线冲突,首先将控制开关电路的所有开关拨到输出高电平“1”状态,所有对应的指示灯亮。

本实验中所有控制开关拨动,相应指示灯亮代表高电平“1”,指示灯灭代表低电平“0”。

连线时应注意:对于横排座,应使排线插头上的箭头面向自己插在横排座上;对于竖排座,应使排线插头上的箭头面向左边插在竖排座上。

1、按图 3-5 接线图接线:

2、拨动清零开关 CLR,使其指示灯显示状态为亮—灭—亮。

3、往存储器写数据:

以往存储器的(FF)地址单元写入数据“AABB”为例,操作过程如下:

4、按上述步骤按表 3-2 所列地址写入相应的数据

5、从存储器里读数据:

以从存储器的(FF)地址单元读出数据“AABB”为例,操作过程如下:

6、按上述步骤读出表 3-2 数据,验证其正确性。

实验线路图如下所示

四、实验总结(每项不少于20字)

存在问题:由于对操作系统不熟悉和本实验对线路需求大,排线出现错误;读取数据时也出现错误。

解决方法:在实验之前检查线路,发现错误及时纠错;将读取错误的数据进行重新存储,再验证查询。

收获:了解了半导体静态随机存储器RAM的特性和使用方法、地址和数据在计算机总线的传送关系。

五、教师批语。