16通道高分辨CAMAC时间数字转换器

sii9777scluc规格书

SII9777SCLU规格书一、设备概述SII9777SCLU是一款高性能的模拟-数字转换器(ADC),适用于各种高精度测量和控制系统。

它具有高分辨率、低噪声、低失真和低功耗等优点,能够满足各种复杂应用的需求。

二、设备规格1. 分辨率:16位2. 采样率:最高250ksps3. 输入电压范围:±10V4. 精度:±0.5LSB5. 信噪比(SNR):≥80dB6. 总谐波失真(THD):≤-90dB7. 电源电压:±5V8. 工作温度:-40℃~+85℃三、引脚配置SII9777SCLU采用标准的SOIC封装,共有20个引脚。

引脚排列如下:1. Vrefp (正参考电压输入)2. Vrefn (负参考电压输入)3. Vinp (正模拟输入)4. Vinn (负模拟输入)5. CLK (时钟输入)6. DOUT (数据输出)7. Vcc (电源正极)8. GND (地线)9-20. 无连接或可用于其他扩展功能。

四、电气特性1. 参考电压范围:±10V2. 时钟频率:最高1MHz3. 数据输出速率:最高25MHz4. 功耗:≤180mW (典型值)5. 输入阻抗:≥1MΩ6. 输出阻抗:≤50Ω7. 输入偏置电流:≤1nA8. 输入失调电压:≤10μV (典型值)9. 线性误差:≤±0.5LSB (最大值)10. 温漂:≤±1LSB/℃ (最大值)五、机械规格尺寸:4mm x 4mm x 1.3mm (SOIC封装)重量:约0.2g (根据封装和材料的不同会有所变化) 材料:塑料封装,金属引脚。

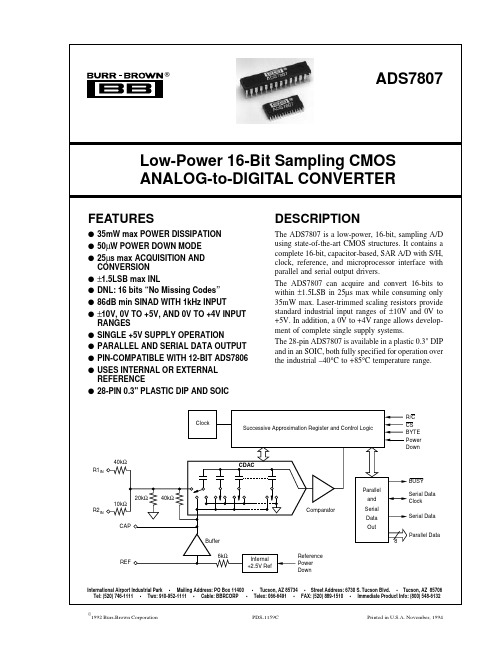

ads7807_低功耗16位采样CMOS AD转换器

10kΩ R2IN CAP

Out Parallel Data Buffer 6kΩ Internal +2.5V Ref Reference Power Down 8

REF

International Airport Industrial Park • Mailing Address: PO Box 11400 • Tucson, AZ 85734 • Street Address: 6730 S. Tucson Blvd. • Tucson, AZ 85706 Tel: (520) 746-1111 • Twx: 910-952-1111 • Cable: BBRCORP • Telex: 066-6491 • FAX: (520) 889-1510 • Immediate Product Info: (800) 548-6132

®

ADS7807

Low-Power 16-Bit Sampling CMOS ANALOG-to-DIGITAL CONVERTER

FEATURES

q 35mW max POWER DISSIPATION q 50µW POWER DOWN MODE q 25µs max ACQUISITION AND CONVERSION q ±1.5LSB max INL q DNL: 16 bits “No Missing Codes” q 86dB min SINAD WITH 1kHz INPUT q ±10V, 0V TO +5V, AND 0V TO +4V INPUT RANGES q SINGLE +5V SUPPLY OPERATION q PARALLEL AND SERIAL DATA OUTPUT q PIN-COMPATIBLE WITH 12-BIT ADS7806 q USES INTERNAL OR EXTERNAL REFERENCE q 28-PIN 0.3" PLASTIC DIP AND SOIC

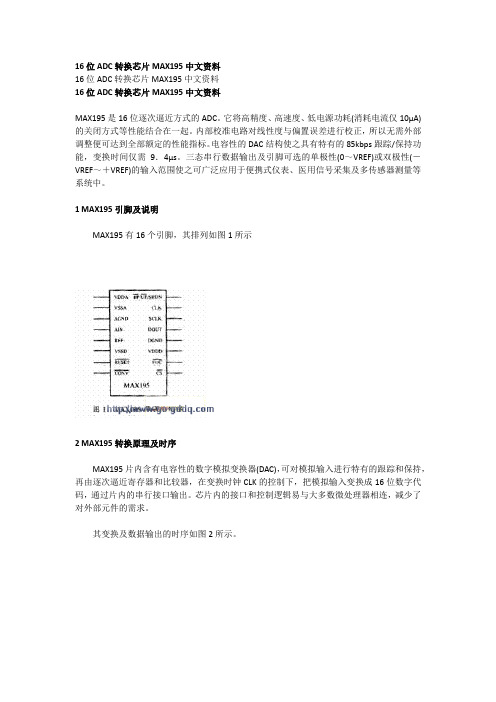

16位ADC转换芯片MAX195中文资料

16位ADC转换芯片MAX195中文资料16位ADC转换芯片MAX195中文资料16位ADC转换芯片MAX195中文资料MAX195是16位逐次逼近方式的ADC。

它将高精度、高速度、低电源功耗(消耗电流仅10μA)的关闭方式等性能结合在一起。

内部校准电路对线性度与偏置误差进行校正,所以无需外部调整便可达到全部额定的性能指标。

电容性的DAC结构使之具有特有的85kbps跟踪/保持功能,变换时间仅需9.4μs。

三态串行数据输出及引脚可选的单极性(0~VREF)或双极性(-VREF~+VREF)的输入范围使之可广泛应用于便携式仪表、医用信号采集及多传感器测量等系统中。

1 MAX195引脚及说明MAX195有16个引脚,其排列如图1所示2 MAX195转换原理及时序MAX195片内含有电容性的数字模拟变换器(DAC),可对模拟输入进行特有的跟踪和保持,再由逐次逼近寄存器和比较器,在变换时钟CLK的控制下,把模拟输入变换成16位数字代码,通过片内的串行接口输出。

芯片内的接口和控制逻辑易与大多数微处理器相连,减少了对外部元件的需求。

其变换及数据输出的时序如图2所示。

由时序可以看出,在前次变换结束至少经过三个或三个以上时钟周期后,变换在有效后的CLK时钟下降沿开始(MAX195对信号的跟踪/保持、采集需4个CLK周期)。

同时,在下一个时钟下降沿变高,待经过9.4μs(CLK为1.7MHz)变换结束后,由高变低,给出变换结束信号,可送去中断或被查询。

变换结束由三态串行口DOUT端输出。

在变换期间由CLK控制读出数据,也可在两次变换之间由SCLK串行时钟定时读出数据,最高速率可达5Mbps。

图2中所示情况为后者,在保持低电平后,在每个SCLK的下降沿,DOUT端按MSB在前的次序输出一位数据,否则,DOUT处于高阻态。

3 MAX195的校准MAX195在上电时自动进行校准。

为了减少噪声的影响,每一个校准试验进行多次并对其结果求平均值。

CAMAC介绍

在插件中的用途 选择插件(从控制器连来的单线) 选择插件的一部分 确定插件内将完成的功能 控制第一阶段的操作(机箱数据通道信号可变化) 控制第二阶段的操作(机箱数据通道信号可变化) 输出信息到插件 从插件取信息

C A M A C 总 线 的 功 能

命令

定时

选通1 选通1 选通2 选通2

数据

写 读

状态

② ③ ④ ⑤ ⑥ ⑦ ⑧

名称

符号 站号 子地址 功能码 N A1,2,4,8 F1,2,4,8,16 S1 S2 W1-W24 W1R1-R24 R1L B Q X Z I C P1, P2 P3-P5 P3+24 +6 -6 -24 0 +12 -12 E Y1, Y2

接点数 1 4 5 1 1 24 24 1 1 1 1 1 1 1 2 3 1 1 1 1 2 1 1 1 2

CAMAC总线的特点 CAMAC总线的特点

① CAMAC通过总线转换模板可和各种计算机相连,数据线宽度为24 CAMAC通过总线转换模板可和各种计算机相连,数据线宽度为24 位,数据传输速率最高可达500Kbi/s(在一些先进的CAMAC数据 位,数据传输速率最高可达500Kbi/s(在一些先进的CAMAC数据 采集系统中,可达几Mbit)。距离一般为25m~50m,如果采用平 采集系统中,可达几Mbit)。距离一般为25m~50m,如果采用平 衡差分长线传输驱动器,距离可达几百米甚至上千米,采用串 行公路传输则可更远些,但传输速率最高为35Kbit/s。 行公路传输则可更远些,但传输速率最高为35Kbit/s。 CAMAC是一种具有若干功能单元的模块化系统,用这些功能单元 CAMAC是一种具有若干功能单元的模块化系统,用这些功能单元 可以组成各种复杂的装置。 功能单元的电路使用集成电路和类似的高密度的元件。 功能单元制成插件单元装在标准机箱之中。 每个插入单元直接和数据通道(Dataway)相连接。这个数据通道 每个插入单元直接和数据通道(Dataway)相连接。这个数据通道 构成机箱的一个组成部分,由它传送数字信号、控制信号和电 源。 一台机箱和多个插入单元组成的装置能够连接到一台在线的计 算机上。 插入单元的对外连接可以遵守所连接的传感器和计算机等的数 字信号标准或模拟信号标准,也可以遵守本规范所给的推荐标 准。 多机箱装置可以通过并行公路或串行公路来互相连接。

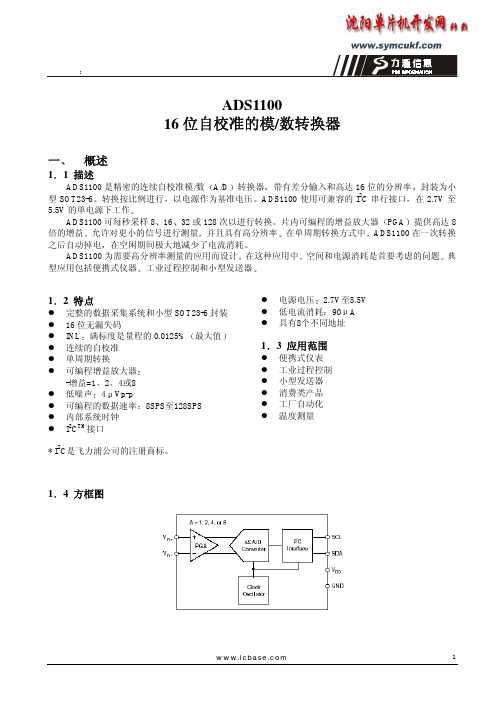

16位自校准模数转换器ADS1100中文资料

多数时候总线是空闲的 不发生通信 而且两条线均为高电平 在产生通信时 总线被激活 只有主 机才能开始一次通信 为了开始通信 主机在总线上形成一个开始条件 通常 只有在时钟线为低电平时 数据线才允许改变状态 如果在时钟线为高电平时 数据线改变了状态 则形成一个开始条件 或相反地 形成一个停止条件 开始条件是当时钟线为高电平时 数据线从高到低的跳变 停止条件则是当时钟线为 高电平时 数据线从低到高的跳变

在设计一个输入滤波器电路时 应考虑到滤波器网络和ADS1100输入阻抗之间的交互作用

四 ADS1100 的使用

4 1 工作方式

ADS1100 以下面两种方式中的一种工作 连续转换和单周期转换 在连续转换方式中 ADS1100 连续地进行转换 一旦转换完成 ADS1100 即将结果置入输出寄存器 并立即开始另一轮转换 当 ADS1100 处于连续转换方式中时 配置寄存器中的 ST/BSY 位总是读作 1 在单周期转换方式中 ADS1100 会等待直到转换寄存器中的 ST/BSY 位被置位为 1 此时 ADS1100 上电并且工作在单周期转换方式下 在转换完成之后 ADS1100 将结果置入输出寄存器中 复位 ST/BSY 位为 0 并掉电 当转换正在进行时 写 1 到 ST/BSY 则不影响该位内容 在从连续转换方式切换到单周期转换方式时 ADS1100 将完成当前转换 复位 ST/BSY 位为 0 并 掉电

–0.3V至+6V 100mA 瞬间 10mA 连续 –0.3V至VDD + 0.3V

ADS1115 超小型,低功耗,16双牛逼的 模拟-数字转换器中文资料

∙特点∙应用∙描述∙订购信息∙绝对最大额定值∙电气特性∙引脚配置∙时序要求∙概览∙快速入门指南∙复用器∙模拟输入∙满量程输入∙数据格式∙走样∙操作模式∙复位和上电∙低功耗税骑自行车∙COMPARATOR(ADS1114/15只)∙转换就绪PIN(ADS1114 / 5只)∙SMBus报警反应∙I2C接口∙I2C地址选择∙I2C广播呼叫∙I2C速度模式∙从属模式操作∙接收模式∙传输模式∙写/读寄存器∙寄存器∙指针寄存器∙转换寄存器∙CONFIG寄存器∙lo_thresh与Hi_thresh寄存器∙应用信息∙基本连接∙连接多个设备∙GPIO端口通信∙单端输入∙低侧电流监视器- ADS111 3 ADS111 月4ADS1115www.ti.co 米SBAS444A 2009年5月- 2009年8月修订超小型,低功耗,16双牛逼的模拟-数字转换器检查样品:ADS1113 ADS1114 ADS1115特点∙超小型QFN封装:2毫米×1.5毫米×0.4毫米∙宽电源电压范围:2.0V至5.5V∙低消耗电流:连续模式:只有150 μ单次模式:自动关闭∙可编程数据速率:8SPS到860SPS∙内部低漂移电压基准∙内部振荡器∙内部PGA∙我2C™接口:引脚可选择的地址∙四个单端或两个差分输入(ADS1115)∙可编程比较器(ADS1114和ADS1115)∙工作温度:-40°C至+140°C时应用∙便携式仪表∙消费品∙电池监控∙温度测量∙工厂自动化和过程控制描述ADS1113,ADS1114和ADS1115是高精度模拟到数字转换器(ADC)号决议第16位,超小型,无铅QFN-10封装或MSOP-10封装中提供。

的ADS1113/4/5设计精度,功耗和易于记住的实施。

ADS1113/4/5功能板载参考和振荡器。

数据传输通过一个I 2 C兼容串行接口,四个I 2 C 从地址。

TDCs 时间数字转换器 产品简介

评估系统 产品名称

GP2-EVA-KIT

GP21-EVA-KIT

ATMD-GPX PCI-System

产品代码 1780

1781

1532

描述

基于TDC-GP2的测量评估系统, 包括PICOPROG编程器,评估软件,导线

TDC的基本原理是采用缓冲延迟阵列。巧妙的电路结 构、担保电路和特殊的芯片布层方法,使其精确再现 了信号通过的门的个数。TDC的最高分辨率取决于芯 片的最小门传播延迟时间。测量由START信号开始以 STOP信号终止。根据环形振荡器的位置和粗值计数器 的数值,可以计算出START和STOP之间的时差。有两 种方法可以修正温度和电压给缓冲延迟带来的影响。 这两种方法都采用了一个范围在1-40MHz的外部参考 时钟。第一种方法是校准,TDC自动测量两个参考时 钟周期并在其内部校准时间测量结果。第二种方法是 精度可调模式,在这种模式下测量单元的电压可以被 调节到固定值,以保证分辨率保持极高的稳定性。

n 双通道,250皮秒分辨率 n 单通道,125皮秒分辨率 n 15ns的脉冲对儿分辨率 n 每个通道可接收4个脉冲信号 n 双通道可达8个脉冲信号 n 测量范围 n 3ns到7.6us(测量范围1) n 60ns到200ms(测量范围2,具有前置配器) n -3.8us到3.8us(分辨率可调模式) n 分辨率可调模式:石英准确的精度调节

时间数字转换器概述

集成电路 产品名称

TDC-GP1 TDC-GP2 TDC-GP21

TDC-GPX TDC-GPX -FG

产品代码 封装 标准包装数量 包装形式 描述

time-to-digital convertersadc特点

time-to-digital convertersadc特点

ADC(Analog-to-Digital Converter)是一种电子设备,将模拟

信号转换为数字信号。

其中一种类型是时钟到数字转换器(Time-to-Digital Converter,TDC)。

TDC具有以下特点:

1. 高分辨率:TDC能够以非常高的精度测量时间间隔,通常

可以达到亚纳秒级别甚至更高的分辨率。

2. 高速性能:TDC可以快速地将时间间隔转换为数字信号,

使其适用于需要高速数据采集和处理的应用。

3. 宽动态范围:TDC具有广泛的测量范围,可以测量从纳秒

到几十皮秒的时间间隔。

4. 低功耗:TDC通常使用低功耗的电路设计,以减少能耗和

热量产生。

5. 可编程性:TDC通常具有可编程的参数设置,可以根据特

定应用的需求进行调整和优化。

6. 多通道支持:TDC可以同时处理多个通道的信号,使其适

用于需要并行处理多个信号的应用。

7. 低噪声:TDC的设计可以最大程度地减少测量过程中的噪

声干扰,提高测量精度。

总的来说,TDC是一种高性能的模拟信号到数字信号转换器,

具有高分辨率、高速性能、宽动态范围、低功耗、可编程性、多通道支持和低噪声等特点,适用于需要高精度时间测量的各种应用场景。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第19卷 第3期核电子学与探测技术V ol119N o13 1999年5月Nuclear E lectronics&Detection T echnology May199916通道高分辨CAMAC时间数字转换器 金革 佐佐木修(中国科学技术大学近代物理系,合肥,230027) (日本国家高能物理研究所物理部)介绍一种16通道高分辨C AM AC时间数字转换器组件,具有12位动态范围,其最小时间分辨达26ps,16个通道的总变换时间仅15μs。

该组件采用C OM M ON ST ART模式,16个独立的ST OP。

该组件有两种读出方式:随机读出和稀疏扫描读出方式。

为了简化设计,提高组件的可靠性,在组件中T AC部分被设计成一个很小的模块,每个模块包含两路独立T AC,组件中共使用了8个这样的T AC模块。

详细介绍了该16通道高分辨C AM AC时间数字转换器组件的原理。

关键词:T DC C AM AC 组件 分辨率0 引言时间数字转换器简称T DC,是一种将时间变换成数字的转换器,它被广泛应用于核物理和高能物理实验以及与时间测量有关的场合。

由于它的应用非常广泛,近几年T DC技术得到了很大的发展,产品的通道数不断增加,分辨率不断提高,变换时间不断降低。

目前国际上已有的C AMAC T DC产品分辨率已达到25ps,变换时间为百μs量级。

我们设计这种16通道高精度C AMAC T DC组件的主要目的在保持高精度的前题下,进一步降低其变换时间到10μs量级,增加通道数目和加大其动态范围。

1 主要性能指标1)该组件被设计成标准单宽C AMAC组件,包含16个通道。

2)采用C OM MON ST ART模式,即一个ST ART输入,16个独立的ST OP输入。

所有输入/输出采用NI M电平,使用LE MO插座。

3)16个通道的总的转换时间仅为15μs。

4)可根据需要通过跳线选择不同的量程和分辨率:量程/ns105206410250500100050010002000分辨率/ps265010262125250125250500 5)可通过编程设置上阈和下阈,以选择有用的数据。

6)可采用随机读出和稀疏扫描读出两种方式:随机读出方式下,不管每个通道是否有有效的数据,所有通道的数据都可以通过F(0)命令以任何顺序读出;稀疏扫描读出方式下,没有ST OP信号的通道和超出所预置的上阈和下阈范围的通道将被跳过,只读那些有有效数据的通道。

采用这种读出方式可节省数据的读出时间。

7)快清除时间小于800ns。

2918)提供一个TEST 输入用于外部测试。

图1 16通道T DC 组件原理框图2 电路原理图1给出了T DC 组件的原理框图。

每个通道中包含一个T AC 电路,它将C OM MON ST ART 输入和ST OP 信号之间的时间间隔转换成电压幅度,并提供一个变换标志信号。

T AC 电路的输出经过缓冲之后由ADC 进行数字化,ADC 的输出按照通道的顺序存入存储器中。

在数据被存入存储器的同时,数据同事先预置在阈寄存器中的上阈和下阈值进行比较以确定数据是否落入给定区间,如果某一通道的数据落入给定区间,则在HIT 寄存器中的相应位上给出标志,以供数据读出时使用。

2.1 前面板输入信号从组件的前面板共输入19个外部信号,其中包括一个C OM MON ST ART 信号,16个ST OP 信号,一个TEST 信号和一个C LE ATR 信号。

所有输入信号为NI M 电平,通过50Ω的LE MO 同轴电缆输入。

因为ST ART 信号要用来产生T AC 的控制信号,为了保证满量程使用,要求ST ART 信号超前ST OP 信号40ns 。

TEST 输入对每通道提供一个公共ST OP ,它主要用于测试。

在任何时侯输入一个C LE AR 信号都将终止转换过程。

图2 T AC 模块电路图2.2 前面板输出信号在T DC 进行转换时,组件通过前面板输出一个MI N 标准BUSY 信号。

2.3 TAC 模块T AC 电路最初是为TK O BOX 系统[1]开发的,之后又经过重新设计和多次改进,最后定形为42mm ×26mm 的小模块。

每个模块有两个T AC 通道,每个通道有一个电流开关,一个RAMP 电容和两个采样/保持电容,如图2所示。

虚线部分已被集成为一个单片电路,它主要用于甄别ST OP ,然后产生驱动电流开关的信号和产生ST OP 信号标志。

图3给出了T AC 的时序图,在RESET 信号之后,RAMP 电容被充电到电源电压。

在ST ART 信号到达之前,BEFORE 输入将RAMP 电容上的电压值保持在采样/保持电路的一个臂上。

391图3 T AC 模块时序图ST ART 信号打开电流开关,RAMP 电容开始通过电流开关放电。

当ST OP 信号到来时,电流开关被关闭,放电过程停止;如果没有ST OP 信号,RAMP 电容上的电压将被放电到最低值。

AFTER 信号将最终的RAMP 电容上的电压保持在采样/保持电路的另一个臂上。

采样/保持电路的两个臂上的电压差代表了ST ART 和ST OP 输入的时间间隔。

2.4 ADC 部分为了减少数字化变换时间,电路中使用了16个12位的逐次比较型ADC 对T AC 的输出进行数字化,每个通道使用一个。

16个ADC的数据最后按通道顺序存入存储器。

数据在存储器中的格式为:16151413121110987654321通道I D 12位数据2.5 控制寄存器控制寄存器用于存放控制变换和比较的控制字,可通过F (6)3A (0)和F (19)来进行读或写,其格式为: 87654321未使用TRGUTELTE TRG 为数据转换控制标志。

TRG 为0时,只要任何一个通道有一个有效的ST OP 信号,就进行数据转换;TRG 为1时,只要有ST ART 信号,就进行数据转换。

UTE 和LTE 为上阈和下阈的使能标志,它们为0时,表示不使用上阈或下阈,无论转换的数据如何,都将在HIT 寄存器的相应位上置1;它们为1时,表示转换的数据将同上阈和/或下阈进行比较,当数据落入上阈和下阈之间时,将在HIT 寄存器的相应位上置1,否则置0。

2.6 阈寄存器和HIT 寄存器为了能剔除不满足要求的数据,组件中设有一个阈寄存器和一个HIT 寄存器。

用户可以通过F (6)3A (2)和F (20)来读或写阈寄存器。

在ADC 的数据被写入存储器的同时,数据要同阈寄存器中的上阈和下阈进行比较。

如果某一通道的数据落在上阈和下阈之间,则在HIT 寄存器的相应的位上置1,否则置0。

上阈和下阈的比较功能可以通过将控制寄存器中的UTE 和LTE 置0来关掉。

阈寄存器的数据格式:16151413121110987654321上阈值下阈值 阈寄存器的高8位用来存放上阈值,低8位用来存放下阈值。

上下阈值的范围都为0~4096,步长为16。

2.7 数据读出491组件提供两种读出方式供用户选择:随机读出方式和稀疏扫描读出方式。

在随机读出方式下,用户可使用F(0)3A(X)读出任何一个通道的数据,X从0到15;当采用稀疏扫描读出方式时,用户可使用F(4)命令。

HIT寄存器记录了有效的通道,读出从最低的有效通道开始,每读出一个通道,则HIT寄存器中相应位被清除,然后再从下一个最低的有效通道开始读,直到全部通道被读完。

在读完最后一个通道时,组件给出一个Q响应。

3 CAMAC命令DAT AW AY命令F(0)3A(X):从数据寄存器中读X+1通道的数据;F(4):以稀疏扫描方式读数据,只读落入上阈和下阈之间的数据,稀疏扫描从最低通道开始,当读完所有通道时,回答一个Q响应。

F(6)3A(0):读控制寄存器。

F(6)3A(1):读HIT寄存器。

F(6)3A(2):读阈寄存器。

F(8):测试LAM,如果有LAM,则产生一个Q=1。

F(9):清除组件,复位前端。

F(10):清除LAM,发生在S2时刻。

F(11):复位控制寄存器,发生在S2时刻。

F(16)3A(X):向数据寄存器中写X+1通道的数据。

F(19):预置/复位控制寄存器位。

F(20):写阈寄存器。

F(24):失效LAM,发生在S2时刻。

F(26):使能LAM,发生在S2时刻。

非DAT AW AY命令C,Z:复位前端,清除和失效LAM,清除控制寄存器和HIT寄存器。

4 性能测试我们利用REPIC公司生产的RPC-070T DC TESTER对该组件进行了测试,积分非线性如图4所示。

由图中可以看出在高达80ns的区域内,积分非线性不超过ADC的一位,即26ps。

转换增益的温度稳定性如图5所示,其温度稳定性好于0.004%/℃,典型值为0.002%/℃。

基点随温度的变化如图6所示,其值小于20ps/℃,典型值10ps/℃。

图4 积分非线性 图5 转换增益的温度稳定性图7给出了从C LE AR到下一个ST ART输入之间的时间间隔曲线。

为了使定时误差小于591一个计数,这个时间间隔应不小于800ns。

图6 基点漂移 图7 C LE AR曲线5 结束语该T DC组件无论在性能上还是在功能上都达到了设计要求。

同国际上目前已存在的T DC产品相比不仅具有功能全,而且还具有比同类产品的变换时间低一个量级的特点。

在本课题的设计过程中,日本国家高能物理研究所的大须贺教授曾给予多方面的帮助和指导,在此表示感谢。

参考文献1Sasaki O,et al.A high res olution T DC in TK O box system.IEEE T rans Nucl Sci,1988,NS35(1):(收稿日期:1998-01-06) 16Channel High Resolution CAMAC T DCJin G e Osamu Sasaki (Dept of M odern Physics,University of Science and T echnology of China,Hefei,230027)(Physics Division,KEK, Tsukuba,Ibaraki305,Japan)Abstract A16channel high C AM AC T DC m odule with26ps res olution and total15μs conversion time was developed. The C omm on ST ART m ode was used.The data can be read out in both random and sparse scan ways.In order to sim plify the circuit and enhance the reliability,a special T AC card with tw o channels was designed.There are8T AC cards in this m odule.In this paper,the principle of this C AM AC T DC m odule will be described in detail.K ey w ords:T DC C AM AC M odule Res olution【作者简介】金革,男,39岁,副教授,博士;佐佐木修,男,42岁,博士。