CMOS晶体管基础共28页文档

CMOS基础及基本工艺流程

CMOS基础及基本工艺流程

1.单晶硅衬底制备:首先需要准备单晶硅衬底,它是整个集成电路的

基础。

这一步骤通常会涉及硅片切割和粗化,最终得到大小合适的硅衬底。

2.外延生长:在单晶硅衬底上外延生长蓝宝石或氮化硅等薄膜,这些

薄膜将作为隔离层使用,以电隔离各个晶体管。

3.门电极制备:在隔离层上制备门电极。

通常使用化学气相沉积(CVD)或物理气相沉积(PVD)等技术,在薄膜上沉积一层金属,如铝或钨。

4.掺杂:利用掺杂技术向单晶硅衬底中注入掺杂物(例如硼或磷),

以改变硅的电子特性。

5.晶体管制备:利用光刻技术定义出晶体管的结构,通过曝光、阻挡、显影等步骤,制造出源极、栅极和漏极之间的结构。

6.金属互连:使用金属沉积和光刻技术,在晶体管上制造出金属互连层,将各个晶体管连接在一起。

7.电介质和过程模拟:制备电介质层,通常使用氧化硅或氧化铝等材料。

过程模拟是为了检测制造过程中的缺陷和问题。

8.上下电极制备:制造上下电极用于晶体管之间的连接。

9.晶体管测试:测试晶体管的性能和可靠性。

10.封装和测试:最后,将制造好的芯片封装成集成电路,并进行最

终的测试。

以上是CMOS基本工艺流程的主要步骤,每个步骤都需精确控制和复杂操作,以确保芯片的性能和可靠性。

CMOS技术由于其功耗低、稳定性好和集成度高等优点,被广泛应用于各种电子设备中,如微处理器、存储器、传感器等。

cmos基础知识

1 W ⇒ I D = µ nCox (VGS − VTH )2 2 L'

(2.10)

若

L' ≈ L

,则 I D 与 VDS 无关.

VDS > (VGS − VTH ) 时, I D 相对恒定,器件工作在饱

和区。

2012-3-15 20

MOS的 I/V特性

*式(2.6),(2.10) 为analog CMOS design 的最基本的 方程式.

V DS < VGS − VTH 时,器件工作在“三极管区”.

2012-3-15 15

MOS的 I/V特性

2.2.3 MOS器件深 Triode区时的导通电阻

MOS器件作为模拟开关,或小值线性电阻运用时, 都会工作于深Triode区。此时VGS较大,MOS管的 VDS很小,若满足:

VDS << 2(VGS − VTH )

MOSEFT

♦ MOSEFT的基本概念 ♦ MOSEFT的工作原理 ♦ MOSEFT的I/V特性

2012-3-15

1

MOSFET的基本概念

1. MOSFET的结构简图

图2.1 NMOSFET结构简图

2012-3-15 2

MOSFET的基本概念

图2.3 CMOS FET的结构简图

2012-3-15 3

W I D = µ n Cox L ID

1 ⎡ 2⎤ (VGS − VTH )VDS − VDS ⎥ ⎢ 2 ⎣ ⎦

(2.6)

1 W = µ n C ox (V GS − VTH ) 2 2 L'

(2.10)

它们描述了ID与工艺常数 µ n Cox , 器件尺寸W和L以及 栅和漏相对于源的电位之间的关系 .

第二章 CMOS器件基础

MOS管的电流方程

2. Cox单位面积栅电容 Cox=ɛ0ɛsio2/tox ɛ0:真空介电常数,8.854x10-12 F/m Ɛsio2:栅氧化层(SiO2)的相对介电常数 3.9 tox:栅氧化层厚度 可以计算:当tox=50A(1A=0.1nm)时, Cox=(8.854x10-12x3.9x10-6)/5x10-3 =6.9fF/μm2 (1fF=10-15F) (学会如何计算,注意单位统一)

同一衬底上的NMOS和PMOS器件

MOS管所有pn结 必须反偏: *N-SUB必须接最 高电位VDD! *P-SUB必须接最 低电位VSS! *阱中MOSFET衬 底常接源极S

寄生二极管

MOS管符号

G

G

(a)

四端器件,一般在模拟电 路设计中采用。

(b)

省去了衬底,默认为 衬底与源 管。只区分管子类 型。常用于数字电 路

在集成电路设计中,在同一硅片衬底上做许多管子,为

二级效应1:体效应

保证它们正常工作,一般N管衬底要全部接最低点位,P 管衬底接最高点位,因此,有些管子源极与衬底之间存在 电位差。 为了保证沟道与衬底之间的隔离,PN结必须反偏,图中 T2管的Vbs<0 当Vbs<0时,导致阈值电压Vth增大,沟道变窄,沟道电 阻变大,ID减小,称此效应为体效应,或者背栅效应, 衬底调制效应。

L=4µ

L=6µ

∂ID/∂VDS∝λ/L∝1/L2

二级效应3:亚阈值导电性

当VGSVTH时和略小于VTH ,“弱”反型层依然存在, 与VGS呈现指数关系。当VDS大于200mV时,

这里ζ>1,VT=kT/q

MOS管亚阈值电流ID一般为几十~几百 nA, 常用于低功耗放大器、带隙基准设计。

晶体管基础知识

前言集成电路只有在高倍放大的情况下才能看到它的真面目。

它的表面到处是错综复杂的细微的连线,而在这下面则是同样错综复杂的掺杂硅的图形,所有这些都是按照一套称作layout的蓝图做出来的。

模拟和混合信号集成电路的layout很难做到自动化。

每个多边形的shape和placement都需要对器件物理,半导体制造和电路理论的深刻理解。

尽管已经有30年的研究了,但仍旧有许多不确定性。

这些知识分布在艰涩难懂的期刊文章和未出版的手稿里。

本书则把这些知识整体统一串连了起来。

原本这本书是打算写给LAYOUT设计师看的,同时它也适合那些希望更好的理解电路和LAYOUT之间关系的电路设计师。

由于本书拥有大量的读者,特别是那些对于高等数学和固体物理学不是很精通的人,所以本书尽量降低了数学运算,并使用了最普遍使用的变量和单位。

读者只要会基本代数和基本的电子学就可以。

书中的练习假定读者能使用LAYOUT编辑软件,不过即使没有,大部分习题还是能用笔和纸完成的。

本书有14章和5篇附录。

前2章是对器件物理学和半导体工艺的一个整体概括。

在这2章里,简单的文字解释和图形模型代替了数学推导。

第3章是关于3种原型工艺:标准BIPOLAR, SILICON-GATE CMOS 和ANALOG BICOMS。

重点将放在截面图和这些截面图与样品器件的传统layout之间的相互关系。

第4章着重讨论了LAYOUT在决定可靠性方面的作用和通常的失效机制。

第5和6章则是电阻和电容的LAY OUT。

第7章以电阻和电容为例讨论了匹配的原理。

第8章到第10章是BIPOLAR器件的LAYOUT,而第11,12章有关场效应管的LAYOUT和匹配。

第13,14章讨论了一些更深入的话题,包括器件合并,G UARD RINGS,ESD保护结构和FLOORPLANNING。

附录则包含缩写表,MILLER指数的讨论,习题中需要的样例LAYOUT规则和书中使用的公式的推导。

CMOS电路基础

CMOS电路基础CMOS(亦称互补金属氧化物半导体)电路是一种在数字电路和模拟电路中广泛应用的技术。

本文将对CMOS电路的基础知识进行论述,包括CMOS电路的构成、工作原理以及应用领域。

一、CMOS电路的构成CMOS电路由PMOS和NMOS晶体管组成,其中PMOS是P型金属氧化物半导体晶体管,NMOS是N型金属氧化物半导体晶体管。

这两种晶体管互补共存,并以互补的方式进行电路设计,因此被称为CMOS电路。

二、CMOS电路的工作原理1. PMOS晶体管PMOS晶体管是由P型衬底、两个N型源/漏极和用于控制的栅极组成。

当栅极电压为低电平(0V)时,PMOS导通,形成一个通路。

当栅极电压为高电平(正电压)时,PMOS截止,断开通路。

2. NMOS晶体管NMOS晶体管是由N型衬底、两个P型源/漏极和栅极组成。

当栅极电压为高电平(正电压)时,NMOS导通,形成一个通路。

当栅极电压为低电平(0V)时,NMOS截止,断开通路。

3. CMOS电路的工作原理在CMOS电路中,通过同时控制PMOS和NMOS的开关状态,可以实现逻辑门以及其他各种电路。

例如,当输入A为低电平(0V),输入B为高电平(正电压)时,通过控制PMOS导通、NMOS断开,可以实现与门的功能。

只有当输入A为低电平且输入B为高电平时,输出为高电平;其他情况下输出为低电平。

三、CMOS电路的应用领域CMOS电路由于其低功耗、高噪声抑制能力和强电流驱动能力等特点,被广泛应用于各个领域。

以下是一些常见的应用领域:1. 数字系统CMOS电路可用于各种数字逻辑电路中,例如计算机、移动设备和通信设备等。

其低功耗特点使得电池供电的设备能够更加高效地工作。

2. 模拟系统CMOS电路也可应用于模拟电路领域,例如运放、模数转换器和数模转换器等。

其高噪声抑制能力使得模拟信号的处理更加准确。

3. 存储器CMOS电路在存储器中扮演着重要角色。

静态随机存储器(SRAM)和动态随机存储器(DRAM)等都采用了CMOS电路技术,以实现高性能和高密度的存储器单元。

CMOS晶体管基础

Cox’ : 表示单位面积氧化层的电容值。

LD: 表示栅极和S、D重叠的宽度(由工艺精度决定)。

深亚微米CMOS It.P+Act. Poly M1 M2 M3 Units

Area (sub.) 526 937 83 25 10 8 aF/um2

Area (poly)

Cox

ox

TOX

and Cox Cox W L

Capacitance is comprised of three components

Cgb

ox

L 2 LDW

TOX

Cgd

Cgs

ox LD W TOX

CGDO W

CGSO W

以上各式中:

Eox: 氧化层的介电常数。

Tox: 氧化层的厚度。

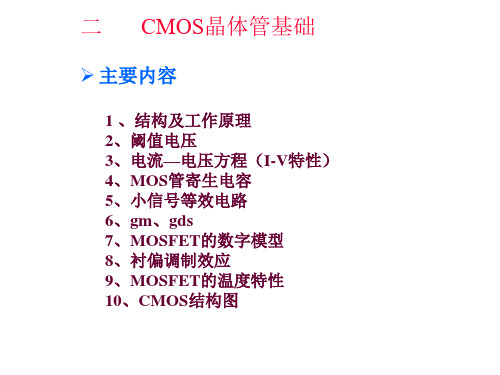

二 CMOS晶体管基础

➢ 主要内容

1 、结构及工作原理 2、阈值电压 3、电流—电压方程(I-V特性) 4、MOS管寄生电容 5、小信号等效电路 6、gm、gds 7、MOSFET的数字模型 8、衬偏调制效应 9、MOSFET的温度特性 10、CMOS结构图

1、工作原理

3D结构图

Polysilicon

决定MOSFET的速度和功耗等众多特性 L和W由设计者选定 通常选取L= Lmin,由此,设计者只需选取W W影响MOSFET的速度,决定电路驱动能力和功耗

① VGS〈Vthn时

下面的结构是N+PN+,耗尽层内是没有 自由移动的电荷的。D、S之间没有形成 一条电流通道,所以IDS=0。

②,VGS>=Vthn时

54 18 11 aF/um2

Area (M1)

46 17 aF/um2

Area (M2)

cmos基础知识

VDS

= (VGS −VTH )

点上,且相应各峰值电流为:

I D,max

=

1 2

µnCox

W L

(VGS

− VTH )2

(2.7)

VGS-VTH为过驱动(overdrive)电压,只有过驱动 电压可以形成反型层电荷。

VDS < VGS − VTH 时,器件工作在“三极管区”.

2012-3-15

15

MOS的I/V特性

2012-3-15

( ) (2.2)

量纲=

⎜⎛C ⎝

m3

⎟⎞ ⎠

*

m

s

=

A m2

10

MOS的I/V特性

(2) 考虑一个源漏都接地的NFET,反型层中的电荷密度为多少?

若假设VGS=VTH时开始反型,那么由栅氧化层电容引起的反 型电荷密度正比于VGS-VTH。当VGS>VTH时,栅电荷必定会被 沟道电荷所镜像,从而产生一个均匀的沟道电荷密度为:

2.2.3 MOS器件深Triode区时的导通电阻

MOS器件作为模拟开关,或小值线性电阻运用时,

都会工作于深Triode区。此时VGS较大,MOS管的

VDS很小,若满足:

VDS << 2(VGS −VTH )

此时(2.6)简化为:

ID≈µnCoxW L(VGS

−VTH

)VDS

(2.8)

(2.8)表明 ID ~ VDS 为直线关系,如图(2.12)所示.

(2.4)

2012-3-15

12

MOS的I/V特性

(3) 电荷漂移速度

υ = µE

(2.5)

υ :漂移速度 drift speed

CMOS器件结构

Cch

t ox

* 单位面积电容最大的电容

N+

N+

Rs

* 沟道电阻问题

P型衬底 沟道

邹志革

EST-ICC

33

集成电容

•MOS电容:

Cch

* 非线性电容 适用于电源滤波

* 沟道长度需权衡考虑

Vc MOS电容C/V特性

减小沟道电阻的方法

邹志革

EST-ICC

34

集成电容

•“夹心”电容

* 线性电容 * 电容值为:

IDS=k′•W/L•[(VG-VT-VS)2-(VG-VT-VD)2]

邹志革

EST-ICC

10

MOS晶体管

• MOS晶体管的电特性

– VG, VS, VD分别是栅, 源, 漏端的电压, VT是开启电压. – k′是本征导电因子, k′=µ•Cox/2, µ是表面迁移率, 属

于硅材料参数, Cox是单位面积栅电容,属于工艺参数 – W, L分别是MOSFET的沟道宽度和长度,属于物理参数 – 管子的最小沟道长度Lmin标志着工艺的水平— — 特征

–衬底PNP BJT –PSD/NWELL Diode –NSD/P-epi Diode

邹志革

EST-ICC

6

MOS晶体管

• MOS晶体管 –最基本的有源元件 –在CMOS工艺中,有PMOS和NMOS 两种 –可用作跨导元件,开关,有源电阻, MOS电容

邹志革

EST-ICC

7

MOS晶体管

• NMOS晶体管的 版图和结构

邹志革

EST-ICC

19

连线

w t h

substrate

单位长度电容的经验公式:

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

3D结构图

Polysilicon

Aluminum

L

W

Gate

Source

Drain

G

S

Poly D

Oxide

n+

p-substrate

Leff LDrawn

n+ LD

n+

n+

W

W

线宽(Linewidth), L

特征尺寸(Feature Size)指什么?

MOSFET的三个重要几何参数

IDVGSVTHN VDSV2D 2S

WhereKPnW L

MOSFET I-V 特性 (饱置在 VGS VTHN ,此时沟道已形成. ➢ 漏源电压较大 (i.e. VDS VGS – VTHN). ➢ 理想的漏极电流可表示为:

ID2

4、MOS Capacitance

MOS电容:由器件本生的构造引起的。 Cgs: 栅极和源极的寄生电容。(平板电容) Cgd: 栅极和漏极的寄生电容。(平板电容) Cgb: 栅极和衬底的寄生电容。 Cdb: 漏极和衬底的寄生电容。(PN结电容) Csb: 源极和衬底的寄生电容。(PN结电容)

是影响最大的

VGSVTHN2

WhereKPnW L

➢ 当晶体管被夹断(pinchoff)时, 发生了什么? ➢ 增大 VDS 使耗尽区扩大到沟道中. ➢ 这导致ID 随 VDS 的增加而增大. 因此ID 可写为:

ID 2V G S V TH 21 N cV D S V D _ S Sat WhereKPnW L

➢ c 是非理想因子,它是考虑了随着漏极电压增加耗尽层加厚而造成的.

MOSFET I-V Characteristics(伏安特性)曲线

VGS:栅极和源极的电压差。 VDS: 漏极和源极的电压差。 ID : 流过漏极和源极的电流。 Vth: 器件的阈值电压,当VGS增加到一定的值时,栅极下面的P型 半导体会发生反型,形成N型半导体的沟道。此时D和S之间可以有 电流流过,这个特定的电压值,称之为值电压。

电容值的计算(了解)

Capacitance values are the same as Accumulation

Co

x

ox

TOX

and

CoxCo xWL

Capacitance is comprised of three components

C gb ox LT 2O LX D W C g dC g s oT xLO W D X CG W D CO G W SO

Area (poly)

54 18 11 aF/um2

Area (M1)

46 17 aF/um2

Area (M2)

49 aF/um2

Area (N+act.)

3599

aF/um2

Area (P+act.)

3415

aF/um2

Fringe (sub.) 249 261

aF/um

5、MOSFET的交流小信号模型(Analog Model for the MOSFET)

➢ 阈值电压可按下式计算:

V TH N m 2 sF Q b C o o Q s x s 2 q C o sN i x A 2 F V S B2 F

其中

ms = 栅和衬底的接触电势(contact potential between the gate and the bulk)

②,VGS>=Vthn时

由于电场的作用,P—SUB中的少量电子移动到了沟 道的顶部。这样就形成了一条电子移动的通道,如 果VDS>0,就会形成源漏电流IDS。

沟道夹断

2、阈值电压(Threshold Voltage)

➢ 阈值电压是当沟道反型时所需的电压 (i.e. 将沟道从p型变 到n型的电压).

截止区:

ID=0, VGS< Vth

线性区 (Linear):

IDVGSVTHN VDSV2D 2S

,VDS〈 VGS-Vth

饱和区 (Saturation):

ID 2V G S V TH 21 N cV D S V D _ S Sat WhereKPnW L

VDS >= VGS-Vth

Lmin、 Wmin和 tox 由工艺确定 Lmin: MOS工艺的特征尺寸(feature size)

决定MOSFET的速度和功耗等众多特性 L和W由设计者选定 通常选取L= Lmin,由此,设计者只需选取W W影响MOSFET的速度,决定电路驱动能力和功耗

① VGS〈Vthn时

下面的结构是N+PN+,耗尽层内是没有 自由移动的电荷的。D、S之间没有形成 一条电流通道,所以IDS=0。

VSB = 源到衬底的电势差(Source to bulk voltage)

对于一般工艺,Vtn= 0.83V(NMOS的阈值电压), Vtp= - 0.91V(PMOS的阈值电压),

阈值电压由工艺参数决定

3、MOSFET的 I-V 特性 (线性区Triode Region)

➢ 晶体管偏置在 VGS VTHN , 此时沟道已形成. ➢ 漏源电压 (VDS) 较小. ➢ 漏极电流可用下式表示:

以上各式中:

Eox: 氧化层的介电常数。

Tox: 氧化层的厚度。

Cox’ : 表示单位面积氧化层的电容值。

LD: 表示栅极和S、D重叠的宽度(由工艺精度决定)。

深亚微米CMOS IC工艺的寄生电容(数据)

Cap. N+Act.P+Act. Poly M1 M2 M3 Units

Area (sub.) 526 937 83 25 10 8 aF/um2

F = 衬底的静电势(electrostatic potential of the substrate) Q`bo = 耗尽区的电荷(charge in the depletion region) Q`ss = Si/SiO2 接触面的电荷(Si/Sicharge at the Si/SiO2

interface)

阈值电压(Threshold voltage): V TH N m 2 sF Q b C o o Q s x s 2 q C o sN i x A 2 F V S B2 F

对于一般工艺,Vtn=0.83V(NMOS的阈值电压), Vtp=-0.91V(PMOS的阈值电压), 阈值电压由工艺参数决定