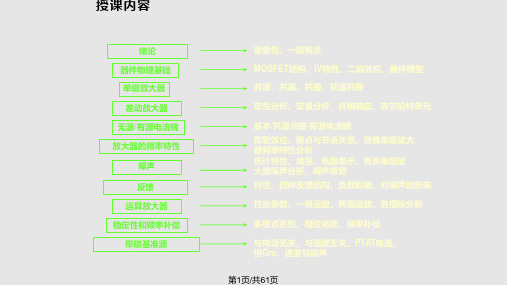

MOS电容仿真方法

功率场效应晶体管MOSFET特性试验研究及仿真 - 副本

3、纯电阻及阻感负载时,MOSFET开关特性的测试研究;

二、基本要求

1、学功率场效应晶体管MOSFET的有关参数的测定方法和工作原理,设计实验步骤,做线路搭接并进行实验研究。

2、实验数据整理、绘制曲线,对实验结果和理论结果进行对比分析。

3、使用MATLAB软件对各主电路进行仿真。

放大原理和主要参数辅以实验来化解和提高学习效率是研究场效应管行之有效的方法。但由于目前MOS场效应管的实验装置普遍存在弊端,即实验装置没有充分考虑到场效应管易损的因素,即实验者误操作、带电连接电路,造成实验中场效应管大量损坏,导致实验不能顺利完成,乃至正常开展。经调查,目前高校开展MOS场效应管测试实验的较少,无法深入甚至放弃。

场效应管是一种电压控制半导体器件,应用非常广泛。目前与我们的日常生活高度相关,如现代电子计算机、超大规模成电路、数码相机、开关电源、控制电路、液晶电视、数码音响、热释电传感器等就是以场效应管为基本器件构成和发展起来的。

MOS场效应管由于特殊的结构和工艺,其栅极与导电沟道没有电接触,即绝缘的,故它的输入电阻很高,可达109Ω以上,工作时几乎栅极不取电流,又栅-源极间电容非常小,极易受外界电磁场或静电的感应而带电,而少量电荷就可在极间电容上形成相当高的电压(U=Q/C),将管子损坏。通俗地说,MOS场效应管比较“娇气”。因此MOS场效应管出厂时各管脚都绞合在一起,或装在金属箔内,使G极与S极呈等电位,防止积累静电荷。管子不用时,全部引线也应短接。在测量时应格外小心,并采取相应的防静电感措施。

1、当需要进入实验室做毕设实验研究时,一定要遵守实验室学生守则。

2、不准在实验室内吸烟,喧哗、打闹等。不准在实验室内吃零食。

3、要爱护设备、仪器、仪表,轻拿轻放。旋钮使用不要用力过猛,防止机械性损坏;不要超量程扭动,以确保仪器、仪表等的完好和安全使用。

MOS结构电容-电压特性

MOS 结构高频C-V 特性测试MOS 结构电容-电压特性(简称C-V 特性)测量是检测MOS 器件制造工艺的重要手段。

它可以方便地确定二氧化硅层厚度ox d 、衬底掺杂浓度N 、氧化层中可动电荷面密度I Q 、和固定电荷面密度fc Q 等参数。

本实验目的是通过测量MOS 结构高频C-V 特性及偏压温度处理(简称BT 处理),确定ox d 、N 、I Q 和fc Q 等参数。

一、 实验原理MOS 结构如图1(a )所示,它类似于金属和介质形成的平板电容器。

但是,由于半导体中的电荷密度比金属中的小得多,所以充电电荷在半导体表面形成的空间电荷区有一定的厚度(—微米量级),而不像金属中那样,只集中在一薄层(—0.1nm )内。

半导体表面空间电荷区的厚度随偏压G V 而改变,所以MOS 电容是微分电容 GG dV dQ A C = (1) 式中G Q 是金属电极上的电荷面密度,A 是电极面积。

现在考虑理想MOS 结构。

所谓理想情形,是假设MOS 结构满足以下条件:(1)金属与半导体间功函数差为零;(2)2O S i 绝缘层内没有电荷;(3)2O S i 与半导体界面处不存在界面态。

偏压V G 一部分在降在2O S i 上,记作ox V ;一部分降在半导体表面空间电荷区,记作S V ,即S OX G V V V += (2)S V 又叫表面势。

考虑到半导体表面空间电荷区电荷和金属电极上的电荷数量相等、符号相反,有G SC Q Q = (3)式中SC Q 是半导体表面空间电荷区电荷面密度。

将式(2)、(3)代入式(1),S ox S ox Sox S ox G G G C C C C C C dV dV dQ A dV dQ A C +=+=+==111 (4) 式(4)表明MOS 电容由ox C 和S C 串联构成,其等效电路如图1(b )所示。

其中ox C 是以2O S i 为介质的氧化层电容,它的数值不随改变G V ;S C 是半导体表面空间区电容,其数值随G V 改变,因此oxro ox G ox d A dV dQ A C εε0== (5) S SC S dV dQ AC = (6) 式中ro ε是2O S i 相对介电常数。

模拟cmos集成电路设计拉扎维MOS器件物理基础PPT课件

第23页/共61页

跨导gm

VGS对IDS的控制能力 IDS对VGS变化的灵敏度

gm ID VGS VDS cons tant

• 直流关系式-I/V特性 • 交流关系式-小信号电路中的参数

第6页/共61页

MOS管简化模型

简化模型——开关 由VG控制的一个开关

第7页/共61页

MOS管的结构

Bulk(body)

源漏在物理结构上是完全对称的,靠什么区分开?

提供载流子的端口为源,收集载流子的端口为漏

最重要的工作区域?

受VG控制的沟道区

• 小信号模型 • 信号相对于偏置工作点而言比较小、不会显著影响偏置工作点时用该模型简化计算 • 由gm、 gmb、rO等构成低频小信号模型,高频时还需加上 CGS等寄生电容、寄生电阻(接触孔电阻、 导电层电阻等)

沟道电荷的产生

当VG大到一定 程度时,表面势 使电子从源流向 沟道区 VTH定义为表面电 子浓度等于衬底 多子浓度时的VG

第12页/共61页

阈值电压

0 栅与衬底功函数差

COX

OX

TOX

常通过沟道注入把VTH0调节到合适值 工艺确定后,VTH0就固定了,设计者无法改变

第13页/共61页

I/V特性-沟道随VDS的变化

第3页/共61页

掌握器件物理知识的必要性

• 数字电路设计师一般不需要进入器件内部,只把它当开关用即可 • AIC设计师必须进入器件内部,具备器件物理知识

• MOS管是AIC的基本元件 • MOS管的电特性与器件内部的物理机制密切相关,设计时需将两者结

第4讲 MOS管的电容和讲解

VGS<0

B

堆积状态的等效电容

主要的电容Cgb串联了一个较大的电阻

G

Cgs

Cgb

Cgd

gnd

耗尽状态

VGS不是足够“负”,也不是足够“正”,栅氧化层下 方自由电子或空穴浓度都很低,下极板情况复杂,电容 随电压变化。 +

B S VGS G 少量数目电子 D

FOXP+Fra bibliotekFOX

N+ 耗尽层

N+ 耗尽层与栅氧 化电容C串联

Cgd 漏

Cdb 栅 Csb Cgb Cgs 体

源

任何两极之间存在电容

作为电容使用的MOS管特性

R R

v S

G B D

v

C

在没有好的多晶电容的工艺中,常使用MOS管(栅) 作为电容。

堆积状态

当VGS<0时,空穴被吸附(堆积)到栅氧化层下 方,相当于电容的一个极板(另一个极板为多晶)。

S Cgs FOX P+ FOX N+ Ldiff P衬底 衬底电阻 堆积的空穴 + Cgd G D Cgd N+ Ldiff FOX

PMOS管输入输出特性曲线

阈值电压测量

有多种工程定义:本课程采用“输入特性曲线斜 率变化最大的点对应的电压”。

输出特性曲线

VGS=5V

线性区 饱和区

VGS=4V

VGS=3V

VGS=2V VGS=1V

线性区和饱和区的实验划分方法

线性区 饱和区

统一为:输出特性曲线中斜率变化最大的点。

一些概念问题

Cox

TOX是栅氧化层厚度

ox

TOX

栅极电容与MOS管的WL乘积成正比

第五章-电路仿真

18

第二节SIM99中的激励源描述

一、直流源 在库Simulation Symbols.Lib中包含 了如下的直流源元件。 (1)VSRC:电压源。 (2)ISRC:电流源。

19

电压/电流源符号 二、正弦仿真源 在库Simulation Symbols.Lib中包含了 如下的正弦源元件。

20

正弦电压/电流源符号 三、其他激励源 在库Simulation Symbols.Lib中包 含的其他激励源有:

38

半波整流电路原理图

39

本电路为一个半波整流电路,输入为 一正弦波的电压源,电压源参数设置如下 设置,经整流滤波后,输出Vhw为一恒压直 流电压。在添加正弦波电压源时,按 “Tab”键修改属性,设置如下对话框。

40

参数设置对话框

41

AC小信号分析电压 信号振幅 叠加正弦信号上的 直流电压

忽略不用的直流参数

压控振荡源元件

26

第三节仿真器的设置

在进行仿真前,设计者必须确定对电 路进行哪种分析,要收集哪个变量数据, 以及仿真完成后要自动显示哪个变量的波 形等。

27

一、进入分析主菜单 1、单击Simulate Setup命令,进入 仿真器的设置。 2、单击Setup选项,将启动仿真器设置 对话框,在General选项中,设计者 可以选择分析类别,如图所示。

仿真后波形

分析仿真结果

电路仿真的一般流程

30

1、编辑原理图

(1) 在编辑原理图过程中,除了导线、 电源符号、接地符号外,原理图中所有元 件都要取自仿真库(Sim.ddb)。否则在仿 真时,因找不到元件参数而给出错误提示并 终止仿真过程。

31

(2)在放置元件操作过程中,元件未固定 前,需按下“Tab”键进入元件属性设置窗 (元件固定后,双击元件同样也会激活属 性设置窗),在分别单击“Attributes”、 Part Fields 等属性窗标签,设置元件的 仿真参数。

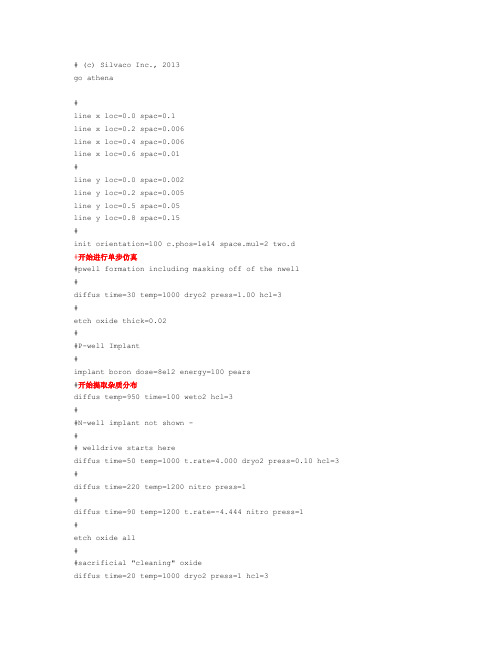

实验四:MOSFET工艺器件仿真(7-8次实验)

# (c) Silvaco Inc., 2013go athena#line x loc=0.0 spac=0.1line x loc=0.2 spac=0.006line x loc=0.4 spac=0.006line x loc=0.6 spac=0.01#line y loc=0.0 spac=0.002line y loc=0.2 spac=0.005line y loc=0.5 spac=0.05line y loc=0.8 spac=0.15#init orientation=100 c.phos=1e14 space.mul=2 two.d#开始进行单步仿真#pwell formation including masking off of the nwell#diffus time=30 temp=1000 dryo2 press=1.00 hcl=3#etch oxide thick=0.02##P-well Implant#implant boron dose=8e12 energy=100 pears#开始提取杂质分布diffus temp=950 time=100 weto2 hcl=3##N-well implant not shown -## welldrive starts herediffus time=50 temp=1000 t.rate=4.000 dryo2 press=0.10 hcl=3 #diffus time=220 temp=1200 nitro press=1#diffus time=90 temp=1200 t.rate=-4.444 nitro press=1#etch oxide all##sacrificial "cleaning" oxidediffus time=20 temp=1000 dryo2 press=1 hcl=3etch oxide all##gate oxide grown here:-diffus time=11 temp=925 dryo2 press=1.00 hcl=3## Extract a design parameterextract name="gateox" thickness oxide mat.occno=1 x.val=0.05##vt adjust implantimplant boron dose=9.5e11 energy=10 pearson#depo poly thick=0.2 divi=10##from now on the situation is 2-D#etch poly left p1.x=0.35#method fermi compressdiffuse time=3 temp=900 weto2 press=1.0#implant phosphor dose=3.0e13 energy=20 pearson#depo oxide thick=0.120 divisions=8#etch oxide dry thick=0.120#implant arsenic dose=5.0e15 energy=50 pearson#method fermi compressdiffuse time=1 temp=900 nitro press=1.0## pattern s/d contact metaletch oxide left p1.x=0.2deposit alumin thick=0.03 divi=2etch alumin right p1.x=0.18# Extract design parameters# extract final S/D Xjextract name="nxj" xj silicon mat.occno=1 x.val=0.1 junc.occno=1# extract the N++ regions sheet resistanceextract name="n++ sheet rho" sheet.res material="Silicon" mat.occno=1 x.val=0.05 region.occno=1# extract the sheet rho under the spacer, of the LDD regionextract name="ldd sheet rho" sheet.res material="Silicon" \mat.occno=1 x.val=0.3 region.occno=1# extract the surface conc under the channel.extract name="chan surf conc" surf.conc impurity="Net Doping" \material="Silicon" mat.occno=1 x.val=0.45# extract a curve of conductance versus bias.extract start material="Polysilicon" mat.occno=1 \bias=0.0 bias.step=0.2 bias.stop=2 x.val=0.45extract done name="sheet cond v bias" \curve(bias,1dn.conduct material="Silicon" mat.occno=1 region.occno=1)\outfile="extract.dat"# extract the long chan Vtextract name="n1dvt" 1dvt ntype vb=0.0 qss=1e10 x.val=0.49structure mirror rightelectrode name=gate x=0.5 y=0.1electrode name=source x=0.1electrode name=drain x=1.1electrode name=substrate backsidestructure outfile=mos1ex01_0.str# plot the structuretonyplot mos1ex01_0.str -set mos1ex01_0.set############# Vt Test : Returns Vt, Beta and Theta ################go atlas# set material modelsmodels cvt srh printcontact name=gate n.polyinterface qf=3e10method newtonsolve init# Bias the drainsolve vdrain=0.1# Ramp the gatelog outf=mos1ex01_1.log mastersolve vgate=0 vstep=0.25 vfinal=3.0 name=gatesave outf=mos1ex01_1.str# plot resultstonyplot mos1ex01_1.log -set mos1ex01_1_log.set# extract device parametersextract name="nvt" (xintercept(maxslope(curve(abs(v."gate"),abs(i."drain")))) \ - abs(ave(v."drain"))/2.0)extract name="nbeta" slope(maxslope(curve(abs(v."gate"),abs(i."drain")))) \ * (1.0/abs(ave(v."drain")))extract name="ntheta" ((max(abs(v."drain")) * $"nbeta")/max(abs(i."drain"))) \ - (1.0 / (max(abs(v."gate")) - ($"nvt")))quit1、画出结构图,进行单步仿真,代码翻译(第7次实验)2、对比实验(第8次实验)注意:对比仿真时只能改变一个参数,其它参数要恢复到参考代码原始值。

ASIC课程设计——MOS输出级电路设计与Hspice仿真

ASIC课程设计——MOS输出级电路设计与Hspice仿真————————————————————————————————作者:————————————————————————————————日期:目录一.背景介绍 (1)二.设计要求与任务 (2)三.电路原理及设计方法 (2)1.电阻负载共源级放大器电路原理分析 (3)2.有源负载共源放大器设计方法 (5)四.HSpice软件环境概述 (7)1.简介 (7)2.特点 (8)3.界面预览 (8)五.设计过程 (10)六.结果和讨论 (11)七.设计心得 (12)八.库文件程序附录 (13)一.背景介绍ASIC是Application Specific Integrated Circuit的英文缩写,在集成电路界被认为是一种为专门目的而设计的集成电路。

ASIC的设计方法和手段经历了几十年的发展演变,从最初的全手工设计已经发展到现在先进的可以全自动实现的过程。

在集成电路界ASIC被认为是一种为专门目的而设计的集成电路。

是指应特定用户要求和特定电子系统的需要而设计、制造的集成电路。

ASIC的特点是面向特定用户的需求,ASIC在批量生产时与通用集成电路相比具有体积更小、功耗更低、可靠性提高、性能提高、保密性增强、成本降低等优点。

ASIC分为全定制和半定制。

全定制设计需要设计者完成所有电路的设计,因此需要大量人力物力,灵活性好但开发效率低下。

如果设计较为理想,全定制能够比半定制的ASIC芯片运行速度更快。

半定制使用库里的标准逻辑单元(Standard Cell),设计时可以从标准逻辑单元库中选择SSI(门电路)、MSI(如加法器、比较器等)、数据通路(如ALU、存储器、总线等)、存储器甚至系统级模块(如乘法器、微控制器等)和IP核,这些逻辑单元已经布局完毕,而且设计得较为可靠,设计者可以较方便地完成系统设计。

现代ASIC常包含整个32-bit处理器,类似ROM、RAM、EEPROM、Flash的存储单元和其他模块. 这样的ASIC常被称为SoC(片上系统)。

MOS器件建模及仿真 ppt课件

IC设计

(DC、AC及瞬态分析)

● MOSFET模型

器件模型是通过I-V, C-V以及器件中载流子输运过程 描述器件的端特性,这些模型应能够反映器件在所有 工作区域的特性. 分为物理模型和等效电路模型。

▲ 器件物理模型 根据器件的几何图形、掺杂分布、载流子输运方程和材

料特性等预测器件的端特性和输运特性. 特点:1)通常需要二维或三维的数值计算;

2)能揭示器件的内在物理效应; 3)一般只适用于器件物理研究和器件开发; 4)部分工作区能找到收敛的解析模型,可应用于电 路模拟器.

▲ 等效电路模型 将器件等效成由一些基本单元组成的电路,器件特性由

该等效电路特性来描述. 特点:1)可解析求解;

2)不能揭示器件的内在物理效应; 3)适合于电路模拟器.

p

x

● MOSFET结构和工作原理

1、MOSFET的基本结构

2 、MOSFET的工作原理

VGS来控制沟道的导电性,从而 控制漏极电流 ID ,是一种电压 控制型器件.

当 VGS<VT(称为阈值电压)时,源漏之间隔着P区,漏结反偏, 故无漏极电流.当VGS >VT 时,栅下的P型硅表面发生强反型,形成 连通源区和漏区的N型沟道,产生漏极电流ID. 对于恒定VDS ,VGS 越大,则沟道中的可移动电子就越多,沟道电阻就越小,ID 就越大.

p t

1 q

Jp

R

上式中,R = U - G ,U、G 、R 分别为复合率、产生率和净

复合率。R > 0 表示净复合,R < 0 表示净产生。

③ 电子与 空穴的电流密度方程:

Jn qDnn qnn J p qDpp q p p