FPGA高速串行收发器,GTP,GTX

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_#用户IO引脚XX代表某个Bank内唯一得一对引脚,Y=[P|N]代表对上升沿还就是下降沿敏感,#代表bank号2.IO_LXXY_ZZZ_#多功能引脚ZZZ代表在用户IO得基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚.D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0就是数据得最低位,在Bit—serial模式下,DIN就是信号数据得输入;在SPI模式下,MISO就是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1就是SPI总线得第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1与D2就是数据总线得低位;在SPI*4模式下,MISO2与MISO3就是SPI总线得MSBs.An:O,A[25:0]为BPI模式得地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式得状态输出引脚。

SUSPEND就是一个专用引脚,AW A KE就是一个多功能引脚。

除非SUSPEND模式被使能,AW AKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B就是一个低电平有效得片选信号;在SPI*2或者SPI*4得模式下,MISO0就是SPI总线得第一位数据。

FCS_B:O,BPI flash 得片选信号.FOE_B:O,BPI flash得输出使能信号FWE_B:O,BPIflash 得写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

Xilinx FPGA 引脚功能详细介绍

XilinxFPGA引脚功能详细介绍注:技术交流用,希望对大家有所帮助。

IO_LXXY_# 用户IO引脚XX代表某个Bank内唯一的一对引脚,Y=[P|N]代表对上升沿还是下降沿敏感,#代表bank 号2.IO_LXXY_ZZZ_# 多功能引脚ZZZ代表在用户IO的基本上添加一个或多个以下功能。

Dn:I/O(在readback期间),在selectMAP或者BPI模式下,D[15:0]配置为数据口。

在从SelectMAP读反馈期间,如果RDWR_B=1,则这些引脚变成输出口。

配置完成后,这些引脚又作为普通用户引脚。

D0_DIN_MISO_MISO1:I,在并口模式(SelectMAP/BPI)下,D0是数据的最低位,在Bit-serial模式下,DIN是信号数据的输入;在SPI模式下,MISO是主输入或者从输出;在SPI*2或者SPI*4模式下,MISO1是SPI总线的第二位。

D1_MISO2,D2_MISO3:I,在并口模式下,D1和D2是数据总线的低位;在SPI*4模式下,MISO2和MISO3是SPI总线的MSBs。

An:O,A[25:0]为BPI模式的地址位。

配置完成后,变为用户I/O口。

AWAKE:O,电源保存挂起模式的状态输出引脚。

SUSPEND是一个专用引脚,AWAKE是一个多功能引脚。

除非SUSPEND模式被使能,AWAKE被用作用户I/O。

MOSI_CSI_B_MISO0:I/O,在SPI模式下,主输出或者从输入;在SelectMAP模式下,CSI_B是一个低电平有效的片选信号;在SPI*2或者SPI*4的模式下,MISO0是SPI总线的第一位数据。

FCS_B:O,BPI flash 的片选信号。

FOE_B:O,BPI flash的输出使能信号FWE_B:O,BPI flash 的写使用信号LDC:O,BPI模式配置期间为低电平HDC:O,BPI模式配置期间为高电平CSO_B:O,在并口模式下,工具链片选信号。

fpga间gtx原理

fpga间gtx原理FPGA是现代计算机系统中一种重要的可编程逻辑设备,而GTX则是一种高速串行收发器。

本文将探讨FPGA与GTX之间的原理和关联。

我们来了解一下FPGA的基本概念。

FPGA全称为Field-Programmable Gate Array,即现场可编程门阵列。

它是一种可编程逻辑器件,可以在制造完成后进行现场编程。

FPGA内部由大量的逻辑单元和可编程的连线网络组成,可以实现各种数字电路的功能。

GTX是NVIDIA公司开发的高速串行收发器。

它是一种用于高速数据传输的接口技术,可以实现数据在设备之间的快速传输。

GTX被广泛应用于高性能计算、数据中心和通信领域。

FPGA与GTX之间存在紧密的关系,主要体现在以下几个方面。

FPGA可以通过GTX接口与其他设备进行高速数据通信。

由于GTX 采用了串行传输方式,可以在保证数据传输速率的同时,减少传输线的数量,提高系统的可靠性和稳定性。

FPGA通过配置GTX接口,可以与其他设备进行高速数据交换,满足实时数据处理和传输的需求。

FPGA内部的逻辑单元可以通过GTX接口与外部设备进行通信。

FPGA中的逻辑单元可以实现各种功能,如数据处理、算法运算等。

通过配置GTX接口,FPGA可以将处理结果传输给外部设备,或者接收外部设备的数据输入,实现与外部设备的交互。

FPGA还可以通过GTX接口与其他FPGA进行通信。

在某些应用场景下,需要多个FPGA之间进行数据交换和协同计算。

通过配置GTX接口,多个FPGA可以通过高速串行通信进行数据传输,实现分布式计算和并行处理。

需要注意的是,FPGA与GTX之间的通信需要遵循一定的协议。

GTX接口支持多种通信协议,如PCI Express、Ethernet等。

在设计FPGA与GTX接口时,需要根据具体的应用需求选择合适的通信协议,并进行相应的配置和调试。

总的来说,FPGA与GTX之间的原理是通过配置GTX接口实现高速数据通信和交互。

Xilinx_7_Series_GTX简介

GTX transceivers

QPLL和CPLL

适用范围: CPLL: 1.6Ghz-3.3Ghz QPLL: 5.9Ghz-12.5Ghz QPLL可以输出频率更高、 抖动更小的时钟,CPLL允 许对每个通道的时钟进行 灵活的配置。可以通过 SYSCLKSEL来选择使用 CPLL或者是QPLL,并且 支持动态切换。

GTX transceivers

主要内容

GTX简介 发送通道的结构

接收通道的结构

GTX的应用

GTX transceivers

GTX简介

发送通道的结构 接收通道的结构

GTX的应用

GTX transceivers

GTX是一种低功耗的吉比特收发器,配置灵活,功能强大,与FPGA内部其他逻 辑紧密联系,可用于实现多种高速串行接口(如PCIE、SATA等)。GTX发送和接收方向 均由PCS和PMA两部分组成。GTX还提供动态重配置接口,用于动态修改GTX的配置。 Group 8B/10B编解码 64B/66B编解码 Feature 内部数据宽度可以设置成2byte或4byte以支持不同的数据速率

② Near-End PMA Loopback

③ Far-End PMA Loopback ④ Far-End PCS Loopback

GTX transceivers

GTX简介

发送通道的结构 接收通道的结构

SATA应用中GTX时钟方案

GTX transceivers

Xilinx FPGA高速资源合理利用的一种思路

电子技术与软件工程Electronic Technology & Software Engineering网络通信技术Network Com m unication TechnologyXilinx F P G A高速资源合理利用的一种思路杨见1陈伟1许杰2陈少林2(1.四川九洲空管科技有限责任公司四川省绵阳市621000 2.空装驻綿阳地区某军事代表室四川省綿阳市621000 )摘要:本文主要结合实际工程案例,遵照X ilin x高速收发器使用规则,对如何充分利用其硬件资源进行高速应用设计,提出一种 相对于常规设计思路更为合理的方式。

关键词:FPG A;高速资源;X ilin x高速收发器随着CML(CurrentModeLogic)、CDR、8b l0b 编码/64b66b 编码技术、预加重/去加重、时钟补偿等技术的出现,能够极大地 减小时钟抖动、收发时钟频偏、信号衰减和线路噪声对接收性能的 影响,从而使高速串行传输方式得到极为广泛的应用,而其接口信 号线数量少、应用成本低等优点,更是让开发人员相比并行数据传 输接口而言,更愿意选择高速串行传输方式。

Xilinx FPGA集成了 可实现不同线速率的高速串行收发器硬核资源,开发人员只需要进 行简单的配置即可实现高速串行应用。

基于成本考虑,在工程应用 中,开发人员依然遵循通过调用尽量少的资源去完成足够多的功能 这一准则展开设计。

本文就针对这一点对Xilinx FPGA高速串行资 源的利用提出一种设计思路进行分析并验证。

1设计需求QUAD116搭建4条常规的10G高速链路与目标设备三通信,QUAD115搭建3条10G高速链路与目标设备二通信,以及一条 千兆网链路与目标设备一通信。

链路设计要求如图1所示。

2设计思路Xilinx 7系列G T X每四个Channel组合成一个QUAD,每个 Q UAD有两组参考时钟输入,一个QPLL,4个CPLL,CPLL输出 时钟频率最高3.125Ghz,通信链路线速率最高6.25Gbps,QPLL输出时钟频率则在5.93Ghz〜12.5G h z范围内。

GTX技术——精选推荐

GTX技术你应该知道点⾼速GTX技术eSATA接⼝只有⼏根线为什么那么快?连上⽹线显⽰的1Gbps是不是很令⼈兴奋!没错他们都⽤了⾼速GTX技术,GTX全称为Gigabit Transceiver即吉bit收发器,是为了满⾜现代数字处理技术和计算技术庞⼤数据的⾼速、实时的传输,⽬前主要应⽤在⽚间通信(两⽚FPGA之间,FPGA与DSP之间等)、板间通信(电脑主板与交换机,硬盘与主板等)等。

传统的并并⾏传输技术存在抗⼲扰能⼒低,同步能⼒差,传输速率低和信号质量差等问题。

GTX⽬前的线速度范围为1Gbps~12Gbps,有效负载范围为0.8Gbps~10Gbps,⽬前GTX已经应⽤于光纤通道(FC),PCI Express,RapidIO,串⾏ATA,千兆以太⽹,万兆以太⽹等,GTX技术已经充斥我们周围很久了,作为⼀个技术⼈员,你是不是该知道点关于⾼速GTX呢?。

本⽂引⽤地址:/article/246023.htm GTX线路实现 GTX收发器采⽤的是差分信号对数据进⾏传输,其中LVDS(Low Voltage Different Signal)和CML(Current Mode Logic)是常⽤的两种差分信号标准。

在普通单⽚机(如51单⽚机中)不包含差分接⼝,均是以地作为参考,差分信号时有两根⼏乎完全相同的线路来组成⼀对等值、反相信号,接收端通过⽐较两端电压差值来确定传输的是“0”还是“1”,如果正参考电压⽐负参考电压低,则信号为⾼;如果负参考⽐正参考电压⾼,则信号为低。

因为线路上受到的噪声⼲扰⼏乎完全相同,在计算差值时相减从⽽达到抵消的效果,这就使得差分信号抗⼲扰能⼒特别强,⾼速传输时不易出错。

如图1所⽰为差分信号传输模式。

图 1 差分传输 除了利⽤差分信号外,GTX采⽤⾃同步技术来解决时钟同步问题。

⽬前常⽤同步⽅式有系统同步,源同步和⾃同步。

三种同步⽅式的结构如图2所⽰。

系统同步利⽤⽚外的晶振进⾏同步,由于板间线路的长度不⼀致,以及⽚内延迟不⼀致,在时钟速度较⾼时可能存在较⼤误差。

Xilinx不同FPGA集成的GTx及性能

10 Gb Attachment Unit Interface (XAUI), Reduced Pin eXtended Attachment Unit Interface (RXAUI), 100 Gb Attachment Unit Interface (CAUI), 40 Gb Attachment Unit Interface (XLAUI); Common Packet Radio Interface (CPRI™)/Open Base StaTIon ; Architecture IniTIaTIve (OBSAI); OC-48/192; OTU-1, OTU-2, OTU-3, OTU-4; Serial RapidIO (SRIO); Serial Advanced Technology Attachment (SATA)/Serial Attached SCSI (SAS); Serial Digital Interface (SDI); SFF-8431 (SFP+)。 GTx 收发器采用的是差分信号对数据进行传输,其中 LVDS(Low Voltage Different Signal)和 CML(Current Mode Logic)是常用的两种差分信号标准。

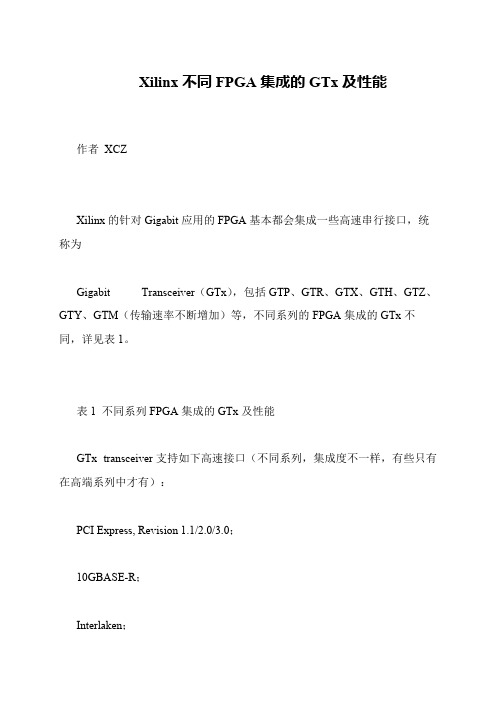

Xilinx 不同 FPGA 集成的 GTx 及性能

作者 XCZ

Xilinx 的针对 Gigabit 应用的 FPGA 基本都会集成一些高速串行接口,统

称为

Gigabit

Transceiver(GTx),包括 GTP、GTR、GTX、GTH、GTZ、

GTY、GTM(传输速率不断增加)等,不同系列的 FPGA 集成的 GTx 不

同,详见表 1。

表 1 不同系列 FPGA 集成的 GTx 及性能

vivado中各个资源模块的意思

vivado中各个资源模块的意思Vivado是Xilinx公司推出的一款集成设计环境,广泛应用于数字信号处理、数字逻辑设计等领域。

在使用Vivado进行FPGA设计时,了解各个资源模块的含义对于高效利用FPGA内部资源具有重要意义。

本文将详细介绍Vivado中各个资源模块的意思,帮助您更好地进行FPGA设计。

一、逻辑资源模块1.LUT(查找表):LUT是FPGA中基本的逻辑资源,可以用来实现组合逻辑或时序逻辑。

在Vivado中,LUT可以配置为不同大小的查找表,如6输入LUT、5输入LUT等。

2.FF(触发器):触发器是实现时序逻辑的基本单元。

在Vivado中,触发器可以配置为D触发器、T触发器等。

3.Carry Chain(进位链):进位链用于实现算术逻辑单元(ALU)中的加法器、减法器等。

在Vivado中,进位链可以提高运算速度和资源利用率。

二、存储资源模块1.Block RAM(块RAM):块RAM是FPGA中的存储资源,可用于实现数据存储、缓存等功能。

Vivado支持不同大小的块RAM配置,如18K、36K 等。

2.Distributed RAM(分布式RAM):分布式RAM是一种较小的存储资源,可用于实现小型缓存、寄存器等功能。

与块RAM相比,分布式RAM的访问速度更快,但容量较小。

三、数字信号处理资源模块1.DSP48(数字信号处理单元):DSP48是FPGA中用于实现数字信号处理功能的资源。

在Vivado中,DSP48可以配置为乘法器、累加器、滤波器等。

2.FFT(快速傅里叶变换):FFT是数字信号处理中常用的算法,Vivado提供了FFT IP核,方便用户在FPGA上实现高速的FFT运算。

四、时钟资源模块1.PLL(锁相环):锁相环是FPGA中的时钟管理资源,用于生成、分频、倍频等时钟信号。

Vivado提供了丰富的PLL IP核,以满足不同设计需求。

2.MMCM(混合模式时钟管理):MMCM是FPGA中的一种高级时钟管理资源,具有更低的相位噪声和更高的频率稳定性。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

第1节高速数据连接功能简介10.1.1 高速数据传输的背景由于现代通信以及各类多媒体技术对带宽的需求迅猛增长,促使一系列基于差分、源同步、时钟数据恢复(clock and data recovery,CDR)等先进技术的互连方式应运而生。

在传统设计中,单端互连方式易受干扰、噪声的影响,传输速率最高只能达到200~250Mbps/Line;在更高速率的接口设计中,多采用包含有源同步时钟的差分串行传输方式(如LVDS、LVPECL等),但在传输过程中时钟与数据分别发送,传输过程中各信号瞬时抖动不一致,破坏了接收数据与时钟之间的定时关系,因而传输速率很难超越1Gbps/通道。

因此迫切需要新的高速数据传输技术。

在目前系统级互连速率已达到Gbps的设计中,先进的高速串行技术迅速取代传统的并行技术,成为业界的主流。

高速串行技术不仅能够带来更高的性能、更低的成本和更简化的设计,克服了并行的速度瓶颈,还节省了I/O资源,使印制板的布线更简单。

因此,被越来越广泛地应用于各种系统设计中,包括PC、消费电子、海量存储器、服务器、通信网络、工业计算和控制、测试设备等。

高速串行传输一般采用差分线,迄今业界已经发展出了多种串行系统接口标准,例如千兆以太网、万兆以太网、PCI-Express、串行RapidIO、串行ATA 等。

10.1.2 Xilinx公司高速连接功能的解决方案基于高速的需求和传统技术的弊端,Xilinx公司在Virtex 2 Pro以及更高系列的部分FPGA部集成了能实现高速数据收发Rocket I/O模块,采用了CML(CurrentMode Logic)、CDR、线路编码(8B/10B)和预加重等技术的Rocket I/O硬核模块,可极减小时钟扭曲、信号衰减和线路噪声对接收性能的影响,从而使传输速率进一步提高,最高可达10Gbps以上,可用于实现吉比特以太网、PCI-Express等常用接口。

除了底层的物理层技术,Xilinx还提供带32 bit LocalLink用户接口的Aurora协议引擎参考设计。

Aurora 协议是为私有上层协议或标准上层协议提供透明接口的串行互连协议,它允许任何数据分组通过Aurora协议封装,并在芯片间电路板间甚至机箱间传输。

Aurora链路层协议在物理层采用千兆位串行技术,每物理通道的传输波特率可从622Mbps扩展到3.125 Gbps。

Aurora还可将1至16个物理通道绑定在一起,形成一个16个通道绑定而成的虚拟链路,可提供50Gbps的传输波特率和最大40Gbps的全双工数据传输速率。

Aurora可支持广泛的应用围,如:路由器和交换机、远程接入交换机、HDTV广播系统、分布式服务器和存储子系统。

在协议中,每个高速串行被称为“弄”。

协议引擎通过与高速收发器配合,可创建带LocalLink用户接口逻辑的串并、并串收发器。

通过这一串行接口方案,用户无须自己设计有关串行接口所涉及的编解码、同步、速率匹配等问题。

用户接口部分包含了所有必要的信号,如协议引擎的状态信号等。

Xilinx通过高品质的技术支持材料来支持其先进的芯片产品,这些材料包括广泛的知识产权核、参考设计、模拟电路模块、信号完整性(SI)设计套件、数字仿真的质量行为模型等。

此外,Xilinx还提供了众多设计服务、开发平台以及最佳的FPGA实现工具,可确保用户的所有设计需求都能获得最佳产品和技术支持。

第2节实现吉比特高速串行I/O的相关技术10.2.1 吉比特高速串行I/O的特点和应用吉比特收发器(MGT)是吉比特级串行器/解串器(SERDES)的别名。

1.优点1)速度高。

高速串行I/O的线速可超过吉比特,甚至数十吉位。

而并行传输线速不可能超越吉比特。

吉比特串行I/O的主要优势是速度。

在从片/片外、板/板外或盒/盒外获取数据时,没有任何技术可以超越高速串行链路。

高速串行链路的线速围为1Gb/s~ 12Gb/s,有效负载围为0.8Gb~10Gb。

2)节省管脚数。

将大量数据传入/出芯片或电路板时所遇到的第一个问题是引脚数,电路板设计时间和成本会随着管脚数的增加而急剧增加。

在大数据量应用下,串行I/O可节省大量的管脚(在低速以及小数据量应用中,MGT比传统并行模式需要更多的电源和接地引脚)。

3)简化同步转换输出。

采用单端并行总线时,设计者应考虑同步转换输出(SSO,即大量寄存器的值在某一时刻同时翻转,会对电源和地平面产生一定的影响,甚至影响到器件部时钟和逻辑的正常工作)。

如果出现太多的同步转换,触地反弹会产生大量噪声。

设计者还可以在所有I/O上都使用差分信号处理技术,以此来消除SSO问题,但是这样做就会使引脚数翻倍。

如果数据流需求比较适中,设计者可以使用具有适当引脚数的并行接口。

4)EMI指标优。

经验表明:时钟越快,放射测试就越难进行,因此,吉比特设计的EMI测试看起来是不可能实现的。

但是,通常高速串行链路的辐射量比以较低速度工作的大型总线低。

这是因为运行时的吉比特链路需要出色的信号完整性,正如经典论断“辐射问题实际上就是信号完整性问题”所言,因此吉比特串行IO具有更好的EMI指标。

5)成本低。

采用MGT通常会降低系统总成本。

连接器采用较小、较经济的封装时,引脚数较少,电路板设计也更简单。

6)预设协议。

采用MGT的另一个好处是可以使用预先定义好的协议和接口标准。

如Xilinx提供了从Aurora到XAUI的多种协议,满足不同的用户需求。

2.缺点吉比特高速串行I/O的最大缺点在于对信号完整性的严格要求。

而且,阻抗控制的PC(印刷电路)板、高速连接器和电缆的费用较高。

因此,必须处理数字仿真中的复杂性和时基较小的问题。

并且,在利用预设协议的时候,必须为集成过程计划时间,以及为协议的开销安排额外的逻辑电路或CPU时钟周期。

3.应用围起初,吉比特级串行器/解串器(SERDES)仅局限于用在电信行业和少数缝隙市场(如广播视频)。

如今,MGT应用出现在电子行业的各个角落——军事、医疗、网络、视频、通信等等。

MGT也可以用于背板或机箱之间的PCB上。

对于电子行业的发展前景而言,MGT至关重要。

下面是采用吉比特级SERDES的行业标准示例。

•光纤通道(FC)•PCI Express•RapidIO串行•先进的交换互连(Advanced Switching Interface)•串行ATA•1Gb以太网•10Gb以太网(XAUI)•Infiniband 1X、4X、12X吉比特级通信似乎强加了一些苛刻限制。

串行设计者必须考虑信号完整性、较小的时基以及可能出现的对额外门电路和CPU周期的需求。

但是,在盒间以及芯片间通信中采用吉比特级技术的优势远远超过了那些可以察觉到的缺点。

例如:高速、引脚数少、低EMI和低成本等,这些都使它成为了众多高速设计的理想之选,并保证了其在未来通信系统中得到广泛的使用。

10.2.2 吉比特串行I/O系统的组成吉比特串行传输是一种通用的传输标准,虽然不同FPGA厂家的模块和组件名不同,但其关键技术都具备下列共同点。

1.系统整体结构吉比特串行传输的系统整体结构如图10-1所示。

下面对其中的主要模块进行简要介绍。

图10-1 吉比特高速串行I/O的系统结构示意图串行器:将速率为y的n位宽并行数据转变成速率为n*y的串行数据。

解串器:将速率为n*y的串行数据转变成速率为y的n位宽并行数据。

Rx(接收)对齐:将接收的数据对齐到合适的字边界。

可以使用不同的方法,从自动检测和对齐特殊的预留比特序列(通常也称作comma字符),到用户控制的比特调整。

时钟管理器:管理各种时钟操作,包括时钟倍频,时钟分频,时钟恢复。

发送FIFO(先进先出):在输入数据发送之前,暂时保存数据。

接收FIFO:在接收数据被提取之前,暂时保存数据。

在需要时钟修正的系统中,接收FIFO是必须的。

接收线路接口:模拟接收电路,包括差分接收器,还可能包括有源或者无源均衡电路。

发送线路接口:模拟发送电路,可以支持多种驱动负荷。

通常还带有转换的预加重部分。

线路编码器:将数据编码成适应不同线路的格式。

编码器通常会消除长的无转变位的序列,同时还可以平衡数据中0、1的出现次数。

需要注意的是,线路编码器是一个可选模块,某些SERDES可能没有。

线路译码器:将线路上的编码数据分解成原始数据。

(这是一个可选模块,编码可能在SERDES外完成)。

时钟修正和通道绑定:修正发送时钟和接收时钟之间的偏差,同时也可实现多通道间的歪斜修正。

(通道绑定是可选的,并不一定包含在SERDES中)。

其他可能包括的功能模块有:循环冗余检测(CRC)码生成器、CRC检测器、多种编码和解码(4b/5b、8b/10b、64b/66b)、可调的扰码器、各种对齐和菊花链选项、可配置的时钟前端和后端以及不同等级的自环。

2.参考时钟的要求1)时钟精度吉比特级收发器的输入时钟、或是参考时钟的规格定义是非常严格的。

其中包含非常严格的频率要求,通常用每百万次容许频率错误的单位PPM来定义。

抖动要求也是十分严格的,通常用时间(皮秒)或者时间间隔(UI)定义。

下面给出这些相关定义。

•PPM:百万分之一;用来描述非常小的比率。

•UI:时间间隔;等价于一个符号的时间长度,例如:0.2UI = 20%的符号时间。

•抖动:理想传输位置的偏差。

如此严格的规定才使得PLL和时钟提取电路能够正常工作。

通常系统的每一个印刷电路板都需要有一个精确石英晶体振荡器供MGT使用。

这些晶体振荡器的精确度比大多数用在数字系统中的晶体振荡器要高一个级别,而且价格也要高出一截。

很多情况下,一般的时钟发生芯片和PLL因为带有很大的抖动,而不能用于MGT。

2)时钟修正策略传输时钟有非常严格的抖动要求,所以吉比特SERDES通常不能将恢复时钟作为传输时钟。

每一个PCB集合都有唯一的振荡器和唯一的频率。

如果两个1GHz的振荡器仅仅有1PPM的频差,同时我们提供1/20的参考时钟,则数据流的时钟每秒钟可能会增加或者缺失20,000个周期。

因此,在8b/10b 编码的系统中,每秒将会额外增加或者损失2万个符号。

大多数的SERDES都有时钟修正选项。

时钟修正需要使用唯一的符号或者符号序列,它们在数据流中是不会出现的。

因为时钟修正是对齐的后续处理,所以可以比较容易地通过保留一个K字符、或者一组有序的K字符、或者一个时钟修正数据序列来实现。

时钟修正进行的频数必须足够多,从而可以通过丢弃或者重复来补偿时钟的差异。

当然,有些系统并不需要时钟修正。

例如,相同的参考时钟和相同的速率意味着不需要进行时钟修正。

同样,如果所有接收电路的时钟都来自恢复时钟,那么时钟修正也是不需要的。

如果FIFO的写入速率和读出速率相等,也没有必要进行时钟修正。