第一讲 FPGA设计基础

FPGA概述PPT课件

6.底层内嵌功能单元 内嵌专用硬核是相对于底层嵌入的软核而言 的,硬核(Hard Core)使FPGA具有强大 的处理能力,等效于ASIC电路。

•12

1.3 IP核简介

IP(Intelligent Property)核

是具有知识产权的集成电路芯核总称,是 经过反复验证过的、具有特定功能的宏模 块,与芯片制造工艺无关,可以移植到不 同的半导体工艺中。

通道绑定原 理示意图

•28

5.预加重技术 在印制的电路板上,线路是呈现低通滤波 器的频率特性的,为解决高频部分的损失, 就要采取预加重技术。

预加重技术的思想是:在传输信号时,抬高 信号的高频信号,以补偿线路上高频分量的 损失。

•29

没有预加重 的发送波形

•30

预加重后的 发送波形

没有预加重 的接收波形

典型的IOB内部结构示意图

2.可配置逻辑块(CLB)

CLB是FPGA内的基本逻辑单元 .

CLB的实际数量和特性会依据器件的不同而不同,但是每 个CLB都包含一个可配置开关矩阵,此矩阵由选型电路(多 路复用器等)、触发器和4或6个输入组成。

典型的CLB结 构示意图

3. 数字时钟管理模块(DCM)

目前FPGA中多使用4输入的LUT,所以每一 个LUT可以看成是一个有4位地址线的RAM。当用 户通过原理图或HDL语言描述一个逻辑电路以后, PLD/FPGA开发软件会自动计算逻辑电路的所有可 能结果,并把真值表(即结果)写入RAM,这样,每 输入一个信号进行逻辑运算就等于输入一个地址去 进行查表,找出地址对应的内容,然后输出即可。

DLL简单模 型示意图

Xilinx DLL的典 型模型示意图

在FPGA设计中,消除时钟的传输延迟,实现高扇出 最简单的方法就是用DLL,把CLK0与CLKFB相连 即可。 利用一个DLL可以 实现2倍频输出

《FPGA入门学习》课件

LED闪烁设计

总结词

通过LED闪烁设计,掌握FPGA的基本控制功能和数字逻辑设计。

详细描述

LED闪烁设计是FPGA入门学习的基本项目之一,通过该设计,学习者可以了解FPGA的基本控制功能 ,掌握数字逻辑设计的基本原理和方法。LED闪烁设计通常涉及到LED灯的驱动和控制,需要学习者 掌握基本的数字逻辑门电路和时序控制。

FPGA具有并行处理和高速计算的优点,适 用于数字信号处理中的实时信号处理和算 法加速。

数字滤波器设计

频谱分析和正交变换

FPGA可以实现高性能的数字滤波器,如 FIR滤波器和IIR滤波器,用于信号降噪和特 征提取。

FPGA可以高效地实现FFT等正交变换算法 ,用于频谱分析和信号频率成分的提取。

图像处理应用

优化设计技巧

时序优化

讲解如何通过布局布线、时序分析等手段优化 FPGA设计,提高时序性能。

资源共享

介绍如何通过资源共享减少FPGA资源占用,提 高设计效率。

流水线设计

讲解如何利用流水线设计技术提高系统吞吐量。

硬件仿真与调试技术

仿真工具使用

介绍常用HDL仿真工具(如ModelSim)的使用方法 。

03

CATALOGUE

FPGA开发实战

数字钟设计

总结词

通过数字钟设计,掌握FPGA的基本开发流程和硬件描述语言的应用。

详细描述

数字钟设计是FPGA入门学习的经典项目之一,通过该设计,学习者可以了解FPGA开 发的基本流程,包括设计输入、综合、布局布线、配置下载等。同时,数字钟设计也涉 及到硬件描述语言(如Verilog或VHDL)的应用,学习者可以掌握基本的逻辑设计和

基础语言。

FPGA开发流程

FPGA课程培训

图1.1.7 RAM的电路结构框图

存储矩阵由许多存储单元排列而成,每个存 储单元能存储1位二进制数据(1或0),在 译码器和读/写控制电路的控制下既可以写 入1或0,又可将所存储的数据读出。 地址译码器将输入的地址代码译成一条字线 的输出信号,使连接在这条字线上的存储单 元与相应的读/写控制电路接通,然后对这 些单元进行读或写。

知识要点

可编程逻辑器件 FPGA 设计方法 设计流程 设计工具。

教学建议

本章的重点是掌握现代数字系统的设计 方法和FPGA设计流程的概念。建议学时 数为2~4学时。FPGA的设计方法和设计 流程,需要通过实际的设计过程加深理 解。注意不同设计工具的特点,注意不 同设计工具的设计流程的相同点和不同 点。FPGA设计工具的使用需要在以后章 节中进行学习。

可擦除的可编程逻辑器件EPLD的基本逻 辑单位是宏单元,它由可编程的与一或 阵列、可编程寄存器和可编程 I/O 3部 分组成。由于EPLD特有的宏单元结构、 大量增加的输出宏单元数和大的与阵列, 使其在一块芯片内能够更灵活性的实现 较多的逻辑功能

复杂可编程逻辑器件CPLD是EPLD的改进 型器件,一般情况下, CPLD器件至少包 含3种结构:可编程逻辑宏单元、可编程 I/O单元和可编程内部连线。部分CPLD 器件还集成了RAM、FIFO或双口RAM等 存储器,以适应DSP应用设计的要求。

现场可编程门阵列FPGA在结构上由逻辑功能块 排列为阵列,并由可编程的内部连线连接这些 功能块,来实现一定的逻辑功能。FPGA的功能 由逻辑结构的配置数据决定,在工作时,这些 配置数据存放在片内的SRAM或者熔丝图上。 使用SRAM的FPGA器件,在工作前需要从芯片 外部加载配置数据,这些配置数据可以存放在 片外的EPROM或其他存储体上,人们可以控制 加载过程,在现场修改器件的逻辑功能。

FPGA入门培训教材共45张PPT课件

# STEP#4: run router, report actual utilization and timing, write checkpoint design, run drc, write verilog and xdc out route_design write_checkpoint -force $outputDir/post_route report_timing_summary -file $outputDir/post_route_timing_summary.rpt report_timing -sort_by group -max_paths 100 -path_type summary -file $outputDir/post_route_timing.rpt report_clock_utilization -file $outputDir/clock_util.rpt report_utilization -file $outputDir/post_route_util.rpt report_power -file $outputDir/post_route_power.rpt report_drc -file $outputDir/post_imp_drc.rpt write_verilog -force $outputDir/bft_impl_netlist.v write_xdc -no_fixed_only -force $outputDir/bft_impl.xdc

FPGA基础知识PPT课件

.

18

基本可编程逻辑单元

由查找表(Look up table)触发器(FF)组成;

LUT一般是4输入查找表,高端器件(xilinx v5)采用LUT-6结构; LUT可看成4位地址线的16x1的RAM 结构

FF是可编程的触发器,可配置成同步/异步复位、同步/异步置位、 使能、装载等功能触发器;

a,b,c,d

.

29

SOPC(System on programmable chip):片上可编 程系统 FPGA内嵌入了CPU/DSP,具备实现软硬件协同 设计的能力; Xilinx:

FPGA基于查找表加触发器的结构,采用SRAM工 艺,也有采用flash或者反熔丝工艺;主要应用高 速、高密度大的数字电路设计;

FPGA由可编程输入/输出单元、基本可编程逻辑 单元、嵌入式块RAM、丰富的布线资源(时钟/长 线/短线)、底层嵌入功能单元、内嵌专用的硬核 等组成;

目前市场上应用比较广泛的FPGA芯片主要来自 Altera与Xilinx。另外还有其它厂家的一些低端芯 片(Actel、Lattice);

.

10

FPGA器件结构 可编程输入/输出单元 可编程逻辑单元 嵌入式块RAM 布线资源 底层嵌入功能单元

.

11

FPGA器件结构

Xilinx spatan-3器件结构

.

12

Altera cyclone II器件结构

LAB

.

13

FPGA器件结构 可编程输入/输出单元 可编程逻辑单元 嵌入式块RAM 布线资源 底层嵌入功能单元

.

5

CPLD器件结构

MAX7000 CPLD内部结构

宏单元

.

6

宏单元(乘积项)

fpga数字电路基础

fpga数字电路基础FPGA数字电路基础数字电路是现代电子技术的基础,而FPGA(Field-Programmable Gate Array)数字电路则是数字电路的一种重要形式。

本文将从FPGA的基本概念、工作原理、应用领域等方面介绍FPGA数字电路的基础知识。

一、FPGA的基本概念FPGA是一种可编程逻辑器件,它由可编程逻辑单元(PLU)、可编程互连资源(PIR)和可编程输入输出单元(PIO)等组成。

PLU是FPGA的核心部分,它由多个可编程逻辑门组成,可以实现各种逻辑功能。

PIR用于连接不同的PLU,形成不同的逻辑电路。

PIO则用于与外部设备进行通信。

二、FPGA的工作原理FPGA的工作原理可以简单描述为:根据用户编写的HDL (Hardware Description Language)代码,通过编译和综合工具将其转化为FPGA可识别的比特流文件,然后将该文件下载到FPGA芯片中,从而实现所需的数字电路功能。

三、FPGA的应用领域由于FPGA具有灵活可重构的特性,因此在各个领域都有广泛的应用。

以下是几个典型的应用领域:1. 通信领域:FPGA可以实现各种通信协议的解析、编码和解码,常用于无线通信系统、卫星通信系统等。

2. 图像处理领域:FPGA可以实现图像采集、图像处理和图像识别等功能,常用于数字摄像机、医疗影像设备等。

3. 数据存储与处理领域:FPGA可以实现数据的存储、处理和传输等功能,常用于数据库系统、数据中心等。

4. 工业控制领域:FPGA可以实现逻辑控制、运动控制和故障检测等功能,常用于工业自动化设备、机器人等。

5. 汽车电子领域:FPGA可以实现汽车电子系统的控制和管理,常用于发动机控制、车载娱乐系统等。

四、FPGA的优势与局限FPGA作为一种可编程逻辑器件,具有以下几个优势:1. 灵活可重构:FPGA可以根据需求进行灵活的硬件配置,支持实时更新和修改。

2. 高性能:FPGA可以实现并行处理,具有较高的运算速度和处理能力。

FPGA 基础知识

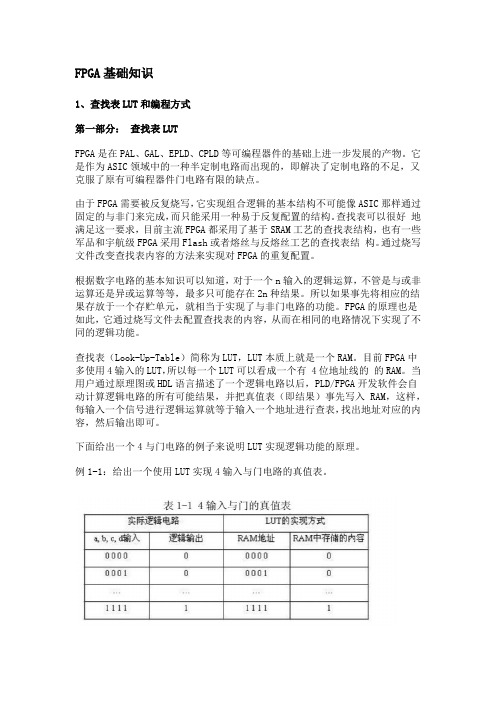

FPGA基础知识1、查找表LUT和编程方式第一部分:查找表LUTFPGA是在PAL、GAL、EPLD、CPLD等可编程器件的基础上进一步发展的产物。

它是作为ASIC领域中的一种半定制电路而出现的,即解决了定制电路的不足,又克服了原有可编程器件门电路有限的缺点。

由于FPGA需要被反复烧写,它实现组合逻辑的基本结构不可能像ASIC那样通过固定的与非门来完成,而只能采用一种易于反复配置的结构。

查找表可以很好地满足这一要求,目前主流FPGA都采用了基于SRAM工艺的查找表结构,也有一些军品和宇航级FPGA采用Flash或者熔丝与反熔丝工艺的查找表结构。

通过烧写文件改变查找表内容的方法来实现对FPGA的重复配置。

根据数字电路的基本知识可以知道,对于一个n输入的逻辑运算,不管是与或非运算还是异或运算等等,最多只可能存在2n种结果。

所以如果事先将相应的结果存放于一个存贮单元,就相当于实现了与非门电路的功能。

FPGA的原理也是如此,它通过烧写文件去配置查找表的内容,从而在相同的电路情况下实现了不同的逻辑功能。

查找表(Look-Up-Table)简称为LUT,LUT本质上就是一个RAM。

目前FPGA中多使用4输入的LUT,所以每一个LUT可以看成一个有 4位地址线的的RAM。

当用户通过原理图或HDL语言描述了一个逻辑电路以后,PLD/FPGA开发软件会自动计算逻辑电路的所有可能结果,并把真值表(即结果)事先写入 RAM,这样,每输入一个信号进行逻辑运算就等于输入一个地址进行查表,找出地址对应的内容,然后输出即可。

下面给出一个4与门电路的例子来说明LUT实现逻辑功能的原理。

例1-1:给出一个使用LUT实现4输入与门电路的真值表。

从中可以看到,LUT具有和逻辑电路相同的功能。

实际上,LUT具有更快的执行速度和更大的规模。

第二部分:编程方式由于基于LUT的FPGA具有很高的集成度,其器件密度从数万门到数千万门不等,可以完成极其复杂的时序与逻辑组合逻辑电路功能,所以适用于高速、高密度的高端数字逻辑电路设计领域。

新手的FPGA学习必备的四个基础知识详解

新手的FPGA学习必备的四个基础知识详解FPGA已成为现今的技术热点之一,无论学生还是工程师都希望跨进FPGA 的大门。

网络上各种开发板、培训班更是多如牛毛,仿佛在告诉你不懂FPGA你就OUT 啦。

那么我们要玩转FPGA必须具备哪些基础知识呢?下面我们慢慢道来。

(一)要了解什么是FPGA既然要玩转FPGA,那我们首先最重要的当然是要了解什么FPGA。

FPGA (Field-Programmable Gate Array),即现场可编程门阵列。

看到编程两个字码农就笑了,不就是编程嘛,那可是我们的强项。

且慢,此编程非彼编程。

一定要把FPGA的编程和软件编程区分开来。

软件的编程,处理器会逐条的把语言翻译成各种控制信号,去控制内部电路完成一个个运算或操作。

那么FPGA的编程是怎么实现的呢?无论Altera家还是Xlinix家的FPGA,叫法有什么差异,基本单元都相似,都是由真值表和D触发器构成。

改变真值表的值就改变了逻辑功能,再通过和D触发器组合来实现任何时序逻辑。

所以我们对FPGA的编程,实际上就是去修改这些真值表和连接关系,使他们组成一张专门的真值表,去实现特定的功能。

这和软件编程一步步运行程序有本质的区别。

要想玩转FPGA,就必须理解FPGA内部的工作原理,学习如何利用这些单元实现复杂的逻辑设计。

(二)正确理解HDL语言HDL(Hardware DescripTIon Language),硬件描述语言。

通过名称我们能看出来,HDL 语言是一种描述语言,这一点和C语言是有本质区别的。

正确理解描述的含义,对学好HDL语言很有帮助。

HDL语言只是用文本的方式把硬件电路描述出来。

我们在阅读HDL 程序的时候,在脑子里应该能反映出一个完整的硬件电路结构。

从另一方面说,我们在编写HDL语言之前,就已经对要实现的电路有清晰的概念。

所以HDL语言只是一个描述我们头脑中具体电路的工具,玩转FPGA的根本不是语言而是逻辑电路设计。