FPGA设计基础

fpga工程师基础知识

fpga工程师基础知识FPGA工程师基础知识FPGA(Field-Programmable Gate Array)是一种可编程逻辑器件,具有灵活性和可重构性,被广泛应用于数字电路设计和开发中。

作为一名FPGA工程师,掌握基础知识是至关重要的。

本文将介绍FPGA工程师所需的基础知识,包括FPGA的概念、工作原理、开发流程以及相关工具和技术。

一、FPGA的概念FPGA是一种可编程逻辑器件,它由一系列可编程逻辑门、存储单元和输入/输出接口组成。

与传统的固定逻辑电路不同,FPGA可以根据用户的需求进行编程,实现各种功能和逻辑运算。

FPGA的灵活性使其成为数字电路设计和开发中的重要工具。

二、FPGA的工作原理FPGA的基本单元是可编程逻辑门,如与门、或门、非门等。

这些逻辑门可以通过编程连接起来,形成复杂的逻辑电路。

FPGA中的存储单元用于存储逻辑电路的状态和数据。

通过配置FPGA中的逻辑门和存储单元,可以实现所需的功能。

FPGA的工作原理可以简单描述为以下几个步骤:1. 设计:首先,FPGA工程师需要使用HDL(硬件描述语言)如VHDL或Verilog来描述所需的逻辑电路。

设计包括逻辑电路的功能、输入输出接口和时序要求等。

2. 综合:设计完成后,需要使用综合工具将HDL代码转换为逻辑门级的表示。

综合工具将根据目标FPGA的特性和约束生成逻辑网表。

3. 布局与布线:在布局阶段,将逻辑网表映射到FPGA芯片的物理结构上。

在布线阶段,将逻辑网表中的逻辑门通过可编程连接资源连接起来。

4. 配置:配置是将设计好的逻辑电路下载到FPGA芯片上的过程。

FPGA芯片内部有一块非易失性存储器(通常是SRAM),用于存储逻辑电路的配置信息。

5. 运行:配置完成后,FPGA开始运行用户设计的逻辑电路。

FPGA 的输入和输出通过引脚与外部电路连接。

三、FPGA开发流程FPGA的开发流程通常包括以下几个步骤:1. 确定需求:明确所需的功能和性能要求。

《FPGA入门学习》课件

LED闪烁设计

总结词

通过LED闪烁设计,掌握FPGA的基本控制功能和数字逻辑设计。

详细描述

LED闪烁设计是FPGA入门学习的基本项目之一,通过该设计,学习者可以了解FPGA的基本控制功能 ,掌握数字逻辑设计的基本原理和方法。LED闪烁设计通常涉及到LED灯的驱动和控制,需要学习者 掌握基本的数字逻辑门电路和时序控制。

FPGA具有并行处理和高速计算的优点,适 用于数字信号处理中的实时信号处理和算 法加速。

数字滤波器设计

频谱分析和正交变换

FPGA可以实现高性能的数字滤波器,如 FIR滤波器和IIR滤波器,用于信号降噪和特 征提取。

FPGA可以高效地实现FFT等正交变换算法 ,用于频谱分析和信号频率成分的提取。

图像处理应用

优化设计技巧

时序优化

讲解如何通过布局布线、时序分析等手段优化 FPGA设计,提高时序性能。

资源共享

介绍如何通过资源共享减少FPGA资源占用,提 高设计效率。

流水线设计

讲解如何利用流水线设计技术提高系统吞吐量。

硬件仿真与调试技术

仿真工具使用

介绍常用HDL仿真工具(如ModelSim)的使用方法 。

03

CATALOGUE

FPGA开发实战

数字钟设计

总结词

通过数字钟设计,掌握FPGA的基本开发流程和硬件描述语言的应用。

详细描述

数字钟设计是FPGA入门学习的经典项目之一,通过该设计,学习者可以了解FPGA开 发的基本流程,包括设计输入、综合、布局布线、配置下载等。同时,数字钟设计也涉 及到硬件描述语言(如Verilog或VHDL)的应用,学习者可以掌握基本的逻辑设计和

基础语言。

FPGA开发流程

FPGA课程培训

图1.1.7 RAM的电路结构框图

存储矩阵由许多存储单元排列而成,每个存 储单元能存储1位二进制数据(1或0),在 译码器和读/写控制电路的控制下既可以写 入1或0,又可将所存储的数据读出。 地址译码器将输入的地址代码译成一条字线 的输出信号,使连接在这条字线上的存储单 元与相应的读/写控制电路接通,然后对这 些单元进行读或写。

知识要点

可编程逻辑器件 FPGA 设计方法 设计流程 设计工具。

教学建议

本章的重点是掌握现代数字系统的设计 方法和FPGA设计流程的概念。建议学时 数为2~4学时。FPGA的设计方法和设计 流程,需要通过实际的设计过程加深理 解。注意不同设计工具的特点,注意不 同设计工具的设计流程的相同点和不同 点。FPGA设计工具的使用需要在以后章 节中进行学习。

可擦除的可编程逻辑器件EPLD的基本逻 辑单位是宏单元,它由可编程的与一或 阵列、可编程寄存器和可编程 I/O 3部 分组成。由于EPLD特有的宏单元结构、 大量增加的输出宏单元数和大的与阵列, 使其在一块芯片内能够更灵活性的实现 较多的逻辑功能

复杂可编程逻辑器件CPLD是EPLD的改进 型器件,一般情况下, CPLD器件至少包 含3种结构:可编程逻辑宏单元、可编程 I/O单元和可编程内部连线。部分CPLD 器件还集成了RAM、FIFO或双口RAM等 存储器,以适应DSP应用设计的要求。

现场可编程门阵列FPGA在结构上由逻辑功能块 排列为阵列,并由可编程的内部连线连接这些 功能块,来实现一定的逻辑功能。FPGA的功能 由逻辑结构的配置数据决定,在工作时,这些 配置数据存放在片内的SRAM或者熔丝图上。 使用SRAM的FPGA器件,在工作前需要从芯片 外部加载配置数据,这些配置数据可以存放在 片外的EPROM或其他存储体上,人们可以控制 加载过程,在现场修改器件的逻辑功能。

fpga笔试题知识点汇总

fpga笔试题知识点汇总

FPGA(现场可编程门阵列)的笔试题目通常会考察以下几个方面的知识点:

1. 数字电路设计基础:理解数字电路的基本原理,包括逻辑门、触发器、寄存器、移位器等基本元件的工作原理和特性。

2. 硬件描述语言:熟悉硬件描述语言(如VHDL或Verilog)的使用,理解这些语言的基本语法、结构、行为和功能描述。

3. FPGA开发工具:了解并熟悉FPGA开发工具,如Xilinx ISE、Vivado,Altera Quartus等,理解这些工具的基本操作和使用方法。

4. FPGA设计流程:理解FPGA设计的流程,包括设计输入、综合、布局布线、时序分析、仿真等步骤,并能根据流程进行设计。

5. 逻辑设计:理解并能够进行基本的逻辑设计,如组合逻辑、时序逻辑等,并理解这些设计在FPGA上的实现方式。

6. 数字信号处理:理解数字信号处理的基本原理和方法,包括滤波器设计、FFT变换等,并理解这些方法在FPGA上的实现方式。

7. 嵌入式系统设计:理解嵌入式系统设计的基本原理和方法,包括微控制器、DSP、ARM等,并理解这些系统在FPGA上的实现方式。

8. 通信协议:理解并能够进行基本的通信协议设计,如UART、SPI、I2C 等,并理解这些协议在FPGA上的实现方式。

9. 时序约束与时序分析:理解时序约束的设定原则,掌握时序分析的方法和技巧,能够进行合理的时序优化。

10. 可靠性设计:理解并能够进行基本的可靠性设计,如容错处理、故障检测与恢复等,并理解这些设计在FPGA上的实现方式。

以上是FPGA笔试中可能会涉及到的知识点,具体会根据不同的职位和招聘要求有所不同。

建议根据具体的招聘要求进行针对性的复习和准备。

fpga逻辑设计方案报告

fpga逻辑设计方案报告FPGA逻辑设计方案报告一、引言FPGA(Field-Programmable Gate Array,现场可编程门阵列)是一种可编程数字逻辑器件,具有灵活性和可重构性。

FPGA的设计涉及到逻辑电路设计、时序设计和综合优化等方面。

本报告旨在介绍FPGA逻辑设计方案的基本原理和方法。

二、FPGA逻辑设计基础1. FPGA架构:FPGA由可编程逻辑单元(CLB)、输入输出模块(IOB)和可编程互连资源(Interconnect)构成。

CLB是FPGA 中最基本的逻辑单元,包含查找表(LUT)、寄存器和多路选择器等。

IOB用于与外部设备进行数据交换。

Interconnect用于连接CLB和IOB,实现不同逻辑单元之间的互连。

2. FPGA编程语言:常见的FPGA编程语言包括VHDL和Verilog。

这些语言提供了描述数字逻辑电路的方式,可以通过编写代码来实现逻辑功能。

三、FPGA逻辑设计流程1. 需求分析:明确设计的功能和性能要求,确定逻辑电路的输入输出接口。

2. 模块划分:将整个设计任务划分为多个模块,每个模块负责实现一个特定的功能。

3. 逻辑设计:使用FPGA编程语言编写每个模块的逻辑电路描述。

在描述中使用逻辑门、寄存器、多路选择器等基本元件,通过组合和时序逻辑的方式实现所需功能。

4. 综合优化:对逻辑电路进行综合,将高级语言描述转化为逻辑门级的电路描述。

综合优化包括逻辑优化、时序优化和面积优化等。

5. 时序设计:对逻辑电路进行时序约束的设置,确保信号的传输满足时序要求。

时序设计包括时钟频率、时钟分频、时钟延迟等方面的考虑。

6. 布局布线:将逻辑电路映射到FPGA的物理资源上。

布局布线包括逻辑单元的位置分配和信号线的路径规划。

7. 静态时序分析:对布局布线后的电路进行时序分析,检查是否满足时序要求。

8. 配置生成:将逻辑电路的配置位流生成,用于配置FPGA芯片。

9. 下载与验证:将配置位流下载到FPGA芯片中,通过验证测试确保设计满足功能和性能要求。

fpga数字电路基础

fpga数字电路基础FPGA数字电路基础数字电路是现代电子技术的基础,而FPGA(Field-Programmable Gate Array)数字电路则是数字电路的一种重要形式。

本文将从FPGA的基本概念、工作原理、应用领域等方面介绍FPGA数字电路的基础知识。

一、FPGA的基本概念FPGA是一种可编程逻辑器件,它由可编程逻辑单元(PLU)、可编程互连资源(PIR)和可编程输入输出单元(PIO)等组成。

PLU是FPGA的核心部分,它由多个可编程逻辑门组成,可以实现各种逻辑功能。

PIR用于连接不同的PLU,形成不同的逻辑电路。

PIO则用于与外部设备进行通信。

二、FPGA的工作原理FPGA的工作原理可以简单描述为:根据用户编写的HDL (Hardware Description Language)代码,通过编译和综合工具将其转化为FPGA可识别的比特流文件,然后将该文件下载到FPGA芯片中,从而实现所需的数字电路功能。

三、FPGA的应用领域由于FPGA具有灵活可重构的特性,因此在各个领域都有广泛的应用。

以下是几个典型的应用领域:1. 通信领域:FPGA可以实现各种通信协议的解析、编码和解码,常用于无线通信系统、卫星通信系统等。

2. 图像处理领域:FPGA可以实现图像采集、图像处理和图像识别等功能,常用于数字摄像机、医疗影像设备等。

3. 数据存储与处理领域:FPGA可以实现数据的存储、处理和传输等功能,常用于数据库系统、数据中心等。

4. 工业控制领域:FPGA可以实现逻辑控制、运动控制和故障检测等功能,常用于工业自动化设备、机器人等。

5. 汽车电子领域:FPGA可以实现汽车电子系统的控制和管理,常用于发动机控制、车载娱乐系统等。

四、FPGA的优势与局限FPGA作为一种可编程逻辑器件,具有以下几个优势:1. 灵活可重构:FPGA可以根据需求进行灵活的硬件配置,支持实时更新和修改。

2. 高性能:FPGA可以实现并行处理,具有较高的运算速度和处理能力。

FPGA的基本原理(详细+入门)

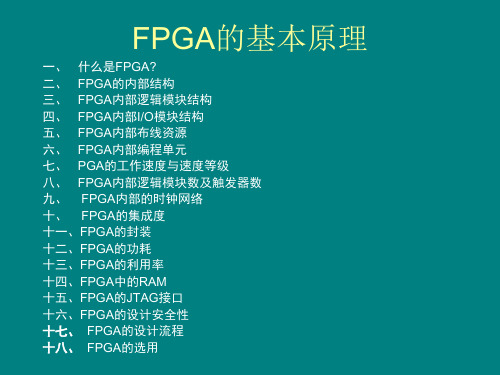

门阵等效门:一个门阵等效门定义为一个两输入端的“与非”门。 系统门:是芯片上门的总数,是厂家指定给器件的一个门数。

十一、FPGA的封装

1、引脚数:FPGA芯片总的引脚数。 2、用户I/O数:指除了电源引脚、特殊功能引脚外的引脚,这些引脚可根据用户的需要进行配置。 3、 I/O驱动电流:8mA 或10mA。 4、时钟网络数:FPGA芯片可能包含1个、2个或4个时钟网络。 5、封装:PLCC,PQFP,CPGA等封装形式。 6、工作温度范围:FPGA芯片一般有商用、工业用及军用等不同的工作温度范围。 7、工作环境:一般分普通工作环境和航天工作环境。

ACT1模块是如何实现三输入与门的?

2、查表型FPGA结构 两输入与门: 4 X 1 RAM 表:

A

B

C

0

0

0

0

1

0

1

0

0

1

1

1

A1

A0

(二)、 什么是FPGA? FPGA是英语(Field programmable Gate Array)的缩写,即现场可编程门阵。它的结构类似于掩膜可编程门阵(MPGA),由可编程逻辑功能块和可编程I/O模块排成阵列组成,并由可编程的内部连线连接这些逻辑功能块和I/O模块来实现不同的设计。 1、FPGA与MPGA的区别: MPGA利用集成电路制造过程进行编程来形成金属互连,而FPGA利用可编程的电子开关实现逻辑功能和互连。 2、FPGA与CPLD的区别: 1) 结构不同:FPGA是由可编程的逻辑模块、可编程的分段互连线和I/O模块组成,而CPLD是由逻辑阵列块、可编程连线阵列和I/O模块组成。 2) CPLD延时可预测(Predictable),FPGA的延时与布局布线情况有关。 3) CPLD 组合逻辑多而触发器较少,而FPGA触发器多。

FPGA学习步骤

FPGA学习步骤FPGA(Field-Programmable Gate Array)是可编程逻辑器件的一种,它具有高度可编程性和灵活性,被广泛应用于数字电路设计和嵌入式系统开发。

学习FPGA可以使我们了解数字电路的原理和设计方法,并能够利用FPGA开发和优化各种应用。

下面是一个FPGA学习的步骤,帮助你逐步了解FPGA的原理和应用。

步骤1:掌握数字电路基础知识FPGA是用于设计数字电路的器件,因此首先需要掌握数字电路的基础知识。

学习数字电路的基本逻辑门、布尔代数和组合逻辑电路等概念,理解时序电路、存储器和状态机等高级概念。

步骤2:了解FPGA的原理和架构学习FPGA的原理和架构有助于理解FPGA是如何实现数字电路的。

学习FPGA的片上资源,如查找表、触发器和运算器等,以及FPGA的内部连接结构。

还可以探索FPGA的编程方式,包括寄存器传输级综合(RTL)和硬件描述语言(HDL)等。

步骤3:学习硬件描述语言(HDL)硬件描述语言是FPGA设计的基础,通常使用的HDL是Verilog和VHDL。

学习HDL的语法和基本结构,并掌握如何使用HDL描述数字电路。

可以通过书籍、在线教程和实践项目等方式学习HDL。

步骤4:使用FPGA开发工具步骤5:完成简单的FPGA设计项目开始进行一些简单的FPGA设计项目,如实现基本的逻辑门、组合逻辑电路和时序电路等。

通过这些项目,学会如何使用HDL描述和实现数字电路,如何利用FPGA的资源和工具进行设计和优化。

步骤6:进阶学习FPGA应用进一步学习FPGA的应用,例如数字信号处理(DSP)、图像处理、通信系统和嵌入式系统等。

根据自己的兴趣和需求选择相应的应用领域,并实践相关项目。

学习如何使用FPGA实现更复杂的功能和算法,并了解相应的设计方法和技术。

步骤7:参加竞赛或项目参加FPGA设计竞赛或实际项目有助于提升自己的FPGA设计能力。

通过参赛或项目,可以锻炼自己的团队合作能力和解决问题的能力,并将学到的知识应用到实际应用中。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

Verilog与C语言的比较

(1)Verilog是一种硬件语言,最终是为了产生实际的硬件 电路或对硬件电路进行仿真;而C语言是一种软件语言,是 控制硬件来实现某些功能的语言。

5'O37

5位八进制数(二进制11111)

4'D2

4位十进制数(二进制0011)

4'B1x_01 4位二进制数

7'Hx

7位x(扩展的x),即xxxxxxx

4'hZ

4位z(扩展的z),即zzzz

4'd-4

非法:数值不能为负

8‘h 2A 在位长和字符之间,以及基数和数值

之间允许出现空格

3' b001 非法:`和基数b之间不允许出现空格

(2)常量

Verilog HDL中有三种常量:整型、实型和字符串 型。下划线符号( _ )可以随意用在整数或实数中, 它们就数量本身没有意义,可用来提高易读性,唯 一的限制是下划线符号不能用做首字符。

整型数可以按如下两种方式书写:

十进制形式整数的例子: 32 十进制数32 -15 十进制数-15

基数表示形式整数的例子:

模块

模块(module)是Verilog的基本描述单位,用于描述某 个设计的功能或结构以及与其他模块通信的外部端口。

例 3位加法器的形成语言为

module addr (a, b, cin, count, sum); / /模块名及

输入输出端口列表

input [2:0] a;

/ /定义信号流向及位宽

例

Count

COUNT //与Count不同

R56_68

FIVE$

Verilog HDL定 义的一些常用的

关键词

always edge endspecify

if module

and

assign begin

case

default

disable

else

end endcase endmodule endfunction endprimitive

常用的C语言与 Verilog语言相 对应的关键字与

控制结构

C语言

sub-function if-then-else

Case {,} For While Break Define Int Printf

Verilog语言

module, function, task if-then-else Case begin, end For While Disable Define Int

FPGA设计基础

重点 Verilog HDL基础知识 嵌入式处理器介绍 FPGA设计流程

1 Verilog HDL基础知识

概 述

HDL(Hardware Description Language)是 一种用形式化方法来描述数字电路和数字逻辑系统 的硬件描述语言。

有两种类型:VHDL 和 Verilog HDL。

monitor, display,strobe

常用的C语言与Verilog语言相对应的运算符

C语言 * / + % !

&& || > < >= <= == != ~ & | ^ ~^ >> << ?:

Verilog语言 * / + % !

&& || > < >= <= == != ~ & | ^ ~^ >> << ?:

(2)C语言只要是语法正确,都可以编译执行;而Verilog 语言有可综合的限制,即在所有的Verilog语句中,只有一部 分可以被综合,而另外的部分则不能被综合,只能用来仿真。

(3)C语言是一种软件编程语言,其基本思想是语句的循序 执行;而Verilog语言的基本思想是模块的并行执行。

(4)利用Verilog编程时,要时刻记得Verilog是硬件语言, 要时刻将Verilog与硬件电路对应起来。

input [2:0] b;

input cin;

output com;

assign {count,sum} = a +b + cin; / /功能描述

endmodule

Verilog HDL基本语法 1.标识符

Verilog HDL中的标识符可以是任意一组字母、数 字、$符号和_(下划线)符号的组合,但标识符的 第一个字符必须是字母或者下划线。另外,标识 符是区分大小写的。

例 /* statement1, statement2, …… statementn */

另一种是以//开头的语句,它表示以//开始到 本行结束都属于注释语句。

3. 格式

Verilog HDL是区分大小写的,即大小写不 同的标识符是不同的。另外其书写格式自由, 即一条语句可多行书写,一行可写多个语句。 空白(新行、制表符、空格)没有特殊意义。

功能 乘 除 加 减 取模

反逻辑 逻辑且 逻辑或

大于 小于 大于等于 小于等于 等于 不等于 位反相 按位逻辑与 按位逻辑或 按位逻辑异或 按位逻辑同或 右移 左移 同等于if-else敘述

自顶向下的设计方法

通过自顶向下的设计方法,可以实现设计的结构化,可以 使一个复杂的系统设计由多个设计者分工合作,还可以实 现层次化的管理。

例 input A;input B;与 input A; input B; 是一样的。

4. 数字值集合

(1) 值集合

Verilog HDL中规定了四种基本的值类型,这四 类基本值组成了Verilog HDL中的常量,即

0:逻辑0或“假”; 1:逻辑1或“真”; X:未知值; Z:高阻。

注意,这四种值的解释都内置于语言中。如一个为z的值 总是意味着高阻抗,一个为0 的值通常是指逻辑0;在门 的输入或一个表达式中为“z”的值通常解释成“x ”。此 外,x值和z值都是不分大小写的,也就是说,值0x1z与值 0X1Z相同。

endtable endtask event

for

forever fork function

initial

inout

input

integer

join

large

negedge

nor

not

or

output

2.注释

Verilog HDL中有两种注释方式,一种是以 “/*”符号开始,“*/” 结束,在两个符号之 间的语句都是注释语句,因此可扩展到多行。