EDA实验程序大集合

EDA实验报告实验三、序列检测器的设计

实验三、序列检测器的设计一、预习内容1、预习序列发生器和检测器的基本工作原理;2、画出实验原理草图;3、写出实验的基本步骤和源程序。

二、实验目的1、掌握序列检测器的工作原理;2、学会用状态机进行数字系统设计。

三、实验器材PC机一台、EDA教学实验系统一台、下载电缆一根(已接好)、导线若干四、实验要求1、检测连续4个‘1’的状态机,画出状态转移图,并写出VHD代码;(必做部分)2、了解试验箱,完成数据分配器的硬件实验。

(实验一的硬件操作,首次使用请谨慎使用试验箱!)3、检测“10001110”序列,当检测到该序列后输出为‘1’。

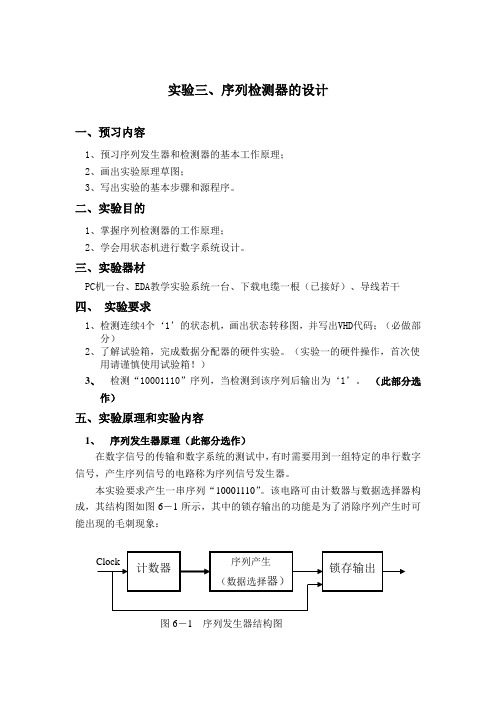

(此部分选作)五、实验原理和实验内容1、序列发生器原理(此部分选作)在数字信号的传输和数字系统的测试中,有时需要用到一组特定的串行数字信号,产生序列信号的电路称为序列信号发生器。

本实验要求产生一串序列“10001110”。

该电路可由计数器与数据选择器构成,其结构图如图6-1所示,其中的锁存输出的功能是为了消除序列产生时可能出现的毛刺现象:图6-1 序列发生器结构图2、序列检测器的基本工作过程:序列检测器用于检测一组或多组由二进制码组成的脉冲序列信号,在数字通信中有着广泛的应用。

当序列检测器连续收到一组串行二进制码后,如果这组码与检测器中预先设置的码相同,则输出1,否则输出0。

由于这种检测的关键在于正确码的收到必须是连续的,这就要求检测器必须记住前一次的正确码及正确序列,直到在连续的检测中所收到的每一位码都与预置的对应码相同。

在检测过程中,任何一位不相等都将回到初始状态重新开始检测。

状态图如图6-2所示:图6-2 序列检测器状态图3、状态机的基本设计思想:在状态连续变化的数字系统设计中,采用状态机的设计思想有利于提高设计效率,增加程序的可读性,减少错误的发生几率。

同时,状态机的设计方法也是数字系统中一种最常用的设计方法。

一般来说,标准状态机可以分为摩尔(Moore)机和米立(Mealy)机两种。

EDA-实验报告

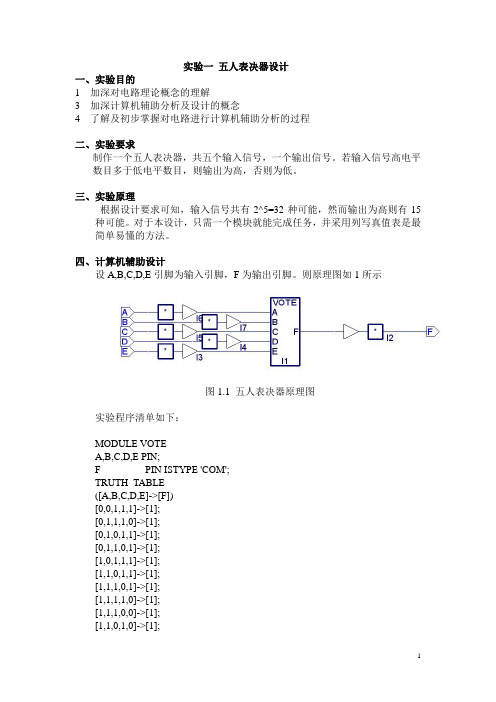

实验一五人表决器设计一、实验目的1 加深对电路理论概念的理解3 加深计算机辅助分析及设计的概念4 了解及初步掌握对电路进行计算机辅助分析的过程二、实验要求制作一个五人表决器,共五个输入信号,一个输出信号。

若输入信号高电平数目多于低电平数目,则输出为高,否则为低。

三、实验原理根据设计要求可知,输入信号共有2^5=32种可能,然而输出为高则有15种可能。

对于本设计,只需一个模块就能完成任务,并采用列写真值表是最简单易懂的方法。

四、计算机辅助设计设A,B,C,D,E引脚为输入引脚,F为输出引脚。

则原理图如1所示图1.1 五人表决器原理图实验程序清单如下:MODULE VOTEA,B,C,D,E PIN;F PIN ISTYPE 'COM';TRUTH_TABLE([A,B,C,D,E]->[F])[0,0,1,1,1]->[1];[0,1,1,1,0]->[1];[0,1,0,1,1]->[1];[0,1,1,0,1]->[1];[1,0,1,1,1]->[1];[1,1,0,1,1]->[1];[1,1,1,0,1]->[1];[1,1,1,1,0]->[1];[1,1,1,0,0]->[1];[1,1,0,1,0]->[1];[1,1,1,1,1]->[1];[1,1,0,0,1]->[1];[1,0,0,1,1]->[1];[1,0,1,0,1]->[1];[1,0,1,1,0]->[1];END五、实验测试与仿真根据题目要求,可设输入分别为:0,0,0,0,0;1,1,1,1,1;1,0,1,0,0;0,1,0,1,1。

其测试程序如下所示:MODULE fivevoteA,B,C,D,E,F PIN;X=.X.;TEST_VECTORS([A,B,C,D,E]->[F])[0,0,0,0,0]->[X];[1,1,1,1,1]->[X];[1,0,1,0,0]->[X];[0,1,0,1,1]->[X];END测试仿真结果如图1.2所示:图1.2 五人表决器设计仿真图可知,设计基本符合题目要求。

EDA实验程序汇总

实验二组合逻辑电路设计(一)设计一个四舍五入判别电路,其输入为842lBCD码,要求当输入大于或等于5时判别电路输为l,反之为0。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_ARITH.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY ZQF ISPORT(A:IN UNSIGNED (3 DOWNTO 0);BCD0,BCD1:OUT STD_LOGIC_VECTOR(3 DOWNTO 0);SEVEN0,SEVEN1:OUT STD_LOGIC_VECTOR(6 DOWNTO 0));END ZQF ;ARCHITECTURE A OF ZQF ISSIGNAL XC:STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINPROCESS(A)BEGINIF A<10 THENBCD1<="0000";BCD0<=STD_LOGIC_VECTOR(A);SEVEN1<="0111111";XC<=STD_LOGIC_VECTOR(A);ELSEBCD1<="0001";BCD0<=A-10;SEVEN1<="0000110";XC<=STD_LOGIC_VECTOR(A)-10;END IF;END PROCESS;SEVEN_SEGMENT:BLOCKBEGINSEVEN0<="0111111" WHEN XC="0000" ELSE"0000110" WHEN XC="0001" ELSE"1011011" WHEN XC="0010" ELSE"1001111" WHEN XC="0011" ELSE"1100110" WHEN XC="0100" ELSE"1101101" WHEN XC="0101" ELSE"1111101" WHEN XC="0110" ELSE"0000111" WHEN XC="0111" ELSE"1111111" WHEN XC="1000" ELSE"1101111" WHEN XC="1001" ELSE"0000000";END BLOCK SEVEN_SEGMENT;END A;实验五英语字母显示电路LIBRARY IEEE;USE IEEE.std_logic_1164.all;USE IEEE.STD_LOGIC_ARITH.ALL;use ieee.std_logic_unsigned.all;----------------------------------------------------entity zimum isport(clk: in std_logic;ledag:out std_logic_vector(6 downto 0));end zimum;architecture behave of zimum issignal clk1khzs: std_logic;signal charcnt: std_logic;signal cnt: integer range 0 to 7 :=0;BEGINprocess(clk)variable clknum:integer range 0 to 1999999 :=0;beginif clk'event and clk='1' thenif clknum=1999999 then clknum:=0;clk1khzs<= not clk1khzs; -----1s else clknum:=clknum+1;end if;end if;end process;process(clk1khzs)beginif clk1khzs'event and clk1khzs='1' thenif cnt=7 then cnt<=0;else cnt<=cnt+1;end if;end if;end process;process(cnt)begincase cnt iswhen 0=>ledag<="0110111"; ------Hwhen 1=>ledag<="1001111"; ------Ewhen 2=>ledag<="0001110"; ------Lwhen 3=>ledag<="0001110"; ------Lwhen 4=>ledag<="1001110"; ------Cwhen 5=>ledag<="1100111"; ------Pwhen 6=>ledag<="0001110"; ------Lwhen 7=>ledag<="1111101"; ------Dwhen others=>null;END CASE;end process;END ARCHITECTURE BEHAVE;实验九异步计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY DFF_4ISPORT (CLK,KEY,RESET:IN STD_LOGIC;Q:BUFFER STD_LOGIC_VECTOR(0 TO 3));END DFF_4;ARCHITECTURE BEHAVE OF DFF_4ISCOMPONENT D_FFPORT(CLK,D,RESET:IN STD_LOGIC;Q,QN:OUT STD_LOGIC);END COMPONENT;SIGNAL KEY_FLAG:STD_LOGIC;SIGNAL CLK20HZ:STD_LOGIC;SIGNAL QN:STD_LOGIC_VECTOR(0 TO 3);SIGNAL CNT:STD_LOGIC;BEGINPROCESS(CLK)VARIABLE CLKNUM:INTEGER RANGE 0 TO 99999 :=0;BEGINIF CLK'EVENT AND CLK='1' THENIF CLKNUM=99999 THEN CLKNUM:=0;CLK20HZ<=NOT CLK20HZ;ELSE CLKNUM:=CLKNUM+1;END IF;END IF;END PROCESS;PROCESS(CLK20HZ)BEGINIF CLK20HZ'EVENT AND CLK20HZ='1' THENIF KEY='1' AND KEY_FLAG='0' THENKEY_FLAG<='1';ELSIF KEY='0' AND KEY_FLAG='1' THENKEY_FLAG<='0';END IF;END IF;END PROCESS;DFF1:D_FF PORT MAP(KEY_FLAG,QN(0),RESET,Q(0),QN(0));DFFX:FOR I IN 1 TO 3 GENERATEDFF2TO4: D_FF PORT MAP(QN(I-1),QN(I),RESET,Q(I),QN(I));END GENERATE;END BEHAVE;例化:LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY D_FF ISPORT(CLK,D,RESET:IN STD_LOGIC;Q,QN:OUT STD_LOGIC);END ENTITY;ARCHITECTURE BEHAVE OF D_FF ISSIGNAL Q1:STD_LOGIC;BEGINPROCESS(CLK,RESET)BEGINIF RESET='1' THENQ1<='0';ELSIF CLK'EVENT AND CLK='1' THENQ1<=D;END IF;Q<=Q1;QN<=NOT Q1;END PROCESS;END BEHAVE;实验十九频率计1、设计一个3位十进制频率计,其测量范围为lMHz。

EDA实验程序总结(全)

EDA实验程序总结3/8译码器library ieee;use ieee.std_logic_1164.all;entity decoder isport ( inp: in std_logic_vector(2 downto 0);outp: out std_logic_vector(7 downto 0)); end decoder;architecture behave of decoder isbeginoutp(0) <= '1' when inp = "000" else '0';outp(1) <= '1' when inp = "001" else '0';outp(2) <= '1' when inp = "010" else '0';outp(3) <= '1' when inp = "011" else '0';outp(4) <= '1' when inp = "100" else '0';outp(5) <= '1' when inp = "101" else '0';outp(6) <= '1' when inp = "110" else '0';outp(7) <= '1' when inp = "111" else '0';end behave;全加器(五种方法)1--布尔代数法library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity adder_01 isport( ai,bi,ci_1:in bit;si,ci:out bit);end entity adder_01; architecture beheave of adder_01 isbeginsi<=ci_1 xor ( ai xor bi );ci<=(ai and bi) or (ci_1 and ( ai xor bi )) ;end architecture beheave ;2--use when_else sentenceslibrary ieee;use ieee.std_logic_1164.all;entity adder_02 isport( ai,bi,ci_1:in std_logic;si,ci:out std_logic );end entity adder_02;architecture beheave of adder_02 issignal n2:std_logic_vector(1 downto 0);signal n3:std_logic_vector(2 downto 0);beginn3 <= ci_1 & ai & bi;n2<="00" when n3="000" else"10" when n3="001" else"10" when n3="010" else"01" when n3="011" else"10" when n3="100" else"01" when n3="101" else"01" when n3="110" else"11" ;si<=n2(1);ci<=n2(0);end beheave;3--use with_select_when sentences library ieee;use ieee.std_logic_1164.all;entity adder_03 isport( ai,bi,ci_1:in std_logic;si,ci:out std_logic);end entity adder_03 ; architecture dataflow of adder_03 is signal n2:std_logic_vector(1 downto 0); signal n3:std_logic_vector(2 downto 0);beginn3<=ci_1 & ai & bi ;with n3 selectn2<="00" when "000","10" when "001","10" when "010","01" when "011","10" when "100","01" when "101","01" when "110","11" when others;si<=n2(1);ci<=n2(0);end dataflow;4--use if_elsif_else sentencelibrary ieee;use ieee.std_logic_1164.all;entity adder_04 isport ( ai,bi,ci_1:in std_logic ;si,ci:out std_logic ) ;end entity adder_04 ; architecture beheave of adder_04 issignal n3:std_logic_vector(2 downto 0); signal n2:std_logic_vector(1 downto 0); beginn3<= ci_1 & ai & bi ;process ( n3 )beginif n3="000" then n2<="00";elsif n3="001" then n2<="10";elsif n3="010" then n2<="10";elsif n3="011" then n2<="01";elsif n3="100" then n2<="10";elsif n3="101" then n2<="01";elsif n3="110" then n2<="01";else n2<="11";end if;si<=n2(1);ci<=n2(0);end process;end beheave;5--use case_when sentence library ieee;use ieee.std_logic_1164.all;entity adder_05 isport ( ai,bi,ci_1:in std_logic ;si,ci:out std_logic);end entity adder_05; architecture beheave of adder_05 is signal n3:std_logic_vector(2 downto 0); signal n2:std_logic_vector(1 downto 0); beginn3<=ci_1 & ai & bi;process ( n3 )begincase n3 iswhen "000" => n2<="00";when "001" => n2<="10";when "010" => n2<="10";when "011" => n2<="01";when "100" => n2<="10";when "101" => n2<="01";when "110" => n2<="01";when others => n2<="11";end case ;si<=n2(1);ci<=n2(0);end process;end beheave;D触发器分频:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fenpin isgeneric(n:integer:=10000000);port(clk:in std_logic ;clock: buffer std_logic);end fenpin;architecture behave of fenpin isbeginprocess(clk)variable num:integer range 0 to 50000000; beginif clk'event and clk='1' thenif num=n thennum:=0;clock<=not clock;else num:=num+1;end if;end if;end process;end behave;D触发器:library ieee;use ieee.std_logic_1164.all;entity dff1 isport (d,clk :in std_logic;q:out std_logic);end dff1;architecture behave of dff1 issignal q1:std_logic;beginprocess (clk,q1)beginif clk'event and clk='1'thenq1<=d;end if ;end process;q<=q1;end behave;顶层文件:library ieee;use ieee.std_logic_1164.all;entity Df isport (dd,clck :in std_logic;qq:out std_logic);end Df;architecture behave of Df is component fenpin is--分频器generic(n:integer:=10000000);port(clk:in std_logic ;clock: out std_logic);end component;component dff1 is--D触发器port (d,clk :in std_logic;q:out std_logic);end component;signal a:std_logic;beginu1:fenpin generic map(n=>10000000) port map(clk=>clck,clock=>a);u2:dff1 port map(d=>dd,clk=>a,q=>qq); end behave;JK触发器:分频:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity fenpin isgeneric(n:integer:=10000000);port(clk:in std_logic ;clock: buffer std_logic);end fenpin;architecture behave of fenpin isbeginprocess(clk)variable num:integer range 0 to 50000000; beginif clk'event and clk='1' thenif num=n thennum:=0;clock<=not clock;else num:=num+1;end if;end if;end process;end behave;J触发器:library ieee;use ieee.std_logic_1164.all;entity jkff1 isport (sd,rd,clk,j,k:in std_logic;q,qb:out std_logic);end entity;architecture behave of jkff1 issignal q1,qb1:std_logic;beginprocess(sd,rd,clk,q1,qb1)beginif (sd='0' and rd='1') thenq1<='1';qb1<='0';elsif (sd='1' and rd='0') thenq1<='0';qb1<='1';elsif (sd='1' and rd='1' and rising_edge(clk)) thenq1<=(j and (not q1)) or ((not k)and q1);qb1<=not q1;end if;q<=q1; qb<=qb1;end process;end behave;顶层文件:library ieee;use ieee.std_logic_1164.all;entity JK isport (sd1,rd1,clk1,j1,k1:in std_logic;q1,qb1:out std_logic);end entity;architecture behave of JK iscomponent fenpin is--分频器generic(n:integer:=10000000);port(clk:in std_logic ;clock: out std_logic);end component;component jkff1 isport (sd,rd,clk,j,k:in std_logic;q,qb:out std_logic);end component;signal q0:std_logic;signal a:std_logic;begina<=clk1;u1:fenpin generic map(n=>10000000)port map(clk=>a,clock=>q0);u2:jkff1 port map(sd=>sd1,rd=>rd1,j=>j1,k=>k1,q=>q1,qb=>qb1,clk=>q0); end behave;十进制:分频:library ieee;use ieee.std_logic_1164.all;entity fenpin isport(clk:in std_logic;qout:buffer std_logic);end;architecture behave of fenpin isbeginprocess(clk)variable num: integer :=1;beginif falling_edge(clk)then if num=10000000then num:=1;qout<=not qout;else num:=num+1;end if;end if;end process;end behave;十进制:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity sjz isport(CLR,LD,CLK:in std_logic;EN:in std_logic_vector(1 downto 0);D:in std_logic_vector(3 downto 0);Q:out std_logic_vector(3 downto 0);C:out std_logic);end sjz;architecture ls of sjz issignal Q1:std_logic_vector(3 downto 0);signal EN1:std_logic;beginEN1<=EN(1)AND EN(0);process(CLR,LD,CLK,EN)beginif CLR='0' then Q1<="0000";C<='0';elsif CLK'event and CLK='1' thenif LD='0' then q1<=D;C<='0';elsif EN1='1' thenif Q1="1001" then Q1<="0000";C<='1';else Q1<=Q1+1;end if;end if;end if;end process;Q<=Q1;end ls;顶层文件:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity shijingzhi isport(CLR,LD,CLK:in std_logic;EN:in std_logic_vector(1 downto 0);D:in std_logic_vector(3 downto 0);Q:out std_logic_vector(3 downto 0);C:out std_logic);end entity shijingzhi;architecture ls of shijingzhi iscomponent sjzport(CLR,LD,CLK:in std_logic;EN:in std_logic_vector(1 downto 0);D:in std_logic_vector(3 downto 0);Q:out std_logic_vector(3 downto 0);C:out std_logic);end component;component fenpinport(clk:in std_logic;qout:buffer std_logic);end component;signal clk1:std_logic;beginu1:sjz port map(CLK=>clk1,LD=>LD,CLR=>CLR,EN=>EN,D=>D,Q=>Q,C=>C); u2:fenpin port map(CLK=>clk,qout=>clk1);end ls;扫描显示电路:分频:library ieee;use ieee.std_logic_1164.all;entity fenpin isport(clk:in std_logic;qout:buffer std_logic);end;architecture behave of fenpin isbeginprocess(clk)variable num: integer :=1;beginif falling_edge(clk)then if num=4000then num:=1;qout<=not qout;else num:=num+1;end if;end if;end process;end behave;七段译码:library ieee;use ieee.std_logic_1164.all;entity qiduan isport(din:in std_logic_vector(3 downto 0);led7:out std_logic_vector(6 downto 0) );end ;architecture behave of qiduan isbeginprocess(din)begincase din iswhen "0000" => led7<="0111111";when "0001" => led7<="0000110";when "0010" => led7<="1011011";when "0011" => led7<="1001111";when "0100" => led7<="1100110";when "0101" => led7<="1101101";when "0110" => led7<="1111101";when "0111" => led7<="0000111";when "1000" => led7<="1111111";when "1001" => led7<="1101111";when "1010" => led7<="1110111";when "1011" => led7<="1111100";when "1100" => led7<="0111001";when "1101" => led7<="1011110";when "1110" => led7<="1111001";when "1111" => led7<="1110001";when others => null;end case;end process;end behave;计数器:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity counter8 isport(clk: in std_logic;count: out std_logic_vector(2 downto 0);sel: out std_logic_vector(3 downto 0)); end counter8;architecture behave of counter8 isbeginprocess(clk)variable cnt: integer :=0;beginif rising_edge(clk)thenif cnt=7then cnt:=0;else cnt:=cnt+1;end if;end if;case cnt iswhen 0 => count<="111";sel<="0001";when 1 => count<="110";sel<="0010";when 2 => count<="101";sel<="0011";when 3 => count<="100";sel<="0100";when 4 => count<="011";sel<="0101";when 5 => count<="010";sel<="0110";when 6 => count<="001";sel<="0111";when 7 => count<="000";sel<="1000";when others => null;end case;end process;end behave;顶层文件:library ieee;use ieee.std_logic_1164.all;entity shumaguan isport(clk:in std_logic;duan:out std_logic_vector(6 downto 0);wei:out std_logic_vector(2 downto 0));end ;architecture behave of shumaguan iscomponent qiduanport(din:in std_logic_vector(3 downto 0);led7:out std_logic_vector(6 downto 0) );end component;component counter8port(clk: in std_logic;count: out std_logic_vector(2 downto 0);sel: out std_logic_vector(3 downto 0));end component;component fenpinport(clk:in std_logic;qout:buffer std_logic);end component;signal duan1:std_logic_vector(3 downto 0);signal clks:std_logic;beginu1: qiduan port map(led7=>duan,din=>duan1);u2: counter8 port map(count=>wei,sel=>duan1,clk=>clks);u3: fenpin port map(clk=>clk,qout=>clks);end behave;交通灯:计数器:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity counter8 isport(clk:in std_logic;counter:out std_logic_vector(2 downto 0));end entity counter8;architecture bhv of counter8 issignal counter1:std_logic_vector(2 downto 0); beginprocess (clk)beginif clk'event and clk='1' thenif counter1="001" then counter1<="000";else counter1<=counter1 +1;end if;end if;end process;counter<=counter1;end architecture bhv;七段译码器:library ieee;use ieee.std_logic_1164.all;entity seg7 isport(din:in std_logic_vector(3 downto 0);led7:out std_logic_vector(6 downto 0) );end seg7;architecture behave of seg7 isbeginprocess(din)begincase din iswhen "0000" => led7<="0111111";when "0001" => led7<="0000110";when "0010" => led7<="1011011";when "0011" => led7<="1001111";when "0100" => led7<="1100110";when "0101" => led7<="1101101";when "0110" => led7<="1111101";when "0111" => led7<="0000111";when "1000" => led7<="1111111";when "1001" => led7<="1101111";when "1010" => led7<="1110111";when "1011" => led7<="1111100";when "1100" => led7<="0111001";when "1101" => led7<="1011110";when "1110" => led7<="1111001";when "1111" => led7<="1110001";when others => null;end case;end process;end behave;分频library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity fenpin isgeneric(N:integer:=50000);port(clk:in std_logic;q:buffer std_logic);end entity fenpin;architecture bhv of fenpin isbeginprocess (clk)variable a1:integer:=N-1 ;beginif rising_edge(clk) thenif a1=N-1 then a1 :=0;q<=not q;else a1 :=a1+1;end if;end if;end process;end architecture bhv;顶层文件:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--实体的说明entity jiaotongdeng isport (clk:in std_logic;--内部信号的输入rst:in std_logic;--复位--数码的输入segout:out std_logic_vector(6 downto 0);--七段译码器的输出counter:buffer std_logic_vector(2 downto 0); --8进制计数器的输出q:out std_logic_vector(11 downto 0));end;--结构体说明architecture bhv of jiaotongdeng iscomponent fenpin --分频generic(N:integer);port(clk:in std_logic;q:buffer std_logic);end component ;component seg7 -- 七段译码器port(din:in std_logic_vector(3 downto 0);led7:out std_logic_vector(6 downto 0));end component ;component counter8 --8进制port(clk:in std_logic;counter:out std_logic_vector(2 downto 0));end component ;--中间信号signal bcdin:std_logic_vector(3 downto 0);signal number1: std_logic_vector(3 downto 0);signal number2: std_logic_vector(3 downto 0);signal clk1: std_logic;--100HZsignal clk2: std_logic;--1HZtype state_value is( s1,s2,s3,s4);signal state:state_value;begin--各元件的端口连接关系M1 :fenpin generic map(N=>30000) port map(clk,clk1);--100HZM2 :fenpin generic map(N=>10000000) port map(clk,clk2); --1HZM3 :counter8 port map(clk1,counter);G1 :seg7 port map(bcdin,segout);process(rst,clk2)beginif rst='0' then state <= s1; number2<="0010";number1<="0000";q<="100001100001";elsif rising_edge(clk2) thencase state iswhen s1 =>if number2 ="0000" thenif number1 ="0000" then state <= s2; q<="100010100010";number2<="0000";number1<="0011";else number1<=number1-1;end if;elsif number1="0000" then number2<=number2-1;number1<="1001";else number1 <= number1 - 1;end if ;when s2 =>if number1 ="0000" then state <= s3; q<="001100001100";number2<="0010";number1<="0000";else number1<=number1-1;end if ;when s3 =>if number2 ="0000" thenif number1 ="0000" then state <= s4; q<="010*********";number2<="0000";number1<="0011";else number1<=number1-1;end if;elsif number1="0000" then number2<=number2-1;number1<="1001";else number1 <= number1 - 1;end if ;when s4 =>if number1 ="0000" then state <= s1; q<="100001100001";number2<="0010";number1<="0000";else number1<=number1-1;end if ;end case;end if;end process;process(counter)--每一位对应的数值begincase counter iswhen "000"=>bcdin<=number1;when "001"=>bcdin<=number2;when others=>null;end case;end process;end bhv;数字钟:拨码开关:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all; entity boma isport( clk : in std_logic ;kaiguan : in std_logic;q :buffer std_logic);end entity;architecture bhv of boma is type state_value is( s0,s1,s2,s3); signal state:state_value;beginprocess( clk ,state)beginif rising_edge(clk) thencase state iswhen s0 =>if kaiguan = '0' thenstate <= s1;else state <= s0;end if;when s1 =>if kaiguan = '1' thenstate<= s2;else state<= s1;end if;when s2 =>if kaiguan= '1' thenstate<= s3;else state <= s1;end if;when s3 =>if kaiguan = '0' thenstate <= s0;q<=not q;end if;end case;end if;end process;end bhv;分频:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity fenpin isgeneric(N:integer:=10000000);port(clk:std_logic;q:buffer std_logic);end fenpin;architecture behave of fenpin isbeginprocess(clk)variable a:integer:=N-1;beginif rising_edge(clk) thenif a=N-1 then a:=0;q<=not q;else a:=a+1;end if;end if;end process;end behave;计数器:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;use ieee.std_logic_arith.all;entity counter8 isport(clk:in std_logic;counter:out std_logic_vector(2 downto 0));end entity counter8;architecture bhv of counter8 issignal counter1:std_logic_vector(2 downto 0); beginprocess (clk)beginif clk'event and clk='1' thenif counter1="101" then counter1<="000";else counter1<=counter1 +1;end if;end if;end process;counter<=counter1;end architecture bhv;七段译码器:library ieee;use ieee.std_logic_1164.all;entity seg7 isport(din:in std_logic_vector(3 downto 0);led7:out std_logic_vector(6 downto 0)); end seg7;architecture behave of seg7 isbeginprocess(din)begincase din iswhen "0000" => led7<="0111111";when "0001" => led7<="0000110";when "0010" => led7<="1011011";when "0011" => led7<="1001111";when "0100" => led7<="1100110";when "0101" => led7<="1101101";when "0110" => led7<="1111101";when "0111" => led7<="0000111";when "1000" => led7<="1111111";when "1001" => led7<="1101111";when "1010" => led7<="1110111";when "1011" => led7<="1111100";when "1100" => led7<="0111001";when "1101" => led7<="1011110";when "1110" => led7<="1111001";when "1111" => led7<="1110001";when others => null;end case;end process;end behave;顶层文件:--库文件的调用library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;--实体的说明entity shuzizhong isport (clk:in std_logic;--内部信号的输入kaiguan1:in std_logic;--拨码开关1,作用启动数码的校准kaiguan2:in std_logic;--拨码开关2,小时校准kaiguan3:in std_logic;--拨码开关3,分校准kaiguan4:in std_logic;--拨码开关4,秒校准c:out std_logic; --蜂鸣器的输入端--数码的输入segout:out std_logic_vector(6 downto 0);--七段译码器的输出counter:buffer std_logic_vector(2 downto 0) --8进制计数器的输出);end shuzizhong;--结构体说明architecture bhv of shuzizhong iscomponent fenpin --分频generic(N:integer);port(clk:in std_logic;q:buffer std_logic);end component ;component seg7 -- 七段译码器port(din:in std_logic_vector(3 downto 0);led7:out std_logic_vector(6 downto 0));end component ;component counter8 --8进制port(clk:in std_logic;counter:out std_logic_vector(2 downto 0));end component ;component boma --拨码port ( clk: in std_logic;kaiguan:in std_logic;q: buffer std_logic);end component ;--中间信号signal bcdin:std_logic_vector(3 downto 0);signal number1: std_logic_vector(3 downto 0);signal number2: std_logic_vector(3 downto 0);signal number3: std_logic_vector(3 downto 0);signal number4: std_logic_vector(3 downto 0);signal number5: std_logic_vector(3 downto 0);signal number6: std_logic_vector(3 downto 0);signal clk1: std_logic;--1000HZsignal clk2: std_logic;--500HZsignal clk3: std_logic;--100HZsignal clk4: std_logic;--1HZsignal a1: std_logic;--拨码开关1产生的相应信号signal a2: std_logic;--拨码开关2产生的相应信号signal a3: std_logic;--拨码开关3产生的相应信号signal a4: std_logic;--拨码开关4产生的相应信号begin--各元件的端口连接关系M1 :fenpin generic map(N=>10000) port map(clk,clk1);--1000HZM2 :fenpin generic map(N=>20000) port map(clk,clk2); --500HZM3 :fenpin generic map(N=>30000) port map(clk,clk3); --100HZM4 :fenpin generic map(N=>10000000) port map(clk,clk4); --1HZM5 :counter8 port map(clk2,counter);B1:boma port map(clk3,kaiguan1,a1);B2:boma port map(clk3,kaiguan2,a2);B3:boma port map(clk3,kaiguan3,a3);B4:boma port map(clk3,kaiguan4,a4);G1 :seg7 port map(bcdin,segout);process(a1,number1,number2,number3,number4) --蜂鸣器的鸣叫beginif a1='0' thenif number4="0101" thenif number3="1001" thenif number2="0101" thenif (number1 and"0001")="0000"then c<=clk2;end if;end if;end if;end if;if(number1="0000" and number2="0000" and number3="0000" andnumber4="0000") then c<=clk1;end if;end if;end process;process(clk4,a1,a2,a3,a4)--数字钟的显示beginif rising_edge(clk4) thenif a1='0' thenif number1="1001" thenif number2="0101" thennumber1<="0000";number2<="0000";number3<=number3+1;if number3="1001" thennumber3<="0000";number4<=number4+1;if number4="0101" thennumber4<="0000"; number3<="0000";number5<=number5+1;if number5="0011" thenif number6="0010" thennumber5<="0000";number6<="0000";end if;elsif number5="1001" thennumber5<="0000";number6<=number6+1;end if;end if;end if;else number1<="0000";number2<=number2+1;end if;else number1<=number1+1;end if;--拨码开关的相应操作elsif a2='1'then --小时的校准if number6= "0010" thenif number5="0011" then number5<="0000";number6<="0000";else number5<=number5+1;end if;elsif number5="1001" thennumber5<="0000";number6<=number6+1;else number5<=number5+1;end if;elsif a3='1' then --分的校准if number4="0101" thenif number3="1001" then number3<="0000" ;number4<="0000" ;else number3<=number3+1;end if;elsif number3="1001" thennumber3<="0000";number4<=number4+1;else number3<=number3+1;end if;elsif a4='1'then --秒的校准number1<="0000";number2<="0000";end if;end if;end process;process(counter)--每一位对应的数值begincase counter iswhen "000"=>bcdin<=number1;when "001"=>bcdin<=number2;when "010"=>bcdin<=number3;when "011"=>bcdin<=number4;when "100"=>bcdin<=number5;when "101"=>bcdin<=number6;when others=>null;end case;end process;end bhv;点阵:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity div isport(clk20m :in std_logic;clkn :out std_logic);end div;architecture bhv of div isconstant div_num :integer :=20000 ;signal n1 :std_logic_vector(24 downto 0); beginprocess(clk20m)beginif rising_edge(clk20m) thenif n1=div_num thenn1<=(others=>'0');else n1<=n1+1;end if;if n1<div_num/2 thenclkn<='0';else clkn<='1';end if;end if;end process;end bhv;16进制:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity cnt16 isport(clkn :in std_logic;bcd_out1 :out std_logic_vector(3 downto 0);bcd_out2 :out std_logic_vector(3 downto 0));end cnt16;architecture bhv of cnt16 issignal q_s :std_logic_vector(3 downto 0); beginprocess(clkn)beginif rising_edge(clkn)thenif q_s<15 thenq_s<=q_s+1;else q_s<="0000";end if;end if;end process;bcd_out1<=q_s;bcd_out2<=q_s;end bhv;点阵:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_unsigned.all;entity dianzhen isport(bcd_in :in std_logic_vector(3 downto 0);q :out std_logic_vector(15 downto 0));end dianzhen;architecture bhv of dianzhen isbeginprocess(bcd_in)begincase bcd_in iswhen "0000" =>q<="1111111111111111";when "0001" =>q<="1111111111111111";when "0010" =>q<="1111111111111111";when "0011" =>q<="1111111111111111";when "0100" =>q<="1111111111111111";when "0101" =>q<="1111111111111111";。

EDA实验1-4

EDA实验1-4本科实验报告课程名称: CPLD/FPGA应用设计实验项目: 1位全加器 2位10进制计数器显示译码器 4位加法计数器实验地点:矿院楼二层EDA实验室专业班级:电子信息工程1101班学号:学生姓名:年月日本科实验报告课程名称: CPLD/FPGA应用设计实验项目: 1位全加器实验地点:矿院楼二层EDA实验室专业班级:电子信息工程1101班学号:学生姓名:年月日实验一 1位全加器一、实验目的1、熟悉ispDesignEXPERT System 、Quartus 原理图设计流程的全过程。

2、学习简单组合电路的设计方法、输入步骤。

3、学习层次化设计步骤。

4、学习EDA 设计的仿真和硬件测试方法。

二、实验原理1位全加器可以由图1那样用两个半加器及一个或门连接而成,因此需要首先完成图2所示的半加器设计。

要求使用原理图输入的方法先进行底层半加器设计,再建立上层全加器设计文件,调用半加器和或门符号,连接完成原理图设计。

图1 - 全加器原理图图2 - 半加器原理图三、实验任务1、用原理图输入方法设计半加器电路。

2、对半加器电路进行仿真分析、引脚锁定、硬件测试。

3、建立顶层原理图电路。

4、对全加器电路进行仿真分析、引脚锁定、硬件测试 四、实验步骤1、建立设计工程打开Quartus Ⅱ6.0软件,新建项目,选择file —new project wizard 命令,指定工程的工作目录,工程名及顶层实体名,并选择FPGA 器件EP1C12Q240C8。

2、原理图源文件输入: a 、新建原理图输入源文件选择file —new 命令,在【New 】对话框中选择Design Files —BlockVCCainINPUT VCCbinINPUT VCCcinINPUT coutOUTPUT sumOUTPUTA BCO SObanjiaqi instA BCO SObanjiaqiinst3OR2inst4P IN_2P IN_3P IN_4P IN_5P IN_6VCCAINPUT VCCBINPUT COOUTPUT SOOUTPUT AND2instNOT inst2XNORinst3P IN_15P IN_16P IN_20P IN_21Diagram/Schematic File 原理图文件输入。

EDA示例汇集

方法二:用键盘直接 输入所需元件名,再 单击“OK”按钮即可将 元件调入原理图编辑 窗中。

2018/12/10

湖北众友科技EDA工作室

11

步骤2:输入设计项目和存盘 (5)排列好调入的元件,连接好原理图。

A

B

连线方法:把鼠标放在 A 处变成十字形, 按处左键保持十字形移至 B 处松开即完成 连接。

输入设计项目和存盘用户工作库末存盘时为默认文件夹此处已存盘到自己建立的文件夹元件符号名输入区可直接输入所需元件的符号名库选择区软件安装在d盘maxplus2文件夹下除了用户工作库外件夹下除了用户工作库外还有四种元件库包含了基本逻辑元件库prim如门触发器等

EDA技术教学系列

EDA 示 例 汇 集

基于EDA-E的实验例程

2018/12/10

湖北众友科技EDA工作室

12

步骤2:输入设计项目和存盘 (6)分别在input和output的PIN_NAME上双击使其变黑色, 再用键盘分别输入各引脚名:a、b、co、so。

半加器表达式:

进位:co=a and b

和: so=a xnor (not b)

注意:半加器用原理图的实现方法很多,此处用同或的方 法来实现。有兴趣的同学可以用其它的方法来实现。

2018/12/10 湖北众友科技EDA工作室 24

步骤5:时序仿真 (3) 设 置 波 形 参 量 。 在 “ Option” 菜 单 中 消 去 网 格 对 齐 项 “Snap to Grid”的对勾,以便能够任意设置输入电平位置, 或设置输入时钟信号的周期。

2018/12/10

湖北众友科技EDA工作室

设置后

步骤4:选择目标器件并编译 (1)选择“Assign”菜单中“Device”项,弹出Device对话框 。

EDA含有(程序-示例图全套)实验报告(吐血推荐)

实验报告(2012----2013学年第一学期)课程名称:EDA技术专业班级:学号:姓名:实验一:原理图输入法设计与仿真实验时间:2012年10月19日(第七周)六、实验心得实验二七人表决器的设计3、引脚匹配实验三 显示电路设计一、实验目的1、学习7段数码显示译码器设计;2、学习VHDL 的多层设计方法。

二、实验仪器设备1、PC 机一台2、GW48-PK2系列SOPC/EDA 实验开发系统 三、实验原理1、七段数码显示工作原理(共阴极接法)7 段数码是纯组合电路,通常的小规模专用IC ,如74 或4000系列的器件只能作十进制BCD 码译码,然而数字系统中的数据处理和运算都是2 进制的,所以输出表达都是16 进制的,为了满足16 进制数的译码显示,最方便的方法就是利用译码程序在FPGA/CPLD 中来实现。

作为7 段译码器,输出信号LED7S 的7 位分别接数码管的7 个段,高位在左,低位在右。

例如当LED7S 输出为“1101101”时,数码管的7 个段:g 、f 、e 、d 、c 、b 、a 分别接1、1、0、1、1、0、1;接有高电平的段发亮,于是数码管显示“5”。

注意,这里没有考虑表示小数点的发光管,如果要考虑,需要增加段h 。

2、显示代码概念 显示代码a b cdefg四、实验内容1、编写7段译码器VHDL 源程序。

2、在Quartus Ⅱ软件上编译和仿真。

3、锁定管脚,建议选择实验电路模式6,显示译码输出用数码8 显示译码输出(PIO46-PIO40),键8、键7、键6 和键5 四位控制输入。

4编程下载与硬件验证。

5、记录系统仿真和硬件验证结果。

五、实验结果:2、波形仿真图:4、 引脚锁定:六、实验心得: 其实本实验的显示我们在模电里面就学习过了,也用集成块进行过实验,本实验用程序加硬件完成。

真所谓条条道路通罗马!实验四 四位全加器一、实验目的通过实验让学生熟悉Quartus Ⅱ的VHDL 文本设计流程全过程,掌握组合逻辑电路的文本输入设计法,通过对设计电路的仿真和硬件验证,让学生进一步了解加法器的功能。

EDA技术实验报告完整版

福建农林大学金山学院信息工程类实验报告课程名称:EDA技术姓名:邱彬彬系:信息与机电工程系专业:电子信息工程专业年级:2010级学号:100201079指导教师:蔡剑卿职称:讲师2013年05月03日实验项目列表福建农林大学金山学院信息工程类实验报告系:信息与机电工程系专业:电子信息工程年级: 2010级姓名:邱彬彬学号: 100201079 实验课程: EDA技术实验室号:__田实405 实验设备号: 2B 实验时间: 2013年4月13日指导教师签字:成绩:实验一Quartus II 9.0软件的使用1.实验目的和要求本实验为验证性实验,其目的是熟悉Quartus II 9.0软件的使用,学会利用Quartus II 9.0软件来完成整个EDA开发的流程。

2.实验原理利用VHDL完成电路设计后,必须借助EDA工具中的综合器、适配器、时序仿真器和编程器等工具进行相应的处理后,才能使此项设计在FPGA上完成硬件实现,并得到硬件测试,从而使VHDL设计得到最终的验证。

Quartus II是Altera提供的FPGA/CPLD开发集成环境,包括模块化的编译器,能满足各种特定设计的需要,同时也支持第三方的仿真工具。

3.主要仪器设备(实验用的软硬件环境)实验的硬件环境是:微机一台GW48 EDA实验开发系统一套电源线一根十芯JTAG口线一根USB下载线一根USB下载器一个实验的软件环境是:Quartus II 9.0软件4.操作方法与实验步骤利用Quartus II 9.0软件实现EDA的基本设计流程:创建工程、编辑文本输入设计文件、编译前设置、全程编译、功能仿真。

利用Quartus II 9.0软件实现引脚锁定和编译文件下载。

利用Quartus II 9.0软件实现原理图输入设计文件的编辑和产生相应的原理图符号元件。

5.实验内容及实验数据记录安装QUARTUSII软件;因为实验时我的机器了已经有QUARTUSII软件,所以我并没有进行安装软件的操作。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

用CA SE语句描述4选1多路选择器。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY MUX41 ISPORT(S1,S2:IN STD_LOGIC;A,B,C,D:IN STD_LOGIC;Z:OUT STD_LOGIC);END ENTITY MUX41;ARCHITECTURE ART OF MUX41 ISSIGNAL S :STD_LOGIC_VECTOR(1 DOWNTO 0);BEGINS<=S1 & S2;PROCESS(S1,S2,A,B,C,D)BEGINCASE S I SWHEN "00"=>Z<=A;WHEN "01"=>Z<=B;WHEN "10"=>Z<=C;WHEN "11"=>Z<=D;WHEN OTHERS =>Z<='X';END CASE;END PROCESS;END ART;END ART1;三八译码器方法1:使用IF语句LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY ENCODER ISPORT(IN1:IN STD_LOGIC_VECTOR(7 DOWNTO 0);OUT1:OUT STD_LOGIC_VECTOR(2 DOWNTO 0));END ENCODER;ARCHITECTURE ART3 OF ENCODER ISBEGINPROCESS(INT1)BEGINIF IN1(7)=…1‟ THEN OUT1<="111";ELSIF IN1(6)=…1‟ THEN OUT1<="110";ELSIF IN1(5)=…1‟ THEN OUT1<="101";ELSIF IN1(4)=…1‟ THEN OUT1<="100";ELSIF IN1(3)=…1‟ THEN OUT1<="011";ELSIF IN1(2)=…1‟ THEN OUT1<="010";ELSIF IN1(1)=…1‟ THEN OUT1<="001";ELSIF IN1(0)=…1‟ THEN OUT1<="000";ELSE OUT1<="XXX";END IF ;END PROCESS;END ART3;【例4.23】T触发器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY TCFQ ISPORT(T,CLK:IN STD_LOGIC;Q:BUFFER STD_LOGIC);END TCFQ;ARCHITECTURE ART OF TCFQ ISBEGINPROCESS(CLK)BEGINIF (CLK'EVENT AND CLK=…1‟)THENQ<=NOT(Q);ELSE Q<=Q;END IF;END PROCESS;END ART;比较器ENTITY COMP_BAD ISPORT( a1,b1 : IN BIT;q1 : OUT BIT );END ;ARCHITECTURE one OF COMP_BAD ISBEGINPROCESS (a1,b1)BEGINIF a1 > b1 THEN q1 <= '1' ;ELSIF a1 < b1 THEN q1 <= '0' ;-- 未提及当a1=b1时,q1作何操作END IF;END PROCESS ;END ;【例 4.9】8位数值比较器的VHDL描述LIBRARY IEEE;USE IEEE.STD_LOGIC_VECTOR(7 DOWNTO 0);ENTITY COMPARE ISPORT (A,B:IN STD_LOGIC_VECTOR(7 DOWNTO 0);EQ:OUT STD_LOGIC);END COMPARE;ARCHITECTURE ART OF COMPARE ISBEGINEQ <=…1‟WHEN A=B ELSE …0‟;END ART;计数器LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNT10 ISPORT (CLK,RST,EN : IN STD_LOGIC;CQ : OUT STD_LOGIC_VECTOR(3 DOWNTO 0);COUT : OUT STD_LOGIC );END CNT10;ARCHITECTURE behav OF CNT10 ISBEGINPROCESS(CLK, RST, EN)V ARIABLE CQI : STD_LOGIC_VECTOR(3 DOWNTO 0);BEGINIF RST = '1' THEN CQI := (OTHERS =>'0') ; --计数器异步复位ELSIF CLK'EVENT AND CLK='1' THEN --检测时钟上升沿IF EN = '1' THEN --检测是否允许计数(同步使能)IF CQI < 9 THEN CQI := CQI + 1; --允许计数, 检测是否小于9ELSE CQI := (OTHERS =>'0'); --大于9,计数值清零END IF;END IF;END IF;IF CQI = 9 THEN COUT <= '1'; --计数大于9,输出进位信号ELSE COUT <= '0';END IF;CQ <= CQI; --将计数值向端口输出END PROCESS;END behav;1. 同步计数器【例 4.32】一个模为60,具有异步复位、同步置数功能的8421BCD码计数器。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;USE IEEE.STD_LOGIC_UNSIGNED.ALL;ENTITY CNTM60 ISPORT(CI:IN STD_LOGIC;NRESET:IN STD_LOGIC;LOAD:IN STD_LOGIC;D:IN STD_LOGIC_VECTOR(7 DOWNTO 0);CLK:IN STD_LOGIC;CO:OUT STD_LOGIC;QH:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0);QL:BUFFER STD_LOGIC_VECTOR(3 DOWNTO 0));END CNTM60;ARCHITECTURE ART OF CNTM60 ISBEGINCO<=…1‟WHEN(QH="0101"AND QL="1001"AND CI=…1‟)ELSE'0';--进位输出的产生PROCESS(CLK,NRESET)BEGINIF(NRESET=…0‟)THEN --异步复位QH<="0000";QL<="0000";ELSIF(CLK'EVENT AND CLK=…1‟)THEN --同步置数IF(LOAD=…1‟)THENQH<=D(7 DOWNTO 4)Q L<=D(3 DOWNTO 0);ELSIF(CI=…1‟)THEN --模60的实现IF(QL=9)THENQL<="0000";IF(QH=5)THENQH<="0000";ELSE --计数功能的实现QH<=QH+1;END IFELSEQL<=QL+1;END IF;END IF;--END IF LOAD END PROCESS;END ART;一个由8个触发器构成的异步计数器,采用元件例化的方式生成。

LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY DIFFR ISPORT(CLK,CLR,D:IN STD_LOGIC;Q,QB;OUT STD_LOGIC);END DIFFR;ARCHITECTURE ART1 OF DIFFR ISSIGNAL Q_IN:STD_LOGIC;BEGINQ<=Q_IN;QB<=NOT Q_IN;PROCESS(CLK,CLR)BEGINIF(CLR=…1‟)THENQ_IN<=…0‟;ELSIF (CLK'EVENT AND CLK=…1') THENQ_IN<=D;END IF;END PROCESS;END ART1;LIBRARY IEEE;USE IEEE.STD_LOGIC_1164.ALL;ENTITY RPLCOUNT ISPORT(CLK,CLR:IN STD_LOGIC;COUNT:OUT STD_LOGIC_VECTOR(7 DOWNTO 0));END RPLCOUNT;ARCHITECTURE ART2 OF RPLCOUNT ISSIGNAL COUNT_IN:STD_LOGIC_VECTOR(8 DOWNTO 0);COMPONENT DIFFRPORT(CLK,CLR,D:IN STD_LOGIC;Q,QB:OUT STD_LOGIC);END COMPONENT;BEGINCOUNT_IN(0)<=CLK;GEN1:FOR I IN 0 TO 7 GENERA TEU:DIFFR PORT MAP(CLK=>COUNT_IN(I),CLR=>CLR,D=>COUNT_IN(I+1),Q=>COUNT_IN(I),QB=>COUNT_IN(I+1));END GENERA TE;END ART2;4.18 8421编码的异步十进制减法计数器源程序:library ieee;use ieee.std_logic_1164.all;use ieee.std_logic_arith.all;use ieee.std_logic_unsigned.all;entity h36 isport(cp:in std_logic;q:out std_logic_vector(3 downto 0);end h36;architecture w of h36 istype state is(s0,s1,s2,s3,s4,s5,s6,s7,s8,s9);signal p:state;signal n:state;signal qn:std_logic_vector(3 downto 0);beginprocess(cp)beginif cp\'event and cp=\'1\'thenp<=n;end if;end process;process(p)begincase p iswhen s0=>n=<=s1;qn<=\"1001\";when s1=>n=<=s2;qn<=\"1000\";when s2>n=<=s3;qn<=\"0111\";when s3=>n=<=s4;qn<=\"0110\";(when s4=>n=<=s5;qn<=\"0101\";when s5=>n=<=s6;qn<=\"0100\";when s6=>n=<=s7;qn<=\"0011\";when s7=>n=<=s8;qn<=\"0010\";when s8=>n=<=s9;qn<=\"0001\";when s9=>n=<=s0;qn<=\"0000\";when other=>n=<=s0;end case;end pricess;q<=qn;end w;【例 4.34】用VHDL 描述的8位二进制加减计数器源程序。