基于固件的系统芯片协同验证平台

DesignWare超高速USB 3.0 IP说明书

白皮书DesignWare超高速USB 3.0 IP要点``支持超高速USB (USB3.0)和高速USB (USB2.0)``针对USB C-类的连接性和USB 的产品规格对DesignWare USB-C™3.1 物理层进行了优化``双重角色设备(DRD)、主机、从设备,控制器提供了全方位的USB 性能特点``支持PIPE、UTMI+和ULPI 物理层接口``架构特征降低耗电量``超高速USB 对控制器和物理层进行了徽标认证``SuperSpeed USB IP 连续13 年市场占有率第一,来自(Gartner 2015)应用目标``智能手机``平板电脑、超级笔记本、网络本``游戏``数码相机与摄影机``存储``无线通信``机顶盒科技``领先的工艺技术,支持工艺从130nm到最新14/16nm 鳍场效应管工艺概述DesignWare®超高速USB IP解决方案是建立在USB开发者论坛中USB 3.0的产品规格基础之上的。

全面的超高速USB IP提供包括主机、设备、双重角色设备控制器、支持或不支持USB C-类TM连接技术规格的物理层、验证IP、IP原型设计套件,和IP软件开发工具。

这些IP能快速发展先进的晶片设计与5.0 Gbps超高速USB标准的结合。

DesignWare超高速USB IP的目标是将Soc芯片集成到用于媒体存储、创作与回放设备中,这就要求较高的接口带宽以保证个人电脑与可携式电子装置之间设实现更快的“同步转发”。

DesignWare超高速USB数字控制器和物理层能使超高速USB在电量较低的情况下完成最快速度的数据传输。

作为USB IP领先的供应商,新思科技(Synopsys)为客户提供了一批高绩效的设计师,提供了一个低功耗、面积优化的IP解决方案,以提高系统晶片设计的成本效率。

新思科技专门发展并支持USB与高速串行解串器构架,帮助客户建立一个低风险、高质量的超高速USB IP解决方案。

智能网联汽车软件在线升级安全风险分析及管理对策建议

智能网联是我国汽车产业重大战略方向,软件定义汽车成为行业发展方向的重要特征。

智能网联汽车软件在线升级可实现全新功能导入、产品性能迭代、用户体验改善,具备经济、高效的显著特征。

近年来,在应用规模、范围等方面均大幅提升。

但是,汽车软件在线升级涉及升级前、升级中、升级后过程状态,对原有汽车管理模式带来新的挑战,需要综合分析国内外汽车创新管理经验,针对智能网联汽车软件在线升级潜在的安全风险,从管理方面提出针对性对策建议。

1 引言远程在线升级(Over-The-Air,OTA)是基于移动通信网络接口完成对移动终端产品的软件数据升级管理的技术,包含软件远程升级(Software Over The Air, SOTA)和固件远程升级(Firmware Over The Air,FOTA),主要用于智能手机行业。

对于汽车行业而言,2000年后,日本汽车制造厂商开始对配置T-BOX车载控制单元的汽车进行T-BOX系统的OTA远程升级。

在此以后,部分汽车制造厂商开始对具备远程通信功能的车载信息娱乐系统(In-Vehicle Infotainment,IVI)进行OTA远程升级,如导航地图、应用音乐等,从OTA远程升级的功能内容范围分析,此时汽车行业主要针对车载信息娱乐系统和简单的电器部件控制功能,属于SOTA 的范畴。

从汽车OTA 远程升级更新内容上分析,特斯拉Model S是一款真正搭载FOTA技术的汽车,通过远程升级修复安全漏洞、提升产品性能、改善用户体验。

自2018年以来,国内汽车OTA远程升级在功能搭载率、升级内容等方面均实现快速提升,OTA 远程升级发展逐渐扩大化,并催生一批功能选装、硬件免费+软件收费等新型商业模式。

由于智能化、网联化技术的赋能,OTA 远程升级技术将成为未来汽车产品软件数据更新的主要方式,逐渐成为汽车智能化、网联化的标准配置,汽车产业将迎来“越用越新”的时代。

其中UN Regulation No.155 和UN Regulation No.156 法规要求销售到58 协约国的汽车制造企业必须获得政府监管部门的汽车信息安全管理认证和汽车软件升级管理体系认证,汽车软件升级管理体系认证要求汽车制造企业从软件更新过程,软件更新的安全性要求、已安装软件的标识等方面建立软件升级管理体系,政府监管部门会保持认证结果不定期复审。

芯片验证平台搭建流程

温馨小提示:本文主要介绍的是关于芯片验证平台搭建流程的文章,文章是由本店铺通过查阅资料,经过精心整理撰写而成。

文章的内容不一定符合大家的期望需求,还请各位根据自己的需求进行下载。

本文档下载后可以根据自己的实际情况进行任意改写,从而已达到各位的需求。

愿本篇芯片验证平台搭建流程能真实确切的帮助各位。

本店铺将会继续努力、改进、创新,给大家提供更加优质符合大家需求的文档。

感谢支持!(Thank you for downloading and checking it out!)阅读本篇文章之前,本店铺提供大纲预览服务,我们可以先预览文章的大纲部分,快速了解本篇的主体内容,然后根据您的需求进行文档的查看与下载。

芯片验证平台搭建流程(大纲)一、前期准备工作1.1了解项目需求1.2确定验证目标1.3选择合适的硬件和软件平台二、搭建硬件环境2.1硬件选型2.2硬件连接三、搭建软件环境3.1选择合适的开发工具3.2配置开发环境四、编写验证代码4.1设计测试向量4.2编写测试平台五、执行验证流程5.1功能验证5.2性能验证5.3电源和热分析六、问题定位和调试6.1分析错误和失败原因6.2调试代码和硬件6.3优化验证流程七、编写验证报告7.1汇总验证结果7.2分析验证覆盖率7.3提出改进建议八、后续工作8.1验证平台维护和更新8.2跟进项目进度,为后续验证提供支持8.3总结经验,提高验证效率和质量一、前期准备工作1.1了解项目需求在芯片验证平台搭建流程的第一步,我们需要充分了解项目需求。

这包括了解芯片的功能、性能、接口以及其他相关特性。

可以通过查阅芯片规格说明书、设计文档、参考手册等资料来获取这些信息。

此外,还需要了解项目的验证范围、验证策略、验证周期等要求,以确保验证平台的搭建能够满足项目的需求。

1.2确定验证目标在了解项目需求的基础上,我们需要明确验证目标。

验证目标包括验证芯片的功能是否符合规格要求、性能是否达到预期、接口是否正常通信等。

基于RoCE V2的SmartNIC芯片设计与验证

基于RoCE V2的SmartNIC芯片设计与验证基于RoCE V2的SmartNIC芯片设计与验证随着云计算和大数据时代的到来,数据中心网络的带宽需求不断增长。

为了满足高带宽和低延迟的要求,传统的以太网协议已经无法满足需求。

为了提高数据中心网络的性能,远程直接内存访问(Remote Direct Memory Access,简称RDMA)技术被引入。

RDMA技术可以绕过传统的协议栈,将数据直接从发送端的内存传输到接收端的内存,而不需要CPU的干预。

这样可以大大减少数据传输的延迟和CPU的负载。

而RoCE(RDMA over Converged Ethernet)是一种基于以太网的RDMA技术,其中RoCE V2是RoCE的第二个版本。

基于RoCE V2的SmartNIC芯片是在传统的网络接口控制器(Network Interface Controller,简称NIC)芯片的基础上增加了RDMA功能。

SmartNIC芯片具有自主处理RDMA数据包的能力,可以极大提高数据中心网络的性能。

SmartNIC芯片的设计与验证主要包括以下几个方面:一、芯片架构设计:根据RoCE V2协议的要求,SmartNIC 芯片需要支持RDMA功能,并且能够在高负载情况下保持低延迟。

因此,在芯片的架构设计中,需要合理划分各个功能模块,使得RDMA功能和其他网络功能可以并行工作,并且能够高效利用硬件资源。

二、硬件设计:SmartNIC芯片的硬件设计主要包括对RDMA功能的支持以及与主机之间的数据交换。

硬件设计需要考虑到高速数据传输的需求,包括高带宽、低功耗和低延迟等要求。

同时,还需要考虑芯片的复杂度和成本的限制。

三、固件开发:SmartNIC芯片的固件开发主要涉及RDMA功能的驱动程序和协议栈的开发。

固件需要能够实现RoCE V2协议的要求,并且能够支持大规模数据中心网络的需求。

四、验证测试:在设计完成后,需要进行验证测试以确保芯片的功能和性能符合设计要求。

TPM及其工作原理

TPM及其⼯作原理TPM安全芯⽚TPM(Trusted Platform Module)安全芯⽚,是指符合TPM(可信赖平台模块)标准的安全芯⽚,它能有效地保护PC、防⽌⾮法⽤户访问。

TPM标准:1999年10⽉,多家IT巨头联合发起成⽴可信赖运算平台联盟(Trusted Computing Platform Alliance,TCPA),初期加⼊者有康柏、HP 、IBM、Intel、微软等,该联盟致⼒于促成新⼀代具有安全且可信赖的硬件运算平台。

2003年3⽉,TCPA增加了诺基亚、索尼等⼚家的加⼊,并改组为可信赖计算组织(Trusted Computing Group,TCG),希望从跨平台和操作环境的硬件和软件两⽅⾯,制定可信赖电脑相关标准和规范。

并在并提出了TPM规范,⽬前最新版本为1.2。

符合TPM的芯⽚⾸先必须具有产⽣加解密密匙的功能,此外还必须能够进⾏⾼速的资料加密和解密,以及充当保护BIOS和操作系统不被修改的辅助处理器。

TPM安全芯⽚⽤途⼗分⼴泛,配合专⽤软件可以实现以下⽤途:1、存储、管理BIOS开机密码以及硬盘密码。

以往这些事务都是由BIOS做的,玩过的朋友可能也知道,忘记了密码只要取下BIOS电池,给BIOS放电就清除密码了。

如今这些密钥实际上是存储在固化在芯⽚的存储单元中,即便是掉电其信息亦不会丢失。

相⽐于BIOS管理密码,TPM安全芯⽚的安全性要⼤为提⾼。

2、TPM安全芯⽚可以进⾏范围较⼴的加密。

TPM安全芯⽚除了能进⾏传统的开机加密以及对硬盘进⾏加密外,还能对系统登录、应⽤软件登录进⾏加密。

⽐如⽬前咱们常⽤的MSN、QQ、⽹游以及⽹上银⾏的登录信息和密码,都可以通过TPM加密后再进⾏传输,这样就不⽤担⼼信息和密码被⼈窃龋3、加密硬盘的任意分区。

我们可以加密本本上的任意⼀个硬盘分区,您可以将⼀些敏感的⽂件放⼊该分区以策安全。

其实有些本本⼚商采⽤的⼀键恢复功能,就是该⽤途的集中体现之⼀(其将系统镜像放在⼀个TPM加密的分区中)。

可信芯片验证平台的设计与实现

可信芯片验证平台的设计与实现随着信息技术的快速发展,芯片在现代社会中的应用越来越广泛。

然而,由于芯片内部的复杂电路结构和功能的多样化,芯片在设计和制造过程中往往容易受到各种攻击,如仿真、非法复制和篡改等。

因此,为了确保芯片的可信性和安全性,可信芯片验证平台的设计和实现变得尤为重要。

可信芯片验证平台是一种基于硬件和软件的综合平台,用于验证芯片的安全性和可信度。

该平台由硬件部分和软件部分组成,各具特定功能。

硬件部分是平台的核心,主要包括多种检测电路、信号处理电路和接口电路等。

检测电路用于检测芯片在运行过程中可能存在的安全隐患,如电压异常、电流波动等。

信号处理电路负责对从芯片输出的信号进行分析和处理,以判断芯片是否受到攻击。

接口电路则用于与外部设备进行连接和数据传输,方便后续的数据处理和分析。

软件部分是平台的灵魂,主要包括验证算法、数据处理算法和用户界面等。

验证算法是核心部分,用于分析和判断芯片是否符合安全性要求。

数据处理算法负责对从硬件部分采集到的数据进行处理和分析,提取有用信息,并生成相应的报告。

用户界面则提供了一个友好的操作界面,方便用户进行参数设置、数据查看和结果分析等操作。

可信芯片验证平台的实现需要经过以下几个步骤:首先,确定验证平台的功能和性能要求,明确验证的目标和指标。

其次,设计硬件部分,选择合适的电路和器件,并进行布局和连接。

然后,编写软件部分的验证算法和数据处理算法,并进行测试和调试。

最后,将硬件和软件部分进行整合,进行系统测试和性能评估。

通过可信芯片验证平台的设计和实现,可以有效提高芯片的可信度和安全性。

验证平台可以对芯片进行全面、细致的检测和分析,及时发现并阻止各种安全威胁。

同时,验证平台还可以为芯片的设计和制造提供重要的参考和指导,指出潜在的安全隐患和改进方向。

总之,可信芯片验证平台的设计与实现是保障芯片可信度和安全性的重要手段。

这一平台的设计需要充分考虑硬件和软件的相互配合和协同工作,确保整个验证过程的准确性和有效性。

SOC ASIC

socSOC,或者SoC,是一个缩写,包括的意思有:1)SoC:System on Chip的缩写,称为系统级芯片,也有称片上系统,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。

2)SOC:Security Operations Center的缩写,成为安全运行中心,或者安全管理平台,属于信息安全领域的词汇。

一般指以资产为核心,以安全事件管理为关键流程,采用安全域划分的思想,建立一套实时的资产风险模型,协助管理员进行事件分析、风险分析、预警管理和应急响应处理的集中安全管理系统。

3)民航SOC:System Operations Center的缩写,指民航领域的指挥控制系统。

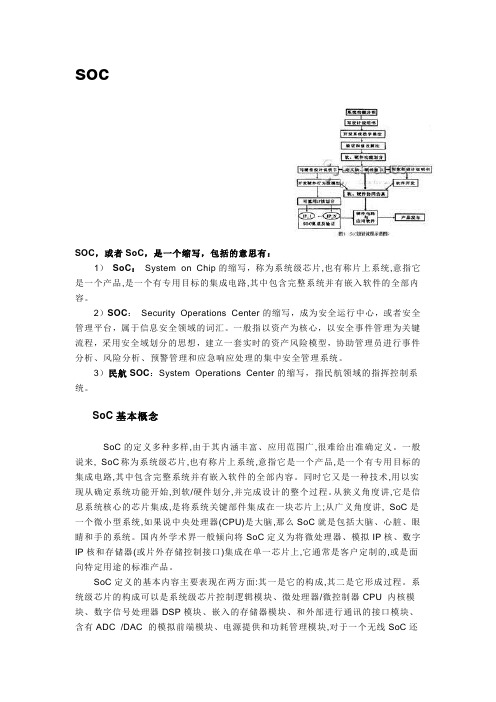

SoC基本概念SoC的定义多种多样,由于其内涵丰富、应用范围广,很难给出准确定义。

一般说来, SoC称为系统级芯片,也有称片上系统,意指它是一个产品,是一个有专用目标的集成电路,其中包含完整系统并有嵌入软件的全部内容。

同时它又是一种技术,用以实现从确定系统功能开始,到软/硬件划分,并完成设计的整个过程。

从狭义角度讲,它是信息系统核心的芯片集成,是将系统关键部件集成在一块芯片上;从广义角度讲, SoC是一个微小型系统,如果说中央处理器(CPU)是大脑,那么SoC就是包括大脑、心脏、眼睛和手的系统。

国内外学术界一般倾向将SoC定义为将微处理器、模拟IP核、数字IP核和存储器(或片外存储控制接口)集成在单一芯片上,它通常是客户定制的,或是面向特定用途的标准产品。

SoC定义的基本内容主要表现在两方面:其一是它的构成,其二是它形成过程。

系统级芯片的构成可以是系统级芯片控制逻辑模块、微处理器/微控制器CPU 内核模块、数字信号处理器DSP模块、嵌入的存储器模块、和外部进行通讯的接口模块、含有ADC /DAC 的模拟前端模块、电源提供和功耗管理模块,对于一个无线SoC还有射频前端模块、用户定义逻辑(它可以由FPGA 或ASIC实现)以及微电子机械模块,更重要的是一个SoC 芯片内嵌有基本软件(RDOS或COS以及其他应用软件)模块或可载入的用户软件等。

航天二院706所

中国航天科工集团第二研究院七〇六所企业简介中国航天科工二院706所始建于1957年,是我国最早从事计算机研究的大型骨干专业研究所之一,是以计算机软硬件研制及产品开发应用为主,集研究、设计、试验、生产和服务于一体的国防领域计算机与控制技术核心研究所。

产品涉及嵌入式计算机软硬件、信息安全、网络存储、软件工程与评测、惯性测量、射频识别、芯片设计、电磁兼容、数控等专业领域,是总装备部军用计算机及软件技术专业组成员单位,是总装备部军用计算机研制生产定点单位。

拥有国防科技工业软件测试与评价实验室、中国航天软件评测中心、国家保密科技评测中心(中国航天科工集团公司)分中心。

技术实力1.技术领域中国航天科工二院706所致力于军队信息化建设,坚持走军民融合式发展之路,注重技术积累与创新,形成嵌入式计算机软硬件技术、信息安全技术、网络存储技术、软件工程与评测技术、惯性测量技术、射频识别技术、芯片设计技术、电磁兼容及电能质量、数控技术等优势技术。

与结构工艺、电源、可靠性等支撑专业共同构建较为完善、互为支撑的专业体系。

获得国防科技工业局50项科研许可和41项生产许可,拥有国家专利45项。

主板全国中文核心期刊、中国计算机学会会刊《计算机工程与设计》承担了多项国防重点型号任务和国家重大工程任务,产品广泛应用于各军兵种、政府机关,以及航天航空、电力能源、石油化工、交通运输等各个领域。

嵌入式计算机技术中国航天科工二院706所建立了先进的嵌入式计算机EDA设计开发、仿真分析及测试验证环境,掌握了嵌入式系统系统总体架构设计、高速电路设计、千万门级FPGA设计、固件和设备驱动软件设计、电磁兼容性设计、抗恶劣环境设计等关键技术,具有面向多种体系架构自主开发板级产品和整机系统的能力。

遵循开放式通用技术标准,基于X86、DSP、PowerPC、龙芯、飞腾等多种高性能处理器,开发了不同体系架构多种总线多个系列的嵌入式高性能计算机产品。

捷联惯性测量技术中国航天科工二院706所建有完备的惯性技术试验室,拥有高精度温控三轴位置速率转台、高精度寻北仪等一系列专业标定测试设备,突破了快速启动,大动态、抗恶劣环境,小型化、低功耗、高精度等核心技术,具备惯性测量装置总体设计能力。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

21 0 1年 9月

计 算机 辅助 设计 与 图形学 学报

J u n lo mp trAie sg & Co p trGrp is o r a fCo u e — d dDein m u e a hc

V 0 . o. 1 23 N 9 Se p. 201 1

f l s s e v rf a i n n o h r e t e e iia i n c ce u l y t m e i c to a d t s o t n h v rf t y l wi F — i c o t h PGA. Ba e n r g a mi g s d o p o r m n i t r a e n fr n e f c s i imwa e CVP e a l s smu a i n o r ,F n b e i l t fDUT ( e i n u d rt s )mo u e n x c t n o o d sg n e e t d ls a d e e u i f o

Ii o ,L a fn ,P n ifn ¨ ,H u n n Ha ¨ i neg Xi agJ eg u a g Ka ",Z e g Ya s n ¨,T n n ¨,a dCh n hn nog o g Do g n e gXu

”( i o r c s r sa c n v lp n e tr e i g U i est Be ig 1 0 7 ) M c p o es Ree rh a d De eo me tC ne ,P k n n v riy, i n 0 8 1 r o j

v rfc ton Th s p p r pr po e e iia i . i a e o s s FCVP,a fr imwa e ba e O ve iia i l tor ,t na e a le r — s d C — rfc ton p a f m o e bl e ri r

(iin e g@ s p u d . n) i a fn x z k .e u c

摘

要 :使 用 F G 进 行 全 系统 仿 真 是 验 证 基 于 平 台设 计 的系 统 芯 片 (o ) P A S C 的有 效 手 段 , F G 原 型 验 证 一 方 面 但 PA

须 等 待 硬 件 设 计 完 成 编 码 , 一 方 面 F GA 全 系 统 环 境 下 的 硬 件 设 计 错 误 定 位 耗 时 , 证 周 期 较 长 . 更 早 展 开 系 另 P 验 为 统 级 验 证 工 作 并 缩 短 验 证 周 期 , 出一 种 基 于 固 件 的协 同 验 证 平 台一 一F V . C P 在 F GA 上 基 于 固 件 模 拟 待 提 c PFV P 测 硬 件 设 计 和 系 统 模 块 , 过 运 行 真 实 工 作 负 载 , 比 F GA 中待 测 硬 件 设 计 和 F VP模 拟 参 考 模 型 的 行 为 , 助 通 对 P C 帮 分 析 、 位硬 件设 计 错 误 . P Unt8 o 上进 行 验 证 的 实 例 表 明 , C 定 在 K i 6S C y F VP可 用 于 SC 设 计 初 期 验 证 , 可 有 效 地 o 并 辅 助 硬 件 设 计 错 误 的定 位 . 能 评 测 显 示 , C 性 F VP模 拟 性 能 优 于纯 软件 模 拟 器 .

( k n i e s t h n he a a e Sc o l he z e 51 0 5) Pe i g Un v r iy S e z n Gr du t h o ,S n h u ls t m m u a i n FPGA s a fe tv y f r r pi e iia i n o a f r b s d l— ys e e l ton o i n e f c i e wa o a d v rfc to f plt o m— a e So C d sgn Ho v r FPGA e u a i r q r s o p e e mplm e t to o ke mo l s nd ei . we e , m l ton e uie c m l t i e n a in f y du e a

基 于 固件 的 系统 芯 片协 同验证 平 台

李 皓” 李险峰 庞九凤” 黄 , , , 侃” 郑衍松” 佟 , , 冬” 程 , 旭

”( 京 大 学 微 处 理 器 研 究 开 发 中 心 北 京 1 0 7 ) 北 0 8 1 。( 京 大 学 深 圳 研 究 生 院 北 深圳 5 8 5 ) 10 5

pr v de e k v s b lt . I s tm e c s o i sw a ii iiy ti i — on um i g t ro m r w a e d sgn e r r l a ia i nd d sg n o pe f r ha d r e i r o oc lz ton a e i n

关 键 词 : 同验 证 ; 统 芯 片 ; 件 ; 系 统 模 拟 器 ; 件 设 计 错 误 ; 于 平 台 的 设 计 协 系 固 全 硬 基

中 图 法 分 类 号 :TP 0 . 36 3

A r wa e Ba e 一 r f c to a f r f r S C Fi m r — s d C0 Ve ii a i n Pl t o m o o