2输入数据选择器(mux2)集成电路课设报告

集成电路实验报告

班级:XX姓名:XXX学号:XXXXXX指导老师:XXX实验日期:XXXX年XX月XX日一、实验目的1. 理解集成电路的基本组成和工作原理。

2. 掌握基本的集成电路设计方法,包括原理图设计、版图设计、仿真分析等。

3. 学习使用集成电路设计软件,如Cadence、LTspice等。

4. 通过实验加深对集成电路理论知识的理解,提高动手能力和问题解决能力。

二、实验内容本次实验主要包括以下内容:1. 原理图设计:使用Cadence软件绘制一个简单的CMOS反相器原理图。

2. 版图设计:根据原理图,使用Cadence软件进行版图设计,并生成GDSII文件。

3. 仿真分析:使用LTspice软件对设计的反相器进行仿真分析,测试其性能指标。

4. 版图与原理图匹配:使用Cadence软件进行版图与原理图的匹配,确保设计正确无误。

三、实验步骤1. 原理图设计:- 打开Cadence软件,选择原理图设计模块。

- 根据反相器原理,绘制相应的电路符号,包括NMOS和PMOS晶体管、电阻和电容等。

- 设置各个元件的参数,如晶体管的尺寸、电阻和电容的值等。

- 完成原理图设计后,保存文件。

2. 版图设计:- 打开Cadence软件,选择版图设计模块。

- 根据原理图,绘制晶体管、电阻和电容的版图。

- 设置版图规则,如最小线宽、最小间距等。

- 完成版图设计后,生成GDSII文件。

3. 仿真分析:- 打开LTspice软件,选择仿真模块。

- 将GDSII文件导入LTspice,生成对应的原理图。

- 设置仿真参数,如输入电压、仿真时间等。

- 运行仿真,观察反相器的输出波形、传输特性和功耗等性能指标。

4. 版图与原理图匹配:- 打开Cadence软件,选择版图与原理图匹配模块。

- 将原理图和版图导入匹配模块。

- 进行版图与原理图的匹配,检查是否存在错误或不一致之处。

- 修正错误,确保版图与原理图完全一致。

四、实验结果与分析1. 原理图设计:- 成功绘制了一个简单的CMOS反相器原理图,包括NMOS和PMOS晶体管、电阻和电容等元件。

mux2

原理图输入方式

建立工程库目录,以存放工程设计文档 建立新的工程 建立原理图源文件(以2选一选择器为例)

单击“NEW”按钮或 选择File/New…菜单

选择第二项Block Diagram/Schemetic File, 新建原理图文件。最后一项 为VHDL文本文件

原理图文件的扩展名 为*.bdf 双击原理图空白区 域,调出元件库窗口

选择Start Simulation按钮或 Processing/Start Simulation菜单 开始仿真。注意:仿真波形结果 和仿真向量文件是分开的

1、QuartusII基本设计流程

添加信号仿真节点 设置最小仿真步长 设置仿真波形(注意常用信号设置按钮的使用) 文件存盘(*.vwf) 仿真参数设置:选择仿真类型和仿真文档 Timing/Funtional 启动仿真 Processing/Start Simulation

单击save按钮或选择filesave保存原理图文件原理图文件名可以和顶层实体名一致如果原理图名和顶层实体名不同以后还可通过菜单调整此复选框使得文件保存的同时被填入工程到此工程以及原理图文件建立完成1quartusii基本设计流程原理图输入方式建立工程库目录以存放工程设计文档建立新的工程建立原理图源文件以2选一选择器为例工程编译选择配置器件的工作方式可以加入jtag用户编码devicepinoptions

选择(修改)目标芯片Assignments/Settings… 选择配置器件的工作方式(可以加入JTAG用户编 码)Device & Pin Options…

如果实体名和文件一致 可以省去上一步

选择Start Compilation按钮或 Processing/ Start Compilation菜 单进行全局编译

数据选择器及其应用实验报告

数据选择器及其应用实验报告实验目的:

本实验的目的是通过实现数据选择器的功能,加深对于数字电路的理解,并提升对于数字电路实现的实践能力。

实验原理:

数据选择器是一种能够从多个数据信号中选择特定信号输出的数字电路,通常它有一个或多个数据输入线、一个或多个控制输入线、一个输出线和一个使能输入线。

在数据选择器输出线上的输出值,取决于控制输入线上的值以及选择从哪一个数据输入线接收数据信号。

在本次实验中,我们使用的是双二选一的数码开关。

“双”指的是它一共有两个信道供选择,“二选一”则代表只会选择其中一个信道作为输出。

实验步骤:

1.根据实验原理和实验材料的提供,搭建实验电路。

2.设置信号源,对选择器进行输入数据和控制信号的测试。

3.根据信号源输出的数据,通过实验电路计算出数据选择器输出的结果。

4.逐一更改控制信号的值,反复测试并记录数据。

并对实验记录进行整理和比较分析,以达到理解、检验和加深对数据选择器的认识。

实验结果:

在实验中我们完成了数据选择器的搭建和调试,并通过多次实验数据的记录与比较,成功实现了数据选择器的功能。

实验结论:

通过本次实验,我们深入学习了数据选择器的工作原理和实现方式,并从中进一步了解了数字电路的基本概念和实现方式。

通

过反复实验和分析,我们成功完成了数据选择器的功能调试,提升了我们的实践能力和对数字电路的理解。

2输入数据选择器mux2集成电路课设报告

姓名

助人为乐

性别

男

专业、班级

课程设计题目:二输入数据选择器版图设计

课程设计答辩或质疑记录:

成绩评定依据:

最终评定成绩(以优、良、中、及格、不及格评定)

指导教师签字:

年月日

3

3

3.1

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称多路选择器或多路开关。数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号,其工作原理如下图所示:

图3-1数据选择器原理图

2输入多路选择器(Mux2)的电路中A、B分别为两路输入端口,Sel为数据选择端,Out为数据输出端。它的逻辑功能是当Sel=0时,选择输入A通过,Y=A;当Sel=1时,选择输入B通过,Y=B。2输入多路选择器有三个与非门(nand2)和一个反相器构成。

5

这次课程设计的主要内容是集成电路版图设计,第一次尝试在电脑上进行版图的设计,有很多地方都不了解,都要通过自己对软件的学习才能顺利的进行实验。在选取了2输入同或门电路的同时,我开始了版图设计,刚开始时我完全不知怎么着手画版图,于是我通过查找图书馆的资料,学习Tanner集成电路设计方法,并从网上找了一些版图设计的实用教程,渐渐地我开始掌握了画版图的技巧,经过半天的努力,我把各个模块的版图画好了,经过几天的努力终于把整个芯片的版图画完,并最终通过了DRC检查。

4.2ﻩ整体版图设计9

4.3设计规则的验证及结果9

5.总结10

参考文献11

摘要

I C(“集成电路”)产业是全球高新技术产业的前沿与核心,是最具活力和挑战性的战略产业。自2000年来,在国家政策的大力支持下,我国集成电路产业得到了长足的发展,而作为集成电路产业最前沿的设计业更是呈现出“百花齐放”的繁荣景象。本文主要介绍了数据选择器的版图设计基本方法,实现了版图设计的基本要求。

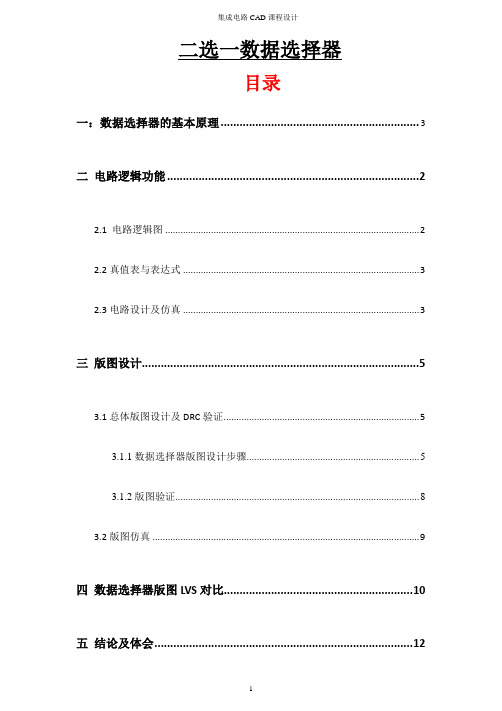

二选一数据选择器

二选一数据选择器目录一:数据选择器的基本原理 (3)二电路逻辑功能 (2)2.1 电路逻辑图 (2)2.2真值表与表达式 (3)2.3电路设计及仿真 (3)三版图设计 (5)3.1总体版图设计及DRC验证 (5)3.1.1数据选择器版图设计步骤 (5)3.1.2版图验证 (8)3.2版图仿真 (9)四数据选择器版图LVS对比 (10)五结论及体会 (12)一:数据选择器的基本原理数据选择器是指经过选择,把多个通道的数据传送到唯一的公共数据通道上去,实现数据选择功能的逻辑电路称为数据选择器。

它的作用相当于多个输入的单刀多掷开关,其示意图如下:图1 n位通道选择信号数据选择器除了可以实现一些组合逻辑功能以外,还可以做分时多路传输电路、函数发生器及数码比较器等。

常见的数据选择器有4选1、8选1、16选1电路。

在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号下图所示为二选一数据选择器原理图,a,b为输入端,sel为控制端,out为输出端图1-1数据选择器原理图二电路逻辑功能2.1 电路逻辑图=+(S是数据选择控制端,S为0时选择A,为1时选S择B)Y SA SB要实现2选1选择器,逻辑电路图如下所示图2-1数据选择器逻辑电路图2.2真值表与表达式二选一数据选择器逻辑表达式为:Y SA SB =+根据逻辑表达式所列真值表如下图所示图2-2数据选择器真值表图2.3电路设计及仿真根据原理电路图并使用S-Edit 软件设计出数据选择器的电路图及对应符号图如下:S A B Y 01 1 1 1 0 1 0 1 0 0 0 0 1 1 1 1 1 0 0 0 1 1 0图2-3数据选择器符号图根据符号图并使用S-Edit软件设计出的数据选择器电路图如下所示图2-4数据选择器电路图导出的SPICE文件,如下图所示图2-5 spice文件加载包含文件,如下图所示图2-6 加载后的SPICE文件在其基础上进行仿真:下图从上到下依次为Y. S B A,结合逻辑表达式及真值表可知,电路为正确的图2-7 模拟波形仿真图三版图设计3.1总体版图设计及DRC验证3.1.1数据选择器版图设计步骤(1)新建文件夹:在电脑本地磁盘新建文件夹,文件夹名为shuju。

二选一数据选择器报告

EDA实验报告组合电路设计一、实验目的1、熟悉quartusⅡ的VHDL文本设计全过程,2、学习简单组合电路的设计、多层次电路设计、仿真和硬件测试。

二、实验内容1、实验内容2:将此多路选择器看成一个元件mux21a,利用元件例化语句描述成三选一,然后进行编译、综合、仿真。

2、实验内容3:引脚锁定以及硬件下载测试。

选实验电路模式5,用键1(PIO0)控制s0;用键2(PIO1)控制s1;a3、a2和a1分别接clock5、clock0和clock2;输出信号outy仍接spker,通过短路帽选择clock0接256Hz信号,clock5接1024Hz信号,aclock2接8 Hz信号。

最后进行编译、下载和硬件测试实验。

三、实验器材PC机一台、Quartus II软件、EDA实验箱一台、下载电缆一根(已接好)。

四、实验程序实验内容2:三选一library ieee;use ieee.std_logic_1164.all;entity muxk isport(a1,a2,a3: in std_logic;s0,s1: in std_logic;outy: out std_logic);end entity muxk;architecture bhv of muxk iscomponent mux21aport( a,b: in std_logic;s: in std_logic;y: out std_logic);end component;signal tmp: std_logic;beginu1: mux21a port map(a=>a2,b=>a3,s=>s0,y=>tmp);u2: mux21a port map(a=>a1,b=>tmp,s=>s1,y=>outy);end architecture bhv;五、实验步骤实验二:在实验一的基础上,新建VHDL文件,命名为muxk。

集成电路课程设计(CMOS二输入与门)

武汉理工大学《集成电路软件》课程设计课程设计任务书学生姓名:王伟专业班级:电子1001班指导教师:刘金根工作单位:信息工程学院题目: 基于CMOS的二输入与门电路初始条件:计算机、Cadence软件、L-Edit软件要求完成的主要任务:(包括课程设计工作量及其技术要求,以及说明书撰写等具体要求)1、课程设计工作量:2周2、技术要求:(1)学习Cadence IC软件和L-Edit软件。

(2)设计一个基于CMOS的二输入的与门电路。

(3)利用Cadence和L-Edit软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2013.11.25-11.27学习Cadence IC和L-Edit软件,查阅相关资料,复习所设计内容的基本理论知识。

2013.11.28-12.5对二输入与门电路进行设计仿真工作,完成课设报告的撰写。

2013.12.6 提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录摘要 (2)绪论 (3)一、设计要求 (4)二、设计原理 (4)三、设计思路 (4)3.1、非门电路 (4)3.2、二输入与非门电路 (6)3.3、二输入与门电路 (8)四、二输入与门电路设计 (9)4.1、原理图设计 (9)4.2、仿真分析 (10)4.3、生成网络表 (13)五、版图设计................................................... (20)5.1、PMOS管版图设计 (20)5.2、NMOS管版图设计 (22)5.3、与门版图设计 (23)5.4、总版图DRC检查及SPC文件的生成 (25)六、心得体会 (28)七、参考文献 (29)八、附录 (30)摘要本文从设计到仿真以及后面的版图制作等主要用到了Cadence IC软件和L-Edit软件等。

CMOS版图设计MUX2

一、实验目的1)请提取版图MUX2,并用标尺测量每个晶体管的尺寸;2)将提取出的电路绘制在S-Edit中,并调用T-Spice进行仿真。

二、实验步骤⑴提取MUX2,测量晶体管的尺寸M1 Vdd Sel 12 Vdd PMOS L=2u W=21u* M1 DRAIN GATE SOURCE BULK (32 41 34 62)M2 Vdd Sel 7 Vdd PMOS L=2u W=21u* M2 DRAIN GATE SOURCE BULK (8 41 10 62)M3 Out 8 Vdd Vdd PMOS L=2u W=28u* M3 DRAIN GATE SOURCE BULK (44 38 46 66)M4 12 B 8 Vdd PMOS L=2u W=21u* M4 DRAIN GATE SOURCE BULK (28 41 30 62)M5 8 A 11 Vdd PMOS L=2u W=21u* M5 DRAIN GATE SOURCE BULK (20 41 22 62)M6 11 7 Vdd Vdd PMOS L=2u W=21u* M6 DRAIN GATE SOURCE BULK (16 41 18 62)M7 10 Sel Gnd Gnd NMOS L=2u W=21u* M7 DRAIN GATE SOURCE BULK (16 0 18 21)M8 Gnd Sel 7 Gnd NMOS L=2u W=21u* M8 DRAIN GATE SOURCE BULK (8 0 10 21)M9 Out 8 Gnd Gnd NMOS L=2u W=28u* M9 DRAIN GATE SOURCE BULK (44 0 46 28)M10 9 B 8 Gnd NMOS L=2u W=21u* M10 DRAIN GATE SOURCE BULK (28 0 30 21)M11 Gnd 7 9 Gnd NMOS L=2u W=21u* M11 DRAIN GATE SOURCE BULK (32 0 34 21)M12 8 A 10 Gnd NMOS L=2u W=21u如上红色所示,除了M3和M9晶体管的宽为28u外,其它的都为L=2u W=21u⑵将提取到的电路绘制在S-Edit中根据版图分析得知:此版图是二输入选择器表达式为:F = A & Sel + B & (!Sel)当Sel为1时,F输出为A当Sel为0时,F输出为B⑶MUX2的版图的spc文件* Circuit Extracted by Tanner Research's L-Edit Version 9.00 / Extract Version 9.00 ;* TDB File: F:\学习\数字电路设计\Tanner\Tanner\LEdit90\Samples\SPR\example1\lightslb.tdb* Cell: Mux2 Version 1.00* Extract Definition File: lights.ext* Extract Date and Time: 05/24/2011 - 16:33.include morbn20.md* Warning: Layers with Unassigned AREA Capacitance. * <NMOS Capacitor ID>* <PMOS Capacitor ID>* <Poly Resistor ID>* <Poly2 Resistor ID>* <N Diff Resistor ID>* <P Diff Resistor ID>* <P Base Resistor ID>* <N Well Resistor ID>* Warning: Layers with Unassigned FRINGE Capacitance. * <Pad Comment>* <Poly1-Poly2 Capacitor ID>* <NMOS Capacitor ID>* <PMOS Capacitor ID>* <Poly Resistor ID>* <Poly2 Resistor ID>* <N Diff Resistor ID>* <P Diff Resistor ID>* <P Base Resistor ID>* <N Well Resistor ID>* Warning: Layers with Zero Resistance.* <Pad Comment>* <Poly1-Poly2 Capacitor ID>* <NMOS Capacitor ID>* <PMOS Capacitor ID>* <P Base Resistor ID>M14 5 4 12 5 PMOS L=2u W=21u* M14 DRAIN GATE SOURCE BULK (32 41 34 62)M13 5 4 7 5 PMOS L=2u W=21u* M13 DRAIN GATE SOURCE BULK (8 41 10 62)M12 1 8 5 5 PMOS L=2u W=28u* M12 DRAIN GATE SOURCE BULK (44 38 46 66)M11 12 2 8 5 PMOS L=2u W=21u* M11 DRAIN GATE SOURCE BULK (28 41 30 62)M10 8 3 11 5 PMOS L=2u W=21u* M10 DRAIN GATE SOURCE BULK (20 41 22 62)M9 11 7 5 5 PMOS L=2u W=21u* M9 DRAIN GATE SOURCE BULK (16 41 18 62)M8 10 4 6 6 NMOS L=2u W=21u* M8 DRAIN GATE SOURCE BULK (16 0 18 21)M7 6 4 7 6 NMOS L=2u W=21u* M7 DRAIN GATE SOURCE BULK (8 0 10 21)M6 1 8 6 6 NMOS L=2u W=28u* M6 DRAIN GATE SOURCE BULK (44 0 46 28)M5 9 2 8 6 NMOS L=2u W=21u* M5 DRAIN GATE SOURCE BULK (28 0 30 21)M4 6 7 9 6 NMOS L=2u W=21u* M4 DRAIN GATE SOURCE BULK (32 0 34 21)M3 8 3 10 6 NMOS L=2u W=21u* M3 DRAIN GATE SOURCE BULK (20 0 22 21)* Pins of element D2 are shorted:* D2 5 5 D_lateral* D2 PLUS MINUS (37 60 41 66)* Pins of element D1 are shorted:* D1 6 6 D_lateral* D1 PLUS MINUS (36.999 0 41.001 6.001)* Total Nodes: 12* Total Elements: 14* Total Number of Shorted Elements not written to the SPICE file: 0 * Extract Elapsed Time: 0 seconds.END⑷使用T-SPICE进行仿真.include "F:\学习\数字电路设计\Tanner\Tanner\TSpice70\models\ml2_125.md" V A A Gnd PWL (0 0 5n 5 90n 5 100n 0 110n 0 120n 5 130n 0)VB B Gnd PWL (0 0 10n 5 80n 5 100n 0 110n 5 120n 0 130n 5)VSel Sel Gnd PWL (0 0 20n 5 70n 5 100n 0 110n 5 120n 0 130n 5)VCC Vdd Gnd 5.print tran v(Sel,Gnd) v(A,Gnd) v(B,Gnd) v(Out,Gnd).tran/op 50n 500n method=bdf由图可得:当Sel为1时,F输出为A当Sel为0时,F输出为B⑸使用LVS进行比较电路不完全相等经分析得知:是我自己画出的原理图的宽度(22u)不够,版图中的宽度为(28u)经过改正电路完全相等⑹实验总结经过对MUX2版图的原理图提取,使我更加深入的理解了实际的原理图和版图之间的关系,以前做实验只是简单的拿个原理图画出版图,这次就不同了,当从版图中提取原理图后,再进行仿真和比较,从而就更清楚了从版图到原理图的映射关系。

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

课程设计任务书学生姓名:助人为乐专业班级:不计得失指导教师:一定过工作单位:信息工程学院题目: 二输入数据选择器版图设计初始条件:计算机、ORCAD软件、L-EDIT软件要求完成的主要任务:1、课程设计工作量:2周2、技术要求:(1)学习ORCAD软件、L-EDIT软件软件。

(2)设计一个二输入数据选择器电路。

(3)利用ORCAD软件、L-EDIT软件对该电路进行系统设计、电路设计和版图设计,并进行相应的设计、模拟和仿真工作。

3、查阅至少5篇参考文献。

按《武汉理工大学课程设计工作规范》要求撰写设计报告书。

全文用A4纸打印,图纸应符合绘图规范。

时间安排:2013.11.22布置课程设计任务、选题;讲解课程设计具体实施计划与课程设计报告格式的要求;课程设计答疑事项。

2013.11.25-11.27学习ORCAD软件、L-EDIT软件,查阅相关资料,复习所设计内容的基本理论知识。

2013.11.28-12.5对二输入数据选择器电路进行设计仿真工作,完成课设报告的撰写。

2013.12.6提交课程设计报告,进行答辩。

指导教师签名:年月日系主任(或责任教师)签名:年月日目录1.绪论 (2)2.软件简介 (3)2.1Cadence简介 (3)2.2L-edit简介 (3)3.二输入多路选择器电路设计及仿真 (4)3.1数据选择器原理 (4)3.2电路原理图的绘制 (5)3.3电路图仿真 (6)4.集成电路版图设计 (7)4.1CMOS数字电路基本单元版图设计 (7)4.1.1反相器版图设计 (7)4.1.2与非门版图设计 (8)4.2整体版图设计 (9)4.3设计规则的验证及结果 (9)5.总结 (10)参考文献 (11)摘要I C(“集成电路”)产业是全球高新技术产业的前沿与核心,是最具活力和挑战性的战略产业。

自2000年来,在国家政策的大力支持下,我国集成电路产业得到了长足的发展,而作为集成电路产业最前沿的设计业更是呈现出“百花齐放”的繁荣景象。

本文主要介绍了数据选择器的版图设计基本方法,实现了版图设计的基本要求。

关键词:版图,数据选择器,Orcad1绪论集成电路从60年代开始,经历了小规模集成,中规模集成,大规模集成,到目前的超大规模集成。

单个芯片上已经可以制作含几百万个晶体管的一个完整的数字系统或数模混合的电子系统。

I C(“集成电路”)产业是全球高新技术产业的前沿与核心,是最具活力和挑战性的战略产业。

自2000年来,在国家政策的大力支持下,我国集成电路产业得到了长足的发展,而作为集成电路产业最前沿的设计业更是呈现出“百花齐放”的繁荣景象,作为产业命脉的IC设计人才,在IC产业最集中的长三角地区也仅仅只有几千人。

所以拥有一定工作经验的设计工程师,据国内知名猎头公司烽火猎聘公司数据显示ic已成为人才猎头公司争相角逐的“宠儿”。

在整个设计过程中,版图(layout)设计或者称作物理设计(physical design)是其中重要的一环。

他是把每个原件的电路表示转换成集合表示,同时,元件间连接的线网也被转换成几何连线图形。

IC版图设计是指将前端设计产生的门级网表通过EDA设计工具,根据产品前段设计线路或文件要求,按照工艺设计规则,进行布局布线和进行物理验证并最终产生供制造用的GDSII数据的过程。

其主要工作职责有:芯片物理结构分析、逻辑分析、建立后端设计流程、版图布局布线、版图编辑、版图物理验证、联络代工厂并提交生产数据。

作为连接设计与制造的桥梁,合格的版图设计人员既要懂得IC设计、版图设计方面的专业知识,还要熟悉制程厂的工作流程、制程原理等相关知识。

2软件简介2.1 Cadence简介Cadence Design Systems是一个专门从事电子设计自动化(EDA)的软件公司,由SDA Systems和ECAD两家公司于1988年兼并而成。

是全球最大的电子设计技术(Electronic Design Technologies)、程序方案服务和设计服务供应商。

其产品涵盖了电子设计的整个流程,包括系统级设计,功能验证,IC综合及布局布线,模拟、混合信号及射频IC设计,全定制集成电路设计,IC物理验证,PCB设计和硬件仿真建模等。

包括原理图输入、生成、模拟数字/混合电路仿真,fpga设计,pcb编辑和自动布局布线mcm电路设计、高速pcb 版图的设计仿真。

Cadence Allegro系统互连平台能够跨集成电路、封装和PCB协同设计高性能互连。

应用平台的协同设计方法,工程师可以迅速优化I/O缓冲器之间和跨集成电路、封装和PCB 的系统互联。

该方法能避免硬件返工并降低硬件成本和缩短设计周期。

2.2 L-edit简介Tanner集成电路设计软件是由Tanner Research 公司开发的基于Windows平台的用于集成电路设计的工具软件。

该软件功能十分强大,易学易用,包括S-Edit,T-Spice,W-Edit,L-Edit与LVS,从电路设计、分析模拟到电路布局一应俱全。

其中的L-Edit版图编辑器在国内应用广泛,具有很高知名度。

L-Edit Pro是Tanner EDA软件公司所出品的一个IC设计和验证的高性能软件系统模块,具有高效率,交互式等特点,强大而且完善的功能包括从IC设计到输出,以及最后的加工服务,完全可以媲美百万美元级的IC设计软件。

L-Edit Pro包含IC设计编辑器(Layout Editor)、自动布线系统(Standard Cell Place & Route)、线上设计规则检查器(DRC)、组件特性提取器(Device Extractor)、设计布局与电路netlist的比较器(LVS)、CMOS Library、Marco Library,这些模块组成了一个完整的IC设计与验证解决方案。

L-Edit Pro丰富完善的功能为每个IC设计者和生产商提供了快速、易用、精确的设计系统。

3二输入多路选择器电路设计及仿真3.1 数据选择器原理在多路数据传送过程中,能够根据需要将其中任意一路选出来的电路,叫做数据选择器,也称多路选择器或多路开关。

数据选择器(MUX)的逻辑功能是在地址选择信号的控制下,从多路数据中选择一路数据作为输出信号,其工作原理如下图所示:图3-1 数据选择器原理图2输入多路选择器(Mux2)的电路中A、B分别为两路输入端口,Sel为数据选择端,Out为数据输出端。

它的逻辑功能是当Sel=0时,选择输入A通过,Y=A;当Sel=1时,选择输入B通过,Y=B。

2输入多路选择器有三个与非门(nand2)和一个反相器构成。

输出信号,其工作原理如下图所示:图3-2 数据选择器逻辑电路图3.2 电路原理图的绘制电路图的绘制采用Cadence软件进行。

首先在windows系统中打开Capture CIS软件以进入Capture的工作环境,然后在软件菜单栏中选择file→new→Project新建一个项目,如下图所示:图3-3 软件新建项目在新建项目的原理图编辑窗口中,执行P1ace/Part命令,在弹出窗口“Libraries”列表框中选择所需元件,移到合适的位置按鼠标左键放置,完成后按ESC键或鼠标右键点end mode以结束元件放置。

调整元件摆放位置,利用快捷键“w”对各个元件进行电气连接,将各个元件按设计要求进行连接。

连接电路图如下:图3-4 整体电路图3.3 电路图仿真二选一数据选择器逻辑表达式为:Y=S’A+SB根据逻辑表达式所列真值表如下所示:图3-5 数据选择器真值表在电路图绘制完毕后,首先执行PSpice/Create Netlist命令建立电路网表;然后执行PSpice/New Simulation Profile命令,在弹出窗口中进行仿真参数类型设置;最后执行PSpice/Markers/V oltage Level命令,放置仪器探头进行测量仿真,发现仿真结果和理论相符合。

仿真结果如下图:图3-4 整体电路仿真结果4集成电路版图设计4.1 CMOS数字电路基本单元版图设计4.1.1反相器版图设计图4-1 cmos反相器图4-2 传输特性曲线当输入电压为高时,PMOS因其栅压栅压等于0而截止,而NMOS导通,此时输出电压为低电平而接近0相反,当输入电压为低时,NMOS和PMOS管分别关断和导通。

产生高电平输出电压。

因此,不论那种逻辑状态,串联在高电平和地之间的这两个晶体管中总有一个处于导通状态另一个处于截止状态。

图4-3 非门版图由于非门由一个PMOS和一个CMOS串联而成,因此设计版图的时候可以把两个MOS 串联在一起,以减少图层面积,由于两个MOS的栅极是相连的,故可以直接以poly图层将两个MOS馆相连接。

4.1.2与非门版图设计2输入数据选择器的另外一个主要组成部分是与非门,有两个输入和一个输出。

如果输入为1和0,则输出为1;如果输入为0和0,则输出为1。

与非门则是当输入端中有1个或1个以上是低电平时,输出为高电平;只有所有输入是高电平时,输出才是低电平,下图是与非门的版图设计。

图4-4 与非门原理图从电路图可以看出,与非门是由两个PMOS并联再和两个NMOS串联而成的。

因此在进行版图设计时,可以把两个PMOS的ploy图层画在同一个有源区里面。

然后通过ploy 图层把PMOS和NMOS连接起来。

图4-4 与非门版图4.2 整体版图设计图4-5 数据选择器电路由上述的电路原理图可以看出,一个2输入数据选择器由一个非门和三个与非门组成,因此在绘制版图的时候可以把设计的非门及与非门版图连接一起即可,整体版图设计如下图所示:图4-6 2输入数据选择器版图4.3 设计规则的验证及结果设计规则的验证是版图与具体工艺的接口,因此就显得尤为重要,可以进行设计规则验证(DRC)。

打开要验证单元的版图界面,点击FILE下的DRACULA DRC,弹出在菜单栏上,在DRC菜单下的SETUP中,给出错误文件的路径,即可将错误报告与Virtuoso 的图形界面结合起来,根据错误层的提示,在图中直接修改即可。

修改后再更新编译规则文件,重复进行DRC验证,直至版图完全通过DRC验证。

5总结这次课程设计的主要内容是集成电路版图设计,第一次尝试在电脑上进行版图的设计,有很多地方都不了解,都要通过自己对软件的学习才能顺利的进行实验。

在选取了2输入同或门电路的同时,我开始了版图设计,刚开始时我完全不知怎么着手画版图,于是我通过查找图书馆的资料,学习Tanner集成电路设计方法,并从网上找了一些版图设计的实用教程,渐渐地我开始掌握了画版图的技巧,经过半天的努力,我把各个模块的版图画好了,经过几天的努力终于把整个芯片的版图画完,并最终通过了DRC检查。