单片机与ADC0832的接口技术

ADC0832

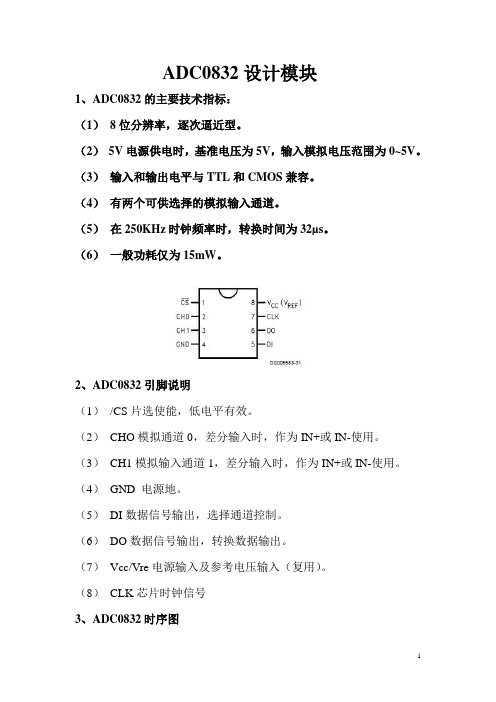

ADC0832设计模块1、ADC0832的主要技术指标:(1)8位分辨率,逐次逼近型。

(2)5V电源供电时,基准电压为5V,输入模拟电压范围为0~5V。

(3)输入和输出电平与TTL和CMOS兼容。

(4)有两个可供选择的模拟输入通道。

(5)在250KHz时钟频率时,转换时间为32µs。

(6)一般功耗仅为15mW。

2、ADC0832引脚说明(1)/CS片选使能,低电平有效。

(2)CHO模拟通道0,差分输入时,作为IN+或IN-使用。

(3)CH1模拟输入通道1,差分输入时,作为IN+或IN-使用。

(4)GND 电源地。

(5)DI数据信号输出,选择通道控制。

(6)DO数据信号输出,转换数据输出。

(7)Vcc/Vre电源输入及参考电压输入(复用)。

(8)CLK芯片时钟信号3、ADC0832时序图4、运用ADC0832设计一个0-5V的数字电压表电路如图所示:设计要求:五位数码管动态显示,第一位显示通道状态(0、1)第二位显示C,第三位是个数,第三位和第四位数码管分别显示十分位和百分位;按键SW1选择通道0,按键SW2选择通道1,并且蜂鸣器和短时间鸣叫;调节滑动变阻器数码管的示数能在0.00~5.00之间变化。

C程序:/************************************************CAUCyeyongan*************************************************/#include <reg52.h>#include <intrins.h>#define uchar unsigned charsbit CS=P3^5;sbit Clk=P1^6; //时钟sbit DO=P3^7; //ADC0832输出引脚sbit DI=P3^6; //ADC0832输入引脚sbit key=P3^3; //按键bit keydownflg; //操作位的定义bit adc_flg;uchar dat,channel;uchar key_buffer;uchar P2_buffer;uchar Beep_cnt;uchar disp_cnt;uchar count4ms;uchar disp_buff[5]; //数码管显示缓存uchar code Tab1[]={0xC0,0xF9,0xA4,0xB0,0x99,0x92,0x82,0xF8,0x80,0x90,0x88,0x83,0xA7,0 xA1,0x86,0x8E}; //共阳数码表uchar code Tab[5]={0x7f,0xbf,0xdf,0xef,0xf7}; //数码管位选表uchar A_D(uchar CH) //AD函数{uchar i,adval,test; //定义局部变量并初始化adval=0x00;test=0x00;Clk=0; //clk低电平DI=1; //DI初始高电平在第一个时钟脉冲的下降沿前保持高电平,表示启动信号_nop_();CS=0; //片选_nop_();Clk=1; //clk上升沿,起始位写入_nop_();if(CH==0x00) //选择通道0{Clk=0; //clk低电平DI=1;_nop_();Clk=1; //clk上升沿,通道0的第一位写入_nop_();Clk=0;DI=0;_nop_();Clk=1; //clk上升沿,通道0的第二位写入_nop_();}else{Clk=0;DI=1;_nop_();Clk=1; //clk上升沿,通道1的第一位写入_nop_();Clk=0;DI=1;_nop_(); //clk上升沿,通道1的第二位写入Clk=1;_nop_();}Clk=0;DI=1;for(i=0;i<8;i++) //从高位向低位读取八位AD值{_nop_();adval<<=1;Clk=1;_nop_();Clk=0;if(DO)adval|=0x01;elseadval|=0x00;}for(i=0;i<8;i++){test>>=1; //从低位向高位读取八位AD值if(DO)test|=0x80;elsetest|=0x00;_nop_();Clk=1;_nop_();Clk=0;}if(adval==test) dat=test; //判断两个读取值是否相等相等就把读取的数赋值给DAT_nop_();CS=1;DO=1;Clk=1;return dat;}void FillDispBuffer(void) //数码管显示缓存函数{disp_buff[0]=channel; //显示通道disp_buff[1]=12; //显示"C"disp_buff[2]=dat/51; //显示个位disp_buff[3]=dat%51*10/51; //显示十分位disp_buff[4]=((dat%51)*10%51)*10/51; //显示百分位}void dealkey(void) //按键处理{if(keydownflg) return; //keydownflg控制位为1,不对按键进行处理key_buffer=P2;if((key_buffer&0x80)!=0x80) channel=0; //选择通道0if((key_buffer&0x40)!=0x40) channel=1; //选择通道1FillDispBuffer(); //数码管显示缓存Beep_cnt=0;keydownflg=1; //keydownflg控制位置1 }void main(void) //主函数{P0=0xff; //初始化P2=0xff;dat=0x00;disp_cnt=0;count4ms=0;channel=0;TMOD=0x10;TH0=(65535-4000)/256;TL0=(65535-4000)%256;EA=1;TR0=1;ET0=1;while(1){if(adc_flg) //ADC转换控制位,防止输入与输出产生冲突{adc_flg=0;A_D(channel); //ADC函数FillDispBuffer(); //数码管显示缓存}if(!key) //按键dealkey();}}void T0_service(void) interrupt 1 //定时器0中断子函数{TH0=(65535-4000)/256;TL0=(65535-4000)%256;P2_buffer=Tab[disp_cnt]; //查表,数码管的位选择if(keydownflg) //蜂鸣器0.4s的短时间鸣叫{P2_buffer=P2_buffer&0xfe;Beep_cnt++;if(Beep_cnt==100) keydownflg=0;}P2=P2_buffer; //数码管显示数字符号if(disp_cnt==2) //第三位数码管显示小数点P0=Tab1[disp_buff[disp_cnt]]&0x7f;elseP0=Tab1[disp_buff[disp_cnt]];disp_cnt++; //if(disp_cnt==5) disp_cnt=0;count4ms++;if(count4ms==50) //0.2s ADC转换一次{adc_flg=1;count4ms=0;}}。

6.4 DAC0832与单片机的接口

与 DAC0832

与

VREF RFB Iout1 Iout2 AGND

VCC DGND

MCS-51与8位DAC0832的接口

有缘学习更多+谓ygd3076考证资料或关注桃报:奉献教育(店铺)

DAC0832

DAC0832 20

CS WR1 GND

DI3 DI2

DI1 DI0 VREF RFB DGND

《单片机原理及应用》

MCS-51与8位DAC0832的接口

MCS-51 8 DAC0832

DAC0832 DAC0832

(NS)

8T

D/A

1us

MCS-51与8位DAC0832的接口

DAC0832

DI0~DI7

ILE CS WR1

WR2 XFER

输入

DAC

D/A

寄

寄

转

存

存

换

器

器

器

与 LE1

LE2

uchar i; while(1) {

for (i=0;i<0xff;i++){ DAC0832=i;

} } }

谢 谢!

MCS-51与8位DAC0832的接口

DAC0832

D/A

D/A

CPU D/A

D/A

MCS-51与8位DAC0832的接口

V FFH

00H

t

T

D/A

有缘学习更多+谓ygd3076考证资料或关注桃报:奉献教育(店铺)

P2.7 8051 WR

P0.0~P0.7

+5V

VCC

ILE CS

WR1 DI0~DI7

WR2 XFER DGND AGND

单片机课件(ADC0809和DAC0832)

解:

MAIN: MOV R1,#40H

;置数据区首址

MOV R7,#8

;置通道数

SETB P1.0

;置P1.0输入态

MOV DPTR,#0FEF8H ;置0809通道0地址

LOOP: MOVX @DPTR,A

;启动A/D

JNB P1.0,$

;查询A/D转换结束否?未完继续查询等待

MOVX A,@DPTR

2021/7/13

14

2、硬件电路设计

该芯片既可用于A/D转换(模拟信号从AIN0~AIN3输 入),又可用于D/A转换(D/A转换模拟量从AOUT输出), 器件地址为1001,若A2A1A0接地,D/A转换写寻址字节 SLAW=90H,A/D转换读寻址字节SLAR=91H。

2021/7/13

15

MOV NUMB,#1

;置发送字节数

LCALL WRNB

;发送控制命令字

MOV R0,#50H

;置A/D数据区首址

VADC0: MOV SLA,#91H

;置接收寻址字节

MOV NUMB,#2

;置接收字节数

LCALL RDNB

;读A/D转换数据

MOV @R0,41H

;存A/D转换数据(存在50H~53H)

2021/7/13

12

ADC3: JNB RI,ADC3

;接收第二字节

CLR RI

;清接收中断标志

MOV A,SBUF

;读第二字节数据

ANL A,#0FH

;第二字节屏蔽高4位

ANL B,#0FOH

;第一字节屏蔽低4位

ORL A,B

;组合

SWAP A

;高低4位互换,组成正确的A/D数据

STC单片机11F01及ADC0832、TM1640组合应用(C语言,经过验证)

STC单片机11F01及ADC0832、TM1640组合使用使用STC 11F01单片机,和ADC0832模数转换芯片,TM1640数码管驱动芯片构成两通道数据输入,分别显示在两组各4颗数码管显示电路。

其中查找了N多资料,很多有写的错误地方,只能用于参考,经调试,下面的C语言调试成功。

开始的程序:#include<reg52.h>#include<intrins.h>#define uint unsigned int#define uchar unsigned char#define nop _nop_()uchar code table[]={0x3f,0x06,0x5b,0x4f,0x66,0x6d,0x7d,0x07,0x7f,0x6f}; //共阴极编码sbit din=P1^3; //P1.3连接TM1640的DIN口sbit clk=P1^2; //P1.2连接TM1640的SCLK口sbit adcs=P3^7; //P3.7连接ADC0832的CS使能端口sbit adclk=P1^0; //P1.0连接ADC0832的CLK时钟输入口sbit addin=P1^1; //ADC0832的D0和D1是分时工作的,所以这两个端口可以接在同一个IO口,P1.1uchar addata;bit y; //位数据,以0和1区别两个通道的输入和输出ADC0832的启动子函数:void adstart() //ADC0832开始子函数{/*说明:根据ADC0832芯片资料,CS使能=1,禁止,CLK和D0/D1随意;需要转换时,先将CS=0使能,并保持到数据传输完成;单片机向CLK输入脉冲,前3个脉冲为启动和通道控制,脉冲上升沿有效;第一个脉冲前使D1=1,启动信号传输;在第二个和第三个脉冲前分别输入两位数字选择输入通道。

10=CH0,11=CH1*/adcs=1;adclk=0;addin=0;nop;adcs=0; //CS=0使能// nop;addin=1; //D1=1必须写在CS=0之后// nop;// nop;adclk=1; //第一个脉冲// nop;// nop;adclk=0;// nop;// nop;adclk=1; //第二个脉冲.之前已经定义了D1=1,这里不用再定义// nop;// nop;adclk=0;if(y==0)addin=0; //如果Y=0,addin=0,通道控制输入信号为10,选择CH0通道,否则为11=CH1通道// nop;// nop;adclk=1; //第三个脉冲// nop;// nop;adclk=0;// nop;// nop;addin=1; //必须在这里置1(高电位)。

单片机与D-A转换器的接口

当 WR1变为高电平时,输入寄存器便将输入数据锁存。 当 XFER 与 WR2 同时为低电平时,使得 LE2 =1,DAC寄存 器的输出随其寄存器的输入而变化, WR2 变为高电平时输入 寄存器的数据被锁存在该寄存器中。

1. DAC0832的性能介绍

分辨率:8位,即输入数字量的最大位数是8位; 转换时间:1μs; 线性误差:2%FSR(满量程); 有两种工作方式:双缓冲器方式和单缓冲器方式; 输入数字信号与TTL电平兼容;

只需在满量程下调整其线性度; 单一电源供电:+5~+15V; 低功耗:20mW。图10.1 DAC0832的引脚

Vcc:电源输入端。

AGND:模拟信号地。

DGND:数字信号地。

3. DAC0832的逻辑结构

DAC0832的逻辑结构如图10.2所示。它是由两2个8位寄存 器和1个8位D/A转换器组成。D/A转换器采用T形解码网络,2个 8位寄存器分别为输入寄存器和DAC寄存器。

DI0~DI7

ILE

CS

WR1 XWFERR2

图中1#0832输入寄存器的片选信号是P2.5,地址为0DFFFH, 2#0832输入寄存器的片选信号是P2.6,地址为0BFFFH。1#0832 和2#0832的ADC寄存器传送控制信号同时由一个片选信号P2.7 控制,因此地址均7FFFH,当选通ADC寄存器时,各自输入寄存 器中的数据可以同时进入各自的ADC寄存器以达到同时转换, 然后同时输出的目的。

所以通过相应的控制信号可以使DAC0832工作于单缓冲 器工作方式和双缓冲器工作方式。

4. DAC0832与8031的接口电路

单片机原理与接口技术_第9章___A/D、D/A转换接口

在实际应用中,通常利用传感器将被控对象的 物理量转换成易传输、易处理的连续变化的电信号, 然后再将其转换成计算机能接受的数字信号,完成 这种转换任务的器件称为模/数(A/D)转换器。而 将计算机输出的数字信号转换为被控对象能接受的 模拟信号的器件称为数/模(D/A)转换器。

9.2 D/A转换接口DAC0832

D/A转换器在测控系统中将计算机产生的数字量控制

信号转换成模拟信号,用于驱动外部执行机构。

DAC0832 是带有两级数据输人缓冲锁存器的 8位D /A转换器。其引脚如图9-2所示。

D/A转换器的基本原理

D/A转换器的基本功能是将一个用二进制表示的

数字量转换成相应的模拟量。实现这种转换的

基本方法是对应二进制数的每一位,产生一个

9.3 模/数转换器ADC0809

A/D转换器是测控系统中将模拟信号转换成数字信 号的重要器件。 ADC0809是一种典型的A/D转换器,是8位8通道的 A/D转换器,其引脚如图9-7所示。

A/D转换器的外部特性

各集成A/D转换芯片的封装不尽相同,性能各异。但从原理和应

用的角度来看,任何一种A/D转换器芯片一般具有以下控制信

. D/A转换器的主要参数

(1) 分辨率:D/A转换器能够转换的二进制的位数,

一般有8、10、12位,位数越多分辨率越高。

(2) 转换时间:一般在几十个纳秒至几个微秒。

(3) 线性度:转换器模拟输出偏离理想输出的最 大值。 (4) 输出电平:电流型和电压型两种。

9.2.2

MCS-51与DAC0832的接口

止所需的时间间隔。

9.3.1

ADC0809的结构

ADC0809由一个8位A/D转换器、一个8路模拟量 开关、8路模拟量地址锁存/译码器和一个三态数据输 出锁存器组成,其内部结构如图9-8所示。

adc0832的工作原理

adc0832的工作原理ADC0832是一款8位精密模数转换器,它具有许多特性,使其成为许多数字系统的理想选择。

在本文中,我们将深入探讨ADC0832的工作原理,以便更好地理解它的功能和应用。

首先,让我们来了解一下ADC0832的基本工作原理。

ADC0832采用了双重转换技术,即首先进行采样保持(S/H)转换,然后进行模数(A/D)转换。

在采样保持转换阶段,输入信号被采样并保持在一个电容器中,以确保在进行模数转换时能够获得准确的输入信号。

接下来,在模数转换阶段,采样保持电压被转换成相应的数字输出,该输出可以通过数字接口进行读取和处理。

ADC0832的工作原理主要涉及到其内部的运算放大器、采样保持电路和模数转换器。

首先,运算放大器负责放大输入信号,并将其传递给采样保持电路。

采样保持电路则负责对输入信号进行采样和保持,并将其传递给模数转换器进行数字化处理。

模数转换器则将模拟信号转换为相应的数字输出,以便于数字系统进行进一步处理和分析。

此外,ADC0832还具有一些特殊的工作原理,如内部参考电压源和串行接口。

内部参考电压源可以提供稳定的参考电压,以确保模数转换的准确性和稳定性。

而串行接口则可以方便地与微控制器或其他数字系统进行通信,实现数据的传输和控制。

总的来说,ADC0832的工作原理是基于运算放大器、采样保持电路和模数转换器的协同作用,通过将模拟信号转换为数字输出,实现对输入信号的准确采样和数字化处理。

同时,其内部的特殊工作原理也为数字系统的应用提供了便利和稳定性。

在实际应用中,了解ADC0832的工作原理对于正确使用和优化其性能至关重要。

只有深入理解其内部原理,才能更好地设计和调试数字系统,实现更高的性能和稳定性。

因此,通过深入研究和理解ADC0832的工作原理,可以更好地发挥其在各种数字系统中的作用,为工程应用提供更多可能性和创新空间。

综上所述,ADC0832是一款功能强大的8位精密模数转换器,其工作原理基于运算放大器、采样保持电路和模数转换器的协同作用。

A-D转换原理与接口

;再次启动A/D转换

RETI

;中断返回

END

C语言参考程序:

#include <reg51.h>//包含特殊功能寄存器库

#include <absacc.h>

//包含定义绝对地址访问库

#define uchar unsigned char //定义uchar为无符号字符数据

类型

#define IN0 XBYTE[0x0000] //定义IN0为通道0的地址

单片机原理与应用

A/D转换原理与接口

1.1 A/D转换器常用芯片简介 A/D转换器是将模拟信号转换为数字信号的器件,种类繁多,性能各

异。与单片机的接口形式也不尽相同,但大致分为并行接口和串行接口两 种。

1、ADC0809

ADC0809具有8路模拟量输入,可在程序控制下对任意通道进行A/D转 换,输出8位二进制数字量。与单片机之间是并行通信。其内部逻辑结构和 引脚如图8-2所示。

CLK=1; //第二个脉冲,第2、3个脉冲下降之前,DI必须分别输入两位数

据用于选择//通道,这里选通道CH0

CLK=0; //第二个脉冲下降沿

DIO=0; //DI置0,选择通道0

CLK=1; //第三个脉冲

CLK=0; //第三个脉冲下降沿

DIO=1; //第三个脉冲下降沿之后,输入端DIO失去作用,应置1

换电路(ADC0832)转换成数字量,并按顺序依次存于片内RAM的

30H~39H单元中。采样完10次后停止。

汇编语言数据采集串行A/D转换参考程序:

ORG 0000H

;

AJMP MAIN

ORG 0100H

MAIN:MOV R7,#0AH

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

串行接口的 % 位 & : ’ 转换

器, 通过三线接口与单片机连接, 功耗低, 性能价格比较 高, 芯片引脚少, 适宜在袖珍式智能仪器中使用。 主要特 点有: 逐次逼近型, 基 准 电 压 为 => ; 输入模 % 位分辨率, 拟 信 号 电 压 范 围 为 "?=> ; 输 入 和 输 出 电 平 与 @@A 和 在 !="CDE 时 钟 频 率 时 , 转 换 时 间 为 )!6<; (8B+ 兼 容 ; 具有两个可供选择的模拟输入通道; 功耗低, F=3G。 一、 引脚排列

!" #$%&’

信 息 技 术

单 片 机 与 &’( "%)! 的 接 口 技 术

郑州铁路职业技术学院 中原工学院

&’("%)! 是 *+( *,-./0,1

产 的 具 有 8.47/9.72 : ;16<

梁明亮 王新强

+23.4/0564-/7)公 司 生

三、 工作时序 选 中 &’("%)! 。 在 时 钟 的 上 升 当 (+ 由高 变 低 时 , 沿, ’H 端 的 数 据 移 入 &’("%)! 内 部 的 多 路 地 址 移 位 寄 存器。在第一个时钟期间, 表示启动位, 紧接着 ’H 为高, 输入两位配置位。当输入启动位和配置位后, 选通输入 模拟通道, 转换开始。 转换开始后, 经过一个时钟周期延 迟, 以使选定的通道稳定。&’("%)! 接着在第 P 个时钟 下降沿输出转换数据。数据输出时先输出最高位( ’Q? 输出完转换结果后, 又以最低位开始重新输出一 ’" ); 遍数据( ’Q?’" ), 两 次 发 送 的 最 低 位 共 用 。 当 片 选 (+ 为高时, 内部所有寄存器清 " , 输出变为高阻态。如果要 再 进 行 一 次 模 : 数 转 换 , 片 选 (+ 必 须 再 次 从 高 向 低 跳 变, 后面再输入启动位和配置位。 四、 单片机与 &’("%)! 的 +;H 串行典型接口

!"

)3+!! )3,

)3

5-!

且 " )5678 { " )3, !! )3}

(.)

最大最小公平性可以通过一个所谓的“填充过程” 图. 简单的线性网络模型 来实现。按照最大最小公平性的定义, 在图 . 的线性网 络中, 业务流带宽分配应当如下式所示:

&! : -&* 9:; *&-&B; -&B5"

图F

M*’ P =

+;H( +27.,1

;27.RS27,1

H0-27T,42 )是 8B@BJBA&

&’("%)! 引脚图

公司推出的一种同步串行外设接口,允许 8(U 与各个 厂家生产的标准外围设备接口,以串行方式交换信息。 将 图 ! 为 &@%V+=F 与 &’( "%)! 的 +;H 串行接口方式,

启 始 位 YF , 对 (D" 通 道 &, X")D; (DFY" 、 (D"YF 、

P%

河南科技 !""#$% 上

!" #$%&’信 息 技术网络拥塞控制中的公平性

信阳职业技术学院

众所周知,网络拥塞控制一般要达到两个目标, 即 效率和公平。 在现实生活中, 对于公用资源的公平利用, 其重要性甚至要超过对资源的有效使用。 一个公用的网 络应当尽量为每个用户提供公平的服务。 在讨论公平性之前, 应先建立一个网络模型, 即把 每条链路 ! ( !! &)都 有 带 网 络 看 作 一 组 链 路 的 集 合 &, 宽 ’!(" , 另外网络上还有一组业务流相互竞争以访问这 些链路, 每个业务流与一条路径相关联, 一条路径是链 记( !! ")表示路径 ) 穿过链路 路的集合 & 的一个子集。

>(( : JKL 为正电源端和基准电压输入端。 M*’ 为电源地。

二、 配置位说明

&’( "%)! 的 (+ 和 (AI 分 别 接 单 片 机 的 ;F$P 和 ;F$=

引脚, 将 ’H 和 ’B 分别接 ;F$# 和 ;F$# 引脚。对 (D" 通 道的模拟信号实行 & : ’ 转换,转换结果传送给 ;" 口 。 下面以单片机汇编语言对其编程。

写入一位 9:; @A , -;

D:E; FGHI -&B; -&B5. @JDK D:E; FGHI -&B

控制读 @: 的位数为 % 位, 即读转换结果 9:; *<, ="%?; 控制连续写三个位 *< , &. ; 延时一个时钟, 使选定的通道稳定 -&* -&B;

1!2 赖麒文 $%"P. 单片机 - 语言彻底应用 $ 北京 N 科学技术出

&’("%)! 有 ’H; 和 +BH( 两 种 封 装 , ’H; 封 装 的 &’("%)! 引脚排列如图 F 所示。

各引脚说明如下:

低电平有效。 (+ 为片选端,

(+

F % ! Q ) #

>44:J2T (AI ’B ’H

(D" (D" , (DF 为两路模拟信号输入端。(DF ’H 为两路模拟输入选择输入端。 ’B 为模数转换结果串行输出端。 (AI 为串行时钟输入端。

数字量串行输出结束, 置位 -F FGHI -F ; 转换结果传送给 E" 口 9:; E" , C; 进行下一次 CL@ 转换 FJ9E FHC*H; 参考文献 等 $CH%M 系 列 单 片 机 原 理 与 接 口 技 术 $ 北 京 N 北 1.2 王 幸 之 , 京航空航天大学出版社, !""O$

版社, !""!$

河南科技 !""#$% 上

OM

(D" N O N

(DF O N N

图 !: &@%V+=F 与 &’("%)! 的 +;H 串行接口方式

单

端

表中“ N”表示输入通道的端点为正极性; “ O”表示 输入端点为负极性; 低电平。 输入配置位 D 或 A 表示高、 低位( (DF )在后。 时, 高位( (D" )在前,

BJM""""D +@&J@: (AJ (+ 8B>

;F$P ;F$= ;F$# ;F$Q &@%V+=F

(+ (AI ’H ’B KWU KWU KWU KWU

(+ (AI (D" ’H ’B &’("%)!

片选 ;F$P ; 串行时钟输入端 ;F$= ; 模拟输入选择输入端 ;F$# ; 数字量串行输出线 ;F$Q ;

(D" A A D D

(DF A D A D

!,记 * 表示路径的集合。这里我们假设业务流是固定

的, 研究公平性的目的就是寻找链路带宽的分配方法以 使所有的流满足某种共享目标。记 " ) 为路径 ) 的带宽 分配。很显然,可行的带宽分配必须满足

!"

)+!! ),

)

!-!,

!! # 的约束。

为讨论几种公平性, 我们用图 . 所示的一个简单的 线性网络来阐述不同的分配策略。

苏锡亮

李

君

这些路径的集合记为 *"; 有 $0 条 $" 条路径穿过所有链路, 这些路径的集合记为 *( 。 路径仅仅穿过链路 !, ! !! &) 要 使 网 络 达 到 最 高 使 用 效 率 的 目 标 1.2, 也就对应着 对带宽的可行分配 " ) 应当满足最大化

!"

)! *

)

的约束条

件。 然而这样的带宽分配目标却可能导致有些流根本分 配不到带宽, 而这样做却是不公平的, 所以要想带宽分 配达到公平性, 效率通常是要做折衷的, 也就是说, 带宽 分配只能在满足某种公平性标准的基础上追求效率。 一、 最大最小公平性 用于定义数 最大最小公平性最早出现在文献[ .]中, 据网络公平性的标准。 它的目标就是在网络容量的约束 条件下, 可行流的分配{ " )/"! * }中将最小的那一个 可 行分配最大化, 这也是它名称的由来。 更确切地说, 最大 最小公平性的可行分配可定义如下, 增加任何一个可行 ( " )34 分 配 " ), 都 必 然 导 致 某 个 其 他 的 可 行 分 配 " )3 对每一条可行路 " ))的降低。该定义的形式化表述为: 至少有一条链路 !! ), 使 +.,成立(已证明): 径 ),

&’("%)! 工 作 时 , 模 拟 通 道 的 选 择 及 单 端 输 入 和

差分输入的选择, 都取决于输入时序的配置位。当差分 输入时, 要分配输入通道的极性, 两个输入通道的任何 一 个 通 道 都 可 作 为 正 极 或 负 极 。 &’("%)! 的 配 置 位 逻 辑表如表 F 所列。 表F 配置位 输入格式 差 分 选择通道号

转换结果暂存 C 中 C;

有 图中, 网络由具有单位带宽容量的 /&/条链路组成,

的模拟信号进行转换

9:;

控制往 @A 写位的位数为 > 位, 即写 . 位 *< , =">?;