lab4

BOBeoLab4音响中的“高富帅”[权威资料]

![BOBeoLab4音响中的“高富帅”[权威资料]](https://img.taocdn.com/s3/m/2a09b7362e60ddccda38376baf1ffc4ffe47e23f.png)

B&O BeoLab 4音响中的“高富帅”作为一个标新立异的时尚音响品牌,BO很多时候给人的感觉就是华丽的外形和高不可攀的价格,而其华丽的造型和优质的声音也一直备受众多用户青睐。

要说到丹麦的BO,绝大部分人的第一反应就是贵。

的确,作为一个标新立异的时尚音响品牌,BO很多时候给人的感觉就是华丽的外形和高不可攀的价格,就拿今天的BeoLab 4来说,作为一款品牌中入门级的电脑音响,其价格就在万元,而且选配的支架价格都在几千元,如此高的定价也注定了这是一个小众的品牌,一个属于高富帅的品牌。

如果你是一个设计控,如果你要彰显你不凡的品味和财力,那么恭喜你,BO绝对适合你。

O的故事国际设计界BangOlufsen(简称BO)是一个非常响亮的名字,在每年的国际设计年鉴和其他设计刊物上,在世界各地的设计博物馆和设计展览中,BO公司的设计都以其新颖、独特而受到人们的关注。

在中国的设计师和音响发烧友中,BO已经有了相当的认知度。

BO是丹麦一家生产家用音像及通讯设备的公司。

多年来,该公司把设计视为生命线,一方面系统地研究新产品的技术开发,另一方面瞄准国际市场上的最高层次,并致力于使技术设施适合于家庭环境,设计出了众多质量优异、造型高雅、操作方便并富于公司一贯特色的产品,达到了世界一流的水准,享誉西方各国。

BO的设计成了丹麦设计的经典和象征。

1925午11月17日,两位年轻的丹麦工程师Peter Bang和Svend Olufsen在丹麦小镇Quistrup一间小小的阁楼里合伙创立了BangOlufsen公司,设计和生产收音机,揭开了BO公司辉煌历史的序幕。

到1927年,公司已有30余名员工,生产出了当时十分先进的七灯电子管收音机,能自然而逼真地重现电台播送的音乐和其他节目,为公司带来了良好的商誉。

1928年,公司正式启用BO商标,商标的字体设计明显受到包豪斯平面设计风格的影响,颇具现代感,被一直沿用至今。

不久,该商标就与公司的著名广告语“丹麦质量的标志”一并使用,成了丹麦最有影响、最有价值的品牌之一。

北邮电子院专业实验报告

电子工程学院ASIC专业实验报告班级:姓名:学号:班内序号:第一部分语言级仿真LAB 1:简单的组合逻辑设计一、实验目的掌握基本组合逻辑电路的实现方法;二、实验原理本实验中描述的是一个可综合的二选一开关,它的功能是当sel = 0时,给出out = a,否则给出结果out = b;在Verilog HDL中,描述组合逻辑时常使用assign结构;equal=a==b1:0是一种在组合逻辑实现分支判断时常用的格式;parameter定义的size参数决定位宽;测试模块用于检测模块设计的是否正确,它给出模块的输入信号,观察模块的内部信号和输出信号;三、源代码module scale_muxout,sel,b,a;parameter size=1;outputsize-1:0 out;inputsize-1:0b,a;input sel;assign out = sela:selb:{size{1'bx}};endmodule`define width 8`timescale 1 ns/1 nsmodule mux_test;reg`width:1a,b;wire`width:1out;reg sel;scale_mux`widthm1.outout,.selsel,.bb,.aa;initialbegin$monitor$stime,,"sel=%b a=%b b=%b out=%b",sel,a,b,out;$dumpvars2,mux_test;sel=0;b={`width{1'b0}};a={`width{1'b1}};5sel=0;b={`width{1'b1}};a={`width{1'b0}};5sel=1;b={`width{1'b0}};a={`width{1'b1}};5sel=1;b={`width{1'b1}};a={`width{1'b0}};5 $finish;endendmodule四、仿真结果与波形LAB 2:简单时序逻辑电路的设计一、实验目的掌握基本时序逻辑电路的实现;二、实验原理在Verilog HDL中,相对于组合逻辑电路,时序逻辑电路也有规定的表述方式;在可综合的Verilog HDL模型中,我们常使用always块和posedge clk或negedge clk的结构来表述时序逻辑;在always块中,被赋值的信号都必须定义为reg型,这是由时序逻辑电路的特点所决定的对于reg 型数据,如果未对它进行赋值,仿真工具会认为它是不定态;为了正确地观察到仿真结果,在可综合的模块中我们通常定义一个复位信号rst-,当它为低电平时对电路中的寄存器进行复位;三、源代码`timescale 1 ns/100 psmodule countercnt,clk,data,rst_,load;output4:0cnt ;input 4:0data;input clk;input rst_;input load;reg 4:0cnt;alwaysposedge clk or negedge rst_ifrst_cnt<=0;elseifloadcnt<=3 data;elsecnt<=4 cnt + 1;endmodule`timescale 1 ns/1 nsmodule counter_test;wire4:0cnt;reg 4:0data;reg rst_;reg load;reg clk;counter c1t cnt,.clk clk,.datadata,.rst_rst_,.loadload;initial beginclk=0;forever begin10 clk=1'b1;10 clk=1'b0;endendinitialbegin$timeformat-9,1,"ns",9;$monitor"time=%t,data=%h,clk=%b,rst_=%b,load=%b,cnt=%b", $stime,data,clk,rst_,load,cnt;$dumpvars2,counter_test;endtask expect;input 4:0expects;ifcnt ==expectsbegin$display"At time %t cnt is %b and should be %b", $time,cnt,expects;$display"TEST FAILED";$finish;endendtaskinitialbeginnegedge clk{rst_,load,data}=7'b0_X_XXXXX;negedge clkexpect5'h00;{rst_,load,data}=7'b1_1_11101;negedge clkexpect5'h1D;{rst_,load,data}=7'b1_0_11101;repeat5negedge clk;expect5'h02;{rst_,load,data}=7'b1_1_11111;negedge clkexpect5'h1F;{rst_,load,data}=7'b0_X_XXXXX;negedge clkexpect5'h00;$display"TEST PASSED";$finish;endendmodule四、仿真结果与波形五、思考题该电路中,rst-是同步还是异步清零端在的always块中reset没有等时钟,而是直接清零;所以是异步清零端;LAB 3:简单时序逻辑电路的设计一、实验目的使用预定义的库元件来设计八位寄存器;二、实验原理八位寄存器中,每一位寄存器由一个二选一MUX和一个触发器dffr组成,当load=1,装载数据;当load=0,寄存器保持;对于处理重复的电路,可用数组条用的方式,使电路描述清晰、简洁; 三、源代码`timescale 1 ns /1 nsmodule clockclk;reg clk;output clk;initial beginclk=0;forever begin10 clk=1'b1;10 clk=1'b0;endendendmodulemux及dffr模块调用代码mux mux7.outn17,.selload,;dffr dffr7 .qout7, .dn17, .clkclk, .rst_rst_ ;mux mux6 .outn16, .selload, .bdata6, .aout6;dffr dffr6 .qout6, .dn16, .clkclk, .rst_rst_ ;mux mux5 .outn15, .selload, .bdata5, .aout5;dffr dffr5 .qout5, .dn15, .clkclk, .rst_rst_ ;mux mux4 .outn14, .selload, .bdata4, .aout4;dffr dffr4 .qout4, .dn14, .clkclk, .rst_rst_ ;.selload, .bdata3, .aout3;dffr dffr3 .qout3, .dn13, .clkclk, .rst_rst_ ;mux mux2 .outn12, .selload, .bdata2, .aout2;dffr dffr2 .qout2, .dn12, .clkclk, .rst_rst_ ;mux mux1 .outn11, .selload, .bdata1, .aout1;dffr dffr1 .qout1, .dn11, .clkclk, .rst_rst_ ;mux mux0 .outn10, .selload, .bdata0, .aout0;dffr dffr0 .qout0, .dn10,;例化寄存器register r1.datadata,.outout,.loadload,.clkclk,.rst_rst_;例化时钟clock c1.clkclk;添加检测信号initialbegin$timeformat-9,1,"ns",9;$monitor"time=%t,clk=%b,data=%h,load=%b,out=%h",$stime,clk,data,load,out;$dumpvars2,register_test;end四、仿真结果与波形LAB 4:用always块实现较复杂的组合逻辑电路一、实验目的掌握用always实现组合逻辑电路的方法;了解assign与always两种组合逻辑电路实现方法之间的区别;二、实验原理仅使用assign结构来实现组合逻辑电路,在设计中会发现很多地方显得冗长且效率低下;适当地使用always来设计组合逻辑,会更具实效;本实验描述的是一个简单的ALU指令译码电路的设计示例;它通过对指令的判断,对输入数据执行相应的操作,包括加、减、或和传数据,并且无论是指令作用的数据还是指令本身发生变化,结果都要做出及时的反应;示例中使用了电平敏感的always块,电平敏感的触发条件是指在后括号内电平列表的任何一个电平发生变化就能触发always块的动作,并且运用了case结构来进行分支判断;在always中适当运用default在case结构中和else子if…else结构中,通常可以综合为纯组合逻辑,尽管被赋值的变量一定要定义为reg型;如果不使用default或else对缺省项进行说明,易产生意想不到的锁存器;三、源代码电路描述alwaysopcode or data or accumbeginifaccum==8'b00000000zero=1;elsezero=0;caseopcodePASS0: out =accum;PASS1: out =accum;ADD: out = data + accum;AND: out =data&accum;XOR: out =data^accum;PASSD: out=data;PASS6: out=accum;PASS7: out=accum;default: out=8'bx;endcaseend四、仿真结果与波形LAB 5:存储器电路的设计一、实验目的设计和测试存储器电路;二、实验原理本实验中,设计一个模块名为mem的存储器仿真模型,该存储器具有双线数据总线及异步处理功能;由于数据是双向的,所以要注意,对memory的读写在时序上要错开;三、源代码自行添加的代码assign data= readmemoryaddr:8'hZ;always posedge writebeginmemoryaddr<=data7:0;end四、仿真结果与波形LAB 6:设计时序逻辑时采用阻塞赋值与非阻塞赋值的区别一、实验目的明确掌握阻塞赋值与非阻塞赋值的概念和区别;了解阻塞赋值的使用情况;二、实验原理在always块中,阻塞赋值可以理解为赋值语句是顺序执行的,而非阻塞赋值可以理解为并发执行的;实际时序逻辑设计中,一般情况下非阻塞赋值语句被更多的使用,有时为了在同一周期实现相互关联的操作,也使用阻塞赋值语句;三、源代码`timescale 1 ns/ 100 psmodule blockingclk,a,b,c;output3:0b,c;input 3:0a;input clk;reg 3:0b,c;alwaysposedge clkbeginb =a;c =b;$display"Blocking: a=%d,b=%d,c=%d.",a,b,c;endendmodule`timescale 1 ns/ 100 psmodule non_blockingclk,a,b,c;output3:0 b,c;input3:0 a;input clk;reg 3:0b,c;always posedge clkbeginb<=a;c<=b;$display"Non_blocking:a=%d,b=%d,c=%d",a,b,c;endendmodule`timescale 1 ns/ 100 psmodule compareTop;wire 3:0 b1,c1,b2,c2;reg3:0a;reg clk;initialbeginclk=0;forever 50 clk=~clk;endinitial$dumpvars 2,compareTop;initialbegina=4'h3;$display"_______________________________";100 a =4'h7;$display"_______________________________";100 a =4'hf;$display"_______________________________";100 a =4'ha;$display"_______________________________";100 a =4'h2;$display"_______________________________";100 $display"_______________________________";$finish;endnon_blocking nonblockingclk,a,b2,c2;blocking blockingclk,a,b1,c1;endmodule四、仿真结果与波形LAB 7:利用有限状态机进行复杂时序逻辑的设计一、实验目的掌握利用有限状态机FSM实现复杂时序逻辑的方法;二、实验原理控制器是CPU的控制核心,用于产生一系列的控制信号,启动或停止某些部件;CPU何时进行读指令,何时进行RAM和I/O端口的读写操作等,都由控制器来控制;三、源代码补充代码nexstate<=state+1'h01;casestate1:begin sel=1;rd=0;ld_ir=0;inc_pc=0;halt=0;ld_pc=0;data_e=0;ld_ac=0;wr=0;end2:begin sel=1;rd=1;ld_ir=0;inc_pc=0;halt=0;ld_pc=0;data_e=0;ld_ac=0;wr=0;end3:begin sel=1;rd=1;ld_ir=1;inc_pc=0;halt=0;ld_pc=0;data_e=0;ld_ac=0;wr=0;end4:begin sel=1;rd=1;ld_ir=1;inc_pc=0;halt=0;ld_pc=0;data_e=0;ld_ac=0;wr=0;end 5:begin sel=0;rd=0;ld_ir=0;inc_pc=1;ld_pc=0;data_e=0;ld_ac=0;wr=0;ifopcode==`HLThalt=1;end6:beginsel=0;rd=alu_op;ld_ir=0;inc_pc=0;halt=0;ld_pc=0;data_e=0;ld_ac=0;wr=0;end7:beginsel=0;rd=alu_op;ld_ir=0;halt=0;data_e=alu_op;ld_ac=0;wr=0;ifopcode==`SKZinc_pc<=zero;ifopcode==`JMPld_pc=1;end0:beginsel=0;rd=alu_op;ld_ir=0;halt=0;data_e=alu_op;ld_ac=alu_op;inc_pc=opcode==`SKZ&zero||opcode==`JMP;ifopcode==`JMPld_pc=1;ifopcode==`STOwr=1;endNo.00000000 No.00000000 No.00000101 No.00000001 // 1C TEMP: //1 temporary variable00000001 // 1D time: // 1 constant 144 - max value 00000110 // 1E LIMIT: // 6 constant 1一、仿真结果与波形第二部分电路综合一、实验目的掌握逻辑综合的概念和流程,熟悉采用Design Compiler进行逻辑综合的基本方法;二、实验内容采用SYNOPSYS公司的综合工具Design Compiler对实验7的做综合;三、源代码与实验指导书中相同;四、门级电路仿真结果与波形五、思考题1.文件是verilog语言及的描述还是结构化的描述是结构化的描述;2.文件中,对触发器的延迟包括哪些信息包括对逻辑单元和管脚的上升/下降时延的最大值、最小值和典型值;第三部分版图设计一、实验目的掌握版图设计的基本概念和流程,熟悉采用Sysnopsys ICC工具进行版图设计的方法;二、实验内容对电路综合输出的门级网表进行布局布线;三、源代码与实验指导书中相同;四、仿真结果与波形布局规划后结果未产生core ring和mesh前产生core ring和mesh后电源线和电影PAD连接后filler PAD填充后布局后结果时钟树综合后结果布线后结果寄生参数的导出和后仿五、思考题1.简述ICC在design setup阶段的主要工作;创建设计库,读取网表文件并创建设计单元,提供并检查时间约束,检查时钟;在对之前的数据与信息进行读取与检查后保存设计单元;2.为什么要填充filler padfiller pad把分散的pad单元连接起来,把pad I/O区域供电连成一个整体;使它们得到持续供电并提高ESD保护能力;3.derive_pg_connection的作用是什么描述有关电源连接的信息;4.简述floorplan的主要任务;对芯片大小、输入输出单元、宏模块进行规划,对电源网络进行设计;5.简述place阶段的主要任务;对电路中的延时进行估计与分析,模拟时钟树的影响,按照时序要求,对标准化单元进行布局;6.简述CTS的主要步骤;设置时钟树公共选项;综合时钟树;重新连接扫描链;使能传播时钟;Post-CTS布局优化;优化时钟偏移;优化时序;实验总结经过数周的ASIC专业实验,我对芯片设计流程、Verilog HDL语言、Linux基本指令和Vi文本编辑器有了基本的了解;虽然之前对芯片设计、VHDL一无所知,但通过实验初步熟悉了ASIC的体系结构和VHDL的基本语法,对电路中时钟、寄生参数、元件布局带来的影响也有了了解;我在实验中也遇到了许多问题,但我在老师、助教、同学的帮助下解决了这些问题,也有了更多收获;通过这次ASIC专业实验,我加深了对本专业的认识;我会继续努力成为合格的电子人;。

网络安全lab4-

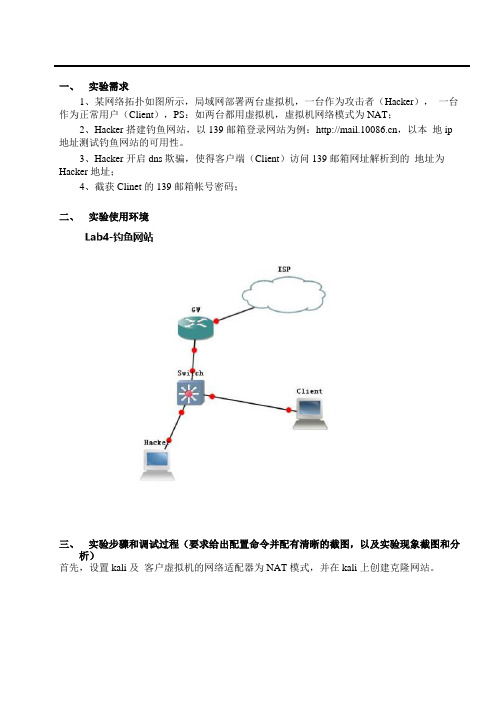

一、实验需求1、某网络拓扑如图所示,局域网部署两台虚拟机,一台作为攻击者(Hacker),一台作为正常用户(Client),PS:如两台都用虚拟机,虚拟机网络模式为NAT;2、Hacker搭建钓鱼网站,以139邮箱登录网站为例:,以本地ip 地址测试钓鱼网站的可用性。

3、Hacker开启dns欺骗,使得客户端(Client)访问139邮箱网址解析到的地址为Hacker地址;4、截获Clinet的139邮箱帐号密码;二、实验使用环境三、实验步骤和调试过程(要求给出配置命令并配有清晰的截图,以及实验现象截图和分析)首先,设置kali及客户虚拟机的网络适配器为NAT模式,并在kali上创建克隆网站。

创建克隆网站1,setoolkit 回车,如有以下提示选择Y。

2,选择1,社会工程学3,选择2,web攻击4,选择3,凭证信息收集5,选择2,网站克隆6,输入网站克隆存放的主机的IP地址,kali eth0的IP 地址7,输入要克隆的网站的链接, 验证克隆网站是否成功,kali浏览器输入127.0.0.1 或者正常用户访问kali的ip地址。

验证克隆网站是否成功,kali浏览器输入127.0.0.1 ,成功运行克隆网站,即表示克隆成功。

正常用户可访问kali的ip地址。

然后,DNS欺骗。

ettercap的使用,修改ettercap.dns中的A记录。

vi /etc/ettercap/etter.dnsettercap工具的使用1,ettercap –G打开工具。

2,选择嗅探接口eth03,先选择主机列表,再选择扫描主机。

4,添加攻击目标1,再添加攻击目标2,一个网关,一个用户。

5,选择中间人攻击,arp欺骗,嗅探远程主机。

6,选择工具,管理工具,双击点击dns_spoof,前面会出现带星号。

7,开始攻击最后,开始测试,xp客户端ping 回复的地址为kali地址。

证明欺骗成功。

xp用户通过浏览器正常访问,并用自己的学号和名字登陆验证。

饥荒海滩物品代码

birdtrap(鸟陷阱)

amulet(红色护身符)

blueamulet(蓝色护身符)

purpleamulet(紫色护身符)

yellowamulet(黄色护身符)

orangeamulet(橙色护身符)

greenamulet(绿色护身符)

pickaxe(镐)

goldenpickaxe(黄金镐)

purplegem(紫宝石)

greengem(绿宝石)

orangegem(橙宝石)

yellowgem(黄宝石)

houndstooth(犬牙)

pigskin(猪皮)

log(木头)

livinglog(活木头)

twigs(树枝)

cutgrass(草)

petals(花瓣)

seaweed 海藻

seaweed_dried 海带

limpets 帽贝

mussel 青口贝

fish_raw_small 爽口鱼

tropical_fish 热带鱼

shark_fin 鱼翅

sweet_potato 红薯

coral_brain 智慧果

clothsail 布帆

snakeskinsail 蛇鳞帆

feathersail 羽毛轻帆

boat_torch 航海火炬

boat_lantern 航海提灯

boatcannon 航海加农炮

seatrap 海洋陷阱

trawlnet 拖网

telescope 望远镜

swordfish 剑鱼

sharx 鲨鱼

stungray 浮游

whale_blue 蓝鲸

Lab4 介绍

3. 使用PDX(VPT)在页目录在查找,得到一个特殊的页

表(SPT)——页目录本身 (自映射的作用)

4. 使用PDX(addr)在SPT(也就是页目录)里找到一个特 殊的页(SPage)——实际上是页表

5. 使用PTX(addr)|00得到页表项

fork() vs dumb_fork()

dumb_fork

dumbfork

一个古老的fork,采用复制地址空间的内容的方法 创建子进程

user/dumbfork.c

fork

实现了copy‐on‐write的fork函数 lib/fork.c

dumbfork流程

1. sys_exofork

env_alloc eax (0) Status (ENV_NOT_RUNNABLE)

关键点

curenv全局变量

在运行第一个用户进程之前,curenv的值为NULL

调度过程

调度过程

envs[1]、envs[2]… envs[NENV‐1]形成一个逻辑 上的环状结构

如果curenv==NULL,就从envs[1]开始检查;否 则就从curenv指向的Env结构的下一个envs数 组元素开始检查。从环上寻找第一个状态为 ENV_RUNNABLE的进程

利用一些系统调用来实现一个用户空间的、写 时复制的库函数fork

用户创建进程相关的系统调用:

sys_exofork sys_env_set_status sys_page_alloc sys_page_map sys_page_unmap

fork()的流程

1. set_pgfault_handler 2. sys_exofork

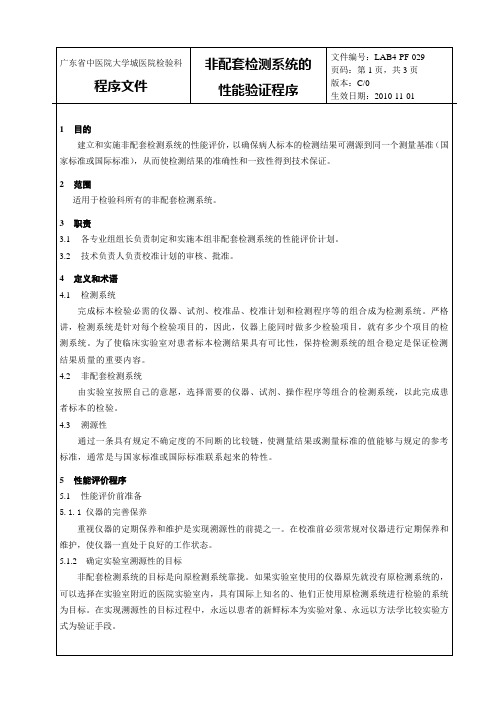

LAB4-PF-029非配套检测系统的性能验证程序

5.2

由实验室按照自己的意愿,选择需要的仪器、试剂、操作程序等组合的检测系统,以此完成患者标本的检验。

溯源性

5.3

通过一条具有规定不确定度的不间断的比较链,使测量结果或测量标准的值能够与规定的参考标准,通常是与国家标准或国际标准联系起来的特性。

性能评价

6

性能评价

6.1

5.1.1

重视仪器的定期保养和维护是实现溯源性的前提之一。在校准前必须常规对仪器进行定期保养和维护,使仪器一直处于良好的工作状态。

广东省中医院检测系统的

性能验证程序

文件编号:LAB4-PF-029

页码:第1页,共3页

版本:C/0

生效日期:2010-11-01

1

2

建立和实施非配套检测系统的性能评价,以确保病人标本的检测结果可溯源到同一个测量基准(国家标准或国际标准),从而使检测结果的准确性和一致性得到技术保证。

5.2.8非配套检测系统分析灵敏度的评估

参照美国国家临床实验室标准化委员会(NCCLS) EP17-A文件要求,对非配套检测系统项目的检测低限、功能灵敏度进行评价。检测低限:测定空白样本20天,计算其均值及标准差。按99.7%可能性定

广东省中医院大学城医院检验科

程序文件

非配套检测系统的

性能验证程序

文件编号:LAB4-PF-029

LAB4-PF-021《检验方法选择和评审程序》

LAB4-PF-023《生物参考区间评审程序》

LAB4-PF-025《检验结果量值溯源管理程序》

LAB4-PF-028《不同检测系统间的比对程序》

页码:第3页,共3页

版本:C/0

生效日期:2010-11-01

义检测低限LLD=X空白+3s空白。功能灵敏度:测定系列低浓度检测限样品20天,计算各浓度的变异系数,绘制浓度与CV的关系曲线图,以理论浓度为X轴,各浓度的变异系数为Y轴,从曲线上查阅CV为20%所对应的浓度,即为功能灵敏度。

Lab4

6 FileI/O

Opening and closing data files. Reading data from and writing data to files. Reading from and writing to spreadsheet-formatted files. Moving and renaming files and directories. Changing file characteristics. Creating, modifying, and reading a configuration file.

1D Array

Waveform graph terminal (1D array)

1D Array

Waveform graph terminal (cluster)

2. Multiple-Plot Waveform Graphs

Build Array function (Array subpalette)

Build Array

1D Arrays

2D array

Waveform graph terminal (2D array)

clusters

cluster array

Waveform graph terminal (cluster array)

5.2 Charts

1. Chart Update Modes

6.2.3 More Writing and Reading of Files

1.Writing and Reading Text Files 可以进行纯文本的读写 Write To Text File Read From Text File 2. Writing and Reading Binary Files

EEE 333 lab4

Explanation: This part is controlling code to realize the adder count up/down, reset, and pause functions.

Pins Assignments for Design

ห้องสมุดไป่ตู้

Time Diagram for Counter Test Bench

Time Diagram for Display Controller Test Bench

Conclusions: In this lab, there are two main issues need to be highly concerned. The first thing to use the frequency divider to make the anode selection and number displaying speed slow enough to been seen. The second thing is to control the display speed and number displaying speed so that we can the four digits illuminate at the same time, and number is always change correctly. At the same time we sent the fastest four digits to the LEDs to let them show the adding movement in binary, and send the slowest frequency signal to the flash signal. The controller part is pretty straightforward.

- 1、下载文档前请自行甄别文档内容的完整性,平台不提供额外的编辑、内容补充、找答案等附加服务。

- 2、"仅部分预览"的文档,不可在线预览部分如存在完整性等问题,可反馈申请退款(可完整预览的文档不适用该条件!)。

- 3、如文档侵犯您的权益,请联系客服反馈,我们会尽快为您处理(人工客服工作时间:9:00-18:30)。

实验四

三、实验内容

离散系统分析

5.利用load mtlb命令读入一段语音信号得到序列 x [ k ] ,然后在该段 语音信号中加入500Hz的正弦型干扰信号得到信号 y [ k ] ,利用 FFT分析其频谱。 (1)下列数字滤波器能够滤除信号 y [ k ] 中500Hz正弦型干扰信号。

(3) 计算前100个时刻的完全响应 filter(b,a,x,zi)中的初始值zi不是y[-1]= 1, y[-2]= 2, 它可以由filtic函数计算。 N=100; b=[1,2]; a=[1,0.4,-0.12]; x=ones(1,N); zi=filtic(b,a,[1,2]); y=filter(b,a,x,zi);

实验四

离散系统分析

1. 离散系统的时域响应

离散系统响应y[k]的计算

y = filter(b, a, x): 计算系统在输入x作用下的零状态响应y[k];

a [1, a 1 , , a N 1 , a N ]

b [ b 0 , b1 , , b M 1 , b M ]

y = filter(b, a, x, zi): 计算系统在输入x和初始状态作用下的完全响应y[k]。 zi是由系统的初始状态经过filtic函数转换而得到的初始条 件:zi= filtic (b, a, Y0) ,Y0为系统的初始状态, Y0= [ y[-1],y[-2],y[-3],...]。

2

2

0 . 1428 z

3

3

0 . 03571 z

4

4

0 . 8264 z

0 . 2605 z

0 . 04033 z

(1)计算系统的单位脉冲响应。 (2)当信号

x [ k ] u [ k ] cos( 4

k ) u [ k ] cos(

2

k )u [ k ]

5

k ) u [ k ]; x 3 [ k ] cos(

7 10

k )u [ k ]

(3)该系统具有什么特性?

实验四

三、实验内容

离散系统分析

2.已知某因果LTI系统的系统函数为:

H (z) 0 . 03571 0 . 1428 z 1 1 . 035 z

1 1

0 . 2143 z

a [1, a 1 , , a N 1 , a N ]

b ] = impz(b, a, n):计算n点单位脉冲响应h[k]; 也可简写为:h = impz(b, a, n)。 impz(b, a):绘制单位脉冲响应h[k]的图形。

再利用 H = Y./X 和 h = ifft(H,N) 可以得到系统的单位脉冲响应h[k]。

实验四

三、 实验内容

离散系统分析

1.已知某LTI系统的差分方程为:

y [ k ] 1 . 143 y [ k 1 ] 0 . 412 y [ k 2 ] 0 . 0675 x [ k ] 0 . 1349 x [ k 1] 0 . 0675 x [ k 2 ]

5

4

Magnitude

3

2

1

0

0

0.5

1

1.5 2 Frequency(rad)

2.5

3

3.5

实验四

离散系统分析

4.利用DTFT和DFT确定离散系统的特性

在很多情况下,需要根据LTI系统的输入和输出对系 统进行辨识,即通过测量系统在已知输入x[k]激励下的响 应y[k]来确定系统的特性。 若系统的脉冲响应为h[k],由于存在y[k]=x[k]* h[k], 因而可在时域通过解卷积方法求解h[k]。 在实际应用中,进行信号解卷积比较困难。因此,通 常从频域来分析系统,这样就可以将时域的卷积转变为频 域的乘积,从而通过分析系统输入序列和输出序列的频率 特性来确定系统的频率特性 H ( e j ) ,再由 H ( e ) 得到系统 的脉冲响应h[k]。

变连续系统的函数,主要包含有系统函数、

系统时域响应、系统频域响应等分析函数。

实验四

离散系统分析

1. 离散系统的时域响应

离散时间LTI系统可用如下的线性常系数差分方程来描述:

y[k ] a1 y[k 1] aN 1 y[k ( N 1)] aN y[k N ]

b0 x[k ] b1 x[k 1] bM 1 x[k ( M 1)] bM x[k M ]

M

N

k

( z z 1 )( z z 2 )...( z z M ) ( z p 1 )( z p 2 )...( z p N )

使用MATLAB提供的roots函数计算离散系统的零极点; 使用zplane函数绘制离散系统的零极点分布图。 注意:在利用这些函数时,要求H(z)的分子多项式和分母多项 式的系数的个数相等,若不等则需要补零。

1 z 1 z

1 1 2

已知某离散系统的系统函数为:

H (z) 0 .5 z

分析系统的幅频特性。

6

Magnitude response

b=[1,1]; a=[1,-1,0.5]; [H,w]=freqz(b,a); plot(w,abs(H)) xlabel('Frequency(rad)'); ylabel('Magnitude'); title('Magnitude response');

a [1, a 1 , , a N 1 , a N ] b [ b 0 , b1 , , b M 1 , b M ]

这些系数均从z0按z的降幂排列。

实验四

离散系统分析

1. 离散系统的时域响应

离散系统的单位冲激响应h[k]的计算 1) [h,k] = impz(b, a):计算系统的单位脉冲响应h[k]和相应 的时间向量k;也可简写为:h = impz(b, a)。其中:

已知输入信号x[k]以及系统初始状态y[-1],y[-2] ..., 就可以求出系统的响应。MATLAB提供了计算差分方程的 数值解的函数,可以计算上述差分方程描述的离散系统的 单位脉冲响应、零状态响应和完全响应等。

实验四

离散系统分析

1. 离散系统的时域响应

在调用MATLAB函数时,需要利用描述该离散系统的系数 函数。对差分方程进行Z变换即可得系统函数:

实验四

已知系统函数为 H ( z )

离散系统分析

1 2z 1 0 .4 z

1 1 2

0 . 12 z

,计算

(1) 离散系统的单位脉冲响应; (2) 输入x[k]= u[k],求系统的零状态响应y[k]; (3) 输入x[k]= u[k],初始条件y[-1]= 1, y[-2]= 2,求系统的完全响应y[k]。

(1)初始状态 y [ 1] 1, y [ 2 ] 2 ,输入 x [ k ] u [ k ] 计算系统的完全响应。 (2)当以下三个信号分别通过系统时,分别计算离散系统 的零状态响应:

x 1 [ k ] cos(

10

k ) u [ k ]; x 2 [ k ] cos(

实验四

三、实验内容

离散系统分析

4.已知某离散系统的输入输出序列。 输入序列:2,0.8333,0.3611,0.162,0.0748,0.0354,0.017, 0.0083,0.0041,0.002,0.001,0.0005,0.0002,0.0001, 0.0001,后面的数值均趋于0; 输出序列:0.0056,-0.0259,0.073,-0.1593,0.297, -0.4974,0.7711,-1.1267,1.5702,-2.1037,2.724,-3.4207, 4.174,-4.9528,5.7117,-6.3889,6.9034,-7.1528,7.012, -6.3322,4.9416,-2.648,-0.7564,5.4872,-11.7557, 19.7533,-29.6298,41.4666,-55.2433,70.7979,-87.7810 (1)绘出输入输出信号的波形。 (2)计算该系统的频率响应 ,并绘出其幅频特性。 j H (e (3)计算该系统的单位脉冲响应 ) ,并绘出其波形。

H (z) Y (z) X (z) b 0 b1 z 1 a1 z

1 1

b M 1 z a N 1 z

( M 1 ) ( N 1 )

bM z aN z

M

N

b( z) a(z)

在MATLAB中可使用向量a和向量b分别保存分母多项式和 分子多项式的系数:

实验四

离散系统分析

2.离散系统的系统函数零极点分析

离散LTI系统的系统函数H(z)可以表示为零极点形式:

H (z) Y (z) X (z) b 0 b1 z 1 a1 z

1 1

b M 1 z a N 1 z

( M 1 ) ( N 1 )

bM z aN z

通过系统时,计算系统的零状态响应。

实验四

三、实验内容

离散系统分析

3.已知LTI系统的输入输出序列分别为

( a ) x [ k ] ( ) u [ k ], 2

k

1

1 1 k 1 k y[ k ] ( ) u[ k ] ( ) u[ k ] 4 2 4 1 k 1 k 1 y [ k ] ( ) u [ k ] ( ) u [ k 1] 4 4

)e

j ( )

[H, w]=freqz(b, a, n): 计算系统的n点频率响应H,w为频率点向量。 H=freqz(b, a, w) :计算系统在指定频率点向量w上的频响; freqz(b,a): 绘制频率响应曲线。 其中:b和a分别为系统函数H(z)的分子分母系数矩阵;